# FS450, FS451 i-Net TV Interface Video Processor

#### **Features**

- Flexible clock, data, and electrical interfaces allows glue-less digital interface to Intel 82810, National Geode and most other graphic controller chips ("GCC")

- Capable of operating as clock master, pseudo-master, and slave and supports both single and differential master clocks

- Programmable 2D scaling †

- Variable horizontal up and down scale

- Variable vertical downscale

- Output format can be tuned to the exact dimensions of the TV

- Advanced 2-D flicker filter †

- Supports Multiple Progressive Input Resolutions

- 640x480 to 1024x768

- Multiple Output Standards

- NTSC, NTSC-EIAJ, PAL-B/D/G/H/I/M/N

- Composite, S-Video, RGB SCART

- Composite Y-Notch and C-Bandpass Filters

- Genlock the GCC and incoming Video

- Provides the pixel clock to the GCC generated from a single 27MHz clock

- Provides frame synchronization output signal for other video components

- CCIR 656 outputs

- CCIR 656 input to the encoder

- 10-bit output D/A converters

- Macrovision 7 compliant (FS451 only)

- I<sup>2</sup>C<sup>‡</sup> compatible port controls

- High level programming interface

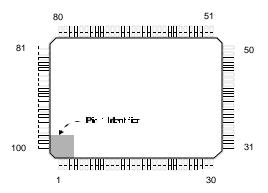

- 100 pin PQFP package

- 3.3V operation

†Note: Covered under US Patent # 5,862,268 and/or patents pending.

<sup>‡</sup>Note:  $^{\circ}$ C is a registered trademark of Philips Corporation. The FS450 SIO bus is similar but not identical to Philips  $^{\circ}$ C bus

#### **Description**

The i-Net TV FS450 is a fourth generation video scan converter. It accepts many input resolutions, rates and formats and converts them to NTSC or PAL standards compliant with SMPTE-170M and CCIR-656 standards. The chip

has a programmable down scaler to fit the incoming resolution to the output display format. The CCIR 656 ports allow external interface to other video chips. The sync control block generates frame reset for genlocking other video components. Required external components are minimal: a single 27 MHz oscillator or crystal and passive parts.

Digital progressive RGB inputs are downscaled or upscaled to the CCIR-656 horizontal pixel count and converted to the 656 format. Vertical scaling and flicker filtering are done in 656 format.

The Flicker Filter is an advanced 2 dimensional filter that enhances text quality. Flicker Filter and Sharpness parameters are programmable.

A digital video encoder that generates analog Y/C and Composite Video outputs is part of the FS450. For the composite output in NTSC, Y-Notch and C-Bandpass filters are available. For RGB and YUV outputs, the encoder may be bypassed via a YUV to RGB transcoder for SCART compatible video.

Scaling and clock parameters are automatically programmed by the driver, so the system remains genlocked with resolution changes. The input parameters to the automatic scaling are TV viewable area, PAL or NTSC, and the GCC CRT Control Registers' settings.

The FS451's encoder incorporates Macrovision 7 anti-copy protection technology.

All parameters can be read and written via the I<sup>2</sup>C compatible serial port.

Power is derived from +3.3V digital and analog supplies. The package is 100-lead Quad Flat Pack (PQFP).

#### **Applications**

- Internet Set Top Boxes

- PC video out (TV Ready PCs)

- Cable/DVD Player Set Top Boxes

- Web Appliances

- Information Appliances

- Video Kiosks

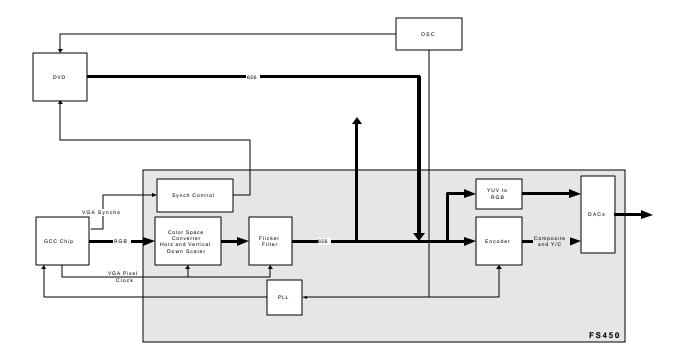

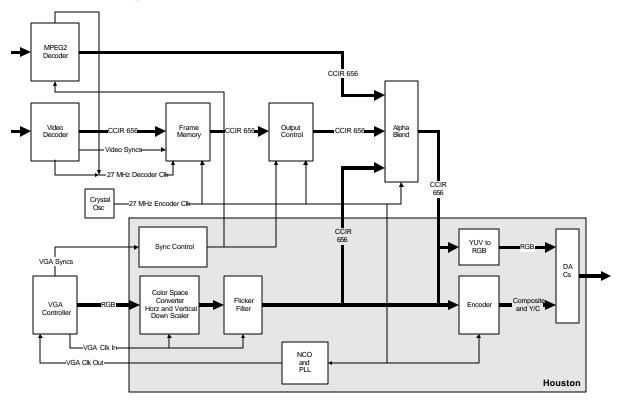

## **Typical System Architectural Block Diagram**

Figure 1: Typical System Block Diagram

# 1. Table of Contents, Figures & Tables

| 1. |                 | f Contents, Figures & Tables             | 3   | 6.2.      | 19 Chroma Phase, Miscellaneous          |        |

|----|-----------------|------------------------------------------|-----|-----------|-----------------------------------------|--------|

| 2. |                 | ctural Overview                          | 5   |           | 45                                      |        |

|    |                 | llators and PLLs                         |     | 6.2.2     |                                         |        |

|    |                 | al Control Port                          |     |           | and 47                                  |        |

|    |                 | Control                                  |     | 6.2.2     |                                         |        |

|    |                 | and Output Frame Formats                 |     |           | (49)                                    |        |

|    |                 | r Space Converter and Scaler             |     | 6.2.2     | ` , ;                                   |        |

|    |                 | er Filter                                |     |           | Amplitude (4B)                          | 40     |

|    |                 | oder                                     |     | 6.2.2     | • • • • • • • • • • • • • • • • • • • • |        |

|    | 2.8 YUV         | to RGB Converter                         | 7   |           | Miscellaneous Bits Register 4D          | 0 . 41 |

| 3. | Typical         | System Configurations                    | 8   | 6.2.2     | 24 Black Level (4E)                     | 41     |

|    | 3.1 GCC         | ⇒ TV Output Only                         | 8   | 6.2.2     | 25 Blank Level (50)                     | 42     |

|    | 3.2 GCC         | or DVD Output Switched $\Rightarrow$ TV. | 9   | 6.2.2     | 26 Number of Lines (57-58)              | 42     |

|    | 3.3 Multi       | ple Digital Video Sources Blende         | d   | 6.2.2     | 27 White Level (5E)                     | 43     |

|    | $\Rightarrow T$ | /                                        | 10  | 6.2.2     | 28 Cb Color Saturation (60)             | 43     |

| 4. | Pin Ass         | signments                                | 11  | 6.2.2     | 29 Cr Color Saturation (62)             | 43     |

|    | 4.1 FS45        | 50 ⇔ GCC Pin Mapping                     | 12  | 6.2.3     | 30 Tint (65)                            | 44     |

| 5. |                 | scriptions                               | 13  | 6.2.3     |                                         |        |

| 6. | Control         | Register Definitions                     | 16  | 6.2.3     |                                         |        |

|    | 6.1 Cont        | rol Register Map                         | 16  | 6.2.3     | 33 Active Video Line (71-72), First     |        |

|    |                 | rol Register Definitions                 |     |           | Video Line (73)                         |        |

|    | 6.2.1           | IHO - Input Horizontal Offset            | 20  | 6.2.3     | 34 Miscellaneous Bits 74, Sync Le       | evel   |

|    | 6.2.2           | IVO - Input Vertical Offset              |     |           | (75)                                    |        |

|    | 6.2.3           | IHW - Input Horizontal Width             | 21  | 6.2.3     | • •                                     |        |

|    | 6.2.4           | VSC - Vertical Scaling Coefficie         |     | 6.2.3     | , ,                                     |        |

|    | 6.2.5           | HDSC, HUSC – Horizontal                  |     |           | Soft Reset, Encoder Version             |        |

|    |                 | Down/Up Scaling Coefficients             | 22  | 6.2.3     |                                         |        |

|    | 6.2.6           | CR - Command Register                    |     |           | 82), WSS Data F1(83-85)                 | •      |

|    | 6.2.7           | SP - Status Port                         |     | 6.2.3     | , , ,                                   |        |

|    | 6.2.8           | NCON - Numerator of NCO Wor              |     |           | Line Number Field 1 (89)                |        |

|    | 6.2.9           | NCOD - Denominator of NCO V              |     | 6.2.3     | • ,                                     |        |

|    |                 |                                          |     |           | Level, Misc. Bits Reg. 8D (8A-8         |        |

|    | 6.2.10          | APO, ALO, AFO - Auxiliary Pix            | el. | 7. Design | gn and Layout Considerations            | 52     |

|    |                 | Line, and Field Offsets                  |     |           | xel Phase Lock Loop                     | 52     |

|    | 6.2.11          | HSOUTWID, HSOUTST,                       |     |           | deo Output Filters                      |        |

|    |                 | HSOUTEND - HSync Out Width               | ٦,  |           | nalog Power Supply Bypassing,           |        |

|    |                 | Starting and Ending Edge                 |     |           | tering, and Isolation                   | 52     |

|    | 6.2.12          | SHP, FLK - Sharpness and Flic            |     |           | ower and Ground                         |        |

|    |                 | Filter                                   |     |           | terfacing to the FS450 in a Mixed       |        |

|    | 6.2.13          | REV - Revision Number                    |     |           | oltage Environment                      | 53     |

|    | 6.2.14          |                                          |     | 7.5.      | _                                       |        |

|    |                 | Register                                 |     |           | ifications                              | 55     |

|    | 6.2.15          | FIFOL, FIFOH - FIFO Status Po            |     | •         | solute Maximum and Recommend            | ed     |

|    |                 | Full/Empty                               |     |           | atings                                  |        |

|    | 6.2.16          | FFO_LAT - FIFO Latency                   |     |           | ectrical Characteristics                |        |

|    | 6.2.17          | -                                        |     |           | vitching Characteristics                |        |

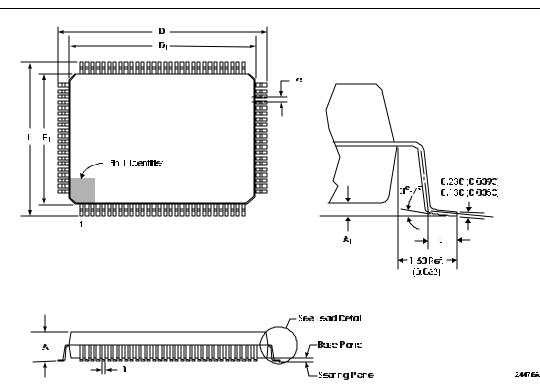

|    |                 | VSOUTEND - VSync Out Width               | ٦.  |           | nanical Dimensions                      | 58     |

|    |                 | Starting and Ending Edge                 |     |           | 0-Lead PQFP (KH) Package                |        |

|    | 6.2.18          |                                          |     |           | sion History                            | 59     |

|    |                 | Frequency                                |     |           | r Information                           | 59     |

| Figure 1: Typical System Block Diagram           | 2  |

|--------------------------------------------------|----|

| Figure 2: FS450 Functional Block Diagram         |    |

| Figure 3: GCC Frame Format                       | 6  |

| Figure 4: CCIR 601/656 Field Format              | 7  |

| Figure 5: GCC ⇒ TV Output Only                   | 8  |

| Figure 6: GCC or DVD output switched ⇒ TV        | 9  |

| Figure 7: Multiple digital video sources blended |    |

| ⇒ TV                                             | 10 |

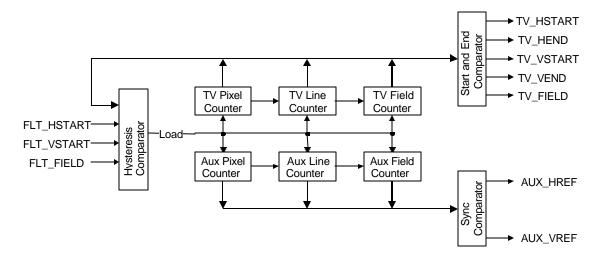

| Figure 8: CCIR 656 Timing Block Diagram          | 30 |

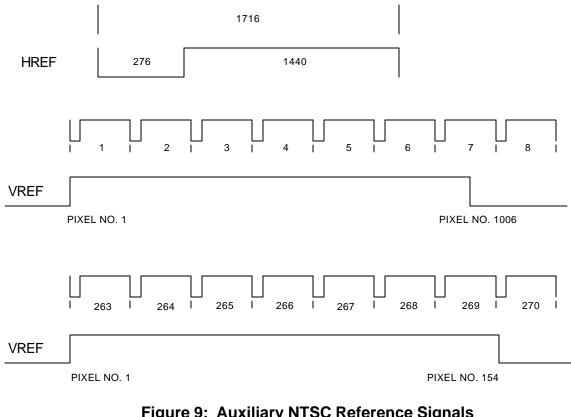

| Figure 9: Auxiliary NTSC Reference Signals       | 31 |

| Figure 10: Auxiliary PAL Reference Signals       | 31 |

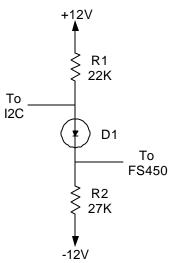

| Figure 11. SIO Translation Using Long-tail       |    |

| Resistors D1 = 1N4148                            | 53 |

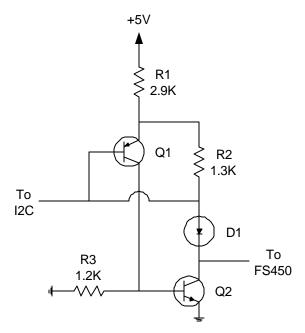

| Figure 12. SIO Translation Using Current Mirrors |    |

| D1 = 1N4148, Q1 = 2N3906, Q2 = 2N3904            | 54 |

| Figure 13: Package Outline & Dimensions          | 58 |

| rable i. | F545X Pin Assignments               |    |

|----------|-------------------------------------|----|

| Table 2: | FS450 to GCC Pin Mapping            | 12 |

| Table 3: | SAV and EAV Control Words           | 24 |

| Table 4: | GCC Port Mapping (UIM_MOD)          | 24 |

| Table 5: | NCO_LOAD Control Bits               | 34 |

| Table 6: | NOTCH_FRQ Values                    | 50 |

| Table 7: | Typical Register Values for Various |    |

| Sta      | ndards                              | 5′ |

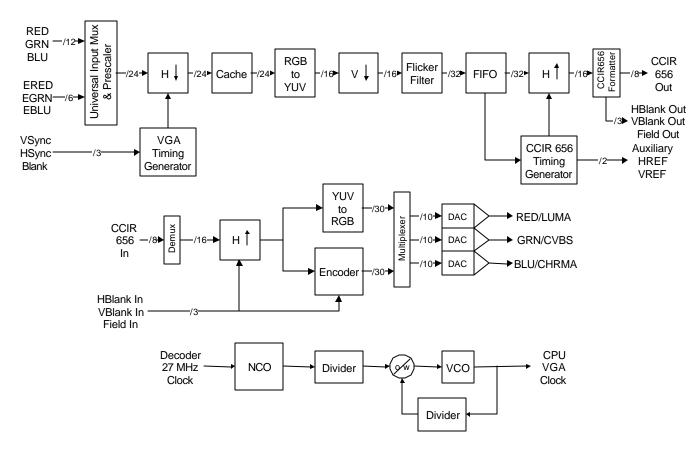

#### 2. Architectural Overview

The FS450 i-Net TV Video Interface Processor provides NTSC or PAL TV out for Intel's 82810 Video Co-processor and many other 3D graphic controller ("GCC") chips. It accepts digital RGB in, converts it to CCIR 656 digital video, provides interfaces to external 656 digital DVD systems, windowing hardware, alpha blenders, et al and outputs very high quality RGB, YUV, S-Video, or Composite Video. The chip consists of the following major sections:

- · Oscillators and PLLs

- Serial Control Port

- Sync Control

- Input and Output Frame Formats

- Color Space Converter & Scaler

- Flicker Filter

- Encoder

- YUV to RGB Converter

Figure 2: FS450 Functional Block Diagram

#### 2.1 Oscillators and PLLs

The FS450 synthesizes a 27 to 85 MHz clock off of the 27 MHz Television clock and supplies this clock (VGA\_CKOUT) to the GCC. This clock is buffered and returned to the FS450 (VGA\_CKIN) synchronous to the RGB data and Sync information. This clock has a 1½ Hz resolution and must be adjusted so the GCC scaled input data rate exactly matches the CCIR 656 data output rate.

The VG\_CKOUT Phase Lock Loop (PLL) synthesizer uses Numerically Controlled Oscillator (NCO) to fine adjust the 27MHz oscillator to a clock precisely matched to the digital RGB data coming from the GCC. Additionally, the PLL itself can be controlled by programming the numerator (M) and denominator (N) of the PLL itself. The combination of the PLL synthesizer and NCO are used to precisely match the input to the output.

#### 2.2 Serial Control Port

FS450 setup is programmed by registers that are accessible via the I<sup>2</sup>C<sup>‡</sup> compatible serial port (SIO). Status and Revision ID can also be read from the registers.

<sup>‡</sup>Note: I<sup>2</sup>C is a registered trademark of Philips Corporation. The FS450 SIO bus is similar but not identical to Philips I<sup>2</sup>C bus.

### 2.3 Sync Control

The FS450 operates in a slave mode, pseudo-master mode or full master mode. In pseudo-master mode, the GCC graphic controller derives the VGA pixel clock, horizontal sync, and vertical sync from VGA\_CLKOUT supplied by the FS450. The syncs are used inside the FS450 to capture the computer video and are regenerated to supply to external devices such as genlocked video from a DVD player or tuner. In full master mode, the FS450 supplies to the GCC horizontal and vertical sync in addition to the VGA pixel clock.

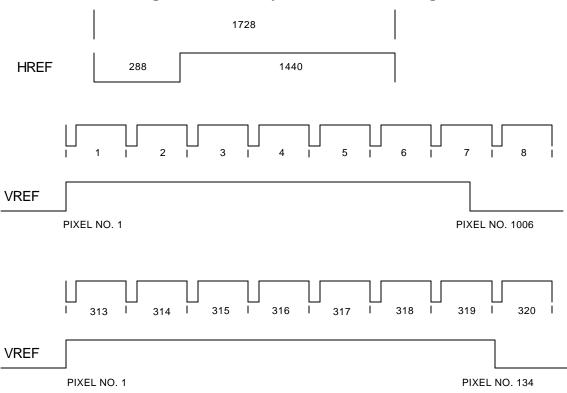

### 2.4 Input and Output Frame Formats

The FS450 does not contain a frame memory. Therefore, the FS450 output frame rate must be synchronous to the input frame rate. To accomplish this, the active video portion in the output stream must overlay the corresponding active video time in the input stream. Several registers on the FS450 control this timing as illustrated in the following figures:

|           | VGA_H | ISYNC<br>IHO |              | В     |           |

|-----------|-------|--------------|--------------|-------|-----------|

| VGA_VSYNC |       |              | Α            |       | IHO + IHW |

| IVO       | Blank | Blank        | Blank        | Blank | Blank     |

| С         | Blank | Black        | Black        | Black | Blank     |

| D         | Blank | Black        | Active Video | Black | Blank     |

| IVO + IVW | Blank | Black        | Black        | Black | Blank     |

|           | Blank | Blank        | Blank        | Blank | Blank     |

Figure 3: GCC Frame Format

IHO = OHO / Hscale IVO = OVO / Vscale IHW = OHW / Hscale IVW = OVW / Vscale

The output frame timing is determined by the CCIR601 and 656 specifications. Input parameters IHO, IVO, and IHW must be set correctly so that when the image is scaled to the 656 output frame, the timing requirements are met. Parameters A, B, C, and D are determined by the amount of underscan the user wants on the target television screen.

|           | 656_H | SYNC<br>OHO |              | <b>B</b> ^ |           |

|-----------|-------|-------------|--------------|------------|-----------|

| 656_VSYNC |       |             | A^           |            | OHO + OHW |

| OVO       | Blank | Blank       | Blank        | Blank      |           |

| C^        | Blank | Black       | Black        | Black      |           |

| D^        | Blank | Black       | Active Video | Black      |           |

| OVO + OVW | Blank | Black       | Black        | Black      |           |

|           | Blank | Blank       | Blank        | Blank      |           |

Figure 4: CCIR 601/656 Field Format

OHO = 139 NTSC, 145 PAL OVO = 20 NTSC, 23 PAL OHW = 720 OVW = 487 NTSC, 576 PAL

### 2.5 Color Space Converter and Scaler

The digital RGB from the GCC is horizontally compressed, stored into a line buffer cache. As the data is pulled from the line buffer cache, it is converted to 656 YUV and compressed vertically.

#### 2.6 Flicker Filter

The FS450 flicker filter provides significantly more control over the display characteristics than a typical 3 line average flicker filter. The FS450's flicker filter consists of both horizontal (Sharpness) and vertical (Flicker) controls. Thus, it is called a 2D flicker filter. Both the Sharpness and Flicker registers can be programmed over a wide range to allow the user to tradeoff flicker and sharpness for readability and reduced eye fatigue.

#### 2.7 Encoder

The FS450 contains a high quality 2x oversampled video encoder. The 656 luma information is up-sampled from 13.5 MHz sample rate to 27 MHz with a 19 tap filter which offers excellent flatness to 6MHz and 50 dB image aliasing suppression. Chrominance information is up-sampled from 6.75MHz sample rate to 27 MHz with four user selectable bandwidths. The encoder has programmable width and frequency luma notch filter.

The encoder subcarrier is programmable in frequency and phase and with the independence of color format, vsync, and number of lines allows for the support of the many video standards, including all South American variations. The FS450 video encoder outputs NTSC M, J and PAL B, D, G, H, I, M, N, Combination N formats with 10 bits of resolution. Both Composite and S-Video outputs are available simultaneously.

#### 2.8 YUV to RGB Converter

As an alternative to encoded PAL or NTSC, the user may select analog RGB outputs. Each channel of RGB has 10 bits of resolution.

## 3. Typical System Configurations

There are 3 "typical" system configurations envisioned for the FS450:

- 1) GCC  $\Rightarrow$  TV output only;

- 2) GCC or DVD output switched  $\Rightarrow$  TV;

- 3) Multiple digital video sources blended  $\Rightarrow$  TV.

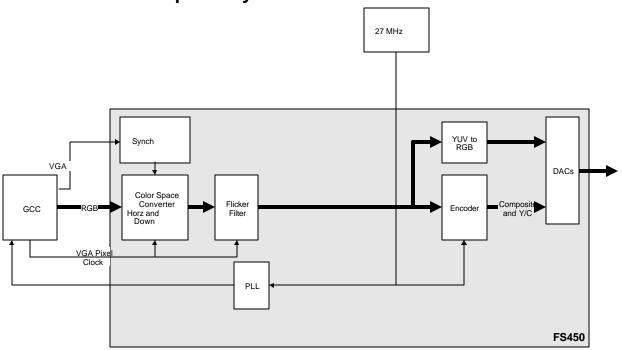

### 3.1 GCC P TV Output Only

Figure 5: GCC P TV Output Only

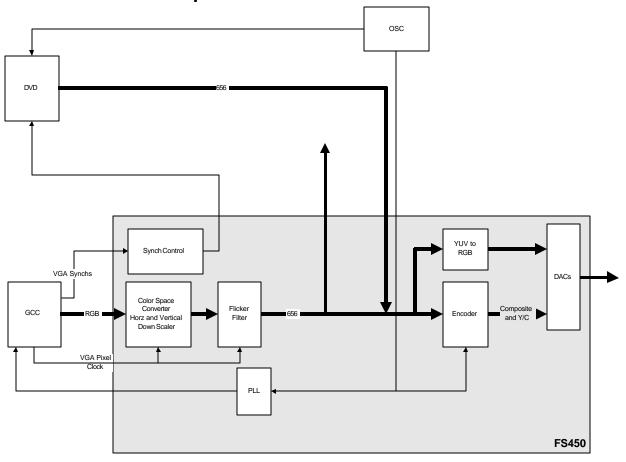

# 3.2 GCC or DVD Output Switched P TV

Figure 6: GCC or DVD output switched P TV

# 3.3 Multiple Digital Video Sources Blended P TV

Figure 7: Multiple digital video sources blended P TV

# 4. Pin Assignments

| Pin   | Name                | Pin   | Name            | Pin   | Name                  | Pin    | Name                  |

|-------|---------------------|-------|-----------------|-------|-----------------------|--------|-----------------------|

| 1. R  | TV_CKIN             | 31. P | VGA_CKOUT       | 51. R | P <sub>2</sub>        | 81. O  | V656_OUT <sub>4</sub> |

| 2. O  | XTAL                | 32. R | V <sub>SS</sub> | 52. R | P <sub>3</sub>        | 82. R  | $V_{DD}$              |

| 3. R  | V <sub>DDOSC</sub>  | 33. R | $V_{DD}$        | 53. R | P <sub>4</sub>        | 83. O  | V656_OUT <sub>5</sub> |

| 4. R  | V <sub>ssosc</sub>  | 34. O | Reserved (open) | 54. R | P <sub>5</sub>        | 84. O  | V656_OUT <sub>6</sub> |

| 5. G  | Reserved (GND)      | 35. O | Reserved (open) | 55. R | GTL_REF               | 85. O  | V656_OUT <sub>7</sub> |

| 6. N  | Reserved (open)     | 36. S | E₅              | 56. R | $V_{DD}$              | 86. R  | V <sub>SS</sub>       |

| 7. R  | V <sub>SSDA</sub>   | 37. O | E <sub>4</sub>  | 57. R | P <sub>6</sub>        | 87. S  | FIELD_IN              |

| 8. R  | $V_{REF}$           | 38. R | V <sub>SS</sub> | 58. R | P <sub>7</sub>        | 88. S  | VBNK_IN               |

| 9. R  | R <sub>REF</sub>    | 39. O | VGA_CKOUTTL     | 59. R | P <sub>8</sub>        | 89. S  | HBNK_IN               |

| 10. R | $V_{DDDA}$          | 40. O | $E_3$           | 60. R | $P_9$                 | 90. R  | $V_{DD}$              |

| 11. R | C <sub>BYPASS</sub> | 41. O | E <sub>2</sub>  | 61. R | V <sub>SS</sub>       | 91. S  | V656_IN <sub>0</sub>  |

| 12. O | Y/Red               | 42. O | E <sub>1</sub>  | 62. R | P <sub>10</sub>       | 92. S  | V656_IN <sub>1</sub>  |

| 13. R | $V_{DDDA}$          | 43. O | E <sub>0</sub>  | 63. R | P <sub>11</sub>       | 93. S  | V656_IN <sub>2</sub>  |

| 14. R | V <sub>SSDA</sub>   | 44. R | BLANK           | 64. R | VGA_NCKIN             | 94. S  | V656_IN <sub>3</sub>  |

| 15. O | CVBS/Green          | 45. R | $V_{DD}$        | 65. R | VGA_PCKIN             | 95. R  | $V_{SS}$              |

| 16. R | $V_{DDDA}$          | 46. R | VSYNC_IN        | 66. R | $V_{DD}$              | 96. S  | V656_IN <sub>4</sub>  |

| 17. O | C/Blue              | 47. R | HSYNC_IN        | 67. O | AVREF                 | 97. S  | V656_IN <sub>5</sub>  |

| 18. R | $V_{DDDA}$          | 48. R | $P_0$           | 68. O | VSYNC_OUT             | 98. S  | V656_IN <sub>6</sub>  |

| 19. O | CSYNC               | 49. R | P <sub>1</sub>  | 69. O | AHREF                 | 99. S  | V656_IN <sub>7</sub>  |

| 20. N | Reserved (open)     | 50. R | $V_{SS}$        | 70. R | $V_{SS}$              | 100. N | Reserved (open)       |

| 21. N | Reserved (open)     |       |                 | 71. O | HSYNC_OUT             |        |                       |

| 22. R | $V_{DDPA}$          |       |                 | 72. O | FIELD_OUT             |        |                       |

| 23. R | SCLK                |       |                 | 73. O | VBNK_OUT              |        |                       |

| 24. R | SDATA               |       |                 | 74. R | $V_{DD}$              |        |                       |

| 25. R | SA <sub>10/7</sub>  |       |                 | 75. O | HBNK_OUT              |        |                       |

| 26. R | SA <sub>0</sub>     |       |                 | 76. O | V656_OUT <sub>0</sub> |        |                       |

| 27. R | V <sub>SSPA</sub>   |       |                 | 77. O | V656_OUT <sub>1</sub> |        |                       |

| 28. R | RESET               |       |                 | 78. R | V <sub>SS</sub>       |        |                       |

| 29. G | Reserved (GND)      |       |                 | 79. O | V656_OUT <sub>2</sub> |        |                       |

| 30. G | Reserved (GND)      |       |                 | 80. O | V656_OUT <sub>3</sub> |        |                       |

Table 1: FS45x Pin Assignments

R = Signal Required

O = Signal if used, else no connect

S = Signal if used, else ground

G = Always Ground N = Always No Connect

### 4.1 FS450 Û GCC Pin Mapping

The following table maps the FS450/1 pins to the host GCC controller chip. Please contact your FOCUS representative to obtain the most up-to-date reference schematics before initiating a design.

| FS450<br>Pin # | FS450/1<br>Pin Name | Intel<br>82810<br>Pin Name<br>UIM_MOD=0 | National<br>Cx5530<br>MediaGX<br>UIM_MOD=3 | nVidia<br>Riva TNT<br>Pin Name<br>UIM_MOD=1 | S3<br>Savage<br>Pin Name<br>UIM_MOD=1 |

|----------------|---------------------|-----------------------------------------|--------------------------------------------|---------------------------------------------|---------------------------------------|

| 31             | VGA_CKOUT           | TVCLKIN                                 |                                            |                                             |                                       |

| 39             | VGA_CKOUTTL         |                                         | TVCLK                                      | TVCLKIN                                     | TVCLK                                 |

| 65             | VGA_PCKIN           | CLKOUT0                                 |                                            |                                             |                                       |

| 64             | VGA_NCKIN           | CLKOUT1                                 | FP_CLK                                     | TVCLKOUT                                    | TVCLKR                                |

| 47             | HSYNC_IN            | TVHSYNC                                 | FP_HSYNC_OUT                               |                                             | TVHS                                  |

| 46             | VSYNC_IN            | TVVSYNC                                 | FP_VSYNC_OUT                               |                                             | TVVS                                  |

| 71             | HSYNC_OUT           |                                         |                                            | TVHSYNC                                     |                                       |

| 68             | VSYNC_OUT           |                                         |                                            | TVVSYNC                                     |                                       |

| 44             | BLANK               | BLANK                                   |                                            |                                             | BLANK                                 |

| 48             | P <sub>0</sub>      | LTVDATA0                                | FP_DATA6                                   | TVD0                                        | TVDAT0                                |

| 49             | P <sub>1</sub>      | LTVDATA1                                | FP_DATA7                                   | TVD1                                        | TVDAT1                                |

| 51             | P <sub>2</sub>      | LTVDATA2                                | FP_DATA8                                   | TVD2                                        | TVDAT2                                |

| 52             | P <sub>3</sub>      | LTVDATA3                                | FP_DATA9                                   | TVD3                                        | TVDAT3                                |

| 53             | P <sub>4</sub>      | LTVDATA4                                | FP_DATA10                                  | TVD4                                        | TVDAT4                                |

| 54             | P <sub>5</sub>      | LTVDATA5                                | FP_DATA11                                  | TVD5                                        | TVDAT5                                |

| 57             | P <sub>6</sub>      | LTVDATA6                                | FP_DATA12                                  | TVD6                                        | TVDAT6                                |

| 58             | P <sub>7</sub>      | LTVDATA7                                | FP_DATA13                                  | TVD7                                        | TVDAT7                                |

| 59             | P <sub>8</sub>      | LTVDATA8                                | FP_DATA14                                  | TVD8                                        | TVDAT8                                |

| 60             | P <sub>9</sub>      | LTVDATA9                                | FP_DATA15                                  | TVD9                                        | TVDAT9                                |

| 62             | P <sub>10</sub>     | LTVDATA10                               | FP_DATA16                                  | TVD10                                       | TVDAT10                               |

| 63             | P <sub>11</sub>     | LTVDATA11                               | FP_DATA17                                  | TVD11                                       | TVDAT11                               |

| 43             | E <sub>0</sub>      |                                         | FP_DATA0                                   |                                             |                                       |

| 42             | E <sub>1</sub>      |                                         | FP_DATA1                                   |                                             |                                       |

| 41             | E <sub>2</sub>      |                                         | FP_DATA2                                   |                                             |                                       |

| 40             | E <sub>3</sub>      |                                         | FP_DATA3                                   |                                             |                                       |

| 37             | E <sub>4</sub>      |                                         | FP_DATA4                                   |                                             |                                       |

| 36             | E <sub>5</sub>      |                                         | FP_DATA5                                   |                                             |                                       |

| 23             | SCLK                | LTVCL                                   | DDC_SCL                                    | SPSCL                                       | SPCLK1                                |

| 24             | SDATA               | LTVDA                                   | DDC_SDA                                    | SPSDA                                       | SPD1                                  |

Table 2: FS450 to GCC Pin Mapping

# 5. Pin Descriptions

| Pin             | Pin        | Type/Value      | Pin Function Description                                     |  |

|-----------------|------------|-----------------|--------------------------------------------------------------|--|

| Name            | Number     |                 |                                                              |  |

| Clocks          |            |                 |                                                              |  |

| VGA_CKOUT       | 31         | GTLP output     | VGA Clock Output. Clock to GCC TVCLKIN. Synthesized          |  |

|                 |            | (open drain)    | from TV_CKIN. 27 to 85 MHz range.                            |  |

| VGA_CKOUTTL     | 39         | LVTTL output    | VGA Clock Output. Clock to GCC TVCLKIN. Synthesized          |  |

|                 |            |                 | from TV_CKIN. 27 to 85 MHz range.                            |  |

| VGA_PCKIN       | 65         | GTLP input      | VGA Clock Input Positive Edge. Clock from GCC                |  |

|                 |            |                 | CLKOUT, buffered form of VGA_CKOUT. Used to latch rising     |  |

|                 |            |                 | edge RGB data.                                               |  |

| VGA_NCKIN       | 64         | GTLP input      | VGA Clock Input Negative Edge. Clock from GCC                |  |

|                 |            |                 | CLKOUT, buffered form of VGA_CKOUT. Used to latch            |  |

|                 |            |                 | negative edge RGB data.                                      |  |

| TV_CKIN         | 1          | LVTTL input     | Television Clock Input. Clock for the CCIR 656 I/O and the   |  |

|                 |            |                 | video encoder. 27 MHz.                                       |  |

| XTAL            | 2          | LVTTL output    | Television Clock XTAL Output. Buffered version of            |  |

|                 |            |                 | TV_CKIN. For use with a 27 MHz crystal.                      |  |

| HSYNC_OUT       | 71         | LVTTL output    | ·                                                            |  |

|                 |            |                 | mode operation.                                              |  |

| VSYNC_OUT       | 68         | LVTTL output    | VSYNC Output. Output from FS450 to GCC to support slave      |  |

| mode operation. |            | mode operation. |                                                              |  |

| Global Controls |            |                 |                                                              |  |

| RESET           | 28         | TTL input       | Reset. Active Low. Resets internal state machines and        |  |

|                 |            | (pull down)     | initializes default register values.                         |  |

| Reserved        | 5,29,30    | TTL input       | Reserved Inputs. Connect to VSS.                             |  |

|                 |            | (ground)        |                                                              |  |

| Reserved        | 6,20,21,   | LVTTL output    | Reserved Outputs. Do not connect.                            |  |

|                 | 34,35,100  | (leave open)    |                                                              |  |

| Digital RGB Inp |            | T               | T                                                            |  |

| P11-P0          | 63,62,60,5 | GTLP input      | Digital GTLP port input. Digital video input, multiplexed or |  |

|                 | 9,58,57,54 |                 | non-multiplexed. Connects to GCC's digital video out.        |  |

|                 | ,53,52,51, |                 |                                                              |  |

|                 | 49,48      |                 |                                                              |  |

| E5-E0           | 36,37,40,4 | GTLP input      | Digital GTLP port input. Non-multiplexed extended digital    |  |

|                 | 1,42,43    |                 | video input. Connects to GCC's digital video out.            |  |

| GTL_REF         | 55         | GTLP REF        | Digital GTLP Reference input. Voltage threshold reference    |  |

|                 |            |                 | for GTLP inputs. Reference is 1.0 volts.                     |  |

| HSYNC_IN        | 47         | GTLP input      | Digital HSYNC VGA input. Connects to GCC TVHSYNC.            |  |

| VSYNC_IN        | 46         | GTLP input      | Digital VSYNC VGA input. Connects to GCC TVVSYNC.            |  |

| BLANK           | 44         | GTLP input      | Digital BLANK VGA input. True outside of GCC active          |  |

|                 |            |                 | area. Connects to GCC BLANK#.                                |  |

| Pin                    | Pin                             | Type/Value               | Pin Function Description                                                                                                                                                                                                                                                                                                    |  |

|------------------------|---------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                   | Number                          |                          |                                                                                                                                                                                                                                                                                                                             |  |

| Video Outputs          |                                 |                          |                                                                                                                                                                                                                                                                                                                             |  |

| Y/Red                  | 12                              | analog video             | Video output. As programmed by Command Register OFMT bit:  0 Luminance component Y of S-video.  1 Red component of RGB.                                                                                                                                                                                                     |  |

| CVBS/Green             | 15                              | analog video             | Video output. As programmed by Command Register OFMT bit:  0 Composite video. 1 Green component of RGB.                                                                                                                                                                                                                     |  |

| C/Blue                 | 17                              | analog video             | Video output. As programmed by Command Register OFMT bit:  0 Chrominance component of S-video.  1 Blue component of RGB.                                                                                                                                                                                                    |  |

| CSYNC                  | 19                              | LVTTL output             | ut Composite sync output. Active high digital composite sync for SCART video outputs.                                                                                                                                                                                                                                       |  |

| Voltage Reference      |                                 |                          |                                                                                                                                                                                                                                                                                                                             |  |

| VREF                   | 8                               | +1.276 V                 | Voltage reference input/output. If unconnected, except for a 0.1µF capacitor to ground for noise decoupling, the internal 1.276 Volt band-gap reference will be supplied to the three D/A Converters. An external 1.276 Volt reference connected to the V <sub>REF</sub> pin, will override the internal voltage reference. |  |

| R <sub>REF</sub>       | 9                               | 390/780Ω                 | <b>Reference resistor.</b> Connected between R <sub>REF</sub> and ground, this resistor sets the current range of the D/A converters. Use $390\Omega$ for a $37.5\Omega$ load and $780\Omega$ for a $75\Omega$ load.                                                                                                        |  |

| CBYPASS                | 11                              | 0.1 μF                   | Bypass Capacitor. A 0.1μF capacitor must be connected between C <sub>BYPR</sub> and V <sub>DDDA</sub> to reduce noise at the D/A outputs.                                                                                                                                                                                   |  |

| CCIR 656 Input         | Port                            |                          |                                                                                                                                                                                                                                                                                                                             |  |

| V656_IN <sub>7-0</sub> | 99,98,97,9<br>6,94,93,92<br>,91 | TTL input<br>(pull down) | Digital CCIR 656 port input. 8 bits wide. Y, Cr, Cb multiplexed digital input port                                                                                                                                                                                                                                          |  |

| HBNK_IN                | 89                              | TTL input<br>(pull down) | <b>Digital TV Horizontal Blank input</b> . Horizontal Blank for use with the V656_IN ports.                                                                                                                                                                                                                                 |  |

| VBNK_IN                | 88                              | TTL input<br>(pull down) | <b>Digital TV Vertical Blank input.</b> Vertical Blank for use with the V656_IN ports.                                                                                                                                                                                                                                      |  |

| FIELD_IN               | 87                              | TTL input (pull down)    | <b>Digital TV Field input.</b> Field bit for use with the V656_IN ports.                                                                                                                                                                                                                                                    |  |

| Pin                     | Pin        | Type/Value   | ue Pin Function Description                                                |  |

|-------------------------|------------|--------------|----------------------------------------------------------------------------|--|

| Name                    | Number     |              |                                                                            |  |

| CCIR 656 Outp           | ut Port    |              |                                                                            |  |

| V656_OUT <sub>7-0</sub> | 85,84,83,8 | LVTTL output | Digital CCIR 656 port output. 8 bits wide. Y, Cr, Cb                       |  |

|                         | 1,80,79,77 |              | multiplexed digital output port                                            |  |

|                         | ,76        |              |                                                                            |  |

| HBNK_OUT                | 75         | LVTTL output | Digital TV Horizontal Blank output. Horizontal Blank for                   |  |

|                         |            |              | use with the V656_OUT ports.                                               |  |

| VBNK_OUT                | 73         | LVTTL output | Digital TV Vertical Blank output. Vertical Blank for use                   |  |

|                         |            |              | with the V656_OUT ports.                                                   |  |

| FIELD_OUT               | 72         | LVTTL output | <b>Digital TV Field output.</b> Field bit for use with the V656_OUT ports. |  |

| AHREF                   | 69         | LVTTL output | Digital Auxiliary Horizontal Reference output. Horizontal                  |  |

| AHIKEI                  |            | EVITE output | Sync for external hardware. Programmable advance or                        |  |

|                         |            |              | retard.                                                                    |  |

| AVREF                   | 67         | LVTTL output | Digital Auxiliary Vertical Reference output. Vertical Sync                 |  |

|                         |            |              | for external hardware. Programmable advance or retard.                     |  |

| Serial Port             |            |              |                                                                            |  |

| SA10/7                  | 25         | TTL input    | Serial address length select. Selects the length of the                    |  |

|                         |            | (pull down)  | serial address:                                                            |  |

|                         |            |              | SA10/7 = H: 10-bits                                                        |  |

|                         |            |              | SA10/7 = L: 7-bits                                                         |  |

| SA <sub>0</sub>         | 26         | TTL input    | <b>Serial data address bit 0.</b> . Selects the serial bus address:        |  |

|                         |            | (pull down)  | $SA_0 = H: 0x6A, 276$                                                      |  |

|                         |            |              | $SA_0 = L: 0x4A, 224$                                                      |  |

| SDATA                   | 24         | TTL I/O      | Serial data. Data line of the serial port. Connect to GCC                  |  |

|                         |            | (open drain) | LTVDA.                                                                     |  |

| SCLK                    | 23         | TTL Input    | <b>Serial clock.</b> Clock line of the serial port. Connect to GCC LTVCL.  |  |

| Power and Gro           | ound       |              | 11102                                                                      |  |

| VDDPA                   | 22         | +3.3 V       | VGA_CKOUT Phase-locked loop Power. Filtered +3.3 volt                      |  |

| DDI A                   |            |              | power for VGA_CKOUT phase locked loop.                                     |  |

| VDDOSC                  | 3          | +3.3 V       | TV Crystal Oscillator Power. Filtered +3.3 volt power for                  |  |

| DDOOO                   |            |              | TV XTAL oscillator.                                                        |  |

| $V_{DD}$                | 33,45,56,6 | +3.3 V       | <b>Digital Power.</b> 3.3 volt power for digital section of chip.          |  |

| 55                      | 6,74,82,90 |              |                                                                            |  |

| V <sub>DDDA</sub>       | 10,13,16,1 | +3.3 V       | D/A Converter Power. Filtered +3.3 volt power for 10 bit                   |  |

|                         | 8          |              | video D/A converters.                                                      |  |

| VSSPA                   | 27         | 0 V          | VGA_CKOUT phase-locked loop ground.                                        |  |

| Vssosc                  | 4          | 0 V          | TV Crystal Oscillator ground.                                              |  |

| Vss                     | 32,38,50,6 | 0 V          | Digital ground. +3.3 volt power return.                                    |  |

|                         | 1,70,78,86 |              |                                                                            |  |

|                         | ,95        |              |                                                                            |  |

| VSSDA                   | 7,14       | 0 V          | D/A Converter Ground.                                                      |  |

# 6. Control Register Definitions

# 6.1 Control Register Map

| <del></del> |            |                          | <del>-</del> |               |

|-------------|------------|--------------------------|--------------|---------------|

| Functi      | on         |                          |              |               |

| Reg.        | Bit #      | Name                     | Type         | Reset Value   |

| Input I     | Horizonta  | I Offset                 |              |               |

| 0           | 7-0        | IHO <sub>7-0</sub>       | R/W          | 00            |

| 1           | 2-0        | IHO <sub>10-8</sub>      | R/W          | 00            |

|             | Vertical C |                          | 10,00        |               |

| 2           | 7-0        |                          | R/W          | 00            |

|             |            | IVO <sub>7-0</sub>       |              | 00            |

| 3           | 2-0        | IVO <sub>10-8</sub>      | R/W          | 00            |

|             | Horizonta  |                          | I            |               |

| 4           | 7-0        | IHW <sub>7-0</sub>       | R/W          | D0 (720.)     |

| 5           | 1-0        | IHW <sub>9-8</sub>       | R/W          | 02            |

| Vertica     | al Scaling | g Coefficient            |              |               |

| 6           | 7-0        | VSC <sub>7-0</sub>       | R/W          | 00            |

| 7           | 7-0        | VSC <sub>15-8</sub>      | R/W          | 00            |

|             | 1          | n/Up Scaling Co          |              |               |

| 8           | 7-0        | HDSC <sub>7-0</sub>      | R/W (Down)   | 00            |

| 9           | 1          |                          | ` '          |               |

|             | 7-0        | HUSC <sub>7-0</sub>      | R/W (Up)     | 00            |

|             | and Reg    |                          | I = a        | 1 22          |

| С           | 7-0        | CR <sub>7-0</sub>        | R/W          | 00            |

| D           | 7-0        | CR <sub>15-8</sub>       | R/W          | 10            |

| Status      | Port       |                          |              |               |

| Е           | 7-0        | SP <sub>7-0</sub>        | R            | 00            |

| F           | -          | -                        | R            | 00            |

| Numer       | ator of N  | CO Low Word              | l            | 1 2 2         |

| 10          | 7-0        | NCON <sub>7-0</sub>      | R/W          | 00 (131,072.) |

| 11          | 7-0        | NCON <sub>15-8</sub>     | R/W          | 00 (131,072.) |

|             |            |                          | 11/ 11/      | 00            |

|             |            | CO High Word             | DAM          |               |

| 12          | 7-0        | NCON <sub>23-16</sub>    | R/W          | 02            |

| 13          | -          | -                        |              |               |

| Denon       | ninator of | NCO Low Word             |              |               |

| 14          | 7-0        | NCOD <sub>7-0</sub>      | R/W          | 00 (524,288.) |

| 15          | 7-0        | NCOD <sub>15-8</sub>     | R/W          | 00            |

| Denon       | ninator of | NCO High Word            | d            | ·             |

| 16          | 7-0        | NCOD <sub>23-16</sub>    | R/W          | 08            |

| 17          | -          | - 23-10                  | ,            |               |

|             | ary Pixel  | Offset                   | L            | <u>_</u>      |

|             | , ,        |                          | D/M          | 00            |

| 18          | 7-0        | APO <sub>7-0</sub>       | R/W          | 00            |

| 19          | 1-0        | APO <sub>9-8</sub>       | R/W          | 00            |

|             | ary Line ( |                          | T            |               |

| 1A          | 6-0        | ALO <sub>6-0</sub>       | R/W          | 00            |

| 1B          |            |                          | R/W          | 00            |

| Auxilia     | ary Field  | Offset                   |              |               |

| 1C          | 0          | AFO                      | R/W          | 00            |

| 1D          | -          | -                        |              | 00            |

|             | Pulse W    | /idth                    | I            | 1 00          |

| 1E          |            | HSOUTWID <sub>7-0</sub>  | R/W          | 00            |

|             | 7-0        |                          |              |               |

| 1F          | 2-0        | HSOUTWID <sub>10-8</sub> | R/W          | 00            |

| Function            |             |                          |               |             |  |  |  |  |

|---------------------|-------------|--------------------------|---------------|-------------|--|--|--|--|

| Reg.                | Bit #       | Name                     | Туре          | Reset Value |  |  |  |  |

| HSync Starting Edge |             |                          |               |             |  |  |  |  |

| 20                  | 7-0         | HSOUTST <sub>7-0</sub>   | R/W           | 00          |  |  |  |  |

| 21                  | 2-0         | HSOUTST <sub>10-8</sub>  | R/W           | 00          |  |  |  |  |

| HSync               | Ending I    | Edge                     |               |             |  |  |  |  |

| 22                  | 7-0         | HSOUTEND <sub>7-0</sub>  | R/W           | 00          |  |  |  |  |

| 23                  | 2-0         | HSOUTEND <sub>10-8</sub> | R/W           | 00          |  |  |  |  |

| Flicke              | r Filter Sl | harpness                 |               |             |  |  |  |  |

| 24                  | 4-0         | SHP <sub>4-0</sub>       | R/W           | 00          |  |  |  |  |

| 25                  | -           | -                        | -             | 00          |  |  |  |  |

| Flicke              | r Filter    |                          |               |             |  |  |  |  |

| 26                  | 4-0         | FLK <sub>4-0</sub>       | R/W           | 00          |  |  |  |  |

| 27                  | -           | -                        | -             | 00          |  |  |  |  |

| Part R              | evision     |                          |               |             |  |  |  |  |

| 32                  | 7-0         | REV <sub>7-0</sub>       | R/W           | 01          |  |  |  |  |

| 33                  | 7-0         | REV <sub>15-8</sub>      | R/W           | 00          |  |  |  |  |

| Misc R              | Register    |                          |               |             |  |  |  |  |

| 34                  | 7-0         | MISC <sub>7-0</sub>      | R/W           | 00          |  |  |  |  |

| 35                  | 7-0         | MISC <sub>15-8</sub>     | R/W           | 80          |  |  |  |  |

| FIFO S              | tatus Po    | rt Full/FIFO Statu       | us Port Empty |             |  |  |  |  |

| 36                  | 7-0         | FIFOF <sub>7-0</sub>     | R/W           | 00          |  |  |  |  |

| 37                  | 7-0         | FIFOE <sub>7-0</sub>     | R/W           | 00          |  |  |  |  |

| FIFO L              | atency      |                          |               |             |  |  |  |  |

| 38                  | 7-0         | FIFOL <sub>7-0</sub>     | R/W           | 00          |  |  |  |  |

| 39                  | 7-0         | FIFOL <sub>15-8</sub>    | R/W           | 00          |  |  |  |  |

| VSync               | Pulse W     | idth                     |               |             |  |  |  |  |

| 3A                  | 7-0         | VSOUTWID <sub>7-0</sub>  | R/W           | 00          |  |  |  |  |

| 3B                  | 2-0         | VSOUTWID <sub>10-8</sub> | R/W           | 00          |  |  |  |  |

| VSync               | Starting    |                          |               |             |  |  |  |  |

| 3C                  | 7-0         | VSOUTST <sub>7-0</sub>   | R/W           | 00          |  |  |  |  |

| 3D                  | 2-0         | VSOUTST <sub>10-8</sub>  | R/W           | 00          |  |  |  |  |

| VSync               | Ending I    | Edge                     |               |             |  |  |  |  |

| 3E                  | 7-0         | VSOUTEND <sub>7-0</sub>  | R/W           | 00          |  |  |  |  |

| 3F                  | 2-0         | VSOUTEND <sub>10-8</sub> | R/W           | 00          |  |  |  |  |

| Function     | Function  |                           |         |                   |  |  |  |  |  |  |

|--------------|-----------|---------------------------|---------|-------------------|--|--|--|--|--|--|

| Reg.         | Bit #     | Name                      | Туре    | Reset Value       |  |  |  |  |  |  |

| Chrom        | a Freque  | ency                      |         |                   |  |  |  |  |  |  |

| 40           | 7-0       | CHR_FREQ <sub>31-24</sub> | R/W     | 21 (569,408,543.) |  |  |  |  |  |  |

| 41           | 7-0       | CHR_FREQ <sub>23-16</sub> | R/W     | F0                |  |  |  |  |  |  |

| 42           | 7-0       | CHR_FREQ <sub>15-8</sub>  | R/W     | 7C                |  |  |  |  |  |  |

| 43           | 7-0       | CHR_FREQ <sub>7-0</sub>   | R/W     | 1F                |  |  |  |  |  |  |

| Chrom        | a Phase,  | Miscellaneous E           | Bits 45 |                   |  |  |  |  |  |  |

| 44           | 7-0       | CHR_PHASE <sub>7-0</sub>  | R/W     | 00                |  |  |  |  |  |  |

| 45           | 1,0       | MISC45                    | R/W     | 00                |  |  |  |  |  |  |

| Miscel       | laneous l | Bits 46, 47               |         |                   |  |  |  |  |  |  |

| 46           | 7-0       | MISC46                    | R/W     | 05                |  |  |  |  |  |  |

| 47           | 3-0       | MISC47                    | R/W     | 00                |  |  |  |  |  |  |

| <b>HSync</b> | Width, E  | Burst Width               |         |                   |  |  |  |  |  |  |

| 48           | 7-0       | HSYNC_WID <sub>7-0</sub>  | R/W     | 7E (126.)         |  |  |  |  |  |  |

| 49           | 6-0       | BURST_WID <sub>6-0</sub>  | R/W     | 44 (68.)          |  |  |  |  |  |  |

| Backp        | orch Wid  | th, CB Burst Lev          | el      |                   |  |  |  |  |  |  |

| 4A           | 7-0       | BPORCH <sub>7-0</sub>     | R/W     | 76 (118.)         |  |  |  |  |  |  |

| 4B           | 7-0       | CB_BURST <sub>7-0</sub>   | R/W     | 3B (59.)          |  |  |  |  |  |  |

| CR Bu        | rst Level | , Miscellaneous E         | Bits 4D |                   |  |  |  |  |  |  |

| 4C           | 7-0       | CR_BURST <sub>7-0</sub>   | R/W     | 00                |  |  |  |  |  |  |

| 4D           | 1-0       | MISC4D                    | R/W     | 00                |  |  |  |  |  |  |

| Black        | Level     |                           |         |                   |  |  |  |  |  |  |

| 4E           | 7-0       | BLACK_LVL <sub>9-2</sub>  | R/W     | 86 (282.)         |  |  |  |  |  |  |

| 4F           | 1-0       | BLACK_LVL <sub>1-0</sub>  | R/W     | 02                |  |  |  |  |  |  |

| Blank        | Level     |                           |         |                   |  |  |  |  |  |  |

| 50           | 7-0       | BLANK_LVL <sub>9-2</sub>  | R/W     | 3C (240.)         |  |  |  |  |  |  |

| 51           | 1-0       | BLANK_LVL <sub>1-0</sub>  | R/W     | 00                |  |  |  |  |  |  |

| Numbe        | er Lines  |                           |         |                   |  |  |  |  |  |  |

| 57           | 7-0       | LINE_FRAME <sub>9-2</sub> | R/W     | 83 (525.)         |  |  |  |  |  |  |

| 58           | 1-0       | LINE_FRAME <sub>1-0</sub> | R/W     | 01                |  |  |  |  |  |  |

| White        | Level     |                           |         |                   |  |  |  |  |  |  |

| 5E           | 7-0       | WHITE_LVL <sub>9-2</sub>  | R/W     | C8 (800.)         |  |  |  |  |  |  |

| 5F           | 1-0       | WHITE_LVL <sub>1-0</sub>  | R/W     | 00                |  |  |  |  |  |  |

| Cb Ga        | in        |                           |         |                   |  |  |  |  |  |  |

| 60           | 7-0       | CB_GAIN <sub>7-0</sub>    | R/W     | 22 (137.)         |  |  |  |  |  |  |

| 61           | -         | -                         | R/W     | 01                |  |  |  |  |  |  |

| Cr Gai       | n         |                           |         |                   |  |  |  |  |  |  |

| 62           | 7-0       | CR_GAIN <sub>7-0</sub>    | R/W     | 22 (137.)         |  |  |  |  |  |  |

| 63           | -         | -                         | R/W     | 01                |  |  |  |  |  |  |

| Chrom        | a Tint Ac | djustment                 |         |                   |  |  |  |  |  |  |

| 64           | -         | -                         | R/W     | 00                |  |  |  |  |  |  |

| 65           | 7-0       | TINT <sub>7-0</sub>       | R/W     | 00                |  |  |  |  |  |  |

| Status       | Port      |                           |         |                   |  |  |  |  |  |  |

| 68           | -         | -                         | R/W     | 00                |  |  |  |  |  |  |

| 69           | 4-0       | BREEZE_WAY <sub>4-0</sub> | R/W     | 16 (22.)          |  |  |  |  |  |  |

| Status       | Port      |                           |         |                   |  |  |  |  |  |  |

| 6C           | 5-0       | FRNT_PORCH <sub>5-0</sub> | R/W     | 20 (32.)          |  |  |  |  |  |  |

| 6D           | -         | -                         | R/W     | 00                |  |  |  |  |  |  |

| Function | on        |                            |                      |             |

|----------|-----------|----------------------------|----------------------|-------------|

| Reg.     | Bit #     | Name                       | Туре                 | Reset Value |

| Active   | Line      |                            |                      |             |

| 71       | 7-0       | ACTIVELINE <sub>10-3</sub> | R/W                  | B4 (1440.)  |

| 72       | 2-0       | ACTIVELINE <sub>2-0</sub>  | R/W                  | 00          |

| Chrom    | a Phase   |                            |                      |             |

| 73       | 7-0       | FIRST_LINE <sub>7-0</sub>  | R/W                  | 15 (21.)    |

| Miscel   |           | Bits 74, Sync Le           |                      |             |

| 74       | 7-0       | MISC74                     | R/W                  | 02          |

| 75       | 7-0       | SYNC_LVL <sub>7-0</sub>    | R/W                  | 48 (72.)    |

| VBI BI   | ank Leve  |                            |                      |             |

| 7C       | 7-0       | VBIBLNK_LVL <sub>9-2</sub> | R/W                  | 4A (296.)   |

| 7D       | 1-0       | VBIBLNK_LVL <sub>1-0</sub> | R/W                  | 00          |

| Reset,   | Encoder   |                            |                      |             |

| 7E       | 0         | SOFT_RST                   | R/W                  | 1           |

| 7F       | 7-0       | ENC_VER <sub>7-0</sub>     | R                    | 20          |

| Miscel   | laneous   | Bits 80, WSS Clo           | ck Frequency (upper  | )           |

| 80       | 6-0       | MISC80                     | R/W                  | 7           |

| 81       | 7-0       | WSS_CLK <sub>11-4</sub>    | R/W                  | 2F (759.)   |

| WSS C    | lock Fre  | quency (lower),            | WSS Data Field 1 (up | per)        |

| 82       | 3-0       | WSS_CLK <sub>3-0</sub>     | R/W                  | 07          |

| 83       | 7-0       | WSS_DAT1 <sub>19-12</sub>  | R/W                  | 00          |

| WSS D    | ata Field | 1 (lower)                  |                      |             |

| 84       | 7-0       | WSS_DAT1 <sub>11-4</sub>   | R/W                  | 00          |

| 85       | 3-0       | WSS_DAT1 <sub>3-0</sub>    | R/W                  | 00          |

| WSS D    | ata Field | l 0 (upper)                |                      |             |

| 86       | 7-0       | WSS_DAT0 <sub>19-12</sub>  | R/W                  | 00          |

| 87       | 7-0       | WSS_DAT0 <sub>11-4</sub>   | R/W                  | 00          |

| WSS D    | ata Field | l 0 (lower), WSS           | Line 1 Delay         |             |

| 88       | 3-0       | WSS_DAT0 <sub>3-0</sub>    | R/W                  | 00          |

| 89       | 7-0       | WSS_LINF1 <sub>7-0</sub>   | R/W                  | 00          |

|          | evel (lov | •                          |                      |             |

| 8A       | 7-0       | WSS_LINF0 <sub>7-0</sub>   | R/W                  | 00          |

| 8B       | 7-0       | WSS_LVL <sub>9-2</sub>     | R/W                  | FF (1023.)  |

|          | evel (up  | per), Miscellaneo          |                      |             |

| 8C       | 1-0       | WSS_LVL <sub>1-0</sub>     | R/W                  | 03          |

| 8D       | 4-0       | MISC8D <sub>4-0</sub>      | R/W                  | 00          |

### **6.2 Control Register Definitions**

In the following definitions, range is defined as:

{min value : [max value]}

Please note that registers 0-3F use the little endian numbering scheme while registers 40-8D use the big endian numbering scheme.

#### 6.2.1 IHO - Input Horizontal Offset

#### Input Horizontal Offset Low (0)

| 7                | 6                | 5                | 4    | 3                | 2                | 1    | 0                |

|------------------|------------------|------------------|------|------------------|------------------|------|------------------|

| IHO <sub>7</sub> | IHO <sub>6</sub> | IHO <sub>5</sub> | IHO₄ | IHO <sub>3</sub> | IHO <sub>2</sub> | IHO₁ | IHO <sub>0</sub> |

#### **Input Horizontal Offset High (1)**

| 7 | 6 | 5 | 4 | 3 | 2                 | 1                | 0                |

|---|---|---|---|---|-------------------|------------------|------------------|

| 0 | 0 | 0 | 0 | 0 | IHO <sub>10</sub> | IHO <sub>9</sub> | IHO <sub>8</sub> |

| Reg  | Bit#     | Bit Name            | Description                                                                                                                                                     |

|------|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 0 | 2-0, 7-0 | IHO <sub>10-0</sub> | <b>Input horizontal offset bits [10-0].</b> Horizontal displacement of the image in pixels from the leading edge of horizontal sync. IHO is an unsigned number. |

Range: {0 : [Total Pixels/Line]-1}

### 6.2.2 IVO - Input Vertical Offset

#### Input Vertical Offset Low (2)

| 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| IVO <sub>7</sub> | IVO <sub>6</sub> | IVO <sub>5</sub> | IVO <sub>4</sub> | IVO <sub>3</sub> | IVO <sub>2</sub> | IVO <sub>1</sub> | IVO <sub>0</sub> |

#### Input Vertical Offset High (3)

| 7 | 6 | 5 | 4 | 3 | 2                 | 1                | 0                |

|---|---|---|---|---|-------------------|------------------|------------------|

| 0 | 0 | 0 | 0 | 0 | IVO <sub>10</sub> | IVO <sub>9</sub> | IVO <sub>8</sub> |

| Reg  | Bit#     | Bit Name            | Description                                                                                                                                                                   |

|------|----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3, 2 | 2-0, 7-0 | IVO <sub>10-0</sub> | <b>Input vertical offset bits [10:0].</b> Vertical displacement of the image in lines from the leading edge of vertical sync plus a one line bias. IVO is an unsigned number. |

Range: {0 : [Total Lines/Frame]-1}

### 6.2.3 IHW - Input Horizontal Width

### **Input Horizontal Width Low (4)**

| ſ | 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|---|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|   | IHW <sub>7</sub> | IHW <sub>6</sub> | IHW <sub>5</sub> | IHW <sub>4</sub> | IHW <sub>3</sub> | IHW <sub>2</sub> | IHW <sub>1</sub> | IHW <sub>0</sub> |

### **Input Horizontal Width High (5)**

| 7 | 6 | 5 | 4 | 3 | 2 | 1                | 0                |

|---|---|---|---|---|---|------------------|------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | IHW <sub>9</sub> | IHW <sub>8</sub> |

| Reg  | Bit#     | Bit Name           | Description                                                                                          |

|------|----------|--------------------|------------------------------------------------------------------------------------------------------|

| 5, 4 | 1-0, 7-0 | IHW <sub>9-0</sub> | Input horizontal width [9:0]. Total number of active VGA pixels per line. IHW is an unsigned number. |

**Range:** {0 : 970}

### **6.2.4 VSC – Vertical Scaling Coefficient**

### **Vertical Scaling Coefficient (6)**

| 7                | 6                | 5                | 4    | 3                | 2                | 1    | 0                |

|------------------|------------------|------------------|------|------------------|------------------|------|------------------|

| VSC <sub>7</sub> | VSC <sub>6</sub> | VSC <sub>5</sub> | VSC₄ | VSC <sub>3</sub> | VSC <sub>2</sub> | VSC₁ | VSC <sub>0</sub> |

### **Vertical Scaling Coefficient (7)**

| 7                 | 6                 | 5                 | 4                 | 3                 | 2                 | 1                | 0                |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| VSC <sub>15</sub> | VSC <sub>14</sub> | VSC <sub>13</sub> | VSC <sub>12</sub> | VSC <sub>11</sub> | VSC <sub>10</sub> | VSC <sub>9</sub> | VSC <sub>8</sub> |

| Reg  | Bit# | Bit Name           | Description                                                                                                                                                                      |

|------|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6 | 7-0  | VSC <sub>7-0</sub> | <b>Vertical scaling coefficient bits [15:0].</b> Vertical down scaling factor = (1 + VSC/65,536). VSC is a two's complement number. If VSC => 0, then the image is not effected. |

**Range:** { [-32,769]:0}

### 6.2.5 HDSC, HUSC - Horizontal Down/Up Scaling Coefficients

### **Horizontal Down Coefficient (8)**

| 7                 | 6                 | 5     | 4                 | 3                 | 2                 | 1     | 0     |

|-------------------|-------------------|-------|-------------------|-------------------|-------------------|-------|-------|

| HDSC <sub>7</sub> | HDSC <sub>6</sub> | HDSC₅ | HDSC <sub>4</sub> | HDSC <sub>3</sub> | HDSC <sub>2</sub> | HDSC₁ | HDSC₀ |

### **Horizontal Up Coefficient (9)**

| 7                 | 6                 | 5     | 4     | 3     | 2                 | 1     | 0     |

|-------------------|-------------------|-------|-------|-------|-------------------|-------|-------|

| HUSC <sub>7</sub> | HUSC <sub>6</sub> | HUSC₅ | HUSC₄ | HUSC₃ | HUSC <sub>2</sub> | HUSC₁ | HUSC₀ |

| Reg | Bit# | Bit Name            | Description                                                                                                                                                                      |

|-----|------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | 7-0  | HDSC <sub>7-0</sub> | Horizontal down scaling coefficient bits [7:0]. Horizontal down scaling factor = (1 + VSC/128). HDSC is a two's complement number. If HDSC => 0, then the image is not effected. |

| 9   | 7-0  | HUSC <sub>7-0</sub> | Horizontal up scaling coefficient bits [7:0]. Horizontal up scaling factor = (1 + VSC/128). HDSC is a two's complement number. If HDSC <= 0, then the image is not effected.     |

**HDSC Range:** { [-63]:0 } **HUSC Range:** { 0:127 }

### 6.2.6 CR - Command Register

### **Command Register (C)**

| 7       | 6        | 5     | 4     | 3       | 2      | 1      | 0      |

|---------|----------|-------|-------|---------|--------|--------|--------|

| FFO_CLR | CACQ_CLR | LP_EN | YCOFF | COMPOFF | NCO_EN | CLKOFF | SRESET |

### **Command Register (D)**

| 7                    | 6                    | 5 | 4       | 3       | 2    | 1       | 0          |

|----------------------|----------------------|---|---------|---------|------|---------|------------|

| UIM_MOD <sub>1</sub> | UIM_MOD <sub>0</sub> | 0 | UIM_DEC | UIM_CLK | OFMT | STD_VMI | NTSC_PALIN |

| Reg | Bit# | Bit Name               | Description                                                                                                                                                                                                                                                                            |

|-----|------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С   | 0    | SRESET                 | Soft Reset. Resets the FS450.                                                                                                                                                                                                                                                          |

| С   | 1    | CLKOFF                 | Clock Off. Turns off FS450 clock to minimize power.                                                                                                                                                                                                                                    |

| С   | 2    | NCO_EN                 | <b>Enable NCO Latch.</b> When this bit is set, transfers the NCO words from the I2C registers into the NCO. The NCO synthesizes the VGA clock from the 27MHz FS450 clock. This clock must be adjusted so the VGA scaled input data rate exactly matches the CCIR 656 data output rate. |

| С   | 3    | COMPOFF                | Composite (CVBS) Output Off. Turns off the CVBS output D/A.                                                                                                                                                                                                                            |

| С   | 4    | YCOFF                  | SVideo (YC) Outputs Off. Turns off the YC output D/As.                                                                                                                                                                                                                                 |

| С   | 5    | LP_EN                  | <b>Loop Through Enable.</b> Enables the CCIR 656 data on the output port to loop directly to the input port (no external routing).                                                                                                                                                     |

| С   | 6    | CACQ_CLR               | Counter Acquisition Flag Clear. Setting this bit clears the Counter Acquisition Flag.                                                                                                                                                                                                  |