### superior video technology

# FS401, FS403 PC to TV Video Scan Converters

#### **Features**

- Frame rate Conversion †

- Programmable 2D scaling †

- Pan and Zoom †

- Advanced 2-D flicker filter †

- Frame-store memory controller

- Supports Multiple Progressive Input Resolutions †

- -Minimum 640x 400

- -Maximum 2048 x 1536

- Supports Interlaced Input

- -XGA and above

- Input refresh rates up to 150Hz

- Multiple Output Standards

- -NTSC, NTSC-EIAJ, PAL-B/G/H/I †

- -Composite, S-Video, SCART

- -RGB, YUV

- Standard NTSC and PAL

- ■Super NTSC & PAL

- ■VGA Progressive

- ■SVGA Progressive

- ■NTSC Progressive

- ■PAL 100Hz Interlaced

- Automatically detects input active video area

- Automatically selects the best output and scaling for any input resolution

- Programmable sharpness, brightness, contrast and color saturation

- Customizable On Screen Display via glueless integration with Zilog and Philips OSD Microprocessors (FS403)

- C, H, and V Sync tri-state outputs

- H and V Sync monitoring for DPMS Support

- Exceeds all PC97 and PC98 requirements

- General Purpose Output Pins (2 on FS401, 7 on FS403)

- Genlock (FS403)

- 8-bit A/D converters with frequency adaptive input filtering support

- 10-bit output D/A converters

- Digital RGB Inputs (FS403)

- I<sup>2</sup>C<sup>‡</sup> compatible port controls (SIO)

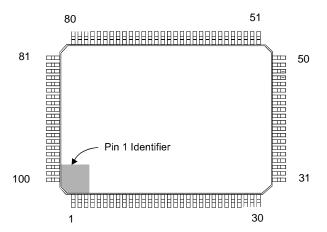

- 100 pin PQFP (FS401)

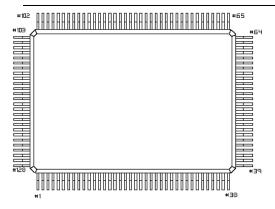

- 128 pin PQFP (FS403)

- 3.3V operation

- RoHS Compliant

†Note: Covered under US Patent # 5,862,268, # 5,905,536, # 5,966,184 and/or patents pending.

### Description

The FS400 family is a fourth generation video scan converter. It accepts many input resolutions and rates and converts them to NTSC or PAL standards compliant with SMPTE-170M and CCIR-656 standards. Also available as output options are VGA 640 x 480 at 60Hz progressive, SVGA 800 x 600 at 60Hz progressive, and 100 Hz interlaced. The chip has a programmable down scaler to fit the incoming resolution to the output display format. Within the FS400 are capture and encoder engines separated by the frame buffer memory controller. Required external components are minimal: a single 16M SDRAM memory, clocks and passive parts.

Analog progressive RGB inputs are digitized and converted to the YUV 4:2:2 format. Vertical scaling and flicker filtering are implemented at the computer frame rate ahead of the frame store interface.

Interlaced input is supported for XGA resolution and above. In this mode, only the first field is processed.

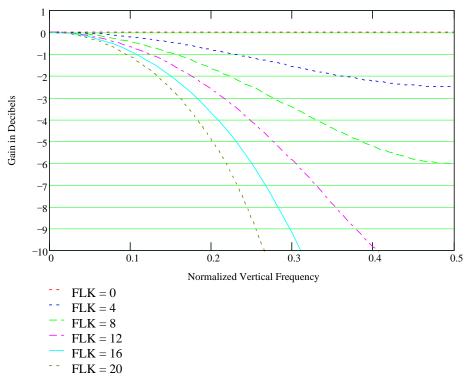

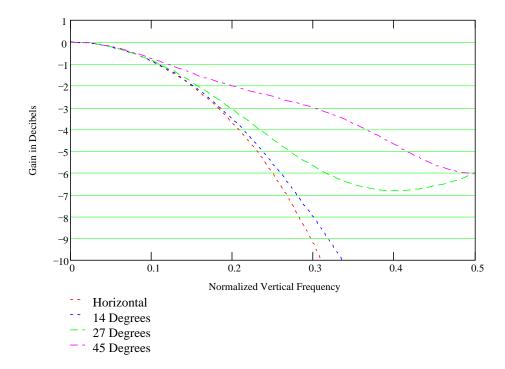

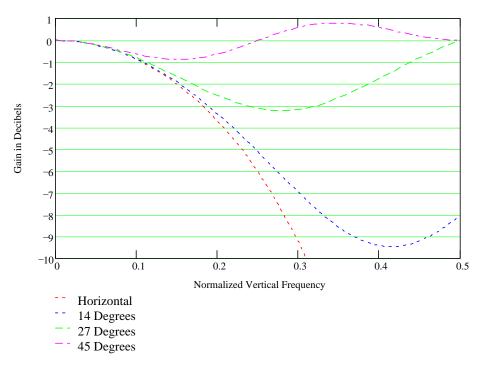

The Flicker Filter is an advanced 2 dimensional filter that enhances text quality. Flicker Filter parameters are programmable to allow user tradeoffs between flicker and sharpness.

The FS400 family contains controls for programmable sharpness, brightness, contrast, and color saturation. These controls allow output to be tuned to match user desires and tastes.

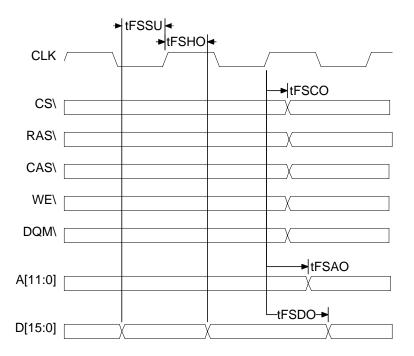

Frame rate conversion is implemented by a Frame Store Controller that interfaces with an external SDRAM frame store memory.

YUV 4:2:2 data is recovered from the memory at the outgoing frame rate. Data is scaled prior to the

Downloaded from Elcodis.com electronic components distributor

digital video encoder that generates Y/C and Composite Video outputs. For RGB and YUV outputs, the encoder may be bypassed via a YUV to RGB transcoder for SCART compatible video, and for output to VGA or SVGA displays.

The FS400 has built in capability to automatically detect the incoming video mode and automatically select optimal sampling and scaling parameters. The chip can detect the location of the active video in the input, and can automatically center the input on the TV screen. All parameters can be read and written via the SIO serial port.

The FS403 has support for glueless integration with Zilog and Philips On Screen Display (OSD) microcontrollers. The OSD interface allows a customized on

screen user interface that can contain opaque or halftone video backgrounds.

The FS403 has direct digital inputs, bypassing the built-in ADCs.

Power is derived from +3.3V digital and analog supplies. Packages are 100-lead (FS401) or 128-lead (FS403) Plastic Quad Flat Pack (PQFP).

### **Applications**

- PC video out

- PC ready TV's

- Video Text Displays

- Web Appliances

- PC-to-TV Scan Converter Peripherals

- Video Kiosks

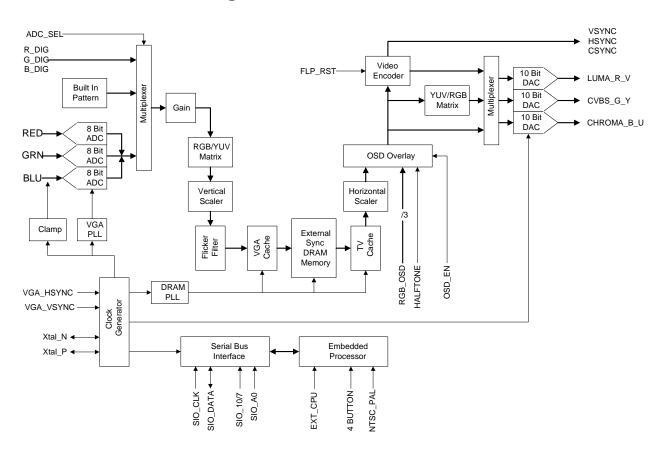

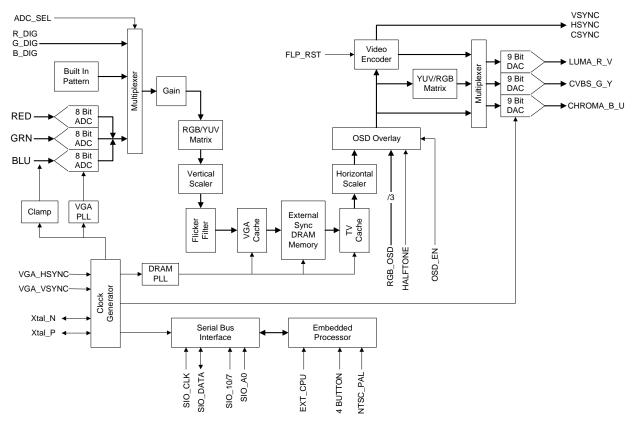

# **Architectural Block Diagram**

## **Contents**

| 1. | Architectural Overview5                     | 4.5.20 Contrast Coefficient47                  |

|----|---------------------------------------------|------------------------------------------------|

|    | 1.1 Video Capture Engine 5                  | 4.5.21 Brightness Coefficient48                |

|    | 1.2 Frame Store Memory Controller 6         | 4.5.22 Sharpness Coefficient49                 |

|    | 1.3 Video Encoder Engine 6                  | 4.5.23 Flicker Filter Coefficient50            |

|    | 1.4 Serial Control Port 6                   | 4.5.24 Color Saturation Coefficient51          |

|    | 1.5 Typical System Configurations 7         | 4.5.25 General Purpose Outputs52               |

|    | 1.5.1 External Scan Converter               | 4.5.26 SCR – Software Control                  |

|    | 1.5.2 Embedded Television Interface 8       | Register 53                                    |

|    | 1.5.3 Deleted 8                             | 4.5.27 SSR – Software Status Register55        |

|    | 1.5.4 Professional and Pro-Consumer         | 4.5.28 HCRS – Hardware Control                 |

|    | Video Designs9                              | Register Shadow56                              |

| 2. |                                             | 4.5.29 HCRES – Hardware Control                |

|    | 2.1 100-Lead PQFP Package (FS401) 10        | Register Extended Shadow57                     |

|    | 2.2 128-Lead PQFP Package (FS403) 11        | 4.5.30 HPO – Horizontal Position               |

| 3. |                                             | Offset 58                                      |

| 4. | •                                           | 4.5.31 VPO – Vertical Position Offset59        |

| ᢇ. | 4.1 Control Register Functions              | 4.5.32 HSS – Horizontal Scale Step60           |

|    | 4.2 Internal Micro-Controller               | 4.5.33 VSS – Vertical Scale Step61             |

|    | Programming                                 | 4.5.34 HPP – Horizontal Pan Position62         |

|    | 4.2.1 Input Calibration                     | 4.5.35 VPP – Vertical Pan Position63           |

|    | 4.2.1.1 Auto Input Calibration              | 4.5.36 TVP – TV Pixels64                       |

|    |                                             | 4.5.37 TVL – TV Lines                          |

|    | • • • • • • • • • • • • • • • • • • •       |                                                |

|    | · · · · · · · · · · · · · · · · · · ·       | <u> </u>                                       |

|    | 4.2.2 Output Calibration                    | Register 66<br>4.5.39 CDR – Configuration Data |

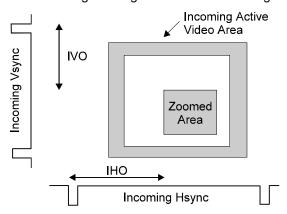

|    | 4.2.3 Zoom                                  | 9                                              |

|    | •                                           | Register 67                                    |

|    | 4.2.5 Picture Control                       | 4.5.40 HOHOS – Hardware Output                 |

|    | 4.2.6 Video Mode Changes                    | Horizontal Offset Shadow68                     |

|    | 4.2.7 By-passing the Internal Micro-        | 4.5.41 HOVOS – Hardware Output                 |

|    | Controller                                  | Vertical Offset Shadow69                       |

|    | 4.2.8 Special Internal Micro-Controller     | 4.6 Configuration Values70                     |

|    | SIO Requirements                            | Addr70                                         |

|    | 4.3 Disabling the Internal Micro-           | 5. Functional Description                      |

|    | Controller                                  | 5.1 Capture Engine                             |

|    | 4.4 Control Register Definitions            | 5.1.1 Timing and Control                       |

|    | 4.5 Control Registers Definitions           | 5.1.2 Clamps                                   |

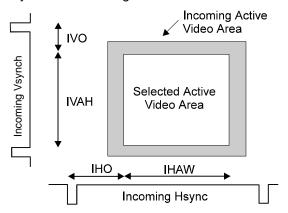

|    | 4.5.1 IHO - Input Horizontal Offset         | 5.1.3 Analog-to-Digital Converters76           |

|    | 4.5.2 IVO - Input Vertical Offset           | 5.1.4 24-bit Digital RGB Port (FS403           |

|    | 4.5.3 IHAW - Horizontal Active Width 30     | only) 77                                       |

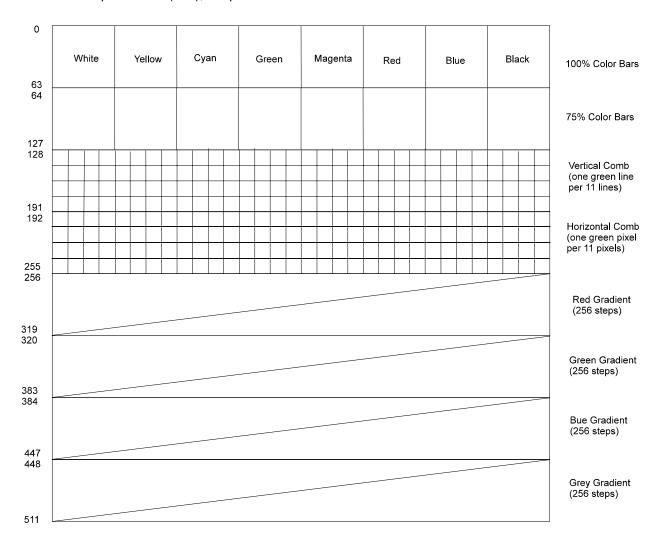

|    | 4.5.4 ILS - Input Lines Stored              | 5.1.5 Built In Pattern Generator               |

|    | 4.5.5 IHS - Input Horizontal Samples 32     | 5.1.6 Digital RGB Multiplexer78                |

|    | 4.5.6 IHC - Input Horizontal Count          | 5.1.7 RGB Gain                                 |

|    | 4.5.7 IVC - Input Vertical Count            | 5.1.8 RGB/YUV Matrix                           |

|    | 4.5.8 VSC – Vertical Scaling Coefficient 35 | 5.1.9 Vertical Scaler                          |

|    | 4.5.9 CR - Command Register                 | 5.1.10 Flicker Filter                          |

|    | 4.5.10 SR – Status Register                 | 5.2 Frame Store Controller80                   |

|    | 4.5.11 CRE – Command Register               | 5.2.1 SDRAM Interface81                        |

|    | Extended 38                                 | 5.2.2 Phase Locked Loop81                      |

|    | 4.5.12 Start Horizontal Active VGA 39       | 5.2.3 Input Offset and Size Control81          |

|    | 4.5.13 End Horizontal Active VGA 40         | 5.2.4 Output Offset and Size Control82         |

|    | 4.5.14 Start Vertical Active VGA            | 5.2.5 Freeze Frame82                           |

|    | 4.5.15 End Vertical Active VGA              | 5.2.6 Zoom                                     |

|    | 4.5.16 Active Video Threshold               | 5.3 Encoder Engine                             |

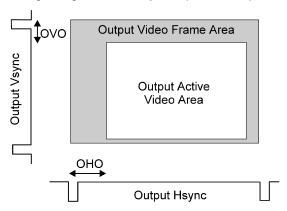

|    | 4.5.17 OHO - Output Horizontal Offset 44    | 5.3.1 Timing and Control83                     |

|    | 4.5.18 OVO – Output Vertical Offset 45      | 5.3.2 Horizontal Scaler84                      |

|    | 4.5.19 HSC – Horizontal Scaling             | 5.3.3 Digital Video Encoder84                  |

|    | Coefficient46                               | 5.3.4 YUV/RGB Matrix84                         |

Downloaded from **Elcodis.com** electronic components distributor

| 5.3.5 Digital-to-Analog Converters 85 5.3.6 On-Screen Display (FS403 only) 85 | Figures                                                               |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 5.4 Serial Control Port (R-Bus)                                               | Figure 1: External Scan Converter Block Diagram7                      |

| 5.4.2 Serial Interface Read/Write                                             | Figure 2: Embedded Television Design Block                            |

| Examples                                                                      | Diagram8                                                              |

| 5.4.2.1 Write to one control register 88<br>5.4.2.2 Write to two consecutive  | Figure 3: Deleted8                                                    |

| 5.4.2.2 Write to two consecutive control registers89                          | Figure 4: Professional & Pro-Consumer Video                           |

| 5.4.2.3 Read from one control                                                 | Design Block Diagram9                                                 |

| register 89                                                                   | Figure 5. Functional Block Diagram                                    |

| 5.4.2.4 Read from two consecutive                                             | Figure 6. FAZE Sets ADCK Sampling Edge on Incoming Pixels             |

| data registers89                                                              | Figure 7: BiPGEN Image77                                              |

| 5.5 Embedded Microprocessor 89                                                | Figure 8: Two Dimensional Flicker Filter                              |

| 6. Specifications90                                                           | Response (FLK=0,4,8,12,16,20; SHP=0)79                                |

| 6.1 Absolute Maximum Ratings90                                                | Figure 9: FLK = 16, SHP = 8; Response at                              |

| 6.2 Operating Conditions                                                      | Horizontal, 14, 27, 45 Degrees79                                      |

| 6.3 Electrical Characteristics                                                | Figure 10: FLK = 16, SHP = 16; Response at                            |

| 6.5 System Performance Characteristics 94                                     | Horizontal, 14, 27, 45 Degrees80                                      |

| 7. Application Notes                                                          | Figure 11. Timing Parameter Definition, SDRAM                         |

| 7.1 Circuit Example - PC                                                      | Interface81 Figure 12. Input Offset and Size Definitions82            |

| 7.2 FS400 Design and Layout                                                   | Figure 13. Output Horizontal and Vertical Offset                      |

| Considerations96                                                              | Definitions82                                                         |

| 7.2.1 Video Input to A-D Converters 96                                        | Figure 14. Zoomed image showing offsets83                             |

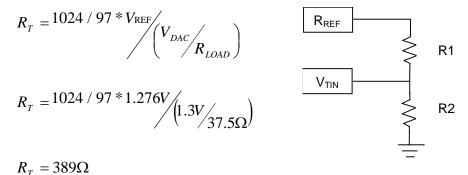

| 7.2.2 Input ADC Phase Lock Loop 96                                            | Figure 15. R <sub>REF</sub> and V <sub>TIN</sub> Setup85              |

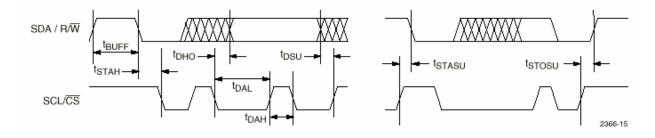

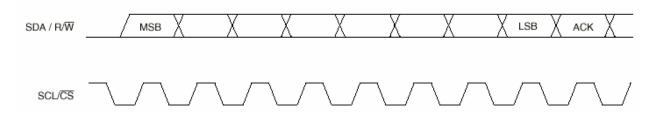

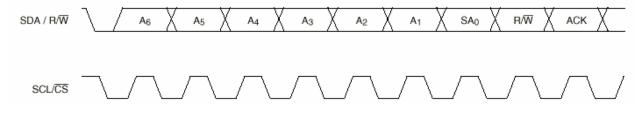

| 7.2.3 Memory Clock Phase Lock Loop 96                                         | Figure 16. Serial Port Read/Write Timing86                            |

| 7.2.4 External SDRAM Interface                                                | Figure 17. Serial Interface – Typical Byte                            |

| 7.2.5 HSYNC and VSYNC                                                         | Transfer86                                                            |

| 7.2.6 Video Output Filters97 7.2.7 Analog Power Supply Bypassing,             | Figure 18. 7-bit Slave Address with Read/Write\                       |

| Filtering, and Isolation                                                      | Bit                                                                   |

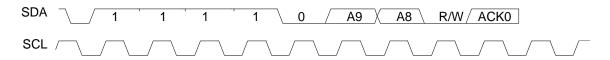

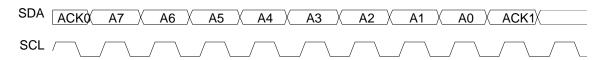

| 7.2.8 Power and Ground                                                        | Figure 19. 10-bit address transfer, upper two bits87                  |

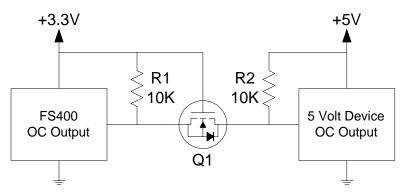

| 7.3 Interfacing to the FS400 in a Mixed                                       | Figure 20. 10-bit address transfer, lower eight                       |

| Voltage Environment98                                                         | bits87                                                                |

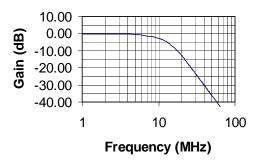

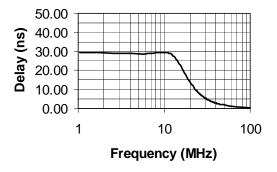

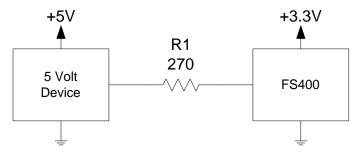

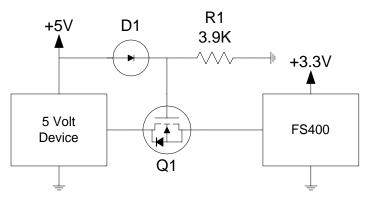

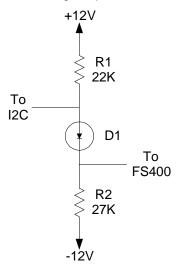

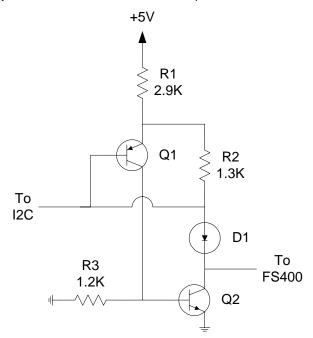

| 7.3.1 5 to 3.3 Volt Translation 98                                            | Figure 21. Video Filter Response95                                    |

| 7.3.2 SIO Bus Interfacing                                                     | Figure 22. Video Filter Delay95                                       |

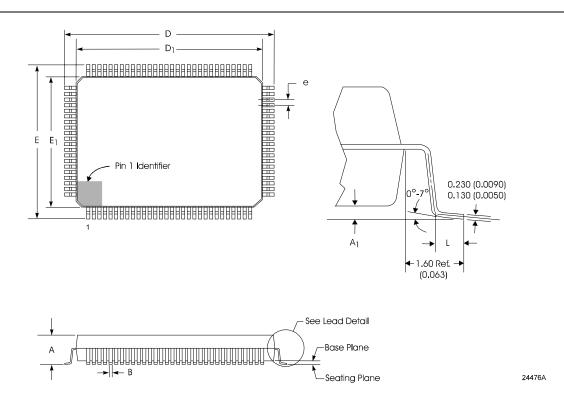

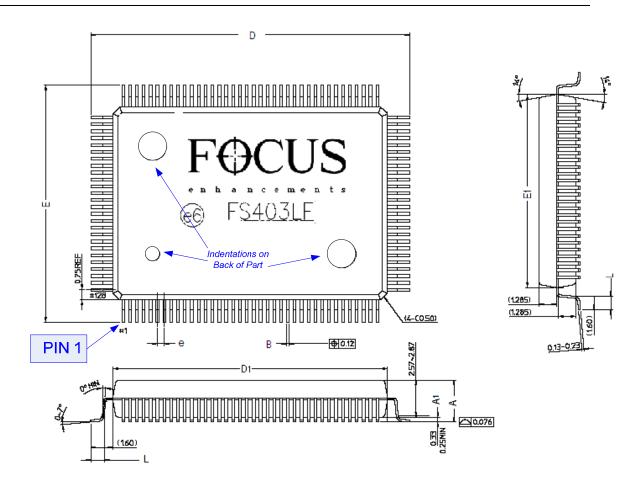

| 8. Mechanical Dimensions                                                      | Figure 23. 5 to 3.3 Volt Translation using a                          |

| 8.1 100-Lead PQFP (KH) Package -                                              | Resistor98                                                            |

| FS401LF 101<br>8.2 128-Lead PQFP Package, FS403 LF. 102                       | Figure 24. 5 to 3.3 Volt Translation using a                          |

| 9. Revision History103                                                        | MOSFET Q1 = BSS138, D1 = 1N414898                                     |

| 10. Ordering Information                                                      | Figure 25. SIO Translation Using Long-tail<br>Resistors D1 = 1N414899 |

| 10.1 Package Markings: 104                                                    | Figure 26. SIO Translation Using Current                              |

| J J                                                                           | Mirrors D1 = 1N4148, Q1 = 2N3906, Q2 =                                |

|                                                                               | 2N390499                                                              |

| Tables                                                                        | Figure 27. SIO (Open Collector) Translation                           |

| Tables                                                                        | using a MOSFET Q1 = BSS138100                                         |

| Table 1. Pin Designations (FS401, 100-pin                                     | -                                                                     |

|                                                                               |                                                                       |

| Table 2. Pin Designations (FS403, 128-pin                                     |                                                                       |

| package)                                                                      |                                                                       |

| Table 3. Control Register Map                                                 |                                                                       |

| Table 5. Serial Port Addresses                                                |                                                                       |

| . 22.5 5. 55.14.1 5.1.7 (44.05000                                             |                                                                       |

Downloaded from  $\underline{Elcodis.com}$  electronic components distributor

### 1. Architectural Overview

Overall design principles are included in this section. Details of how to use and setup the FS400 are included in the *Functional Description* section, starting on *page 75*.

RGB video inputs are asynchronously converted to either NTSC/PAL, YUV or RGB video formats. Architecturally, the FS400 is divided into five major sections:

- 1. Video Capture Engine

- 2. Clock Processor

- 3. Frame Store Controller

- 4. Video Encoder Engine

- 5. Serial Bus Interface

Besides power and a few external passive components, the FS400 requires only a single 16M external SDRAM and external clocks to implement a high quality video scan converter.

Either analog or digital inputs (FS403 only) with separate horizontal and vertical sync signals are accepted. Analog VGA video must be RGB. Digital video (FS403 only) must be 24-bit RGB clocked by external clock, VGACK\_IN.

A wide range of resolution formats can be accepted, including common standards such as 320x240, 640x400, 720x400, 640x480, 800x600, 832x624, 1024x768, 1152x864, 1280x1024, and 1600x1200. Incoming RGB signals are converted to either the NTSC or PAL TV Standards, 100Hz PAL, or progressive scan VGA, SVGA, or NTSC. Output video format can be selected to be either composite and Y/C (NTSC and PAL only), or RGB or YUV (all standards).

Incoming frame rate may range to over 150 Hz according to the table below. The Video Capture engine runs asynchronously relative to the Video Encoder Engine. An external frame store memory separates the two engines with write and read access controlled by the FS400.

Transformation operations include overscan, underscan, pan and zoom. Scaling operations are separated by the frame store with vertical down-sampling incorporated into the Capture Engine and horizontal up-sampling incorporated into the Encoder Engine.

# 1.1 Video Capture Engine

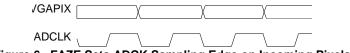

Triple 8-bit A/D converters digitize the analog RGB inputs at rates of up to 50 MHz. Internal A/D sample clock, ADCK is derived from a phase locked loop referenced to the leading edge of horizontal sync. Either positive or negative sync polarity is accepted.

The selected input (A/D converter outputs or digital RGB) is transcoded by the color matrix into a 16-bit YC<sub>R</sub>C<sub>B</sub> 4:2:2 format. A vertical scaler filters the number of incoming video lines by the selected scaling factor. A flicker filter averages lines to eliminate flicker between lines or boundaries.

The Video Capture Engine is programmable as to the number of horizontal samples it takes. The limiting factor in the sample rate is the A/D Converters. By programming fewer samples per line, higher incoming data rates can be accommodated. The following table illustrates the capability:

| Active Samples         | 720 CCIR 601 | 640   | 500   |

|------------------------|--------------|-------|-------|

| Maximum Line Frequency | 56kHz        | 63kHz | 80kHz |

| 640 x 480              | 106Hz        | 119Hz | 152Hz |

| 800 x 600              | 89Hz         | 100Hz | 128Hz |

| 1024 x 768             | 70Hz         | 78Hz  | 100Hz |

| 1152 x 864             | 59Hz         | 66Hz  | 85Hz  |

| 1280 x 1024            | 53Hz         | 59Hz  | 76Hz  |

| 1600 x 1200            | 44Hz         | 50Hz  | 64Hz  |

## 1.2 Frame Store Memory Controller

Inserted between the capture and the encoder engines the frame store has two functions: 1) to act as a reservoir of pixels to match the incoming frame rate to the outgoing field or frame rate; 2) to support vertical scaling by allowing lines to be written into the frame store intermittently, but read out at a constant rate.

Frame store clock, FS\_CK is derived from the OSC1 clock by a second phase locked loop.

## 1.3 Video Encoder Engine

Pixels are retrieved from the external frame store memory asynchronously relative to the incoming frames. Outgoing video timing is set to the selected TV (NTSC or PAL) or progressive scan standard.

Incoming data sampling is normally set to fill complete lines in the Frame Store Memory. Horizontal scaling is applied to pixels exiting the Frame Store. Pixels may be routed through either a digital video encoder or a YC<sub>R</sub>C<sub>B</sub>-to-RGB transformation matrix. Either output is connected to a triple 10-bit D/A converter to generate the video output that may be Composite Video and Y/C, RGB or YUV.

Encoder Engine timing is derived from many clock sources. These standards are shown below.

| Encoder Standard | Total Pixels | Total Lines | Vertical<br>Mode | Clock Rate | Line Freq. |

|------------------|--------------|-------------|------------------|------------|------------|

|                  |              |             |                  |            |            |

| NTSC             | 910          | 525         | 60I              | 14.318 MHz | 15.73 KHz  |

| PAL              | 1135.0064    | 625         | 50I              | 17.734 MHz | 15.62 KHz  |

| RGB NTSC         | 910          | 525         | 60I              | 14.318 MHz | 15.73 KHz  |

| RGB PAL          | 1135         | 625         | 50I              | 17.734 MHz | 15.62 KHz  |

| Super RGB NTSC   | 1280         | 525         | 60I              | 20.140 MHz | 15.73 KHz  |

| Super RGB PAL    | 1280         | 625         | 501              | 20.000 MHz | 15.62 KHz  |

| VGA              | 800          | 525         | 60P              | 25.175 MHz | 31.5 KHz   |

| SVGA             | 1024         | 625         | 60P              | 38.400 MHz | 37.5 KHz   |

| Progressive NTSC | 910          | 525         | 60P              | 28.636 MHz | 31.5 KHz   |

| 100Hz PAL        | 1135         | 625         | 100I             | 35.468 MHz | 31.25 KHz  |

### 1.4 Serial Control Port

FS400 setup is programmed by 39 16-bit registers that are accessible via the I<sup>2</sup>C<sup>‡</sup> compatible serial port (SIO). Status and Revision ID can also be read from the registers.

<sup>‡</sup>Note: I<sup>2</sup>C is a registered trademark of Philips Corporation. The FS400 SIO bus is similar but not identical to Philips I<sup>2</sup>C bus.

## 1.5 Typical System Configurations

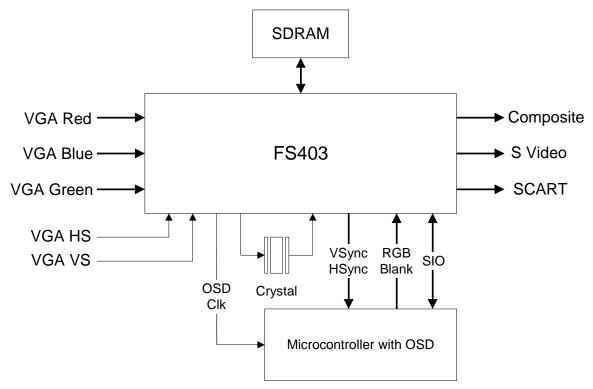

### 1.5.1 External Scan Converter

The FS403 has been optimized for scan converter designs. It provides a maximum amount of flexibility while minimizing system cost. When combined with a Zilog Z902xx Family or Philips P8xC055/145/845 Families, the FS403 provides overlaid On-Screen Display pixels specified by the programmer without any additional external components thus minimizing expense, complexity, and size while maximizing flexibility and features.

Figure 1: External Scan Converter Block Diagram

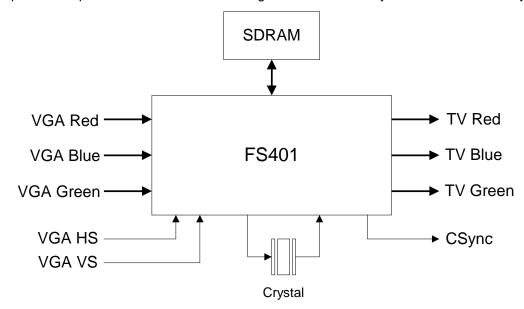

### 1.5.2 Embedded Television Interface

The FS401 has been optimized for television designs. With its built in microprocessor, the FS401 can run freely with minimal control from the television processor while providing complete plug-n-play capability. Simple commands can be sent to the FS401 via the SIO bus to implement remote control functions such as zoom, pan, sizing, positioning, and video quality control (such as brightness, contrast, saturation, flicker, and sharpness). The only components required are the FS401 and a single SDRAM for a truly minimal incremental system cost.

Figure 2: Embedded Television Design Block Diagram

### 1.5.3 Deleted

Figure intentionally left blank.

Figure 3: Deleted

Downloaded from Elcodis.com electronic components distributor

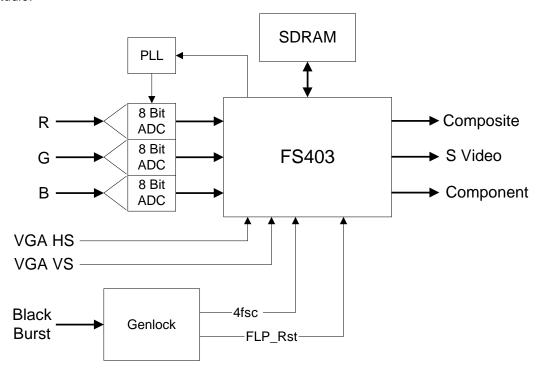

### 1.5.4 Professional and Pro-Consumer Video Designs

In the Professional and Pro-Consumer Video Market, Video quality, video timing accuracy, and Genlock are very important features. Also the system will use external ADCs and PLLs of the highest quality. Genlock to an external studio Black Burst (black screen TV picture) will be used to synchronize the scan converter to the rest of the video studio.

Figure 4: Professional & Pro-Consumer Video Design Block Diagram

# 2. Pin Assignments

# 2.1 100-Lead PQFP Package (FS401)

Table 1. Pin Designations (FS401, 100-pin package)

| Pin | Name                        | Pin | Name                | Pin | Name            | Pin  | Name              |

|-----|-----------------------------|-----|---------------------|-----|-----------------|------|-------------------|

| 1.  | $V_{DDPF}$                  | 31. | TV_VSYNC            | 51. | V <sub>SS</sub> | 81.  | GPO6              |

| 2.  | OSC1                        | 32. | TV_HSYNC            | 52. | EXTVGASEL\      | 82.  | $V_{DD}$          |

| 3.  | OSC1BUF                     | 33. | $V_{DDAD}$          | 53. | VGACLKIN        | 83.  | A0                |

| 4.  | OSC2                        | 34. | $V_{SSAD}$          | 54. | $V_{DD}$        | 84.  | A1                |

| 5.  | OSC2BUF                     | 35. | $V_{SSAD}$          | 55. | V <sub>SS</sub> | 85.  | A2                |

| 6.  | V <sub>SS</sub>             | 36. | R_IN                | 56. | V <sub>SS</sub> | 86.  | A3                |

| 7.  | $V_{SSDA}$                  | 37. | $V_{DDAD}$          | 57. | DQM             | 87.  | A4                |

| 8.  | $C_{COMP}$                  | 38. | $V_{DDAD}$          | 58. | WE\             | 88.  | A5                |

| 9.  | I <sub>REF</sub>            | 39. | G_IN                | 59. | INTCPUEN        | 89.  | A6                |

| 10. | $V_{DDDA}$                  | 40. | V <sub>SSAD</sub>   | 60. | RAS\            | 90.  | A7                |

| 11. | C <sub>BYPASS</sub>         | 41. | V <sub>TOUT</sub>   | 61. | CAS\            | 91.  | A8                |

| 12. | Y/R/V                       | 42. | V <sub>ADCREF</sub> | 62. | D0              | 92.  | A9                |

| 13. | $V_{DDDA}$                  | 43. | V <sub>SSAD</sub>   | 63. | D1              | 93.  | A10               |

| 14. | $V_{SSDA}$                  | 44. | B_IN                | 64. | D2              | 94.  | A11               |

| 15. | CVBS/G/Y                    | 45. | $V_{DDAD}$          | 65. | D3              | 95.  | $V_{DD}$          |

| 16. | $V_{DDDA}$                  | 46. | CLAMP_REF           | 66. | D4              | 96.  | GPO0              |

| 17. | C/B/U                       | 47. | $V_{DDPA}$          | 67. | D5              | 97.  | V <sub>SSPF</sub> |

| 18. | $V_{DDDA}$                  | 48. | $V_{SSPA}$          | 68. | D6              | 98.  | RAMCK_SEL\        |

| 19. | $V_{DD}$                    | 49. | VS_IN               | 69. | D7              | 99.  | RAMCK_OUT         |

| 20. | CSYNC                       | 50. | HS_IN               | 70. | D8              | 100. | RAMCK_IN          |

| 21. | V <sub>SS</sub>             |     |                     | 71. | D9              |      |                   |

| 22. | V <sub>SS</sub>             |     |                     | 72. | D10             |      |                   |

| 23. | SIOCLK                      |     |                     | 73. | D11             |      |                   |

| 24. | SIODATA                     |     |                     | 74. | $V_{DD}$        |      |                   |

| 25. | SIOA <sub>10/7</sub>        |     |                     | 75. | V <sub>SS</sub> |      |                   |

| 26. | SIOA <sub>0</sub>           |     |                     | 76. | D12             |      |                   |

| 27. | V <sub>DD</sub>             |     |                     | 77. | D13             |      |                   |

| 28. | Reserved (V <sub>SS</sub> ) |     |                     | 78. | D14             |      |                   |

| 29. | Reserved (V <sub>SS</sub> ) |     |                     | 79. | D15             |      |                   |

| 30. | RESET                       |     |                     | 80. | V <sub>SS</sub> |      |                   |

# 2.2 128-Lead PQFP Package (FS403)

Table 2. Pin Designations (FS403, 128-pin package)

| Pin | Name                 | Pin | Name                        | Pin | Name            | Pin  | Name              |

|-----|----------------------|-----|-----------------------------|-----|-----------------|------|-------------------|

| 1.  | OSC1                 | 33. | V <sub>DD</sub>             | 65. | VGACLKDIV       | 97.  | D12               |

| 2.  | OSC1BUF              | 34. | Reserved (V <sub>SS</sub> ) | 66. | EXTVGASEL\      | 98.  | D13               |

| 3.  | OSC2                 | 35. | FLP_RST                     | 67. | VGACLKIN        | 99.  | D14               |

| 4.  | OSC2BUF              | 36. | Reserved (V <sub>SS</sub> ) | 68. | $V_{DD}$        | 100. | D15               |

| 5.  | V <sub>SS</sub>      | 37. | RESET                       | 69. | V <sub>SS</sub> | 101. | V <sub>SS</sub>   |

| 6.  | V <sub>SSDA</sub>    | 38. | R0/TV_VSYNC                 | 70. | G3              | 102. | B7/GPO7           |

| 7.  | C <sub>COMP</sub>    | 39. | R1/TV_HSYNC                 | 71. | G2              | 103. | B6/GPO6           |

| 8.  | I <sub>REF</sub>     | 40. | R2/OSDEN                    | 72. | G1              | 104. | B5/GPO5           |

| 9.  | $V_{DDDA}$           | 41. | R3                          | 73. | G0              | 105. | B4/GPO4           |

| 10. | C <sub>BYPASS</sub>  | 42. | $V_{DDAD}$                  | 74. | V <sub>SS</sub> | 106. | $V_{DD}$          |

| 11. | Y/R/V                | 43. | V <sub>SSAD</sub>           | 75. | DQM             | 107. | A0                |

| 12. | $V_{DDDA}$           | 44. | V <sub>SSAD</sub>           | 76. | WE\             | 108. | A1                |

| 13. | $V_{SSDA}$           | 45. | R_IN                        | 77. | INTCPUEN        | 109. | A2                |

| 14. | CVBS/G/Y             | 46. | $V_{DDAD}$                  | 78. | RAS\            | 110. | A3                |

| 15. | $V_{DDDA}$           | 47. | $V_{DDAD}$                  | 79. | CAS\            | 111. | A4                |

| 16. | C/B/U                | 48. | G_IN                        | 80. | V <sub>DD</sub> | 112. | A5                |

| 17. | $V_{DDDA}$           | 49. | V <sub>SSAD</sub>           | 81. | D0              | 113. | A6                |

| 18. | $V_{DD}$             | 50. | V <sub>TOUT</sub>           | 82. | D1              | 114. | A7                |

| 19. | OSDCLK               | 51. | V <sub>ADCREF</sub>         | 83. | D2              | 115. | A8                |

| 20. | CSYNC                | 52. | V <sub>SSAD</sub>           | 84. | D3              | 116. | A9                |

| 21. | V <sub>SS</sub>      | 53. | B_IN                        | 85. | D4              | 117. | A10               |

| 22. | V <sub>SS</sub>      | 54. | $V_{DDAD}$                  | 86. | D5              | 118. | A11               |

| 23. | EXADSEL              | 55. | CLAMP_REF                   | 87. | D6              | 119. | $V_{DD}$          |

| 24. | G6/OSDB              | 56. | R4                          | 88. | D7              | 120. | B3/GPO3           |

| 25. | G5/OSDG              | 57. | R5                          | 89. | V <sub>SS</sub> | 121. | B2/GPO2           |

| 26. | G4/OSDR              | 58. | R6                          | 90. | $V_{DD}$        | 122. | B1/GPO1           |

| 27. | G7/OSDHT             | 59. | R7                          | 91. | D8              | 123. | B0/GPO0           |

| 28. | V <sub>SS</sub>      | 60. | $V_{DDPA}$                  | 92. | D9              | 124. | V <sub>SSPF</sub> |

| 29. | SIOCLK               | 61. | V <sub>SSPA</sub>           | 93. | D10             | 125. | RAMCK_SEL\        |

| 30. | SIODATA              | 62. | VS_IN                       | 94. | D11             | 126. | RAMCK_OUT         |

| 31. | SIOA <sub>10/7</sub> | 63. | HS_IN                       | 95. | $V_{DD}$        | 127. | RAMCK_IN          |

| 32. | SIOA <sub>0</sub>    | 64. | V <sub>SS</sub>             | 96. | V <sub>SS</sub> | 128. | $V_{DDPF}$        |

# 3. Pin Descriptions

| Pin Name            | Pin Number<br>FS401/FS403 | Type/Value        | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|---------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks              |                           |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OSC1                | 2/1                       | TTL input         | Oscillator Number 1. Default clock input to the encoder. Input from an external oscillator; or one pin of a crystal connected between OSC1 and OSC1BUF. NTSC subcarrier frequency can be derived from this 4f <sub>SC</sub> clock. OSC1 must be connected (see Table 4. Clock Connections).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OSC1BUF             | 3/2                       | LVTTL<br>output   | Oscillator 1 Buffer. If a crystal is used, one pin is connected to OSC1, the other to OSC1BUF. Float this pin if OSC1 is connected to an oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OSC2                | 4/3                       | TTL input         | Oscillator Number 2. Input from an external oscillator; or one pin of a crystal connected between OSC2 and OSC2BUF. PAL subcarrier frequency can be derived from this 4f <sub>SC</sub> clock. Ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OSC2BUF             | 5/4                       | LVTTL<br>output   | Oscillator 2 Buffer. If a crystal is used, one pin is connected to OSC2, the other to OSC2BUF. Float this pin if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HS_IN               | 50/63                     | TTL input         | <b>VGA Horizontal Sync Input.</b> Active HIGH or active LOW polarity is sensed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VS_IN               | 49/62                     | TTL input         | VGA Vertical Sync Input. Active HIGH or active LOW polarity is sensed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Global Contro       | ls                        | 1                 | ppersonal control of the control of |

| INTCPUEN            | 59/77                     | TTL input         | Internal CPU enable. INTCPUEN enables the internal CPU when high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FLP_RST<br>403 only | x/35                      | TTL input         | <b>Field, Line and Pixel Reset.</b> Resets video encoder engine to the start location on the outgoing frame. Used for genlock. Active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RESET               | 30/37                     | TTL input         | <b>Reset.</b> Resets internal state machines and initializes default register values. Active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A/D Converter       | Interface                 |                   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R_IN, G_IN,<br>B_IN | 36/45, 39/48,<br>44/53    | 700 or 1000<br>mV | Analog red, blue and green inputs. AC coupled RGB video input signals. Nominal voltage range is 0.7 or 1.0 Volt peak-to-peak (selectable). Inputs are clamped to ground when HS_IN is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>ADCREF</sub> | 42/51                     | 700 or 1000<br>mV | A/D Converter Top Reference Voltage Input. Input to voltage follower that supplies current to A/D converter reference resistors. Range is 0.5 - 2.0 volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>TOUT</sub>   | 41/50                     | 700 or 1000<br>mV | <b>A/D Converter Top Reference Voltage Output.</b> Output of the internal $V_T$ buffer and direct connection to the A/D reference resistor ladder. If an external A/D voltage is used, it must be capable of driving the $100~\Omega$ load of the ladder. If the internal reference is used, it must be connected to an external $0.1~\mu F$ de-coupling capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VGACLKIN            | 53/67                     | TTL input         | A/D VGA converter clock input. Analog-to-digital converter external clock input if EXTVGASEL\ = L.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EXTVGASEL\          | 52/66                     | TTL input         | A/D VGA clock select. Selects the A/D clock source:  EXTVGASEL\ = H: internal phase-locked loop;  EXTVGASEL\ = L: external clock applied to VGACLKIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pin Name                                 | Pin Number<br>FS401/FS403                                    | Type/Value                    | Pin Function Description                                                                                                                                                                                                                                                                                               |

|------------------------------------------|--------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VGACLKDIV<br>403 only                    | x/65                                                         | LVTTL<br>output               | A/D clock divided by N. VGACLKIN divided by N for connection to external phase-locked loop controller. Polarity selectable.                                                                                                                                                                                            |

| CLAMP_REF                                | 46/55                                                        | LVTTL<br>output               | VGA clock reference output. Clamp output signal. CLAMP_REF = H, when the internal clamp is active during the horizontal sync period, HS_IN. CLAMP_REF can be used for a reference input for an external PLL. Polarity selectable.                                                                                      |

| EXADSEL<br>403 only                      | x/23                                                         | TTL input                     | <b>Analog/Digital RGB in select.</b> LOW selects internal A/D converters; HIGH selects external digital R <sub>7-0</sub> G <sub>7-0</sub> B <sub>7-0</sub> inputs. If LOW, B <sub>7-0</sub> become general purpose outputs. This pin has an internal pull-down and should be left open if the internal A/D is desired. |

| Digital RGB In                           | puts or OSD/G                                                | PO Pins                       |                                                                                                                                                                                                                                                                                                                        |

| R <sub>7-3</sub><br>403 only             | x/59-56, x/41                                                | TTL input                     | <b>Digital red inputs.</b> Top 5 bits of 8-bit red input data. No connection if not used.                                                                                                                                                                                                                              |

| R <sub>2</sub> /OSDEN<br>403 only        | x/40                                                         | TTL input                     | <b>Digital red input/OSD enable.</b> Bit 2 of red input data if EXADSEL is high. Else, OSD enable pin (high enabled). No connection if not used.                                                                                                                                                                       |

| R <sub>1</sub> /<br>TV_HSYNC<br>403 only | x/39                                                         | TTL input/<br>LVTTL<br>output | <b>Digital red input/TV_HSYNC.</b> Bit 1 of red input data if EXADSEL is high. Else, digital horizontal sync for YUV, RGB/SCART, and progressive video outputs. No connection if not used.                                                                                                                             |

| R <sub>0</sub> /<br>TV_VSYNC<br>403 only | x/38                                                         | TTL input/<br>LVTTL<br>output | <b>Digital red input/TV_VSYNC.</b> Bit 0 of red input data if EXADSEL is high. Else, digital vertical sync for YUV, RGB/SCART, and progressive video outputs. No connection if not used.                                                                                                                               |

| G <sub>7</sub> /OSDHT<br>403 only        | x/27                                                         | TTL input                     | <b>Digital green input/OSD half tone.</b> Bit 7 of green input data if EXADSEL is high. Else, OSD half tone input pin. No connection if not used.                                                                                                                                                                      |

| G₄/OSDR<br>403 only                      | x/26                                                         | TTL input                     | <b>Digital green input/OSD red.</b> Bit 4 of green input data if EXADSEL is high. Else, OSD red input pin. No connection if not used.                                                                                                                                                                                  |