# **CXA1362Q**

# Read/Write Amplifier for Floppy Disk Drive with Built-in Filter

#### Description

The CXA1362Q is designed for FDD (Floppy Disk Drive) use. This IC combines such functions as Read, Write, Erase and Supply voltage detection circuits in a single chip.

#### **Features**

- 5V single power supply operation.

- Built-in filter permits switching to 4 modes 1M/2M, inner and outer tracks. This contributes to a drastic reduction of the external parts originally meant for the differentiator constant, low pass filter, select switches and others (Down to 1/2 the original number).

- Filter characteristics can be customized.

- Preamplifier input equivalent noise voltage as low as 2.2 nV/√Hz (Typ.) keeps read data output jitter to a minimum. The preamplifier voltage gain can be selected at either 100 or 200 times.

- Built-in function to select the pulse width of the 1st monostable multivibrator in the time domain filter enables selection through 1M/2M mode.

- Built-in write current selection function allows for 4 mode write current selections: 1M/2M, inner and outer tracks (Other than the filter inner/outer track).

- Built-in supply voltage detection circuit prohibits irregular write during power supply rise, fall or abnormal voltage.

- Power consumption is kept to low 120 mW (Typ.) making suitable for battery drive FDD.

- Built-in capacitor of the time constant in the 1st and 2nd monostable multivibrator (The 2nd monostable multivibrator pulse width is fixed).

- Built-in power saving function to reduce power consumption when not in use. In power saving mode only power ON/OFF detector is in operating condition (5 mW Typ.).

- Built-in reset circuit in the write driver. As a result, when mode selection is switched from read to write, should head side 0 be selected, write current sinks from head side 0A. Similarly, if head side 1 is selected, write current sinks from head 1A.

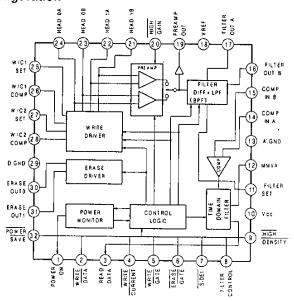

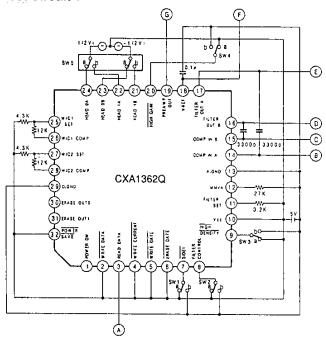

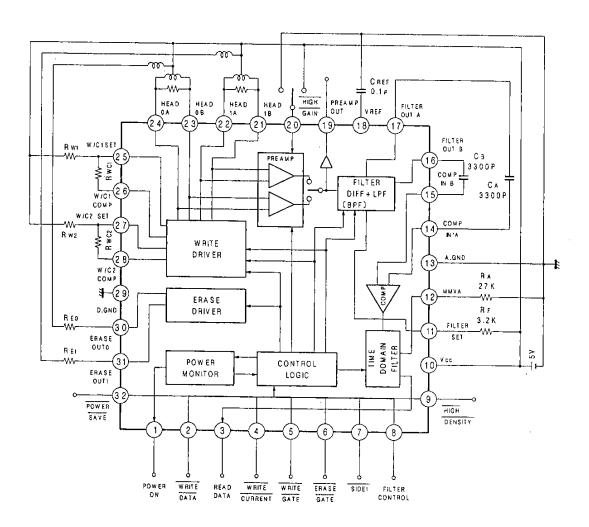

#### **Block Diagram and Pin Configuration**

Sony reserves the right to change products and specifications without notice. This information does not convey any license under patent rights of SONY corporation or others.

#### Structure

Bipolar silicon monolithic IC

| Absolute Maximun | n Ratings i | (Ta⊨ | 25°C) |

|------------------|-------------|------|-------|

|------------------|-------------|------|-------|

| <ul> <li>Supply voltage</li> </ul>                                 | Vcc  |       | 7     |          | V  |

|--------------------------------------------------------------------|------|-------|-------|----------|----|

| <ul> <li>Digital signal input pin (*Note) Input voltage</li> </ul> |      | - 0.5 | to \  | /cc +0.3 | V  |

| <ul> <li>POWER ON output voltage applied</li> </ul>                |      | Vo    | c +0. | 3        | V  |

| <ul> <li>ERASE OUTPUT voltage applied</li> </ul>                   |      | Vc    | c +0. | 3        | V  |

| <ul> <li>Head 0A, 0B, 1A and 1B voltage applied</li> </ul>         |      |       | 15    |          | V  |

| <ul> <li>POWER ON output SINK current</li> </ul>                   |      |       | 7     |          | mΑ |

| <ul> <li>ERASE OUTPUT SINK current</li> </ul>                      |      |       | 150   |          | mΑ |

| <ul> <li>Operating temperature</li> </ul>                          | Topr | -20   | to    | +75      | °C |

| Storage temperature                                                | Tstg | -65   | to    | +150     | °C |

| <ul> <li>Allowable power dissipation</li> </ul>                    | Pο   |       | 500   |          | mW |

|                                                                    |      |       |       |          |    |

| Supply Voltage Range                                               |      |       |       |          |    |

<sup>\*</sup>Note) WRITE DATA, WRITE CURRENT, WRITE GATE, ERASE GATE SIDE1, FILTER CONTROL, HIGH DENSITY, HIGH GAIN, POWER SAVE

Vcc

4.4 to

6.0

٧

# Pin Description

| No. | Symbol            | Voltage | Equivalent Circuit                      | Description                                                                                                                                                                                                                  |

|-----|-------------------|---------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | POWER ON          |         | Vec                                     | Output pin for supply voltage decrease detection. Open collector pin that outputs "L" when Vcc is below normal value.                                                                                                        |

| 2   | WRITE<br>DATA     |         | 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Write data input pin. A schmitt type input triggered when logic voltage shifts from "H" to "L".                                                                                                                              |

| 3   | READ DATA         | _       | 3)<br>0.000                             | Read data output pin. Activated when either write gate signal or erase gate signal logic voltage is at "H".                                                                                                                  |

| 4   | WRITE<br>CURRENT  |         | • ¥ \$100K                              | Write current control pin. Write current increases at logic voltage "L".                                                                                                                                                     |

| 5   | WRITE<br>GATE     |         | ①③   X                                  | Write gate signal input pin. Write system is activated at logic voltage "L".                                                                                                                                                 |

| 6   | ERASE<br>GATE     | _       | A GND                                   | Erase gate signal input pin. Erase system is activated at logic voltage "L".                                                                                                                                                 |

| 7   | SIDE 1            |         |                                         | Head side switching signal input pin. This pin is activated only when logic voltage of both write and erase gates are at "H". At logic voltage "L", HEAD 1 system is selected while HEAD 0 is selected at logic voltage "H". |

| 8   | FILTER<br>CONTROL |         |                                         | Control pin for filter inner/outer tracks. Inner track mode ON at logic voltage "L".                                                                                                                                         |

| 9   | HIGH<br>DENSITY   |         | ·                                       | 1M, 2M mode control pin for filter, time domain filter and write current. 2M mode ON at logic voltage "L".                                                                                                                   |

| 20  | HIGH GAIN         |         |                                         | Voltage gain select pin of the preamplifier.<br>100 times at logic voltage "H" and 200<br>times at logic voltage "L".                                                                                                        |

| No. | Symbol          | Voltage | Equivalent Circuit                                                                     | Description                                                                                                                                                                                 |

|-----|-----------------|---------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | Vcc             | _       |                                                                                        | Power supply (5V) connection pin.                                                                                                                                                           |

| 11  | FILTER SET      | 3.8V    | 1 X X X X X X X X X X X X X X X X X X X                                                | Resistance connecting pin that sets the filter cut off frequency. Connect resistance R <sub>F</sub> for filter cut off setting between this pin and Vcc, then set cut off frequency.        |

| 12  | MMVA            | 0.5V    | V CC  147  A.GND                                                                       | Pulse width setting pin for the 1st monostable multivibrator of the time domain filter. Connect 1st monostable multivibrator pulse width setting resistance RA between this pin and A. GND. |

| 13  | A. GND          | _       |                                                                                        | GND connecting pin for analog system.                                                                                                                                                       |

| 14  | COMP IN A       | 3.3V    | **************************************                                                 | Comparator differential input pin.                                                                                                                                                          |

| 15  | COMP IN B       | 3.3V    | 950 4.043                                                                              |                                                                                                                                                                                             |

| 16  | FILTER<br>OUT B | 3.3V    | 140 \$ 140 <b>T</b>                                                                    | Filter differential output pin.                                                                                                                                                             |

| 17  | FILTER<br>OUT A | 3.3V    | (a)<br>(b)<br>(c)<br>(d)<br>(d)<br>(d)<br>(d)<br>(d)<br>(d)<br>(d)<br>(d)<br>(d)<br>(d |                                                                                                                                                                                             |

| 18  | VREF            | 2.8V    | V CC  W 500  A.GND                                                                     | Connecting pin for the decoupling capacitor of the internal reference voltage. Decoupling capacitor CREF is connected between this pin and A. GND.                                          |

| 19  | PREAMP<br>OUT   | 2.8V    | V <sub>CC</sub> 140  19  200, A.GND                                                    | Preamplifier output pin.                                                                                                                                                                    |

| No. | Symbol         | Voltage                   | Equivalent Circuit  | Description                                                                                                                                                                                         |

|-----|----------------|---------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | HEAD 1B        | _                         | 0000                | Magnetic heads I/O connecting pin. Connects magnetic heads for both Rec/ PB use. Center tap is connected to Vcc. When Pin 7 (SIDE 1) logic voltage is at                                            |

| 22  | HEAD 1A        |                           |                     | "L", HEAD 1 system is activated. At "H", HEAD 0 system is activated.                                                                                                                                |

| 23  | HEAD 0B        | _                         |                     |                                                                                                                                                                                                     |

| 24  | HEAD 0A        | _                         | A GNO               |                                                                                                                                                                                                     |

| 25  | W/C1 SET       | At<br>WG=<br>"H",<br>5V   |                     | Resistance connecting pin for 1M write current setting. Connect Rwi resistance for write current setting between this pin and Vcc, then set write current.                                          |

| 27  | W/C2 SET       | At<br>WG=<br>"L",<br>3.8V | A GNO               | Resistance connecting pin for 2M write current setting. Connect Rw2 resistance for write current setting between this pin and Vcc, then set write current.                                          |

| 26  | W/C1 COMP      |                           | v <sub>cc</sub>     | Resistance connecting pin for 1M write current compensation. Connect resistance Rwc1 for write current compensation between this pin and Pin 25 (W/C1 SET), then set write current increase volume. |

| 28  | W/C2 COMP      | _                         | A.GND               | Resistance connecting pin for 2M write current compensation. Connect resistance Rwc2 for write current compensation between this pin and Pin 27 (W/C2 SET), then set write current increase volume. |

| 29  | D. GND         | _                         | V                   | GND connecting pin for digital system.                                                                                                                                                              |

| 30  | ERASE<br>OUT 0 | -                         | v <sub>cc</sub> 39  | Erase current output pin for HEAD 0 system.                                                                                                                                                         |

| 31  | ERASE<br>OUT 1 | _                         | D.GNO               | Erase current output pin for HEAD 1 system.                                                                                                                                                         |

| 32  | POWER<br>SAVE  |                           | 33 192 K 2.1V A.GND | Input pin for power saving signal. When logic voltage is at "L", power saving is ON. In power saving condition only the power supply ON/OFF detector operates.                                      |

### **Electrical Characteristics**

(Ta=25°C, Vcc=5V)

| Item _                                  | Symbol | Conditions               | Test circuit | Test point | Min. | Тур. | Мах. | Unit |

|-----------------------------------------|--------|--------------------------|--------------|------------|------|------|------|------|

| Consumption current for Read            | ICCR   | Vcc=5V<br>WG="H"         | _            |            | 14.0 | 24.0 | 34.0 | mA   |

| Consumption current for Write and Erase | ICCWE  | Vcc=5V<br>WG="L", EG="L" | _            | _          | 10.5 | 18.0 | 25.5 | mA   |

| Consumption current for<br>Power saving | ICCPS  | Vcc=5V<br>PS="L"         | _            |            | -    | 0.9  | 1.8  | mΑ   |

# Power Supply Observation System

(Ta=25°C)

| Item                                           | Symbol | Conditions        | Test circuit | Test point  | Min. | Тур. | Max. | Unit |

|------------------------------------------------|--------|-------------------|--------------|-------------|------|------|------|------|

| Power supply ON/OFF detector threshold voltage | VTH    |                   | _            | _           | 3.5  | 3.9  | 4.3  | ٧    |

| Power ON output satura-<br>tion voltage        | VSP    | Vcc=3.5V<br>I=1mA | _            | <del></del> |      | 7.5  | 0.5  | V    |

## Read System

| Item                                                     | Symbol | Conditions                                  | Test circuit | Test point | Min.          | Тур.      | Max.          | Unit  |

|----------------------------------------------------------|--------|---------------------------------------------|--------------|------------|---------------|-----------|---------------|-------|

| Preamplifier voltage gain<br>SIDE 0*                     | GV0    | f=100kHz<br>SW4=a,b                         | 1            | G          | 38.1<br>/44.1 | 40<br>/46 | 41.6<br>/47.6 | dB    |

| Preamplifier voltage gain<br>SIDE 1*                     | GV1    | f=100kHz<br>SW4=a,b SW1,5=b                 |              |            | 744.1         | /40       | /47.6         |       |

| Preamplifier frequency characteristics SIDE 0*           | BW0    | Av/Avo=-3dB<br>SW4=a,b                      | 1            | G          | 5             |           |               | MHz   |

| Preamplifier frequency characteristics SIDE 1*           | BW1    | Av/Av1=-3dB<br>SW4=a,b SW1,5=b              |              |            |               |           |               |       |

| Preamplifier input<br>equivalent noise voltage<br>SIDE 0 | EN0    | Bandwidth=400Hz to<br>1MHz<br>SW4=b         | 1            | G          |               | 2.2       | 3.1           | μVrms |

| Preamplifier input<br>equivalent noise voltage<br>SIDE 1 | EN1    | Bandwidth=400Hz to<br>1MHz<br>SW4=b SW1,5=b |              |            |               |           |               |       |

<sup>\*</sup> When SW4=a Vi=10mVp-p When SW4=b Vi=5mVp-p

## **Read System**

| Item                                                                       | Symbol        | Conditions                                         | Test circuit | Test point | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------|---------------|----------------------------------------------------|--------------|------------|------|------|------|------|

| Preamplifier output offset voltage (vs. VREF)                              | VOFSP         | Vi=0<br>SW4=a,b SW1,5=a,b                          | 1            | F, G       | -500 |      | +500 | mV   |

| Preamplifier output voltage amplitude**                                    | VOP           | f=100kHz<br>SW4=a,b SW1,5=a,b                      | 1            | G          | 1.8  | ·    |      | Vp-p |

| Filter differential output offset voltage                                  | VOFSF         | Vi=0                                               | 1            | D, E       | -100 |      | +100 | mV   |

| Filter differential output voltage amplitude                               | VOF           | f=100kHz<br>Vi=60mVp-p                             | 1            | D, E       | 2.8  | 7.1. |      | Vp-p |

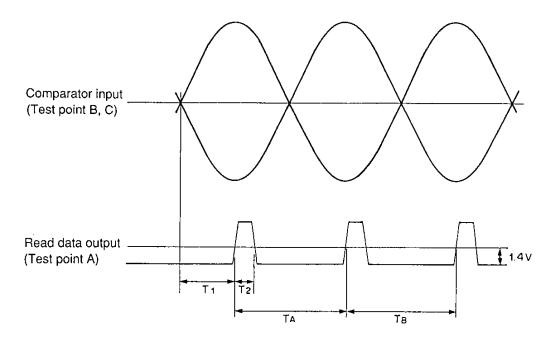

| Time domain filter 1st<br>monostable multivibrator<br>pulse width accuracy | ETM1<br>ETM1' | R <sub>A</sub> =27kΩ<br>See Fig. 1                 | 1            | В, С<br>А  | -10  |      | +10  | %    |

| Time domain filter 2nd<br>monostable multivibrator<br>pulse width (fixed)  | T2            | R <sub>A</sub> =27kΩ<br>See Fig. 1                 | 1            | Α          | 260  | 400  | 540  | ns   |

| Read data output<br>"L" output voltage                                     | VOL           | loL=2mA                                            | 1            | Α          |      |      | 0.5  | V    |

| Read data output<br>"H" output voltage                                     | VOH           | lон=-0.4mA                                         | 1            | Α          | 2.8  |      |      | V    |

| Read data output rise time                                                 | TR            | Rι=2kΩ<br>Cι=20pF                                  | 1            | A          |      |      | 100  | ns   |

| Read data output fall time                                                 | TF            | Rι=2kΩ<br>Cι=20pF                                  | 1            | Α          |      |      | 100  | ns   |

| Peak shift***                                                              | PS            | Vi≃0.25mVp-p to<br>10mVp-p<br>f=62.5kHz See Fig. 1 | 1            | А          |      |      | 1    | %    |

<sup>\*\*</sup> When SW4=a Vi=60mVp-p When SW4=b Vi=30mVp-p

<sup>\*\*\*</sup> When Vi=0.25mVp-p to 5mVp-p, SW4=b (Preamplifier voltage gain 46dB) When Vi=0.5mVp-p to 10mVp-p, SW4=a (Preamplifier voltage gain 40dB)

Fig. 1 1st and 2nd Monostable Multivibrator Pulse Width Accuracy and Peak Shift Test Conditions

1st monostable multivibrator pulse width accuracy When HD="H",

When

$$\overline{HD}$$

="L",  $T_1$  =  $\left(\frac{T_1}{2.45\mu S} - 1\right) \times 100 (\%)$

ETM1' =

$$\left(\frac{T_1}{1.25\mu S} - 1\right) \times 100 (\%)$$

- 2nd monostable multivibrator pulse width = T2

- · Peak shift

$$PS = \frac{1}{2} \left| \frac{T_A - T_B}{T_A + T_B} \right| \times 100 \, (\%)$$

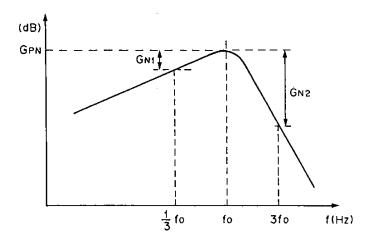

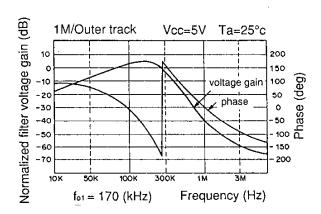

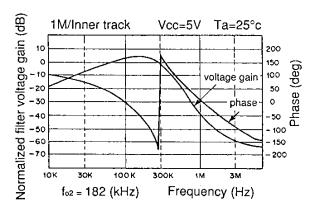

## Read System (FILTER)

(Ta=25°C, Vcc=5V)

|                | Item                          | Symbol           | Conditions                                       | Test circuit | Test point | Min.  | Тур.  | Max.  | Unit |

|----------------|-------------------------------|------------------|--------------------------------------------------|--------------|------------|-------|-------|-------|------|

|                | Peak frequency                | foi              | Vi=3mVp-p HG="L"<br>HD="H" FC="H"                | 1            | D, E       | 153.0 |       | 187.0 | kHz  |

| 1M/Outer track | Peak voltage gain****         | G <sub>P1</sub>  | See Fig. 2 at for                                | 1            | G<br>D, E  | 3.6   | 5.5   | 7.1   | dB   |

| 1M/Out         | Frequency characteristics (1) | Gii              | See Fig. 2<br>at <sup>1</sup> /3 f <sub>01</sub> | 1            | D, E       | -7.6  | -7.1  | -6.6  | dB   |

|                | Frequency characteristics (2) | G12              | See Fig. 2<br>at 3fo <sub>1</sub>                | 1            | D, E       | -25.0 | -23.1 | -21.5 | dΒ   |

|                | Peak frequency                | f <sub>o2</sub>  | Vi=3mVp-p HG="L"<br>HD="H" FC="L"                | 1            | D, E       | 163.8 | 182.0 | 200.2 | kHz  |

| 1M/Inner track | Peak voltage gain****         | G <sub>P2</sub>  | See Fig. 2 at fo2                                | 1            | G<br>D, E  | 3.6   | 5.5   | 7.1   | dB   |

| 1M/Inn         | Frequency characteristics (1) | G21              | See Fig. 2<br>at <sup>1</sup> /3 f <sub>02</sub> | 1            | D, E       | -7.6  | -7.1  | -6.6  | dB   |

|                | Frequency characteristics (2) | G22              | See Fig. 2<br>at 3fo <sub>2</sub>                | 1            | D, E       | -25.0 | -23.1 | -21.5 | dΒ   |

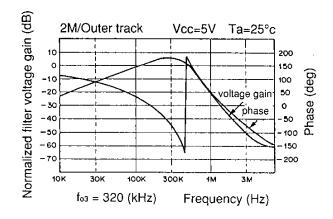

|                | Peak frequency                | f <sub>o</sub> 3 | Vi≃3mVp-p HG="L"<br>HD="L" FC="H"                | 1            | D, E       | 288.0 | 320.0 | 352.0 | kHz  |

| 2M/Outer track | Peak voltage gain****         | GРз              | See Fig. 2 at fo                                 | 1            | G<br>D, E  | 3.6   | 5.5   | 7.1   | dB   |

| 2M/Out         | Frequency characteristics (1) | G31              | See Fig. 2 at 1/3 fo <sub>3</sub>                | 1            | D, E       | -7.6  | -7.1  | -6.6  | dB   |

|                | Frequency characteristics (2) | G32              | See Fig. 2 at 3f <sub>03</sub>                   | 1            | D, E       | -25.0 | -23.1 | -21.5 | dΒ   |

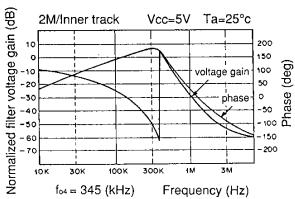

|                | Peak frequency                | fo4              | Vi=3mVp-p HG="L"<br>HD="L" FC="L"                | 1            | D, E       | 310.5 | 345.0 | 379.5 | kHz  |

| 2M/Inner track | Peak voltage gain****         | G <sub>P4</sub>  | See Fig. 2<br>at f <sub>04</sub>                 | 1            | G<br>D, E  | 5.3   | 7.2   | 8.8   | dB   |

| 2M/Inne        | Frequency characteristics (1) | G41              | See Fig. 2<br>at <sup>1</sup> /3 f <sub>04</sub> | 1            | D, E       | -8.6  | -8.1  | -7.6  | dΒ   |

|                | Frequency characteristics (2) | G42              | See Fig. 2<br>at 3f <sub>04</sub>                | 1            | D, E       | -36.2 | -34.3 | -32.7 | dΒ   |

\*\*\*\*  $G_{PN}=20Log (V_{Filterout}/V_{Preout})$

VFilterout : Filter differential output voltage

(N=1 to 4)

Fig. 2 Filter Frequency Characteristics Test Conditions

(N = 1 to 4)

### Write and Erase System

(Ta=25°C, Vcc=5V)

| Item                                           | Symbol | Conditions                                           | Test circuit | Test point | Min. | Тур. | Max. | Unit |

|------------------------------------------------|--------|------------------------------------------------------|--------------|------------|------|------|------|------|

| Write current output accuracy*                 | EW     | WG="L"<br>Rw=4.3kΩ                                   | 2            | LKJI       | -7   |      | +7   | %    |

| Write current output unbalance                 | DW     | WG="L"<br>Rw=4.3kΩ                                   | 2            | LKJI       | -1   |      | +1   | %    |

| Write current compensation current accuracy**  | EWC    | $\overline{WG}$ ="L" $Rw=4.3k\Omega$ $Rwc=12k\Omega$ | 2            | LKJI       | -10  |      | +10  | %    |

| Head I/O pin leak current during write         | ILKW   | WG="L"                                               | 2            | LKJI       |      |      | 10   | μА   |

| Head I/O pin saturation voltage during write   | VSW    | WG="L"<br>SW1=b                                      | 2            | L'K'J'I'   |      |      | 1    | ٧    |

| Erase current switch leak current              | ILKE   | EG="L"                                               | 2            | MN         |      |      | 10   | μА   |

| Erase current switch output saturation voltage | VSE    | EG="L"<br>I=100mA SW2=b                              | 2            | M'N'       |      | 1    | 500  | mV   |

- \* Write current output accuracy  $E_W = \left(\frac{I_W}{2.70 \text{mA}} 1\right) \times 100 (\%)$

- \*\* Write current compensation current accuracy Ewc =  $\left(\frac{\text{Iw'} \text{Iw}}{0.90\text{mA}} 1\right) \times 100 \,(\%)$

Iw: WRITE CURRENT="H"

Iw': WRITE CURRENT="L"

### **Logic Input Section**

| ·····                                               |        | · · · · · · · · · · · · · · · · · · · |              | ····          |      |      | <del></del> |      |  |

|-----------------------------------------------------|--------|---------------------------------------|--------------|---------------|------|------|-------------|------|--|

| Item                                                | Symbol | Conditions                            | Test circuit | Test point    | Min. | Тур. | Max.        | Unit |  |

| Digital signal input "L" input voltage              | VLD    |                                       | 2            | BCDE<br>FGHP  |      |      | 0.8         | ٧    |  |

| Digital signal input "H" input voltage              | VHD    |                                       | 2            | BCDE<br>FGHP  | 2.0  |      |             | ٧    |  |

| Schmitt type digital signal input "L" input voltage | VLSD   |                                       | 2            | Α             |      |      | 0.8         | V    |  |

| Schmitt type digital signal input "H" input voltage | VHSD   |                                       | 2            | Α             | 2.0  |      |             | ٧    |  |

| Digital signal input "L" input current              | ILD    | VL=0V                                 | 2            | ABCD<br>EFGHP | -20  |      |             | μА   |  |

| Digital signal input "H" input current              | IHD    | Vн=5V                                 | 2            | ABCD<br>EFGHP |      |      | 10          | μА   |  |

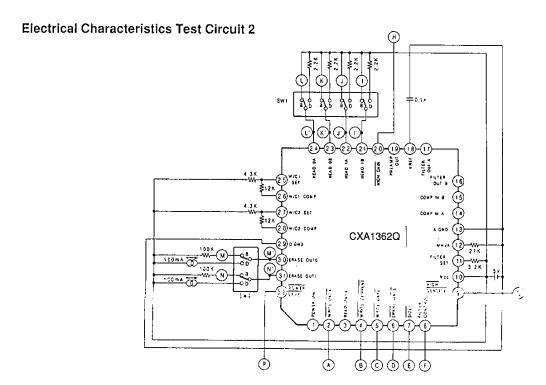

## **Electrical Characteristics Test Circuit 1**

Note) SWs are on side "a", unless otherwise specified.

Note) SWs are on side "a", unless otherwise specified.

#### Operation

#### (1) Read system

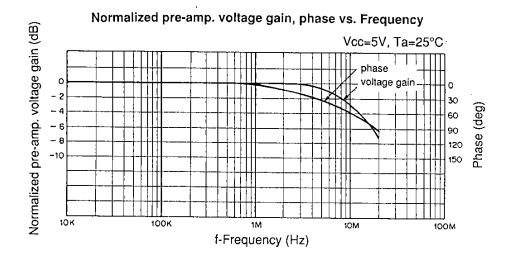

#### Preamplifier

The input signal is amplified.

Voltage gain can be switched to 40dB, 46dB by means of Pin 20.

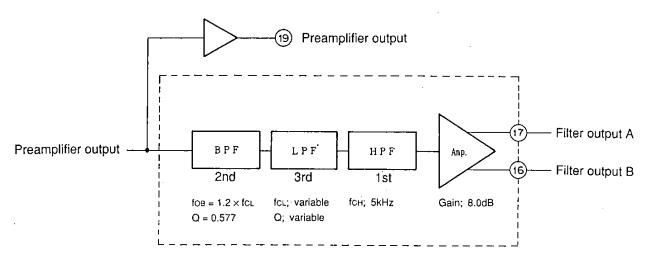

#### Filter

The signal amplified at the preamplifiers is differentiated.

High band noise components are attenuated by means of a low pass filter.

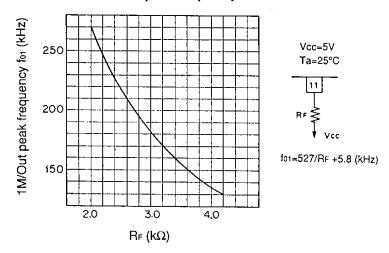

Switching to the filter 4 modes is possible by setting Pins 8 and 9. 1M/outer track mode peak frequency for is set at the external R<sub>F</sub> resistance.

The 3 other  $f_0$  modes are switched according to the value set inside the IC with  $f_{01}$  (1.00) as standard. An explanation on the filter follows.

#### 1 Active filter block

#### Filter characteristics

| Pin 8 | Pin 9 | LPF characteristics  |                      | f₀ ratio |

|-------|-------|----------------------|----------------------|----------|

| Н     | Н     | 1M/Outer track mode: | Butterworth          | 1.00     |

| L     | Н     | 1M/Inner track mode: | Butterworth          | 1.07     |

| H     | L     | 1M/Outer track mode: | Butterworth          | 1.88     |

| L     | L     | 1M/Inner track mode: | Chebychev 1dB ripple | 2.03     |

Table 1

The calculation formula can be explained as follows.

$f_{01}=527/R_F+5.8 \text{ (kHz)}$

for: 1M/Outer track mode peak frequency

R<sub>F</sub>: Filter setting resistance ( $k\Omega$ )

Relation between for and fo with respect to the 4 modes.

$\begin{array}{ll} 1 \text{M/Outer track} & \text{fo1} = 1.0 \times \text{fo1} \\ 1 \text{M/Inner track} & \text{fo2} = 1.07 \times \text{fo1} \\ 1 \text{M/Outer track} & \text{fo3} = 1.88 \times \text{fo1} \\ 1 \text{M/Inner track} & \text{fo4} = 2.03 \times \text{fo1} \end{array}$

This filter can be applied to the customer's requirements.

Application to the customer's requirements is given in pages 16 to 17.

#### Comparator

Detects the filter differential output cross point.

#### Time domain filter

Converts the comparator output into read data.

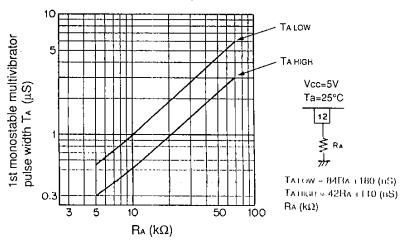

Features 2 monostable multivibrators. The first one eliminates unnecessary pulses. The second determines the read data pulses width. The first monostable multivibrator pulse width T<sub>A</sub> is set by means of resistance R<sub>A</sub> between Pin 12 and A. GND.

Through the setting of Pin 9, Ta can be switched as follows.

```

\overline{\text{HIGH DENSITY}} = "H" Talow = 84Ra +180 (nS) Ra (k\Omega)

\overline{\text{HIGH DENSITY}} = "L" Taligh = 42Ra +110 (nS)

```

The 2nd monostable multivibrator width is fixed at 400 (nS).

### (2) Write system

Write data input from Pin 2 is divided frequency by means of a T flip flop to form the head recording current.

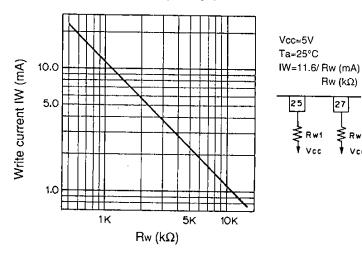

Switching the recording current becomes possible by setting Pin 9. Write current Iw is set by means of resistors Rw between Pin 25 and Vcc, Pin 27 and Vcc.

$lw = 11.6/Rw (mA) Rw (k\Omega)$

Write current compensation lwc is set by means of resistors Rwc between Pins 25 and 26, 27 and 28. lwc = 10.8/Rwc (mA) Rwc (k $\Omega$ )

#### (3) Erase system

Pins 30 and 31 are open collector outputs. Erase current is set through the resistance between these pins and the erase head.

## (4) Power supply ON/OFF detection system

Detects reduced supply voltage.

When Vcc value is below normal, write and erase operations are stopped, which recording and erase functions are prohibited.

#### Notes and Operation

- Select voltage gain so as to obtain a preamplifier output amplitude of 1Vp-p or less.

Should the preamplifier output amplitude exceed 1Vp-p, the filter output waveform would get distorted.

- To mount this device, please take the following precautions.

- Use a Vcc decoupling capacitor of about 0.1 μF and connect it as close to the device as possible.

- · Set as wide GND as possible.

## Application Circuit (for 1M/2M devices)

### **Customer Requirements**

### Filter frequency characteristics

- 4 modes: 1M/Outer track, 1M/Inner track, 2M/Outer track, and 2M/Inner track can vary the filter frequency characteristics.

- The combinations shown below are possible.

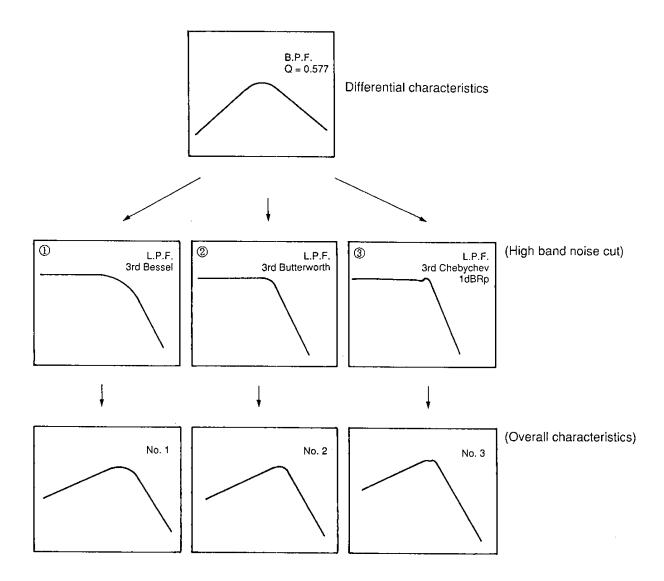

\* No. 1's Bessel characteristics applicable only in 1M/outer track mode.

#### Filter and Customized Selection/Combination

For the filter setting, as shown in Table 1, LPF cut off frequency fc1 in 1M/outer track mode is set at 1.00. For the 3 other modes, fc ratio and the type of LPF are open to selection. LPF selection can be effected from Bessel/Butterworth/Chebychev 1dB ripple. However, for Bessel only the selection of 1M/outer track is possible. BPF center frequency fo<sub>B</sub> is fixed at 1.2 times LPF cut off frequency fc. Also, the relation between peak frequencies fo and fc as regards overall characteristics, is set by the following formula according to the LPF difference in type.

Butterworth characteristics fc = 1.28 fo Chebychev 1dB ripple characteristics fc = 1.12 fo

Table 1. LPF fc ratio and Type

| Mode           | LPF type                                | fc ratio when fc1 is set to 1.00 |

|----------------|-----------------------------------------|----------------------------------|

| 1M/Outer track | ① Bessel                                | 1.00                             |

|                | ② Butterworth                           |                                  |

|                | ③ Chebychev<br>(1dB ripple)             |                                  |

| 1M/Inner track | ② Butterworth                           | 1.07 1.14 1.23 1.33 1.45         |

|                | ③ Chebychev<br>(1dB ripple)             | 1.60 2.00                        |

| 2M/Outer track | ② Butterworth                           | 1.33 1.39 1.45 1.52 1.60         |

|                | ③ Chebychev<br>(1dB ripple)             | 1.68 1.78 1.88 2.00 2.13         |

|                |                                         | 2.29 2.46 2.67                   |

| 2M/Inner track | ② Butterworth  ③ Chebychev (1dB ripple) | 1.33 1.39 1.45 1.52 1.60         |

|                |                                         | 1.68 1.78 1.88 2.00 2.13         |

|                |                                         | 2.29 2.46 2.67                   |

Note) In \_\_\_\_\_ is the setting for CXA1362Q.

Filter 4 modes characteristics (Characteristics where pre-amp. output is normalized. 0dB = pre-amp. output level)

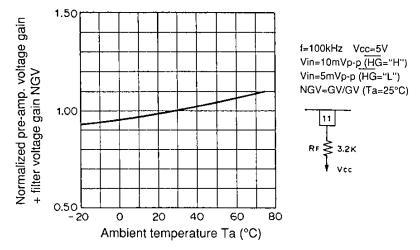

## Normalized pre-amp. voltage gain + filter voltage gain NGV vs. Ambient temperature Ta

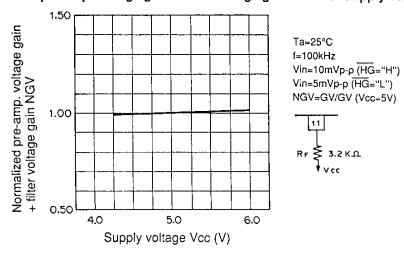

### Normalized pre-amp. voltage gain + filter voltage gain NGV vs. Supply voltage Vcc

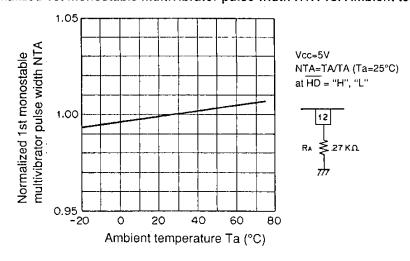

### Normalized 1st monostable multivibrator pulse width NTA vs. Ambient temperature Ta

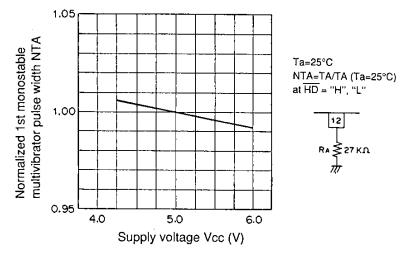

## Normalized 1st monostable multivibrator pulse width NTA vs. Supply voltage Vcc

## 1st monostable multivibrator pulse width TA vs. RA

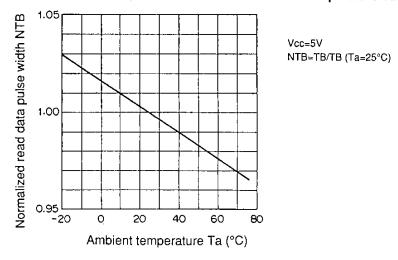

## Normalized read data pulse width NTB vs. Ambient temperature Ta

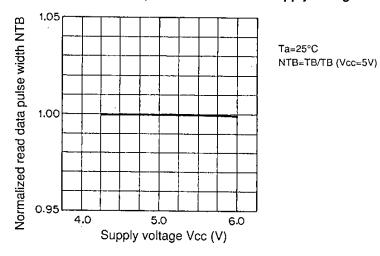

## Normalized read data pulse width NTB vs. Supply voltage Vcc

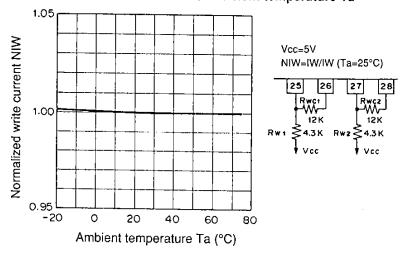

## Normalized write current NIW vs. Ambient temperature Ta

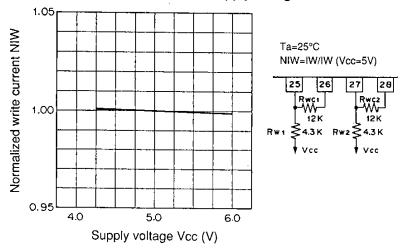

# Normalized write current NIW vs. Supply voltage Vcc

#### Write current IW vs. Rw

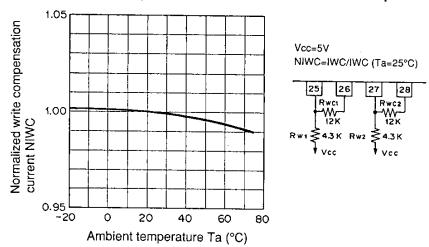

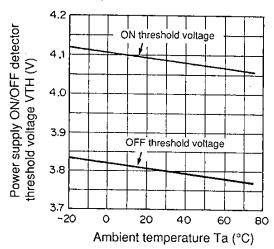

# Normalized write compensation current NIWC vs. Ambient temperature Ta

Rw (kΩ)

## Normalized write compensation current NIWC vs. Supply voltage Vcc

Downloaded from Elcodis.com electronic components distributor

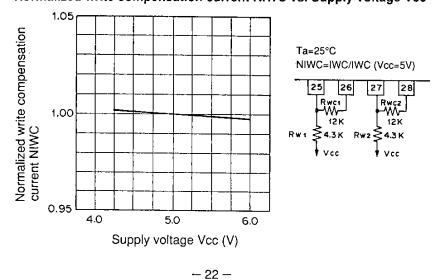

#### Write current compensation quantity IWC vs. Rwc

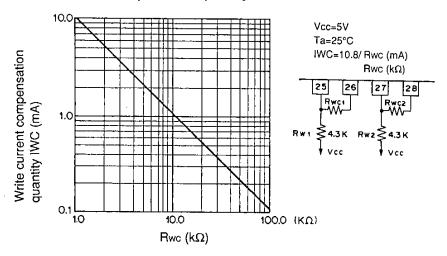

# Power supply ON/OFF detector threshold voltage VTH vs. Ambient temperature Ta

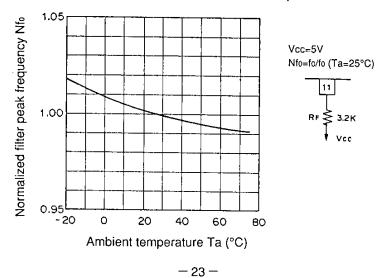

## Normalized filter peak frequency Nfo vs. Ambient temperature Ta

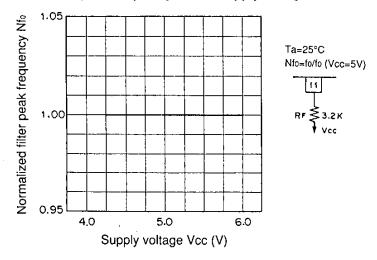

## Normalized filter peak frequency Nfo vs. Supply voltage characteristics Vcc

## 1M/Outer track peak frequency for vs. RF

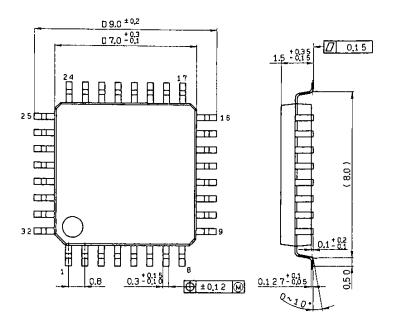

## Package Outline Unit: mm

# 32pin QFP (Plastic) 0.2g

QFP-32P-L01