## 2 Mbit / 4 Mbit / 8 Mbit (x16) Multi-Purpose Flash

SST39LF200A / SST39LF400A / SST39LF800A SST39VF200A / SST39VF400A / SST39VF800A

Data Sheet

#### **FEATURES:**

- Organized as 128K x16 / 256K x16 / 512K x16

- Single Voltage Read and Write Operations

- 3.0-3.6V for SST39LF200A/400A/800A

- 2.7-3.6V for SST39VF200A/400A/800A

- Superior Reliability

- Endurance: 100,000 Cycles (typical)

- Greater than 100 years Data Retention

- Low Power Consumption

- Active Current: 20 mA (typical)

- Standby Current: 3 µA (typical)

- Sector-Erase Capability

- Uniform 2 KWord sectors

- Block-Erase Capability

- Uniform 32 KWord blocks

- Fast Read Access Time

- 45 and 55 ns for SST39LF200A/400A

- 55 ns for SST39LF800A

- 70 and 90 ns for SST39VF200A/400A/800A

- Latched Address and Data

### Fast Erase and Word-Program

- Sector-Erase Time: 18 ms (typical)

- Block-Erase Time: 18 ms (typical)

- Chip-Erase Time: 70 ms (typical)

- Word-Program Time: 14 µs (typical)

- Chip Rewrite Time:

- 2 seconds (typical) for SST39LF/VF200A

- 4 seconds (typical) for SST39LF/VF400A

- 8 seconds (typical) for SST39LF/VF800A

- Automatic Write Timing

- Internal V<sub>PP</sub> Generation

- End-of-Write Detection

- Toggle Bit

- Data# Polling

- CMOS I/O Compatibility

- JEDEC Standard

- Flash EEPROM Pinouts and command sets

- Packages Available

- 48-lead TSOP (12mm x 20mm)

- 48-ball TFBGA (6mm x 8mm)

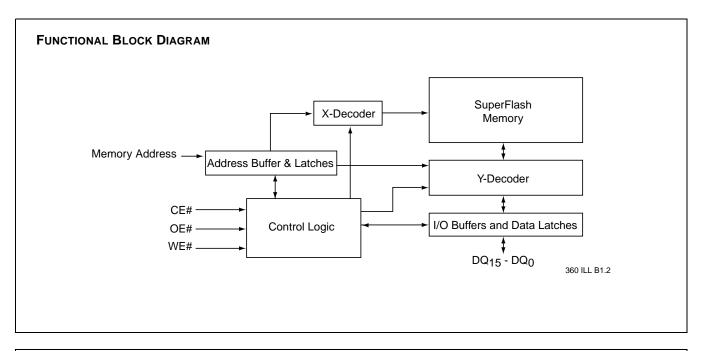

#### PRODUCT DESCRIPTION

The SST39LF200A/400A/800A and SST39VF200A/400A/800A devices are 128K x16 / 256K x16 / 512K x16 CMOS Multi-Purpose Flash (MPF) manufactured with SST's proprietary, high performance CMOS SuperFlash technology. The split-gate cell design and thick oxide tunneling injector attain better reliability and manufacturability compared with alternate approaches. The SST39LF200A/400A/800A write (Program or Erase) with a 3.0-3.6V power supply. The SST39VF200A/400A/800A write (Program or Erase) with a 2.7-3.6V power supply. These devices conform to JEDEC standard pinouts for x16 memories.

Featuring high performance Word-Program, the SST39LF200A/400A/800A and SST39VF200A/400A/ 800A devices provide a typical Word-Program time of 14 µsec. The devices use Toggle Bit or Data# Polling to detect the completion of the Program or Erase operation. To protect against inadvertent write, they have on-chip hardware and software data protection schemes. Designed, manufactured, and tested for a wide spectrum of applications, these devices are offered with a guaranteed endurance of 10,000 cycles. Data retention is rated at greater than 100 years.

The SST39LF200A/400A/800A and SST39VF200A/400A/800A devices are suited for applications that require convenient and economical updating of program, configuration, or data memory. For all system applications, they signifi-

cantly improve performance and reliability, while lowering power consumption. They inherently use less energy during Erase and Program than alternative flash technologies. When programming a flash device, the total energy consumed is a function of the applied voltage, current, and time of application. Since for any given voltage range, the SuperFlash technology uses less current to program and has a shorter erase time, the total energy consumed during any Erase or Program operation is less than alternative flash technologies. These devices also improve flexibility while lowering the cost for program, data, and configuration storage applications.

The SuperFlash technology provides fixed Erase and Program times, independent of the number of Erase/Program cycles that have occurred. Therefore the system software or hardware does not have to be modified or de-rated as is necessary with alternative flash technologies, whose Erase and Program times increase with accumulated Erase/Program cycles.

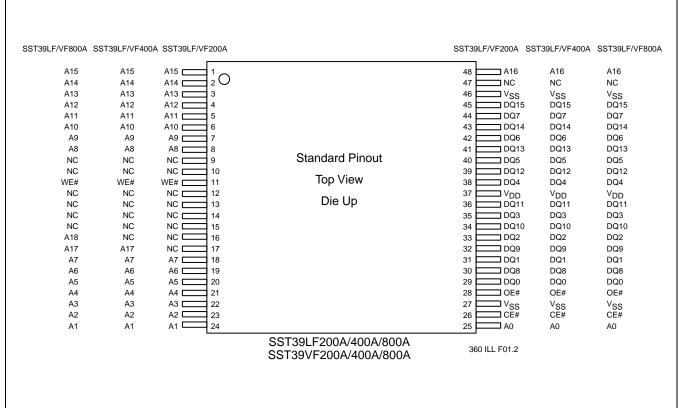

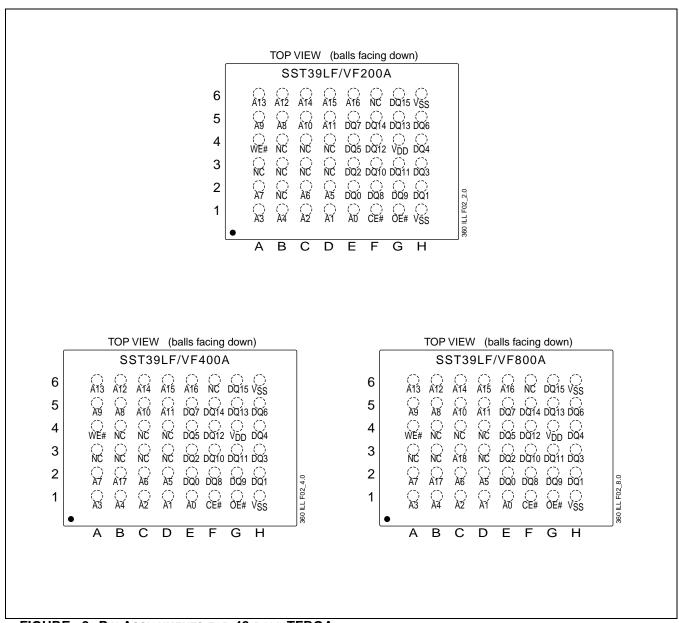

To meet surface mount requirements, the SST39LF200A/400A/800A and SST39VF200A/400A/800A are offered in both 48-lead TSOP packages and 48-ball TFBGA packages. See Figures 1 and 2 for pinouts.

**Data Sheet**

### **Device Operation**

Commands are used to initiate the memory operation functions of the device. Commands are written to the device using standard microprocessor write sequences. A command is written by asserting WE# low while keeping CE# low. The address bus is latched on the falling edge of WE# or CE#, whichever occurs last. The data bus is latched on the rising edge of WE# or CE#, whichever occurs first.

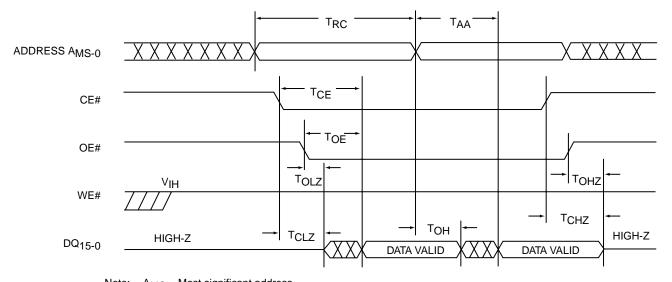

#### Read

The Read operation of the SST39LF200A/400A/800A and SST39VF200A/400A/800A is controlled by CE# and OE#, both have to be low for the system to obtain data from the outputs. CE# is used for device selection. When CE# is high, the chip is deselected and only standby power is consumed. OE# is the output control and is used to gate data from the output pins. The data bus is in high impedance state when either CE# or OE# is high. Refer to the Read cycle timing diagram for further details (Figure 3).

### **Word-Program Operation**

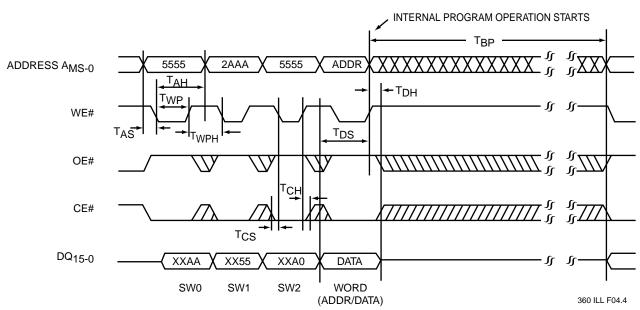

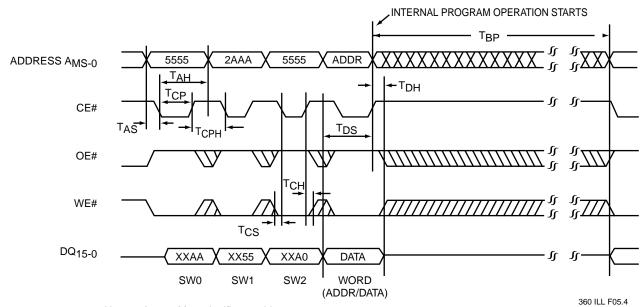

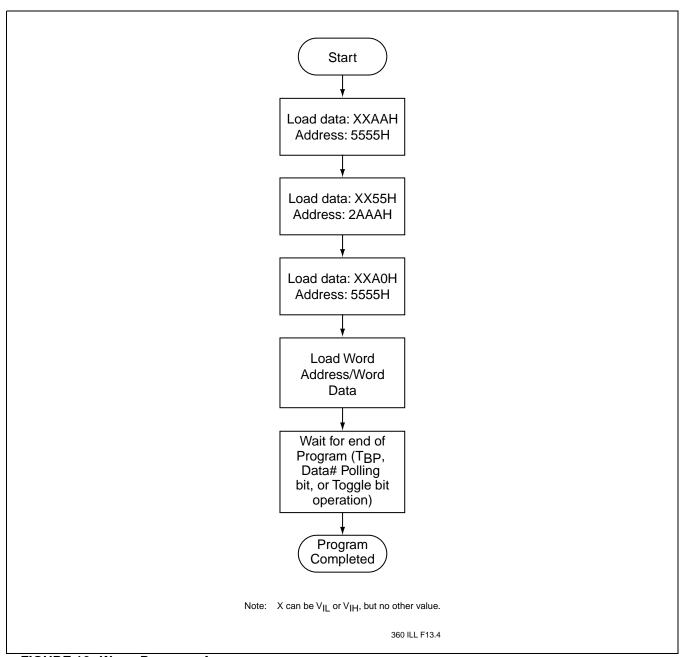

The SST39LF200A/400A/800A and SST39VF200A/400A/ 800A are programmed on a word-by-word basis. Before programming, one must ensure that the sector, in which the word which is being programmed exists, is fully erased. The Program operation consists of three steps. The first step is the three-byte load sequence for Software Data Protection. The second step is to load word address and word data. During the Word-Program operation, the addresses are latched on the falling edge of either CE# or WE#, whichever occurs last. The data is latched on the rising edge of either CE# or WE#, whichever occurs first. The third step is the internal Program operation which is initiated after the rising edge of the fourth WE# or CE#, whichever occurs first. The Program operation, once initiated, will be completed within 20 µs. See Figures 4 and 5 for WE# and CE# controlled Program operation timing diagrams and Figure 16 for flowcharts. During the Program operation, the only valid reads are Data# Polling and Toggle Bit. During the internal Program operation, the host is free to perform additional tasks. Any commands issued during the internal Program operation are ignored.

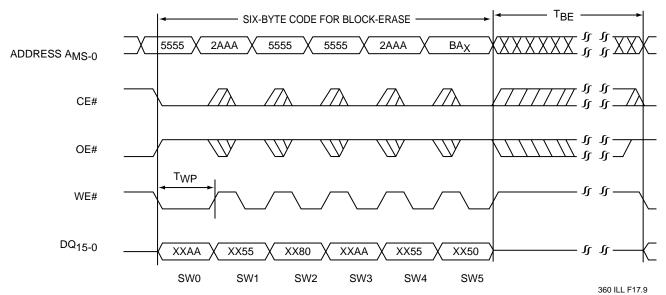

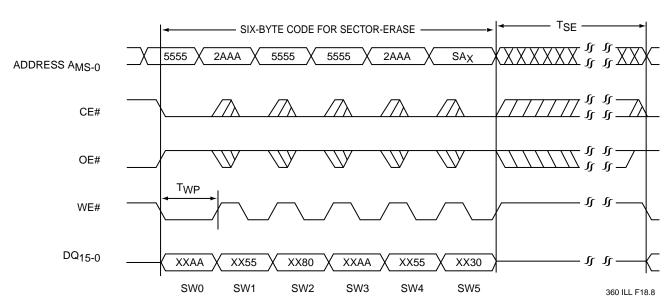

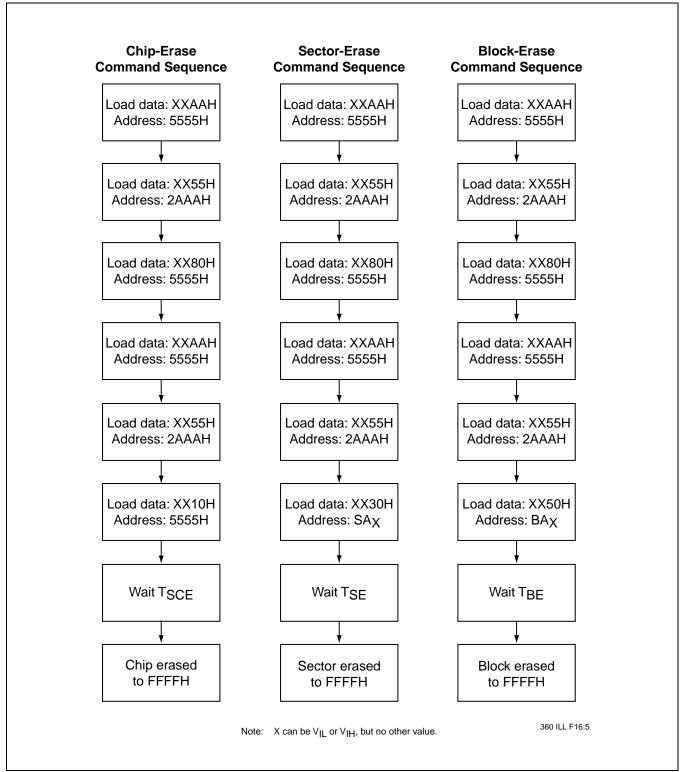

### **Sector/Block-Erase Operation**

The Sector- (or Block-) Erase operation allows the system to erase the device on a sector-by-sector (or block-by-block) basis. The SST39LF200A/400A/800A and SST39VF200A/400A/800A offers both Sector-Erase and Block-Erase mode. The sector architecture is based on uniform sector size of 2 KWord. The Block-Erase mode is based on uniform block size of 32 KWord. The Sector-

Erase operation is initiated by executing a six-byte command sequence with Sector-Erase command (30H) and sector address (SA) in the last bus cycle. The Block-Erase operation is initiated by executing a six-byte command sequence with Block-Erase command (50H) and block address (BA) in the last bus cycle. The sector or block address is latched on the falling edge of the sixth WE# pulse, while the command (30H or 50H) is latched on the rising edge of the sixth WE# pulse. The internal Erase operation begins after the sixth WE# pulse. The End-of-Erase operation can be determined using either Data# Polling or Toggle Bit methods. See Figures 9 and 10 for timing waveforms. Any commands issued during the Sector-or Block-Erase operation are ignored.

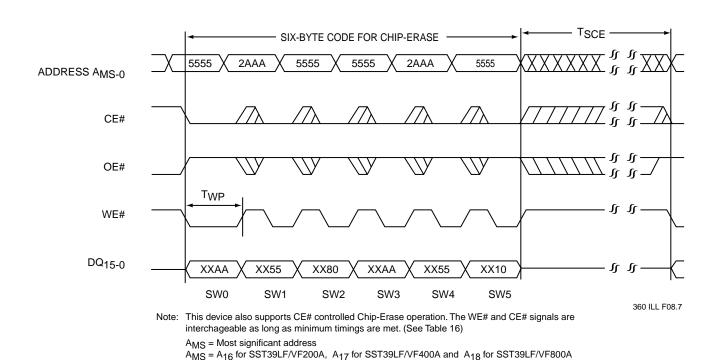

### **Chip-Erase Operation**

The SST39LF200A/400A/800A and SST39VF200A/400A/800A provide a Chip-Erase operation, which allows the user to erase the entire memory array to the "1" state. This is useful when the entire device must be quickly erased.

The Chip-Erase operation is initiated by executing a sixbyte command sequence with Chip-Erase command (10H) at address 5555H in the last byte sequence. The Erase operation begins with the rising edge of the sixth WE# or CE#, whichever occurs first. During the Erase operation, the only valid read is Toggle Bit or Data# Polling. See Table 4 for the command sequence, Figure 8 for timing diagram, and Figure 19 for the flowchart. Any commands issued during the Chip-Erase operation are ignored.

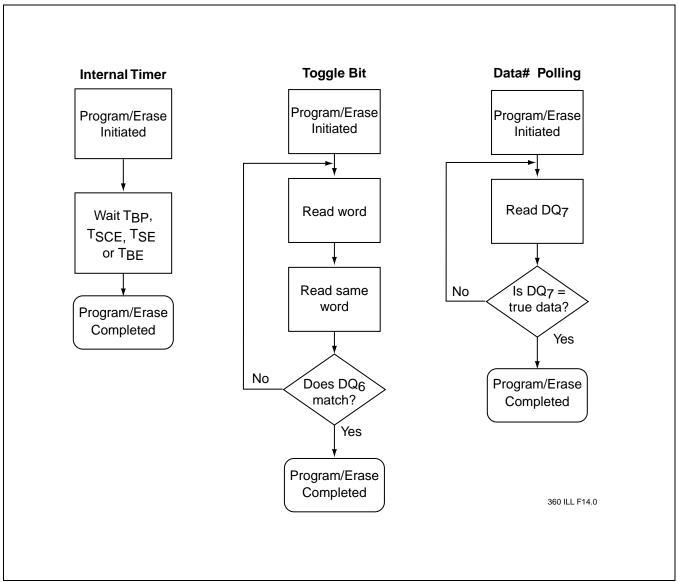

### Write Operation Status Detection

The SST39LF200A/400A/800A and SST39VF200A/400A/800A provide two software means to detect the completion of a write (Program or Erase) cycle, in order to optimize the system write cycle time. The software detection includes two status bits: Data# Polling (DQ $_7$ ) and Toggle Bit (DQ $_6$ ). The End-of-Write detection mode is enabled after the rising edge of WE#, which initiates the internal Program or Erase operation.

The actual completion of the nonvolatile write is asynchronous with the system; therefore, either a Data# Polling or Toggle Bit read may be simultaneous with the completion of the write cycle. If this occurs, the system may possibly get an erroneous result, i.e., valid data may appear to conflict with either  $DQ_7$  or  $DQ_6$ . In order to prevent spurious rejection, if an erroneous result occurs, the software routine should include a loop to read the accessed location an additional two (2) times. If both reads are valid, then the device has completed the write cycle, otherwise the rejection is valid.

**Data Sheet**

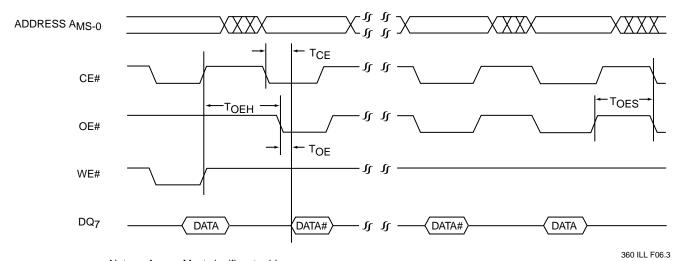

### Data# Polling (DQ<sub>7</sub>)

When the SST39LF200A/400A/800A and SST39VF200A/400A/800A are in the internal Program operation, any attempt to read DQ $_7$  will produce the complement of the true data. Once the Program operation is completed, DQ $_7$  will produce true data. The device is then ready for the next operation. During internal Erase operation, any attempt to read DQ $_7$  will produce a '0'. Once the internal Erase operation is completed, DQ $_7$  will produce a '1'. The Data# Polling is valid after the rising edge of fourth WE# (or CE#) pulse for Program operation. For Sector-, Block- or Chip-Erase, the Data# Polling is valid after the rising edge of sixth WE# (or CE#) pulse. See Figure 6 for Data# Polling timing diagram and Figure 17 for a flowchart.

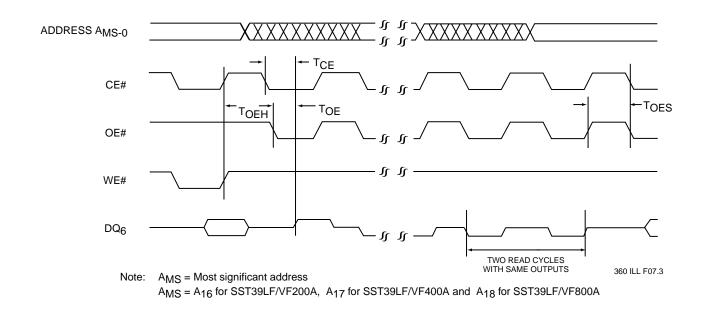

### Toggle Bit (DQ<sub>6</sub>)

During the internal Program or Erase operation, any consecutive attempts to read  $\mathsf{DQ}_6$  will produce alternating 1s and 0s, i.e., toggling between 1 and 0. When the internal Program or Erase operation is completed, the  $\mathsf{DQ}_6$  bit will stop toggling. The device is then ready for the next operation. The Toggle Bit is valid after the rising edge of fourth WE# (or CE#) pulse for Program operation. For Sector-, Block- or Chip-Erase, the Toggle Bit is valid after the rising edge of sixth WE# (or CE#) pulse. See Figure 7 for Toggle Bit timing diagram and Figure 17 for a flowchart.

#### **Data Protection**

The SST39LF200A/400A/800A and SST39VF200A/400A/800A provide both hardware and software features to protect nonvolatile data from inadvertent writes.

### **Hardware Data Protection**

Noise/Glitch Protection: A WE# or CE# pulse of less than 5 ns will not initiate a write cycle.

$V_{DD}$  Power Up/Down Detection: The Write operation is inhibited when  $V_{DD}$  is less than 1.5V.

<u>Write Inhibit Mode</u>: Forcing OE# low, CE# high, or WE# high will inhibit the Write operation. This prevents inadvertent writes during power-up or power-down.

### **Software Data Protection (SDP)**

The SST39LF200A/400A/800A and SST39VF200A/400A/800A provide the JEDEC approved Software Data Protection scheme for all data alteration operations, i.e., Program and Erase. Any Program operation requires the inclusion of the three-byte sequence. The three-byte load sequence is used to initiate the Program operation, providing optimal protection from inadvertent Write operations, e.g., during the system power-up or power-down. Any Erase operation requires the inclusion of six-byte sequence. This group of devices are shipped with the Software Data Protection permanently enabled. See Table 4 for the specific software command codes. During SDP command sequence, invalid commands will abort the device to Read mode within TRC. The contents of DQ<sub>15</sub>-DQ<sub>8</sub> can be V<sub>IL</sub> or V<sub>IH</sub>, but no other value, during any SDP command sequence.

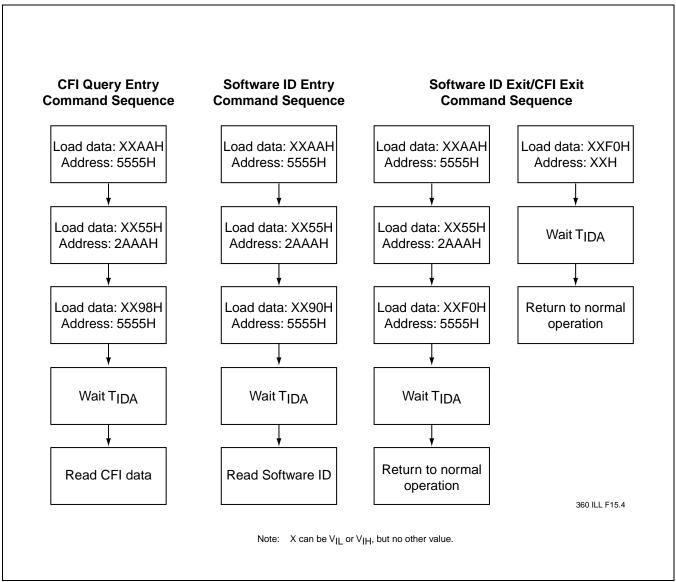

### **Common Flash Memory Interface (CFI)**

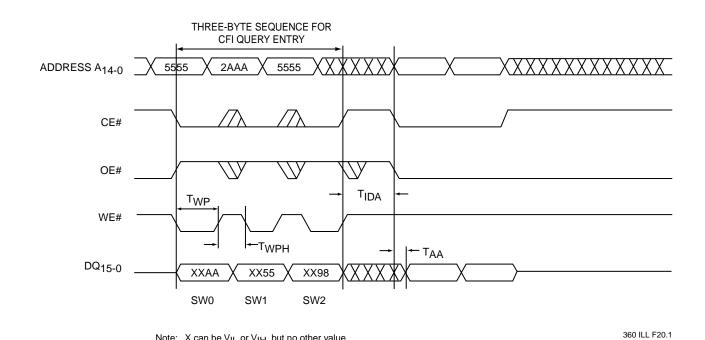

The SST39LF200A/400A/800A and SST39VF200A/400A/800A also contain the CFI information to describe the characteristics of the device. In order to enter the CFI Query mode, the system must write three-byte sequence, same as Software ID Entry command with 98H (CFI Query command) to address 5555H in the last byte sequence. Once the device enters the CFI Query mode, the system can read CFI data at the addresses given in Tables 5 through 9. The system must write the CFI Exit command to return to Read mode from the CFI Query mode.

**Data Sheet**

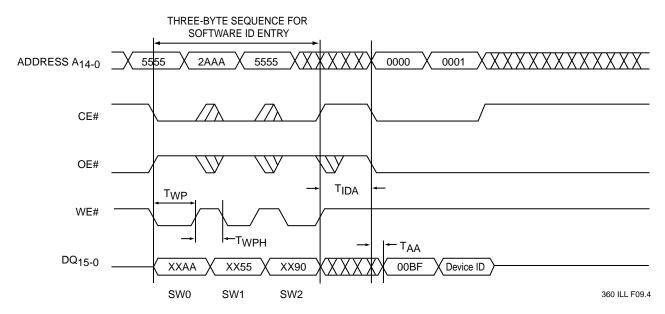

### **Product Identification**

The Product Identification mode identifies the devices as the SST39LF/VF200A, SST39LF/VF400A and SST39LF/VF800A and manufacturer as SST. This mode may be accessed by software operations. Users may use the Software Product Identification operation to identify the part (i.e., using the device ID) when using multiple manufacturers in the same socket. For details, see Table 4 for software operation, Figure 11 for the Software ID Entry and Read timing diagram, and Figure 18 for the Software ID Entry command sequence flowchart.

TABLE 1: PRODUCT IDENTIFICATION TABLE

|                   | Address | Data  |

|-------------------|---------|-------|

| Manufacturer's ID | 0000H   | 00BFH |

| Device ID         |         |       |

| SST39LF/VF200A    | 0001H   | 2789H |

| SST39LF/VF400A    | 0001H   | 2780H |

| SST39LF/VF800A    | 0001H   | 2781H |

T1.3 360

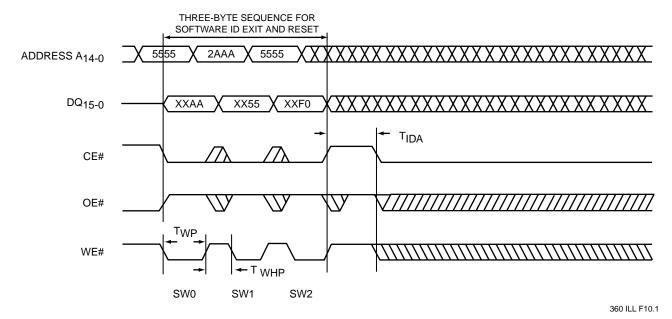

### Product Identification Mode Exit/ CFI Mode Exit

In order to return to the standard Read mode, the Software Product Identification mode must be exited. Exit is accomplished by issuing the Software ID Exit command sequence, which returns the device to the Read mode. This command may also be used to reset the device to the Read mode after any inadvertent transient condition that apparently causes the device to behave abnormally, e.g., not read correctly. Please note that the Software ID Exit/ CFI Exit command is ignored during an internal Program or Erase operation. See Table 4 for software command codes, Figure 13 for timing waveform and Figure 18 for a flowchart.

FIGURE 1: PIN ASSIGNMENTS FOR 48-LEAD TSOP

FIGURE 2: PIN ASSIGNMENTS FOR 48-BALL TFBGA

**Data Sheet**

TABLE 2: PIN DESCRIPTION

| Symbol                                       | Pin Name          | Functions                                                                                                                                                                              |                                                                                                                                                                                        |  |  |  |  |

|----------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A <sub>MS</sub> <sup>1</sup> -A <sub>0</sub> | Address Inputs    |                                                                                                                                                                                        | To provide memory addresses. During Sector-Erase $A_{MS}$ - $A_{11}$ address lines will select the sector. During Block-Erase $A_{MS}$ - $A_{15}$ address lines will select the block. |  |  |  |  |

| DQ <sub>15</sub> -DQ <sub>0</sub>            | Data Input/output | To output data during Read cycles and receive input data during Write cycles.  Data is internally latched during a Write cycle.  The outputs are in tri-state when OE# or CE# is high. |                                                                                                                                                                                        |  |  |  |  |

| CE#                                          | Chip Enable       | To activate the device when CE# is low.                                                                                                                                                |                                                                                                                                                                                        |  |  |  |  |

| OE#                                          | Output Enable     | To gate the data output buffers.                                                                                                                                                       |                                                                                                                                                                                        |  |  |  |  |

| WE#                                          | Write Enable      | To control the Write operations.                                                                                                                                                       |                                                                                                                                                                                        |  |  |  |  |

| $V_{DD}$                                     | Power Supply      | To provide power supply voltage:                                                                                                                                                       | 3.0-3.6V for SST39LF200A/400A/800A<br>2.7-3.6V for SST39VF200A/400A/800A                                                                                                               |  |  |  |  |

| $V_{SS}$                                     | Ground            |                                                                                                                                                                                        |                                                                                                                                                                                        |  |  |  |  |

| NC                                           | No Connection     | Unconnected pins.                                                                                                                                                                      |                                                                                                                                                                                        |  |  |  |  |

T2.2 360

$A_{MS} = A_{16}$  for SST39LF/VF200A,  $A_{17}$  for SST39LF/VF400A, and  $A_{18}$  for SST39LF/VF800A

TABLE 3: OPERATION MODES SELECTION

| Mode                   | CE#             | OE#             | WE#             | DQ                       | Address                                        |

|------------------------|-----------------|-----------------|-----------------|--------------------------|------------------------------------------------|

| Read                   | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | D <sub>OUT</sub>         | A <sub>IN</sub>                                |

| Program                | V <sub>IL</sub> | V <sub>IH</sub> | $V_{IL}$        | D <sub>IN</sub>          | A <sub>IN</sub>                                |

| Erase                  | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | X <sup>1</sup>           | Sector or Block address,<br>XXH for Chip-Erase |

| Standby                | V <sub>IH</sub> | Х               | Х               | High Z                   | X                                              |

| Write Inhibit          | X               | VIL             | Х               | High Z/ D <sub>OUT</sub> | X                                              |

|                        | X               | Х               | $V_{IH}$        | High Z/ D <sub>OUT</sub> | X                                              |

| Product Identification |                 |                 |                 |                          |                                                |

| Software Mode          | V <sub>IL</sub> | V <sub>IL</sub> | $V_{IH}$        |                          | See Table 4                                    |

1. X can be  $V_{IL}$  or  $V_{IH}$ , but no other value.

<sup>1.</sup> A<sub>MS</sub> = Most significant address

**Data Sheet**

T4.2 360

TABLE 4: SOFTWARE COMMAND SEQUENCE

| Command<br>Sequence                         | 1st I<br>Write    |                   | 2nd l<br>Write (  |                   | 3rd<br>Write      |                   | 4th I<br>Write    |                   | 5th E<br>Write    |                   | 6th I<br>Write               |                   |

|---------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------------|-------------------|

|                                             | Addr <sup>1</sup> | Data <sup>2</sup> | Addr <sup>1</sup>            | Data <sup>2</sup> |

| Word-Program                                | 5555H             | AAH               | 2AAAH             | 55H               | 5555H             | A0H               | WA <sup>3</sup>   | Data              |                   |                   |                              |                   |

| Sector-Erase                                | 5555H             | AAH               | 2AAAH             | 55H               | 5555H             | 80H               | 5555H             | AAH               | 2AAAH             | 55H               | SA <sub>X</sub> <sup>4</sup> | 30H               |

| Block-Erase                                 | 5555H             | AAH               | 2AAAH             | 55H               | 5555H             | 80H               | 5555H             | AAH               | 2AAAH             | 55H               | BA <sub>X</sub> <sup>4</sup> | 50H               |

| Chip-Erase                                  | 5555H             | AAH               | 2AAAH             | 55H               | 5555H             | 80H               | 5555H             | AAH               | 2AAAH             | 55H               | 5555H                        | 10H               |

| Software ID Entry <sup>5,6</sup>            | 5555H             | AAH               | 2AAAH             | 55H               | 5555H             | 90H               |                   |                   |                   |                   |                              |                   |

| CFI Query Entry <sup>5</sup>                | 5555H             | AAH               | 2AAAH             | 55H               | 5555H             | 98H               |                   |                   |                   |                   |                              |                   |

| Software ID Exit <sup>7</sup> /<br>CFI Exit | XXH               | F0H               |                   |                   |                   |                   |                   |                   |                   |                   |                              |                   |

| Software ID Exit <sup>7</sup> /<br>CFI Exit | 5555H             | AAH               | 2AAAH             | 55H               | 5555H             | F0H               |                   |                   |                   |                   |                              |                   |

1. Address format A<sub>14</sub>-A<sub>0</sub> (Hex),

Addresses  $A_{15}$  and  $A_{16}$  can be  $V_{IL}$  or  $V_{IH}$ , but no other value, for the Command sequence for SST39LF/VF200A. Addresses  $A_{15}$ ,  $A_{16}$ , and  $A_{17}$  can be  $V_{IL}$  or  $V_{IH}$ , but no other value, for the Command sequence for SST39LF/VF400A. Addresses  $A_{15}$ ,  $A_{16}$ ,  $A_{17}$ , and  $A_{18}$  can be  $V_{IL}$  or  $V_{IH}$ , but no other value, for the Command sequence for SST39LF/VF800A.

- 2.  $DQ_{15}$   $DQ_8$  can be  $V_{IL}$  or  $V_{IH}$ , but no other value, for the Command sequence

- 3. WA = Program word address

- SA<sub>X</sub> for Sector-Erase; uses A<sub>MS</sub>-A<sub>11</sub> address lines BA<sub>X</sub>, for Block-Erase; uses A<sub>MS</sub>-A<sub>15</sub> address lines A<sub>MS</sub> = Most significant address

- $A_{MS} = A_{16}$  for SST39LF/VF200A,  $A_{17}$  for SST39LF/VF400A and  $A_{18}$  for SST39LF/VF800A

- 5. The device does not remain in Software Product ID Mode if powered down.

- 6. With  $A_{MS}$ - $A_1$  =0; SST Manufacturer's ID= 00BFH, is read with  $A_0$  = 0, SST39LF/VF200A Device ID = 2789H, is read with  $A_0$  = 1.

- SST39LF/VF400A Device ID = 2789H, is read with  $A_0 = 1$ . SST39LF/VF400A Device ID = 2780H, is read with  $A_0 = 1$ .

- SST39LF/VF800A Device ID = 2781H, is read with  $A_0 = 1$ .

- 7. Both Software ID Exit operations are equivalent

TABLE 5: CFI QUERY IDENTIFICATION STRING1 FOR SST39LF200A/400A/800A AND SST39VF200A/400A/800A

| Address | Data  | Data                                                        |

|---------|-------|-------------------------------------------------------------|

| 10H     | 0051H | Query Unique ASCII string "QRY"                             |

| 11H     | 0052H |                                                             |

| 12H     | 0059H |                                                             |

| 13H     | 0001H | Primary OEM command set                                     |

| 14H     | 0007H |                                                             |

| 15H     | 0000H | Address for Primary Extended Table                          |

| 16H     | 0000H |                                                             |

| 17H     | 0000H | Alternate OEM command set (00H = none exists)               |

| 18H     | 0000H |                                                             |

| 19H     | 0000H | Address for Alternate OEM extended Table (00H = none exits) |

| 1AH     | 0000H |                                                             |

1. Refer to CFI publication 100 for more details.

T5.0 360

Data Sheet

TABLE 6: SYSTEM INTERFACE INFORMATION FOR SST39LF200A/400A/800A AND SST39VF200A/400A/800A

| Address | Data               | Data                                                                                                                                |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1BH     | 0027H <sup>1</sup> | V <sub>DD</sub> Min. (Program/Erase)                                                                                                |

|         | 0030H <sup>1</sup> | DQ <sub>7</sub> -DQ <sub>4</sub> : Volts, DQ <sub>3</sub> -DQ <sub>0</sub> : 100 millivolts                                         |

| 1CH     | 0036H              | V <sub>DD</sub> Max. (Program/Erase)<br>DQ <sub>7</sub> -DQ <sub>4</sub> : Volts, DQ <sub>3</sub> -DQ <sub>0</sub> : 100 millivolts |

| 1DH     | 0000H              | $V_{PP}$ min. (00H = no $V_{PP}$ pin)                                                                                               |

| 1EH     | 0000H              | $V_{PP}$ max. (00H = no $V_{PP}$ pin)                                                                                               |

| 1FH     | 0004H              | Typical time out for Word-Program $2^N$ µs ( $2^4$ = 16 µs)                                                                         |

| 20H     | 0000H              | Typical time out for min. size buffer program 2 <sup>N</sup> µs (00H = not supported)                                               |

| 21H     | 0004H              | Typical time out for individual Sector/Block-Erase 2 <sup>N</sup> ms (2 <sup>4</sup> = 16 ms)                                       |

| 22H     | 0006H              | Typical time out for Chip-Erase 2 <sup>N</sup> ms (2 <sup>6</sup> = 64 ms)                                                          |

| 23H     | 0001H              | Maximum time out for Word-Program $2^N$ times typical ( $2^1 \times 2^4 = 32 \mu s$ )                                               |

| 24H     | 0000H              | Maximum time out for buffer program 2 <sup>N</sup> times typical                                                                    |

| 25H     | 0001H              | Maximum time out for individual Sector/Block-Erase 2 <sup>N</sup> times typical (2 <sup>1</sup> x 2 <sup>4</sup> = 32 ms)           |

| 26H     | 0001H              | Maximum time out for Chip-Erase 2 <sup>N</sup> times typical (2 <sup>1</sup> x 2 <sup>6</sup> = 128 ms)                             |

T6.2 360

TABLE 7: DEVICE GEOMETRY INFORMATION FOR SST39LF/VF200A

| Address | Data  | Data                                                                              |

|---------|-------|-----------------------------------------------------------------------------------|

| 27H     | 0012H | Device size = 2 <sup>N</sup> Byte (12H = 18; 2 <sup>18</sup> = 256 KBytes)        |

| 28H     | 0001H | Flash Device Interface description; 0001H = x16-only asynchronous interface       |

| 29H     | 0000H |                                                                                   |

| 2AH     | 0000H | Maximum number of byte in multi-byte write = 2 <sup>N</sup> (00H = not supported) |

| 2BH     |       |                                                                                   |

| 2CH     | 0002H | Number of Erase Sector/Block sizes supported by device                            |

| 2DH     | 003FH | Sector Information (y + 1 = Number of sectors; z x 256B = sector size)            |

| 2EH     | 0000H | y = 63 + 1 = 64 sectors (003FH = 63)                                              |

| 2FH     | 0010H |                                                                                   |

| 30H     | 0000H | z = 16 x 256 Bytes = 4 KBytes/sector (0010H = 16)                                 |

| 31H     | 0003H | Block Information (y + 1 = Number of blocks; z x 256B = block size)               |

| 32H     | 0000H | y = 3 + 1 = 4 blocks (0003H = 3)                                                  |

| 33H     | 0000H |                                                                                   |

| 34H     | 0001H | z = 256 x 256 Bytes = 64 KBytes/block (0100H = 256)                               |

T7.2 360

<sup>1. 0030</sup>H for SST39LF200A/400A/800A and 0027H for SST39VF200A/400A/800A

**Data Sheet**

TABLE 8: DEVICE GEOMETRY INFORMATION FOR SST39LF/VF400A

| Address | Data  | Data                                                                              |

|---------|-------|-----------------------------------------------------------------------------------|

| 27H     | 0013H | Device size = 2 <sup>N</sup> Byte (13H = 19; 2 <sup>19</sup> = 512 KBytes)        |

| 28H     | 0001H | Flash Device Interface description; 0001H = x16-only asynchronous interface       |

| 29H     | 0000H |                                                                                   |

| 2AH     | 0000H | Maximum number of byte in multi-byte write = 2 <sup>N</sup> (00H = not supported) |

| 2BH     | 0000H |                                                                                   |

| 2CH     | 0002H | Number of Erase Sector/Block sizes supported by device                            |

| 2DH     | 007FH | Sector Information (y + 1 = Number of sectors; z x 256B = sector size)            |

| 2EH     | 0000H | y = 127 + 1 = 128 sectors (007FH = 127)                                           |

| 2FH     | 0010H |                                                                                   |

| 30H     | 0000H | z = 16 x 256 Bytes = 4 KBytes/sector (0010H = 16)                                 |

| 31H     | 0007H | Block Information (y + 1 = Number of blocks; z x 256B = block size)               |

| 32H     | 0000H | y = 7 + 1 = 8  blocks  (0007H = 7)                                                |

| 33H     | 0000H |                                                                                   |

| 34H     | 0001H | z = 256 x 256 Bytes = 64 KBytes/block (0100H = 256)                               |

T8.1 360

TABLE 9: DEVICE GEOMETRY INFORMATION FOR SST39LF/VF800A

| Address | Data  | Data                                                                        |

|---------|-------|-----------------------------------------------------------------------------|

| 27H     | 0014H | Device size = 2 <sup>N</sup> Byte (14H = 20; 2 <sup>20</sup> = 1 MByte)     |

| 28H     | 0001H | Flash Device Interface description; 0001H = x16-only asynchronous interface |

| 29H     | 0000H |                                                                             |

| 2AH     | 0000H | Maximum number of byte in multi-byte write = $2^N$ (00H = not supported)    |

| 2BH     | 0000H |                                                                             |

| 2CH     | 0002H | Number of Erase Sector/Block sizes supported by device                      |

| 2DH     | 00FFH | Sector Information (y + 1 = Number of sectors; z x 256B = sector size)      |

| 2EH     | 0000H | y = 255 + 1 = 256 sectors (00FFH = 255)                                     |

| 2FH     | 0010H |                                                                             |

| 30H     | 0000H | z = 16 x 256 Bytes = 4 KBytes/sector (0010H = 16)                           |

| 31H     | 000FH | Block Information (y + 1 = Number of blocks; z x 256B = block size)         |

| 32H     | 0000H | y = 15 + 1 = 16 blocks (000FH = 15)                                         |

| 33H     | 0000H |                                                                             |

| 34H     | 0001H | z = 256 x 256 Bytes = 64 KBytes/block (0100H = 256)                         |

T9.0 360

#### **Data Sheet**

**Absolute Maximum Stress Ratings** (Applied conditions greater than those listed under "Absolute Maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

| Temperature Under Bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55°C to +125°C                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65°C to +150°C                 |

| D. C. Voltage on Any Pin to Ground Potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.5V to V <sub>DD</sub> + 0.5V |

| Transient Voltage (<20 ns) on Any Pin to Ground Potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0V to V <sub>DD</sub> + 1.0V |

| Voltage on A <sub>9</sub> Pin to Ground Potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.5V to 13.2V                  |

| Package Power Dissipation Capability (Ta = 25°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.0W                           |

| Surface Mount Lead Soldering Temperature (3 Seconds)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 240°C                          |

| Output Short Circuit Current <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50 mA                          |

| 4. On the character of form and account the contract of the contract of the contract of the character of the contract of the C |                                |

<sup>1.</sup> Outputs shorted for no more than one second. No more than one output shorted at a time.

### OPERATING RANGE: SST39LF200A/400A/800A

| Range      | Ambient Temp | $V_{DD}$ |

|------------|--------------|----------|

| Commercial | 0°C to +70°C | 3.0-3.6V |

### OPERATING RANGE: SST39VF200A/400A/800A

| Range      | Ambient Temp   | $V_{\mathrm{DD}}$ |  |  |

|------------|----------------|-------------------|--|--|

| Commercial | 0°C to +70°C   | 2.7-3.6V          |  |  |

| Extended   | -20°C to +85°C | 2.7-3.6V          |  |  |

| Industrial | -40°C to +85°C | 2.7-3.6V          |  |  |

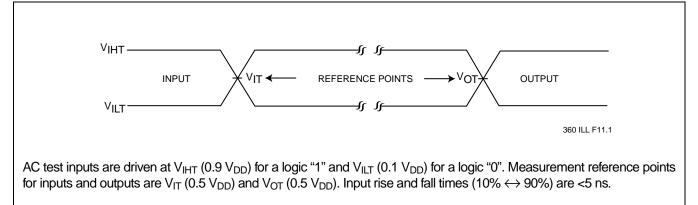

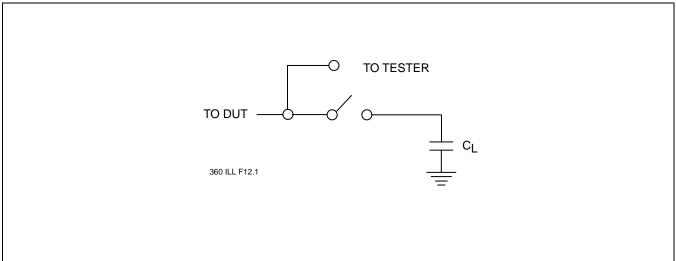

### **AC CONDITIONS OF TEST**

| Input Rise/Fall Time 5 ns |  |

|---------------------------|--|

| Output Load               |  |

| Output Load               |  |

| See Figures 14 and 15     |  |

**Data Sheet**

TABLE 10: DC OPERATING CHARACTERISTICS  $V_{DD} = 3.0\text{-}3.6\text{V for SST39LF200A/400A/800A} \text{ and } 2.7\text{-}3.6\text{V for SST39VF200A/400A/800A}$

|                 |                                 | Limits               |     |       |                                                                               |

|-----------------|---------------------------------|----------------------|-----|-------|-------------------------------------------------------------------------------|

| Symbol          | Parameter                       | Min                  | Max | Units | Test Conditions                                                               |

| I <sub>DD</sub> | Power Supply Current            |                      |     |       | Address input = $V_{IL}/V_{IH}$ , at f=1/ $T_{RC}$ Min., $V_{DD}=V_{DD}$ Max. |

|                 | Read                            |                      | 30  | mA    | CE#=OE#=V <sub>IL</sub> ,WE#=V <sub>IH</sub> , all I/Os open                  |

|                 | Program and Erase               |                      | 30  | mA    | CE#=WE#=V <sub>IL</sub> , OE#=V <sub>IH</sub>                                 |

| I <sub>SB</sub> | Standby V <sub>DD</sub> Current |                      | 20  | μΑ    | CE#=V <sub>IHC</sub> , V <sub>DD</sub> = V <sub>DD</sub> Max.                 |

| ILI             | Input Leakage Current           |                      | 1   | μΑ    | $V_{IN}$ =GND to $V_{DD}$ , $V_{DD}$ = $V_{DD}$ Max.                          |

| $I_{LO}$        | Output Leakage Current          |                      | 10  | μΑ    | $V_{OUT}$ =GND to $V_{DD}$ , $V_{DD}$ = $V_{DD}$ Max.                         |

| V <sub>IL</sub> | Input Low Voltage               |                      | 0.8 |       | $V_{DD} = V_{DD}$ Min.                                                        |

| $V_{IH}$        | Input High Voltage              | 0.7V <sub>DD</sub>   |     | V     | $V_{DD} = V_{DD} Max.$                                                        |

| $V_{IHC}$       | Input High Voltage (CMOS)       | V <sub>DD</sub> -0.3 |     | V     | $V_{DD} = V_{DD} Max.$                                                        |

| V <sub>OL</sub> | Output Low Voltage              |                      | 0.2 | V     | $I_{OL} = 100 \mu A$ , $V_{DD} = V_{DD} Min$ .                                |

| $V_{OH}$        | Output High Voltage             | V <sub>DD</sub> -0.2 |     | V     | $I_{OH} = -100 \ \mu A, \ V_{DD} = V_{DD} \ Min.$                             |

T10.5 360

#### TABLE 11: RECOMMENDED SYSTEM POWER-UP TIMINGS

| Symbol                             | Parameter                           | Minimum | Units |

|------------------------------------|-------------------------------------|---------|-------|

| T <sub>PU-READ</sub> <sup>1</sup>  | Power-up to Read Operation          | 100     | μs    |

| T <sub>PU-WRITE</sub> <sup>1</sup> | Power-up to Program/Erase Operation | 100     | μs    |

T11.0 360

### TABLE 12: CAPACITANCE (Ta = 25°C, f=1 Mhz, other pins open)

| Parameter                     | Description         | Test Condition | Maximum |

|-------------------------------|---------------------|----------------|---------|

| C <sub>I/O</sub> <sup>1</sup> | I/O Pin Capacitance | $V_{I/O} = 0V$ | 12 pF   |

| C <sub>IN</sub> <sup>1</sup>  | Input Capacitance   | $V_{IN} = 0V$  | 6 pF    |

T12.0 360

#### **TABLE 13: RELIABILITY CHARACTERISTICS**

| Symbol                        | Parameter      | Minimum Specification | Units  | Test Method         |

|-------------------------------|----------------|-----------------------|--------|---------------------|

| N <sub>END</sub> <sup>1</sup> | Endurance      | 10,000                | Cycles | JEDEC Standard A117 |

| T <sub>DR</sub> <sup>1</sup>  | Data Retention | 100                   | Years  | JEDEC Standard A103 |

| I <sub>LTH</sub> <sup>1</sup> | Latch Up       | 100 + I <sub>DD</sub> | mA     | JEDEC Standard 78   |

T13.1 360

<sup>1.</sup> This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

<sup>1.</sup> This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

<sup>1.</sup> This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

**Data Sheet**

### **AC CHARACTERISTICS**

TABLE 14: READ CYCLE TIMING PARAMETERS VDD = 3.0-3.6V

|                               |                                 | SST39LF200A/400A-45 |     | SST39LF200A/400A/800A-55 |     |       |

|-------------------------------|---------------------------------|---------------------|-----|--------------------------|-----|-------|

| Symbol                        | Parameter                       | Min                 | Max | Min                      | Max | Units |

| T <sub>RC</sub>               | Read Cycle Time                 | 45                  |     | 55                       |     | ns    |

| T <sub>CE</sub>               | Chip Enable Access Time         |                     | 45  |                          | 55  | ns    |

| T <sub>AA</sub>               | Address Access Time             |                     | 45  |                          | 55  | ns    |

| T <sub>OE</sub>               | Output Enable Access Time       |                     | 30  |                          | 30  | ns    |

| T <sub>CLZ</sub> <sup>1</sup> | CE# Low to Active Output        | 0                   |     | 0                        |     | ns    |

| T <sub>OLZ</sub> <sup>1</sup> | OE# Low to Active Output        | 0                   |     | 0                        |     | ns    |

| T <sub>CHZ</sub> <sup>1</sup> | CE# High to High-Z Output       |                     | 15  |                          | 15  | ns    |

| T <sub>OHZ</sub> <sup>1</sup> | OE# High to High-Z Output       |                     | 15  |                          | 15  | ns    |

| T <sub>OH</sub> <sup>1</sup>  | Output Hold from Address Change | 0                   |     | 0                        |     | ns    |

T14.7 360

TABLE 15: READ CYCLE TIMING PARAMETERS VDD= 2.7-3.6V

|                               |                                 | SST39VF200A/400A/800A-70 |     | SST39VF200A/400A/800A-90 |     |       |

|-------------------------------|---------------------------------|--------------------------|-----|--------------------------|-----|-------|

| Symbol                        | Parameter                       | Min                      | Max | Min                      | Max | Units |

| T <sub>RC</sub>               | Read Cycle Time                 | 70                       |     | 90                       |     | ns    |

| T <sub>CE</sub>               | Chip Enable Access Time         |                          | 70  |                          | 90  | ns    |

| T <sub>AA</sub>               | Address Access Time             |                          | 70  |                          | 90  | ns    |

| T <sub>OE</sub>               | Output Enable Access Time       |                          | 35  |                          | 45  | ns    |

| T <sub>CLZ</sub> <sup>1</sup> | CE# Low to Active Output        | 0                        |     | 0                        |     | ns    |

| T <sub>OLZ</sub> 1            | OE# Low to Active Output        | 0                        |     | 0                        |     | ns    |

| T <sub>CHZ</sub> <sup>1</sup> | CE# High to High-Z Output       |                          | 20  |                          | 30  | ns    |

| T <sub>OHZ</sub> <sup>1</sup> | OE# High to High-Z Output       |                          | 20  |                          | 30  | ns    |

| T <sub>OH</sub> <sup>1</sup>  | Output Hold from Address Change | 0                        |     | 0                        |     | ns    |

T15.6 360

<sup>1.</sup> This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

<sup>1.</sup> This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

**Data Sheet**

TABLE 16: PROGRAM/ERASE CYCLE TIMING PARAMETERS

| Symbol                        | Parameter                        | Min | Max | Units |

|-------------------------------|----------------------------------|-----|-----|-------|

| T <sub>BP</sub>               | Word-Program Time                |     | 20  | μs    |

| T <sub>AS</sub>               | Address Setup Time               | 0   |     | ns    |

| T <sub>AH</sub>               | Address Hold Time                | 30  |     | ns    |

| T <sub>CS</sub>               | WE# and CE# Setup Time           | 0   |     | ns    |

| T <sub>CH</sub>               | WE# and CE# Hold Time            | 0   |     | ns    |

| T <sub>OES</sub>              | OE# High Setup Time              | 0   |     | ns    |

| T <sub>OEH</sub>              | OE# High Hold Time               | 10  |     | ns    |

| T <sub>CP</sub>               | CE# Pulse Width                  | 40  |     | ns    |

| T <sub>WP</sub>               | WE# Pulse Width                  | 40  |     | ns    |

| T <sub>WPH</sub> <sup>1</sup> | WE# Pulse Width High             | 30  |     | ns    |

| T <sub>CPH</sub> <sup>1</sup> | CE# Pulse Width High             | 30  |     | ns    |

| T <sub>DS</sub>               | Data Setup Time                  | 30  |     | ns    |

| T <sub>DH</sub> <sup>1</sup>  | Data Hold Time                   | 0   |     | ns    |

| T <sub>IDA</sub> <sup>1</sup> | Software ID Access and Exit Time |     | 150 | ns    |

| T <sub>SE</sub>               | Sector-Erase                     |     | 25  | ms    |

| T <sub>BE</sub>               | Block-Erase                      |     | 25  | ms    |

| T <sub>SCE</sub>              | Chip-Erase                       |     | 100 | ms    |

T16.0 360

<sup>1.</sup> This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

**Data Sheet**

Note:  $A_{MS}$  = Most significant address  $A_{MS}$  =  $A_{16}$  for SST39LF/VF200A,  $A_{17}$  for SST39LF/VF400A and  $A_{18}$  for SST39LF/VF800A

360 ILL F03.2

FIGURE 3: READ CYCLE TIMING DIAGRAM

Note: A<sub>MS</sub> = Most significant address

$A_{MS} = A_{16} \ \text{for SST39LF/VF200A}, \ A_{17} \ \text{for SST39LF/VF400A} \ \text{and} \ A_{18} \ \text{for SST39LF/VF800A}$

X can be  $V_{IL}$  or  $V_{IH}$ , but no other value.

FIGURE 4: WE# CONTROLLED PROGRAM CYCLE TIMING DIAGRAM

**Data Sheet**

Note: A<sub>MS</sub> = Most significant address

$A_{MS} = A_{16}$  for SST39LF/VF200A,  $\,A_{17}$  for SST39LF/VF400A and  $\,A_{18}$  for SST39LF/VF800A

X can be V<sub>IL</sub> or V<sub>IH</sub>, but no other value.

FIGURE 5: CE# CONTROLLED PROGRAM CYCLE TIMING DIAGRAM

Note: A<sub>MS</sub> = Most significant address

$A_{MS} = A_{16}$  for SST39LF/VF200A,  $A_{17}$  for SST39LF/VF400A and  $A_{18}$  for SST39LF/VF800A

FIGURE 6: DATA# POLLING TIMING DIAGRAM

**Data Sheet**

FIGURE 7: TOGGLE BIT TIMING DIAGRAM

FIGURE 8: WE# CONTROLLED CHIP-ERASE TIMING DIAGRAM

X can be V<sub>IL</sub> or V<sub>IH</sub>, but no other value.

**Data Sheet**

Note: This device also supports CE# controlled Block-Erase operation. The WE# and CE# signals are

interchageable as long as minimum timings are met. (See Table 16)

$BA_X = Block Address$

A<sub>MS</sub> = Most significant address

$A_{MS} = A_{16}$  for SST39LF/VF200A,  $A_{17}$  for SST39LF/VF400A and  $A_{18}$  for SST39LF/VF800A

X can be  $V_{IL}$  or  $V_{IH}$ , but no other value.

FIGURE 9: WE# CONTROLLED BLOCK-ERASE TIMING DIAGRAM

Note: This device also supports CE# controlled Sector-Erase operation. The WE# and CE# signals are

interchageable as long as minimum timings are met. (See Table 16)

SA<sub>X</sub> = Sector Address

A<sub>MS</sub> = Most significant address

$A_{MS} = A_{16}$  for SST39LF/VF200A,  $A_{17}$  for SST39LF/VF400A and  $A_{18}$  for SST39LF/VF800A

X can be  $V_{\mbox{\scriptsize IL}}$  or  $V_{\mbox{\scriptsize IH}},$  but no other value.

FIGURE 10: WE# CONTROLLED SECTOR-ERASE TIMING DIAGRAM

**Data Sheet**

Device ID = 2789H for SST39LF/VF200A, 2780H for SST39LF/VF400A and 2781H for SST39LF/VF800A Note: X can be  $V_{IL}$  or  $V_{IH}$ , but no other value.

FIGURE 11: SOFTWARE ID ENTRY AND READ

FIGURE 12: CFI QUERY ENTRY AND READ

Note: X can be V<sub>IL</sub> or V<sub>IH</sub>, but no other value.

Data Sheet

Note: X can be  $V_{IL}$  or  $V_{IH}$ , but no other value.

FIGURE 13: SOFTWARE ID EXIT/CFI EXIT

**Data Sheet**

Note: V<sub>IT</sub> - V<sub>INPUT</sub> Test V<sub>OT</sub> - V<sub>OUTPUT</sub> Test V<sub>IHT</sub> - V<sub>INPUT</sub> HIGH Test V<sub>ILT</sub> - V<sub>INPUT</sub> LOW Test

FIGURE 14: AC INPUT/OUTPUT REFERENCE WAVEFORMS

FIGURE 15: A TEST LOAD EXAMPLE

FIGURE 16: WORD-PROGRAM ALGORITHM

FIGURE 17: WAIT OPTIONS

FIGURE 18: SOFTWARE ID/CFI COMMAND FLOWCHARTS

FIGURE 19: ERASE COMMAND SEQUENCE

**Data Sheet**

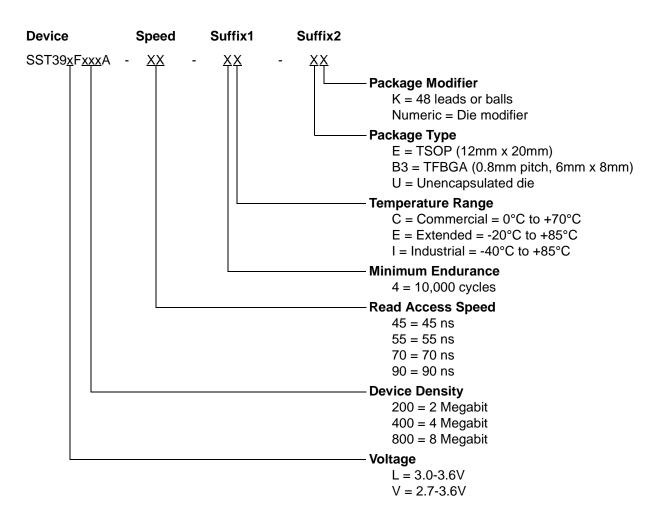

### PRODUCT ORDERING INFORMATION

#### **Data Sheet**

#### Valid combinations for SST39LF200A

SST39LF200A-45-4C-EK SST39LF200A-45-4C-B3K SST39LF200A-55-4C-EK SST39LF200A-55-4C-B3K

#### Valid combinations for SST39VF200A

SST39VF200A-70-4C-EK SST39VF200A-70-4C-B3K SST39VF200A-90-4C-EK SST39VF200A-90-4C-B3K

SST39VF200A-70-4I-EK SST39VF200A-70-4I-B3K SST39VF200A-90-4I-EK SST39VF200A-90-4I-B3K

#### Valid combinations for SST39LF400A

SST39LF400A-45-4C-EK SST39LF400A-45-4C-B3K SST39LF400A-55-4C-EK SST39LF400A-55-4C-B3K

#### Valid combinations for SST39VF400A

SST39VF400A-70-4C-EK SST39VF400A-70-4C-B3K SST39VF400A-90-4C-EK SST39VF400A-90-4C-B3K SST39VF400A-90-4C-U1

SST39VF400A-70-4I-EK SST39VF400A-70-4I-B3K SST39VF400A-90-4I-EK SST39VF400A-90-4I-B3K

#### Valid combinations for SST39LF800A

#### Valid combinations for SST39VF800A

SST39VF800A-70-4C-EK SST39VF800A-70-4C-B3K SST39VF800A-90-4C-EK SST39VF800A-90-4C-B3K

SST39VF800A-90-4C-U1

SST39VF800A-70-4I-EK SST39VF800A-70-4I-B3K SST39VF800A-90-4I-EK SST39VF800A-90-4I-B3K

**Note:** Valid combinations are those products in mass production or will be in mass production. Consult your SST sales representative to confirm availability of valid combinations and to determine availability of new combinations.

**Data Sheet**

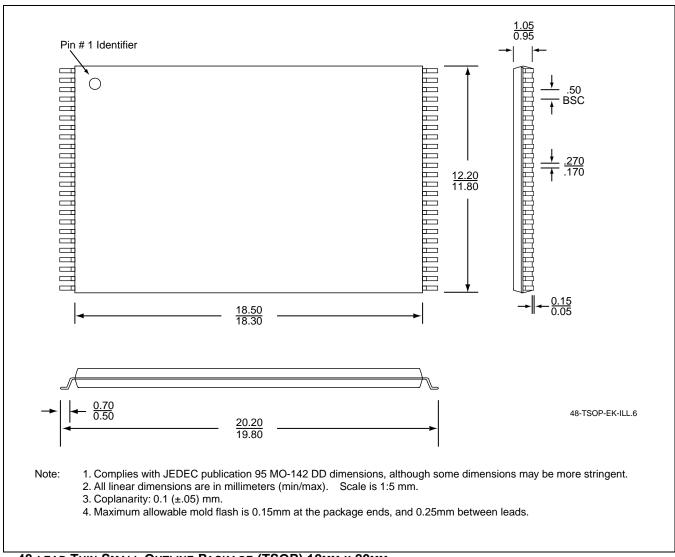

### **PACKAGING DIAGRAMS**

48-LEAD THIN SMALL OUTLINE PACKAGE (TSOP) 12MM X 20MM SST PACKAGE CODE: EK

©2001 Silicon Storage Technology, Inc. S71117-04-000 6/01 360

**Data Sheet**

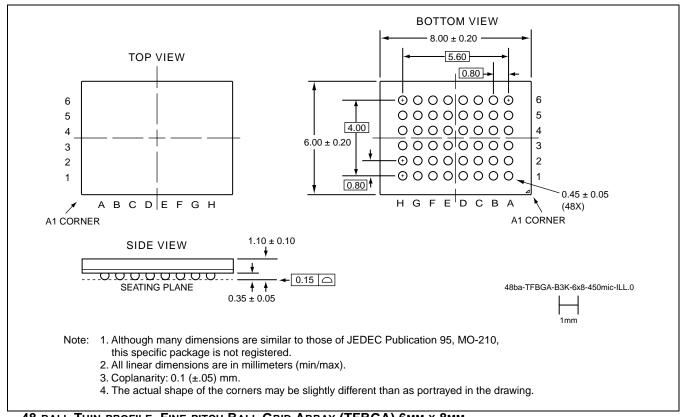

48-BALL THIN-PROFILE, FINE-PITCH BALL GRID ARRAY (TFBGA) 6MM X 8MM SST PACKAGE CODE: B3K

**Data Sheet**

Silicon Storage Technology, Inc. • 1171 Sonora Court • Sunnyvale, CA 94086 • Telephone 408-735-9110 • Fax 408-735-9036 www.SuperFlash.com or www.ssti.com