# 8 bit 35 MSPS RGB 3-Channel D/A Converter

#### Description

CXA1260Q-Z is an 8-bit high-speed D/A converter for video band use. It has an output/input equivalent to 3 channels of R, G and B. It is suitable for use of digital TV, graphic display, etc.

#### **Features**

- · Resolution: 8-bits

- Maximum conversion speed: 35MSPS

- RGB 3-channel input/output

- Differential linearity error. ±1/2LSB

- Digital input voltage: TTL level

- Output voltage full-scale: 1 Vp-p (typ)

- · Low power consumption: 360 mW (typ)

- +5V single power supply

#### Structure

Bipolar silicon monolithic IC

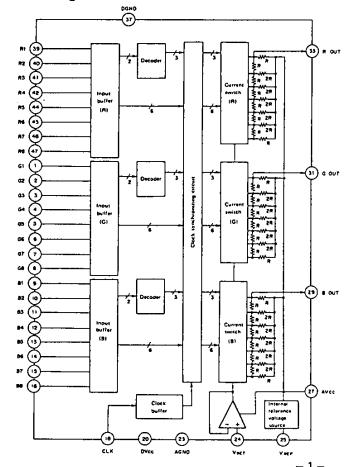

## **Block Diagram**

E89648-ST

| <ul> <li>Supply voltage</li> </ul>              | Vcc  | 0       | to 7    | V  |

|-------------------------------------------------|------|---------|---------|----|

| <ul> <li>Input voltage (digital)</li> </ul>     | Vı   | -0.3    | to Vcc  | V  |

|                                                 | Vclk | -0.3    | to Vcc  | V  |

| <ul> <li>Input voltage (VSET pin)</li> </ul>    | VSET | -0.3    | to Vcc  | V  |

| <ul> <li>Output voltage (analog)</li> </ul>     | Vout | Vcc-2.1 | to Vcc  | V  |

| <ul> <li>Output current (analog)</li> </ul>     | lout | -3      | to +10  | mΑ |

| (VREF pin)                                      | IREF | -5      | to 0    | mΑ |

| <ul> <li>Operating temperature</li> </ul>       | Topr | -20     | to +75  | °C |

| Storage temperature                             | Tstg | -55     | to +150 | °C |

| <ul> <li>Allowable power dissipation</li> </ul> | PD   |         | 0.7     | W  |

# **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul>     |       | AVcc, DVcc | 4.5   | to 5.5   | V  |

|----------------------------------------|-------|------------|-------|----------|----|

|                                        |       | AVcc-DVcc  | -0.2  | to +0.2  | ٧  |

|                                        |       | AGND-DGND  | -0.05 | to +0.05 | ٧  |

| • Digital input voltage H              | level | VIH, VCLKH | 2.0   | to DVcc  | ٧  |

| i.                                     | level | VIL, VCLKL | DGND  | to 0.8   | ٧  |

| <ul> <li>Vset input voltage</li> </ul> |       | VSET       | 0.7   | to 1.0   | V  |

| <ul> <li>VREF pin current</li> </ul>   |       | IREF       | -3    | to -0.4  | mΑ |

| <ul> <li>Clock pulse width</li> </ul>  |       | Tpw1       |       | 15       | ns |

|                                        |       | Tpw0       |       | 10       | ns |

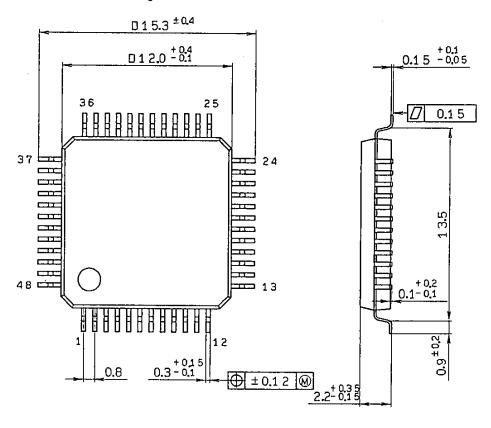

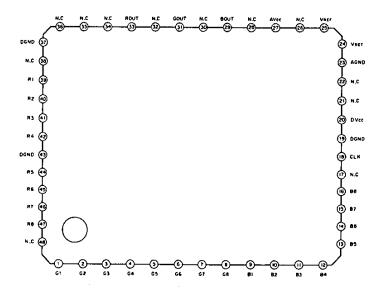

# Pin Configuration (Top View)

# Pin Description

| No.                             | Symbol                           | Equivalent circuit                       | Description                                                                                                                                                                                                     |

|---------------------------------|----------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39 to 42<br>44 to 47<br>1 to 16 | R1 to R8<br>G1 to G8<br>B1 to B8 | 39-42<br>44-47<br>1-16<br>37<br>DGND     | Digital input pin. From pins 39 to 42 and from 44 to 47 are for RED. R1 is MSB and R8 is LSB. From pins 1 to 8 are for GREEN. G1 is MSB and G8 is LSB. From pins 9 to 16 are for BLUE. B1 is MSB and B8 is LSB. |

| 18                              | CLK                              | 18 W J J J J J J J J J J J J J J J J J J | Clock input pin.                                                                                                                                                                                                |

| 20                              | DVcc                             |                                          | Digital Vcc.                                                                                                                                                                                                    |

| 17<br>21 to 22                  | NC                               |                                          | Vacant pin (non-connection)                                                                                                                                                                                     |

| 23                              | AGND                             |                                          | Analog GND.                                                                                                                                                                                                     |

| 24                              | Vset                             | AVC C (27) (24) (23) AGND                | Bias input pin.<br>Normally, apply 0.87V.<br>See "Note on use".                                                                                                                                                 |

| No.            | Symbol | Fauivalent circuit                   | Description                                                                                                          |

|----------------|--------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| INO.           | Зушиот | Equivalent circuit                   | Description                                                                                                          |

| 25             | Vref   | AVCC (27) 20P (23) AGND              | Internal reference voltage out-put pin 1.2V (typ) A pull-down resistance is necessary externally. See "Note on use". |

| 26             | NC     |                                      | Vacant pin (non-connection)                                                                                          |

| 27             | AVcc   |                                      | Analog Vcc                                                                                                           |

| 28             | NC     |                                      | Vacant pin but connect to AVcc*                                                                                      |

| 29             | BOUT   | AVCC<br>(27)<br>(29)<br>(23)<br>AGND | Analog output pin for BLUE.                                                                                          |

| 30             | NC     |                                      | Vacant pin but connect to AVcc*                                                                                      |

| 31             | GOUT   | AVCC  27  Ro  31  4  AGND            | Analog output pin for GREEN.                                                                                         |

| 32             | NC     | ···· ,                               | Vacant pin but connect to AVcc*                                                                                      |

| 33             | ROUT   | AVCC (27)  Ro (33)  AGND             | Analog output pin for RED.                                                                                           |

| 34 to 36       | NC     |                                      | Vacant pin but connect to AVcc*                                                                                      |

| 19<br>37<br>43 | DGND   |                                      | Digital GND                                                                                                          |

| 48             | NC     |                                      | Vacant pin (non-connection)                                                                                          |

<sup>\*</sup>Note) Pins 30, 32, 34 and 36 are vacant, but in order to reduce interference between the individual RGB outputs, connect them to AVcc.

## **Electrical Characteristics**

Ta=25°C, AVcc=DVcc=5.0V, AGND=DGND=0.0V

| ltem                                  |             | Symbol       | Test condition                            | Min.            | Тур. | Max.           | Unit         |      |

|---------------------------------------|-------------|--------------|-------------------------------------------|-----------------|------|----------------|--------------|------|

| Resolution                            |             | RSL          |                                           |                 | 8    |                | bit          |      |

| Monotony                              | •           |              | MNT                                       |                 |      | Guara-<br>ntee |              |      |

| Differential                          | linear      | ity error    | DLE                                       | VSET-AGND=0.87V | -0.5 |                | +0.5         | LSB  |

| Integral linearity error              |             | ILE          | R∟>10kΩ<br>F.S.=Full-scale                | -0.4            |      | +0.4           | % of<br>F.S. |      |

| Maximum c                             | onver       | sion speed   | fmax                                      |                 | 35   |                |              | MSPS |

| Full-scale of voltage*1               | utput       |              | Vors                                      | Vset-AGND=0.87V | 0.85 | 1.0            | 1.15         | Vp-p |

| RGB output voltage full-scale ratio*2 |             | FSR          | RL>10kΩ CL<20pF                           | 0               | 4    | 8              | %            |      |

| Output zero                           | offse       | et voltage   | Voffset                                   | t               | -40  | -6             | 0            | mV   |

| Output resis                          | tance       | •            | Ro                                        |                 | 270  | 340            | 420          | Ω    |

| Consumption current                   |             | lo           | VSET-AGND=0.87V<br>RL>10kΩ<br>IREF=-400μA | 54              | 72   | 90             | mA           |      |

|                                       | Н           | Upper 2 bits | lih(U)                                    | Vi=DVcc         |      | 1.2            | 20           | μΑ   |

| Digital data                          | level       | Lower 6 bits | lin(L)                                    | VI—DVCC         |      | 0.6            | 10           | μΑ   |

| input current                         | L           | Upper 2 bits | lit(U)                                    | VI=DGND         | -10  | 0              | 10           | μΑ   |

|                                       | level       | Lower 6 bits | ligg                                      | VI—DGIND        | -10  | 0              | 10           | μΑ   |

| H level                               |             | ICLKH        | VcLK=DVcc                                 |                 | 3    | 30             | μΑ           |      |

| Clock input current L level           |             | ICLKL        | Vclk=DGND                                 | -10             | 0    | 10             | μΑ           |      |

| VSET input current                    |             | ISET         | VSET-AGND=0.87V                           | -5              | -0.3 | 0              | μΑ           |      |

| Internal reference voltage            |             | VREF         | IREF=-400μA                               | 1.08            | 1.20 | 1.32           | V            |      |

| Set-up time                           | Set-up time |              | ts                                        |                 | 12   |                |              | ns   |

| Hold time                             |             | th           |                                           | 3               |      |                | ns           |      |

Note) \*1. AVcc-Vo

\*2. Maximum value among

$$100 \times \left| \frac{\text{Vofs(R)}}{\text{Vofs(G)}} - 1 \right|, 100 \times \left| \frac{\text{Vofs(G)}}{\text{Vofs(B)}} - 1 \right|, \text{ or } 100 \times \left| \frac{\text{Vofs(B)}}{\text{Vofs(R)}} - 1 \right|$$

# Input-corresponding table

| Input code | Output voltage   |

|------------|------------------|

| MSB LSB    |                  |

| 11111111   | Vcc+Voffset      |

| ,          | •                |

| · .        | •                |

|            | •                |

| 10000000   | Vcc+Voffset-0.5V |

| ,          | •                |

| •          | •                |

|            | •                |

| 00000000   | Vcc+Voffset-1.0V |

In case the output voltage full-scale is 1.00V. (1LSB=3.92 mV)

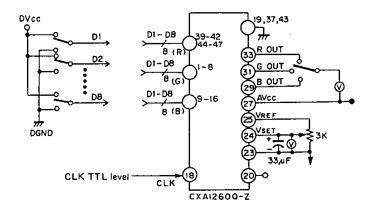

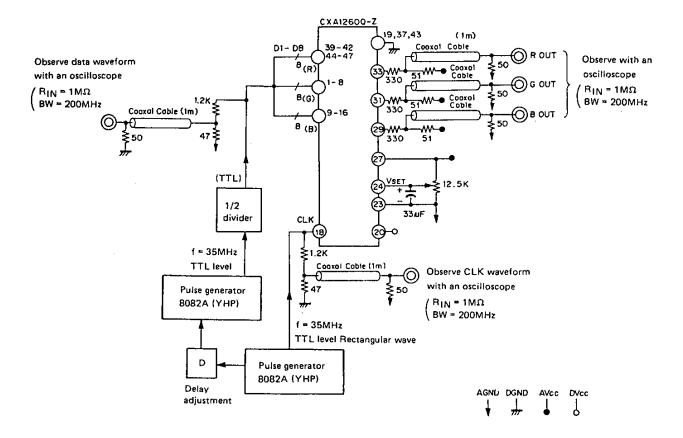

## **Electrical Characteristics Test Circuit**

# Differential linearity and integral linearity test circuits

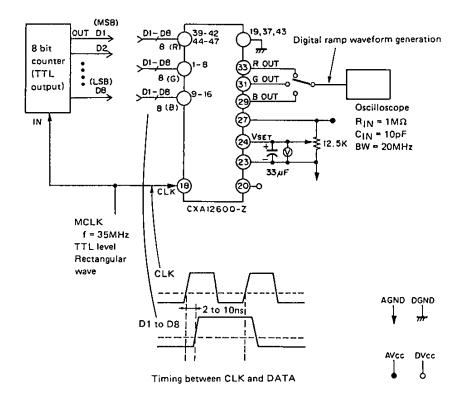

## Maximum conversion speed test circuit

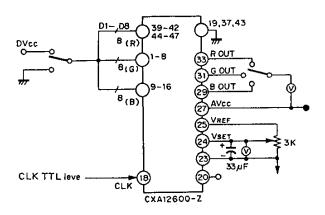

Output voltage full-scale precision, RGB output voltage full-scale ratio, and output zero offset voltage test circuits

Fig. 1

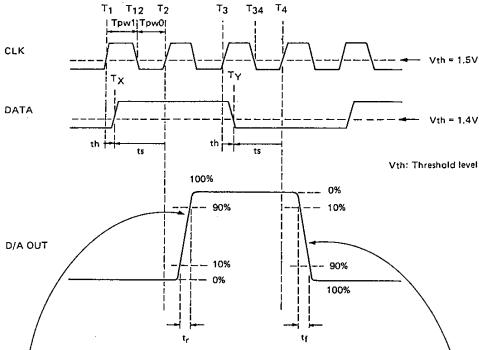

Set-up time, hold time, and rise and fall time test circuits

## Standard Circuit Design Data

Ta=25°C, AVcc=DVcc=5.0V, AGND=DGND=0.0V

| Item                       | Symbol | Measuring condition                                                            | Min. | Тур.       | Max. | Unit |

|----------------------------|--------|--------------------------------------------------------------------------------|------|------------|------|------|

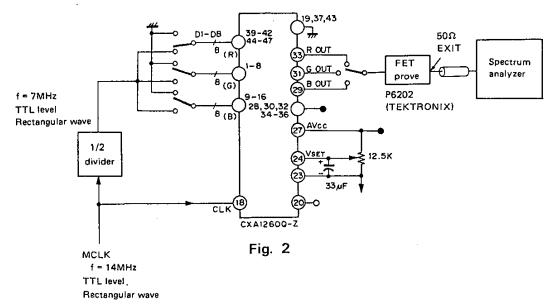

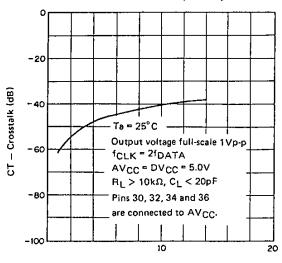

| Crosstalk among R, G and B | СТ     | D/A OUT: 1Vp-p RL>10kΩ CL<20pF fDATA=7MHz fCLK=14MHz See Fig.2                 |      | <b>-40</b> | -35  | dB   |

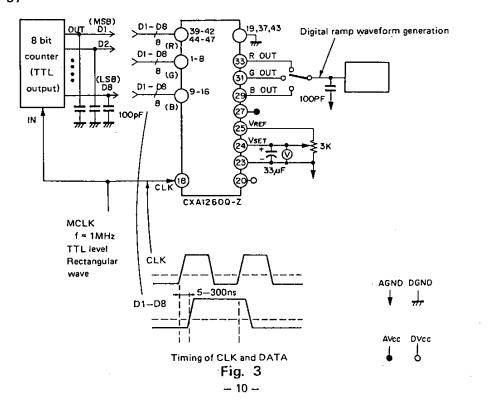

| Glitch energy              | GE     | Vset-AGND=0.87V<br>RL>10kΩ<br>fclk=1 MHz<br>Digital ramp output<br>See Fig.3*1 |      | 30         |      | pV-s |

| Rise time*2                | tr     | Vset-AGND=0.87V                                                                |      | 5.5        |      | ns   |

| Fall time <sup>*2</sup>    | tf     | See Fig. 1.                                                                    | •    | 5.0        |      | ns   |

| Settling time              | tset   |                                                                                |      | 16         |      | ns   |

Note) \*1. Observe the glitch which is generated when the digital input varies as follows:

$0\ 0\ 1\ 1\ 1\ 1\ 1\ 1\ -\ 0\ 1\ 0\ 0\ 0\ 0\ 0\ 0$

01111111 — 10000000

10111111 — 11000000

<sup>\*2.</sup> The time required for the D/A OUT to arrive at 90% of its final value from 10%.

## Standard Circuit Design Data Test Circuit

## Crosstalk among R, G and B test circuit

[Measuring method]

In case the measuring crosstalk of  $\mathsf{G} \to \mathsf{R}$

- 1 Apply the data to G only and measure the power of the frequency component of the data at R OUT.

- Apply the data to R only and measure the power of the frequency component of the data at R OUT.

- 3 Take the difference of the above two powers. The unit is in dB.

#### Glitch energy test circuit

## **Operation Description**

At the time t =  $T_X$ , the data of individual bits are switched and thereafter when the CLK becomes L  $\rightarrow$  H at t =  $T_2$ , the D/A OUT is varied synchronous with it. That is, the D/A OUT is synchronous with the rise of the CLK.

(In this case, fetching of the data is carried out at the fall of the CLK (at the time when  $t = T_{12}$ )).

At the time t = Ty, the data of individual bits are switched and thereafter when the CLK becomes L - H at t = T4, the D/A OUT is varied synchronous with it. That is, the D/A OUT is synchronous with the rise of the CLK.

(In this case, fetching of the data is carried out at the fall of the CLK (at the time when  $t=T_4$ )).

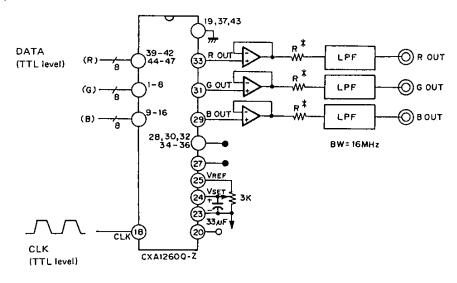

## **Application Circuit**

R\* is matching resistance for LPF

#### Note on Use

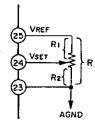

1. Setting of pin 24 (VSET)

The full-scale of the D/A output voltage changes by applying voltage to pin 24 (VSET). When load is connected to pin 25 (VREF), DC voltage of 1.2V is issued and the said voltage is dropped to 0.87V by resistance division.

When the 0.87V is applied to pin 24 (VSET), the D/A output of 1 Vp-p can be obtained. (Example of use)

Adjustment method

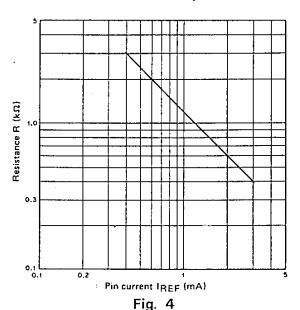

- 1) The resistance R is determined in accordance with the recommended operating condition of IREF (Current flowing through resistance R).

- See R vs. IREF of Fig. 4. The calculation expression is as follows: R=VREF/IREF

- 2) Adjust the volume so that the RGB output voltage full-scale becomes 1.0V. (At this point, it becomes R1:R2=2:5)

#### Resistance vs. VREF pin current

- 2. Phase relationship between data and clock

- In order to obtain the desired characteristics as a D/A converter, it is necessary to set the phase relationship correctly between the externally applied data and clock.

- Satisfy the standard of the set-up time (ts) and hold time (th) indicated in the electrical characteristics. As to the meaning of ts and th, see the timing chart.

- Moreover, the clock pulse width is desired to be as indicated in the recommended operating condition.

3. Regarding the load of D/A output pin

Receive the D/A output of the next stage with high impedance. In other words, perform so that it becomes as follows:

$RL>10 k\Omega$

CL<20 pF

The temperature characteristics indicated in the characteristics diagram has been measured under this condition.

However, when it is made to  $R \leq 10 \text{ k}\Omega$  the temperature characteristics may change considerably. In addition, when it is made to  $C \geq 20 \text{ pF}$ , the rise and fall of the D/A output become slow and will not operate at high speed.

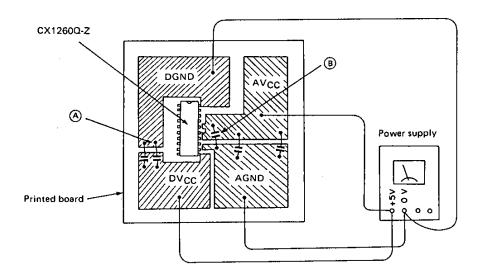

#### 4. Noise reduction measures

As the D/A output voltage is a minute voltage of approximately 4 mV per one step, ingenuity is required in reducing the noise entering from the outside of the IC as much as possible. Therefore use the items given below as reference.

- When mounting onto the printed board, allow as much space as possible to the ground surface and the Vcc surface on the board and reduce the parasitic inductance and resistance.

- It is desirable that the AGND and DGND be separated in the pattern on the board. It is similar

with AVcc and DVcc. As shown in the diagram below, for example, it is recommended that

the wiring to the electric supply of AGND and DGND as also AVcc and DVcc be conducted

separately, and then making AGND and DGND as also AVcc and DVcc in common right near

the power supply respectively.

- Insert in parallel a 47 μF tantalum capacitor and a 1000 pF ceramic capacitor between the Vcc surface on the printed board and the nearmost ground surface. ( A of diagram below). It is also desirable to insert the above between the Vcc surface near the pin of the IC and the ground surface. ( B of diagram below). They are bypass capacitors to prevent bad effects from occurring to the characteristics when the power supply voltage fluctuates due to the clock, etc.

- It is recommended to reduce noise which overlaps the D/A output by inserting a capacitor of over 0.1 μF between pin 23 (AGND) and pin 24 (VSET).

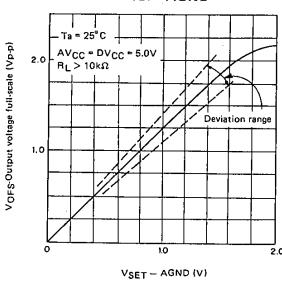

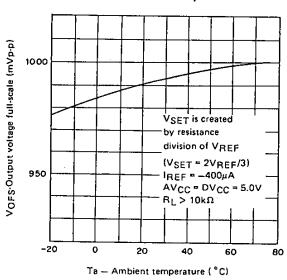

Output voltage full-scale vs. VSET—AGND

Output zero offset voltage vs. Vset—AGND

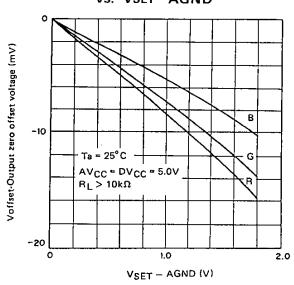

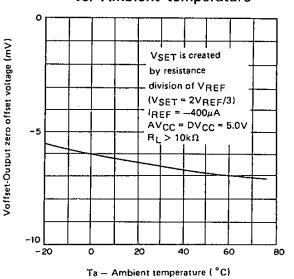

Output voltage full-scale vs. Ambient temperature

Output zero offset voltage vs. Ambient temperature

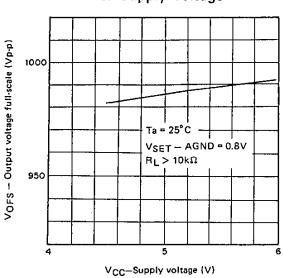

Output voltage full-scale vs. Supply voltage

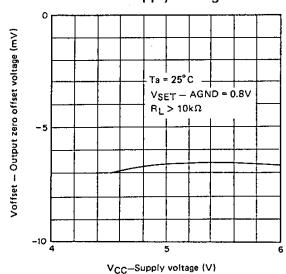

Output zero offset voltage vs. Supply voltage

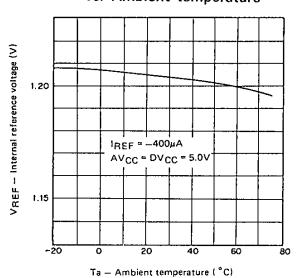

Internal reference voltage vs. Ambient temperature

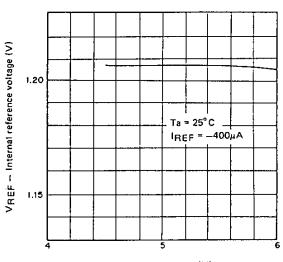

Internal reference voltage vs. Supply voltage

# Crosstalk among R, G and B vs. Data frequency

$f_{\mbox{\scriptsize DATA}}-{

m Data}$  frequency (MHz)

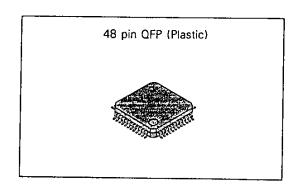

## Package Outline Unit: mm

48 pin QFP (Plastic) 0.6g