# **US Audio Multiplexing Decoder**

# For the availability of this product, please contact the sales office.

# Description

The CXA1734S is an IC designed as a decoder for the Zenith TV Multi-channel System also corresponds with I<sup>2</sup>C BUS. Functions include stereo demodulation, SAP (Separate Audio Program) demodulation and dbx noise reduction. Various kinds of filters are built in while adjustment and mode control are all executed through I<sup>2</sup>C BUS.

### **Features**

- Audio multiplexing decoder and dbx noise reduction decoder are all included in a single chip.

Almost any sort of signal processing is possible through this IC.

- All adjustments are possible through I<sup>2</sup>C BUS to allow for automatic adjustment.

- Various built-in filter circuits greatly reduce external parts.

### Standard I/O Level

- Input level

COMPIN (Pin 11) 245 mVrms

- Output level

LOUT (Pin 29) 490 mVrms ROUT (Pin 28) 490 mVrms

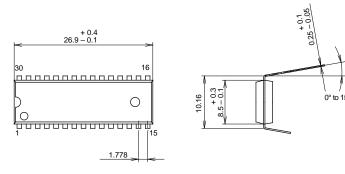

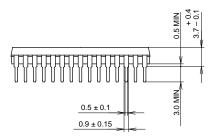

# 30 pin SDIP (Plastic)

### Absolute Maximum Ratings (Ta=25°C)

| <ul> <li>Supply voltage</li> </ul> | Vcc   | 11          | V   |

|------------------------------------|-------|-------------|-----|

| Operating temperature              | Topr  | -20 to +75  | ℃   |

| Storage temperature                | Tstg  | -65 to +150 | ℃   |

| • Allowable power dissipa          | ition |             |     |

|                                    | Dη    | 1 35        | ۱۸/ |

Range of Operating Supply Voltage  $9 \pm 0.5$  V

# **Applications**

TV, VCR and other decoding systems for US audio multiplexing TV broadcasting

### Structure

Bipolar silicon monolithic IC

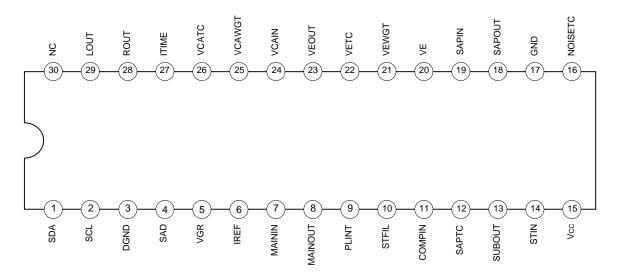

### Pin Configuration (Top View)

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

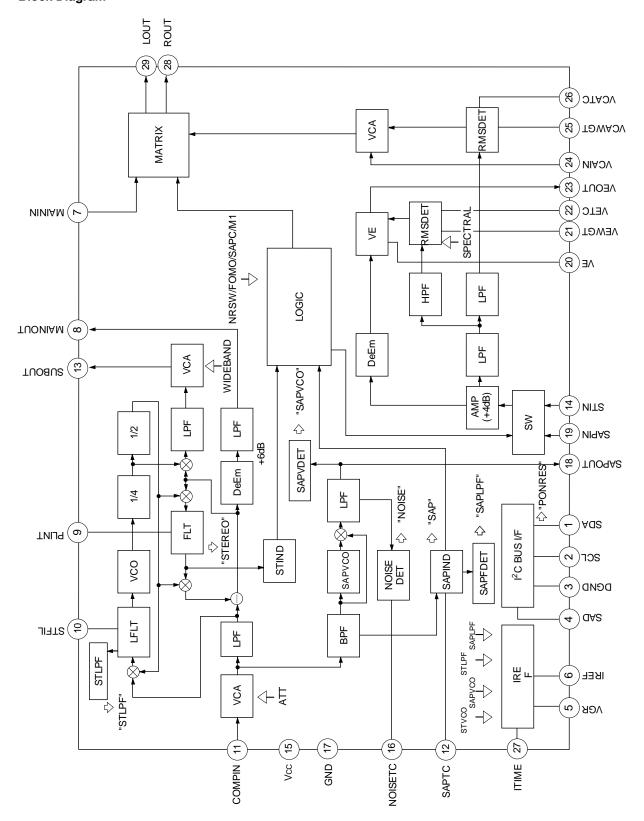

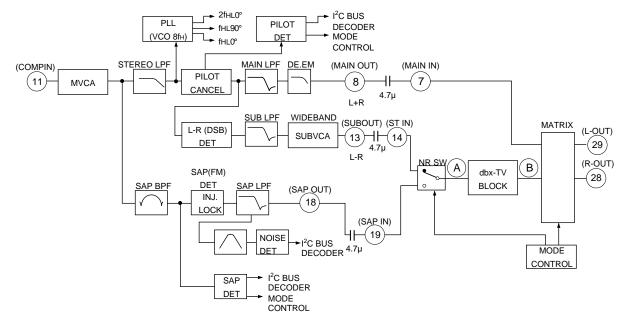

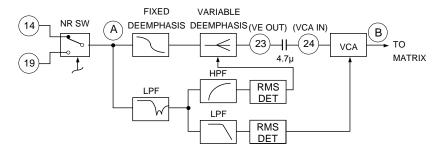

### **Block Diagram**

# **Pin Description**

(Ta = 25°C, V cc = 9 V)

| Pin | Symbol | Pin     | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                              |

|-----|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| No. | Symbol | voltage |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description                                                                                              |

| 1   | SDA    | _       | VCC ₹7.5k<br>↓ 35µ<br>↓ 35µ<br>2.1V<br>↓ 35µ<br>↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7/7 ↑ 7 | Serial data I/O pin. VIH > 3.0 V VIL < 1.5 V                                                             |

| 2   | SCL    | _       | Vcc<br>₹7.5k<br>↓ 35µ<br>2.1V<br>4k<br>7/// 7/// 7/// 7/// 7///                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Serial clock input pin. VIH > 3.0 V VIL < 1.5 V                                                          |

| 3   | DGND   | _       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital block GND.                                                                                       |

| 4   | SAD    | _       | Vcc → 2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Slave address control switch. The slave address is selected by changing the voltage applied to this pin. |

| 5   | VGR    | 1.3V    | 3k 147<br>11k \$\left\{ 9.7k \right\{ 19.4k \right\{ Vcc} \right\{ 1.3V \right\{ 11k \       | Band gap reference output pin. Connect a 10 µF capacitor between this pin and GND.                       |

| Pin<br>No. | Symbol  | Pin<br>voltage | Equivalent circuit                                                       | Description                                                                                                                                                                                           |

|------------|---------|----------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6          | IREF    | 1.3V           | 40k \$40k \$30k \$30k \$15k \$30k<br>×2  Vcc  Vcc  147  6  16k  777  777 | Set the filter and VCO reference current. The reference current is adjusted with the BUS DATA based on the current which flows to this pin. (Connect a 62 kΩ ±1%) resistor between this pin and GND.) |

| 7          | MAININ  | 4.0V           | Vcc                                                                      | Input the (L + R) signal from MAINOUT (Pin 8).                                                                                                                                                        |

| 8          | MAINOUT | 4.0V           | Vcc<br>×4<br>147<br>8<br>147<br>200µ ≸1k<br>////                         | (L + R) signal output pin.                                                                                                                                                                            |

| 9          | PLINT   | 6.3V           | 147<br>147<br>9<br>20k ≥ 20k<br>20k → ₹10k<br>26µ //// 50µ //// ///      | Pilot cancel circuit loop filter integrating pin. (Connect a 1 µF capacitor between this pin and GND.)                                                                                                |

| Pin<br>No. | Symbol | Pin<br>voltage | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Description                                                                                                         |

|------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 10         | STFIL  | 5.3V           | 3k 3k 3k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Stereo block PLL loop filter integrating pin.                                                                       |

| 11         | COMPIN | 4.0V           | Vcc<br>50k 147<br>11<br>30k 20k 30<br>30k 30k 30<br>30k 30k 30<br>30k 30k 30<br>30k 30k 30<br>30k 30k 30<br>30k 30k 30k 30<br>30k 30k 30k 30k 30k 30k 30k 30k 30k 30k | Audio multiplexing signal input pin.                                                                                |

| 12         | SAPTC  | 4.5V           | 3k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Set the time constant for the SAP carrier detection circuit. (Connect a 4.7 µF capacitor between this pin and GND.) |

| 13         | SUBOUT | 4.0V           | 2k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (L - R) signal output pin.                                                                                          |

| Pin<br>No. | Symbol  | Pin<br>voltage | Equivalent circuit                                                                               | Description                                                                                                                                      |

|------------|---------|----------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 14         | STIN    | 4.0V           | ≥ 23k ≥ 23k<br>11.7k                                                                             | Input the (L - R) signal from SUBOUT (Pin 13).                                                                                                   |

| 19         | SAPIN   | 4.0V           | 147 147 19<br>47k 347k 47k 47 19                                                                 | Input the (SAP) signal from SAPOUT (Pin 18).                                                                                                     |

| 15         | Vcc     | _              | (15)                                                                                             | Supply voltage pin.                                                                                                                              |

| 16         | NOISETC | 3.0V           | Vcc<br>\$8k<br>\$3.3k<br>\$1k<br>\$2k<br>\$7/7<br>\$4k<br>\$7/7<br>\$4v<br>\$4v<br>\$16<br>\$7/7 | Set the time constant for the noise detection circuit. (Connect a 4.7 $\mu$ F capacitor and a 200 k $\Omega$ resistor between this pin and GND.) |

| 17         | GND     | _              | 17) 7/1/                                                                                         | Analog block GND.                                                                                                                                |

| 18         | SAPOUT  | 4.0V           | 5P<br>500<br>500<br>7.4k<br>147<br>18<br>24k<br>4k<br>7/7/↓ 10μ<br>7/7/↓ 50μ////                 | SAP FM detector output pin.                                                                                                                      |

| 20         | VE      | 4.0V           | 20 7.5k                                                                                          | Variable de-emphasis integrating pin. (Connect a 2700 pF capacitor and a 3.3 k $\Omega$ resistor in series between this pin and GND.)            |

| Pin<br>No. | Symbol | Pin<br>voltage | Equivalent circuit                          | Description                                                                                                                                                                                                                       |

|------------|--------|----------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21         | VEWGT  | 4.0V           | 21                                          | Weight the variable deemphasis control effective value detection circuit. (Connect a 0.047 $\mu F$ capacitor and a 3 $k\Omega$ resistor in series between this pin and GND.)                                                      |

| 22         | VETC   | 1.7V           | Vcc<br>×4 ×4 ×4 22<br>×4 ×4 ×4 7.5μ 777 777 | Determine the restoration time constant of the variable de-emphasis control effective value detection circuit. The specified restoration time constant can be obtained by connecting a 3.3 µF capacitor between this pin and GND. |

| 23         | VEOUT  | 4.0V           | Vcc<br>500 ₹ 10k                            | Variable de-emphasis output pin. (Connect a 4.7 µF non-polar capacitor between Pins 23 and 24.)                                                                                                                                   |

| 24         | VCAIN  | 4.0V           | Vcc                                         | VCA input pin. Input the variable de- emphasis output signal from Pin 23 via a coupling capacitor.                                                                                                                                |

| Pin<br>No. | Symbol | Pin<br>voltage | Equivalent circuit                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|--------|----------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25         | VCAWGT | 4.0V           | 2.9V <sub>2</sub> 36k                                                | Weight the VCA control effective value detection circuit. (Connect a 1 $\mu$ F capacitor and a 3.9 $k\Omega$ resistor in series between this pin and GND.)                                                                                                                                                                                                                                   |

| 26         | VCATC  | 1.7V           | Vcc<br>×4<br>×4<br>×4<br>×4<br>×4<br>×4<br>×4<br>×6<br>×7.5µ 777 777 | Determine the restoration time constant of the VCA control effective value detection circuit.  The specified restoration time constant can be obtained by connecting a 10 µF capacitor between this pin and GND.                                                                                                                                                                             |

| 27         | ITIME  | 1.3V           | 2.6V 2.6V 30p 1.8k 27 777 777 777                                    | Set the reference current for the effective value detection timing current. The reference current is adjusted with the BUS DATA "SPECTRAL" based on the current which flows to this pin. The timing current determines the restoration time constant of the detection circuit and the variable de-emphasis characteristics. Connect a 43 k $\Omega$ (±1%) resistor between this pin and GND. |

| Pin<br>No. | Symbol | Pin<br>voltage | Equivalent circuit                             | Description               |

|------------|--------|----------------|------------------------------------------------|---------------------------|

| 28         | ROUT   |                | Vcc                                            | Right channel output pin. |

| 29         | LOUT   | 4.0V           | 28 500 3p 7/// 7/// 7/// 7/// 7/// 7/// 7/// 7 | Left channel output pin.  |

| 30         | NC     | _              | 30                                             | _                         |

| stics   |

|---------|

| acteris |

| Chara   |

| trical  |

| Elec    |

COMPIN input level SUB (L-R) =245mVrms (Pre-Emphasis: OFF) SUB (L-R) =49mVrms (dbx-TV: OFF)

Complete SUB (L-R) =49mVrms

Complete SUB (L-R) =49mVrms

Complete SUB (L-R) =49mVrms

fH=15.734kHz

|            | :                                     |         |      |       |                           | Conditions | Suc                                                      |      |       |      | :        |

|------------|---------------------------------------|---------|------|-------|---------------------------|------------|----------------------------------------------------------|------|-------|------|----------|

|            | Item                                  | Symbol  | Mode | Input | Input signal              | Output     | Others                                                   | MIn. | l yp. | Мах. | Onit     |

| J.         | Current consumption                   | cc      |      | I     |                           | 1          |                                                          | 22   | 32    | 42   | mA       |

| ž          | Main output level                     | Vmain   | Mono | 11    | MAIN 1k 100%<br>Pre-em ON | 28         | Using 15 KHz LPF                                         | 440  | 490   | 540  | mVrms    |

| ದ ಕ        | De-emphasis frequency characteristics | FCdeem  | Mono | 11    | MAIN 5k 30%<br>Pre-em ON  | 28<br>29   |                                                          | -1.2 | 0     | 1.0  | Ę        |

| ≥ੋਂ 5      | Main LPF frequency characteristics    | FCmain  | Mono | 11    | MAIN 12k 30%<br>Pre-em ON | 28<br>29   |                                                          | -3.0 | -1.0  | 1.0  | <b>a</b> |

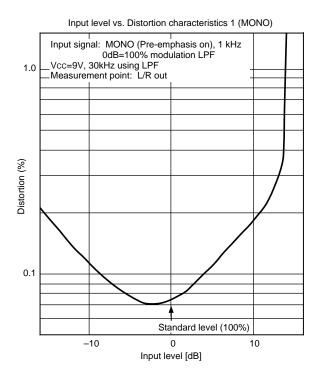

| ≥          | Main distortion                       | THDm    | Mono | 1     | MAIN 1k 100%<br>Pre-em ON | 28<br>29   | Using 15 kHz LPF                                         | I    | 0.1   | 0.5  | ò        |

| ≥ °        | Main overload distortion              | THDmmax | Mono | 1     | MAIN 1k 200%<br>Pre-em ON | 28<br>29   | Using 15 kHz LPF                                         | I    | 0.15  | 0.5  | %        |

| ≥          | Mono S/N                              | SNmain  | Mono | 11    | NO Signal                 | 28<br>29   | Using 15 kHz LPF Compared with the TEST2 output level    | 61   | 69    | I    | dВ       |

| တ          | Sub output level                      | Asub    | ST   | 11    | SUB 1k 100%<br>NR-OFF     | 13         | Using 15 kHz LPF                                         | 150  | 190   | 230  | mVrms    |

| ഗ മ        | Sub LPF frequency characteristics     | FCsub   | ST   | 11    | SUB 12k 30%<br>NR-OFF     | 13         |                                                          | -3.0 | -0.5  | 1.0  | ф        |

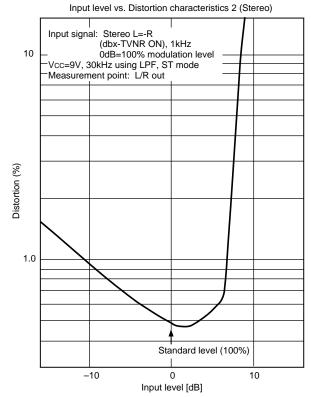

| ဟ          | Sub distortion                        | THDsub  | ST   | 1     | SUB 1k 100%<br>NR-OFF     | 13         | Using 15 kHz LPF                                         | I    | 0.1   | 1.0  | ò        |

| <b>ω</b> - | Sub overload distortion               | THDsmax | ST   | 11    | SUB 1k 200%<br>NR-OFF     | 13         | Using 15 kHz LPF                                         | I    | 0.5   | 2.0  | %        |

| တ          | Sub S/N                               | SNsub   | ST   | 11    | fH 0dB<br>(49mVrms)       | 13         | Using 15 kHz LPF<br>Compared with the TEST8 output level | 56   | 64    | I    | dB       |

| S          | Sub pilot leak                        | PCsub   | ST   | 11    | fн 0dB<br>(49mVrms)       | 13         | Using fH BPF                                             | I    | 1.0   | 7.0  | mVrms    |

| S          | ST on level                           | THst    | ST   | 11    | Ŧ                         | I          | 0dB=49mVrms                                              | -8.0 | -6.0  | 4.0  | 9        |

| S          | ST on/off hysteresis                  | HYst    | ST   | 11    | fн                        | I          | 0dB=49mVrms                                              | 3.5  | 0.9   | 8.5  | <u>a</u> |

| 2  |                                   | S, mbol |      |       |                         | Conditions | NS .                                                     | 7    | É              | 7074 | ::<br>-  |

|----|-----------------------------------|---------|------|-------|-------------------------|------------|----------------------------------------------------------|------|----------------|------|----------|

| 2  |                                   | Symbol  | Mode | Input | Input signal            | Output     | Others                                                   | E    | ı yp.   ıvlax. | Max. | <u> </u> |

| 16 | ST separation 1                   | STsep1  | ST   | 7     | ST 300Hz<br>30%, NR-ON  | 28<br>29   | L→R<br>R→L                                               | 23   | 35             |      | ģ        |

| 17 | ST separation 2                   | STsep2  | ST   | -     | ST 3KHz<br>30%, NR-ON   | 28         | L→R<br>R→L                                               | 23   | 35             | 1    | 9<br>8   |

| 18 | SAP output level                  | Vsap    | SAP  | 1     | SAP 1k 100%<br>NR-OFF   | 18         | Using 15kHz LPF                                          | 150  | 190            | 230  | mVrms    |

| 19 | SAP LPF frequency characteristics | FCsap   | SAP  | 1     | SAP 10k 30%<br>NR-OFF   | 18         |                                                          | -3.0 | 0              | 2.5  | ф        |

| 20 | SAP distortion                    | THDsap  | SAP  | 7     | SAP 1k 100%<br>NR-OFF   | 18         | Using 15kHz LPF                                          | I    | 2.5            | 0.9  | %        |

| 21 | SAP S/N                           | SNsap   | SAP  | 7     | SAP Carrier<br>147mVrms | 18         | Using 15kHz LPF<br>Compared with the TEST18 output level | 46   | 56             | I    |          |

| 22 | SAP on level                      | THsap   | SAP  | 1     | SAP Carrier             |            | 0dB=147mVrms                                             | -12  | 6-             | -6.5 | ВВ       |

| 23 | SAP on/off hysteresis             | HYsap   | SAP  | 11    | SAP Carrier             |            | 0dB=147mVrms                                             | 2.5  | 4              | 5.5  |          |

I<sup>2</sup>C BUS block items (SDA, SCL)

| No. | Item                                                    | Symbol  | Min. | Тур. | Max. | Unit |

|-----|---------------------------------------------------------|---------|------|------|------|------|

| 1   | High level input voltage                                | VIH     | 3.0  |      | 5.0  | V    |

| 2   | Low level input voltage                                 | VIL     | 0    | _    | 1.5  | V    |

| 3   | High level input current                                | lін     | _    | _    | 10   |      |

| 4   | Low level input current                                 | lıL     | _    |      | 10   | μΑ   |

| 5   | Low level output voltage SDA (Pin 1) during 3 mA inflow | Vol     | 0    | _    | 0.4  | V    |

| 6   | Max. inflow current                                     | lol     | 3    |      | _    | mA   |

| 7   | Input capacitance                                       | Cı      |      | _    | 10   | pF   |

| 8   | Max. clock frequency                                    | fSCL    | 0    | _    | 100  | kHz  |

| 9   | Minimum waiting time for data change                    | tBUF    | 4.7  | _    | _    |      |

| 10  | Minimum waiting time for start of data transfer         | tHD:STA | 4.0  | _    | _    |      |

| 11  | Low level clock pulse width                             | tLOW    | 4.7  | _    | _    | ше   |

| 12  | High level clock pulse width                            | tHIGH   | 4.0  | _    | _    | μs   |

| 13  | Minimum waiting time for start preparation              | tsu:sta | 4.7  | _    |      |      |

| 14  | Min. data hold time                                     | thd:dat | 0    | _    | _    |      |

| 15  | Min. data preparation time                              | tsu:dat | 250  | _    | _    | ns   |

| 16  | Rise time                                               | tR      |      | _    | 1    | μs   |

| 17  | Fall time                                               | tF      | _    | _    | 300  | ns   |

| 18  | Minimum waiting time for stop preparation               | tsu:sto | 4.7  |      | _    | μs   |

I²C BUS load conditions: Pull-up resistor 4 k $\Omega$  (Connect to +5 V) Load capacity 200 pF (Connect to GND)

# I<sup>2</sup>C BUS Control Signal

SNOS CXE1134S

Downloaded from  $\underline{Elcodis.com}$  electronic components distributor

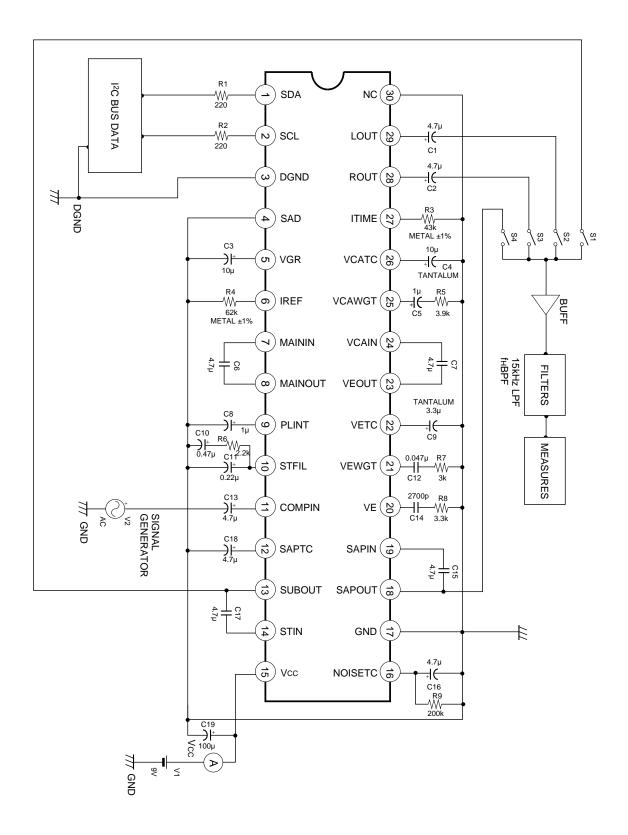

# Electrical Characteristics Measurement Circuit

# I<sup>2</sup>C BUS Register Data Standard Setting Values

| Register | Number of | Classification | Standard | Contents           | Setting value when electrical |

|----------|-----------|----------------|----------|--------------------|-------------------------------|

| register | bits      | Classification | setting  | Contents           | characteristics are measured  |

| ATT      | 4         | Α              | 9        |                    |                               |

| STVCO    | 6         | Α              | 1F       |                    |                               |

| SAPVCO   | 4         | Α              | 8        |                    |                               |

| SAPLPF   | 4         | Α              | 8        | Center point       | Adjustment point              |

| STLPF    | 6         | Α              | 1F       |                    |                               |

| SPECTRAL | 6         | Α              | 1F       |                    |                               |

| WIDEBAND | 6         | Α              | 1F       |                    |                               |

| TEST-DA  | 1         | Т              | 0        | Normal mode        |                               |

| TEST1    | 1         | Т              | 0        | Normal mode        |                               |

| NRSW     | 1         | U              | _        | According to the   |                               |

| FOMO     | 1         | U              | _        | mode control table |                               |

| M1       | 1         | U              | 1        | Mute OFF           |                               |

| SAPC     | 1         | S              | _        | Fixed by the set   |                               |

| ATTSW    | 1         | S              | _        | specifications     |                               |

Classification A: Adjustment

U: User controlS: Proper to set

T: Test

# **List of Adjustment Contents**

|   | Adjustment<br>item              | Adjustment data | Input pin          | Input signal                | Measurement item                       | Adjustment contents                                            | Test mode setting |

|---|---------------------------------|-----------------|--------------------|-----------------------------|----------------------------------------|----------------------------------------------------------------|-------------------|

| 1 | MAIN VCA                        | ATT             | COMPIN<br>(Pin 11) | 100Hz<br>245mVrms           | LOUT output<br>level                   | Adjust as close to 490 mVrms as possible                       | -                 |

| 2 | ST VCO                          | STVCO           | None               | None                        | ROUT output frequency                  | Adjust as close to 62.936 kHz as possible                      | TEST-DA=1         |

| 3 | SAP VCO                         | SAPVCO          | COMPIN<br>(Pin 11) | 5fH<br>(78.67k)<br>147mVrms | STA7<br>(SAPVCO1)<br>STA8<br>(SAPVCO2) | Adjust to the center of the SAPVCO1 = 0, SAPVCO2 = 1 condition |                   |

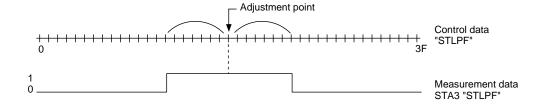

| 4 | ST & dbx<br>FILTER              | STLPF           | COMPIN<br>(Pin 11) | 9.4kHz<br>600mVrms          | STA3<br>(STLPF)                        | Adjust to the center of the STLPF = 1 condition                | TEST1=1           |

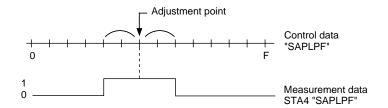

| 5 | SAP<br>FILTER                   | SAPLPF          | COMPIN<br>(Pin 11) | 88kHz<br>120mVrms           | STA4<br>(SAPLPF)                       | Adjust to the center of the SAPLPF = 1 condition               | TEST1=1           |

| 6 | Low frequency<br>ST separation  | WIDEBAND        | COMPIN<br>(Pin 11) | ST-L 30%<br>300Hz           | ROUT output level                      | Minimize the output level                                      |                   |

| 0 | High frequency<br>ST separation | SPECTRAL        | COMPIN<br>(Pin 11) | ST-L 30%<br>3kHz            | ROUT output level                      | Minimize the output level                                      |                   |

### **Adjustment Method**

- 1 ATT adjustment

- 1. TEST BIT is set to "TEST1 = 0" and "TEST-DA = 0".

- 2. Input a 100 Hz, 245 mVrms sine wave signal to COMPIN and monitor the LOUT output level. Then, adjust the "ATT" data for ATT adjustment so that LOUT output goes to the standard value.

- Adjustment range: ±30%

Adjustment bits: 4 bits

### 2 Stereo VCO adjustment

- 1. TEST BIT is set to "TEST1 = 0" and "TEST-DA = 1".

- 2. Monitor the ROUT output (4 fH free run) frequency in a no input state, and adjust "STVCO" adjustment data so that this frequency is as close to 4fH (62.936 kHz) as possible.

- 3. Adjustment range: ±20%Adjustment bits: 6 bits

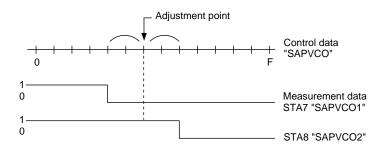

- 3 SAPVCO adjustment

- 1. TEST BIT is set to "TEST1 = 0" and "TEST-DA = 0".

- 2. Input a 5fH (SAP carrier, 78.67 kHz), 147 mVrms sine wave signal to COMPIN. While monitoring the STATUS FLAG (STA7, STA8) condition, adjust "SAPVCO" adjustment data.

- 3. Adjustment range: ±20%Adjustment bits: 4 bits

Align SAPVCO with the center of the STA7 = 0 and STA8 = 1 (adjustment OK) condition range.

- 4 Stereo block dbx filter adjustment

- 1. TEST BIT is set to "TEST1 = 1" and "TEST-DA = 0".

- 2. Input a 9.4 kHz, 600 mVrms sine wave signal to COMPIN. While monitoring the STATUS FLAG (STA3) condition, adjust the "STLPF" adjustment data.

- 3. Adjustment range: ±20%Adjustment bits: 6 bits

Align STLPF with the center of the STA3 = 1 (adjustment OK) condition range.

- 5 SAP block filter adjustment

- 1. TEST BIT is set to "TEST1 = 1" and "TEST-DA = 0".

2. Input a 88 kHz, 120 mVrms sine wave signal to COMPIN. While monitoring the STATUS FLAG (STA4) condition, vary and adjust the "SAPLPF" adjustment data.

3. Adjustment range: ±20%Adjustment bits: 4 bits

Align SAPLPF with the center of the STA4 = 1 (adjustment OK) condition range.

### 6 Separation adjustment

- 1. TEST BIT is set to "TEST1 = 0" and "TEST-DA = 0".

- 2. Set the unit to stereo mode and input the left channel only signal (modulation factor 30%, frequency 300 Hz) to COMPIN. At this time, adjust the "WIDEBAND" adjustment data to reduce ROUT output to the minimum.

- 3. Next, set the frequency only of the input signal to 3 kHz and adjust the "SPECTRAL" adjustment data to reduce ROUT output to the minimum.

- 4. Then, the adjustments in 2 and 3 above are performed to optimize the separation.

- 5. "WIDEBAND" "SPECTRAL"

Adjustment range: ±30% Adjustment range: ±15% Adjustment bits: 6 bits Adjustment bits: 6 bits

### **Description of Operation**

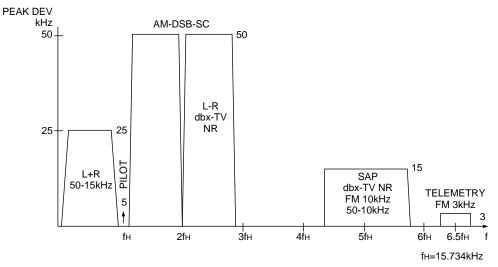

The US audio multiplexing system possesses the base band spectrum shown in Fig. 1.

Fig. 1. Base band spectrum

Fig. 2. Overall block diagram (See Fig. 3 for the dbx-TV block)

Fig. 3. dbx-TV block

### (1) L + R (MAIN)

After the audio multiplexing signal input from COMPIN (Pin 11) passes through MVCA, the SAP signal and telemetry signal are suppressed by STEREO LPF. Next, the pilot signals are canceled. Finally, the L - R signal and SAP signal are removed by MAIN LPF, and frequency characteristics are flattened (de-emphasized) and input to the matrix.

### (2) L - R (SUB)

The L - R signal follows the same course as L + R before the pilot signal is canceled. L - R has no carrier signal, as it is a suppressed-carrier double-sideband amplitude modulated signal (DSB-AM modulated). For this reason, the pilot signal is used to regenerate the carrier signal (quasi-sine wave) to be used for the demodulation of the L - R signal. In the last stage, the residual high frequency components are removed by SUB LPF and the L - R signal is input to the dbx-TV block via the NRSW circuit after passing through SUBVCA.

### (3) SAP

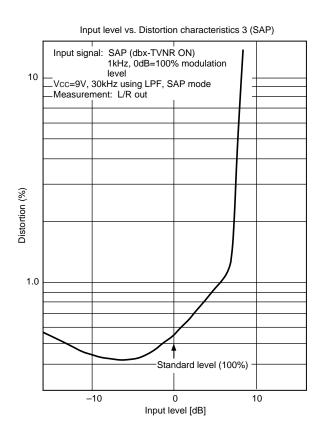

SAP is an FM signal using 5fH as a carrier as shown in the Fig.1. First, the SAP signal only is extracted using SAP BPF. Then, this is subjected to FM detection. Finally, residual high frequency components are removed and frequency characteristics flattened using SAP LPF, and the SAP signal is input to the dbx-TV block via the NRSW circuit. When there is no SAP signal, the Pin 18 output is soft muted.

### (4) Mode discrimination

Stereo discrimination is performed by detecting the pilot signal amplitude. SAP discrimination is performed by detecting the 5fH carrier amplitude. NOISE discrimination is performed by detecting the noise near 25 kHz after FM detection.

### (5) dbx-TV block

Either the SAP signal or L - R signal input respectively from ST IN (Pin 14) or SAP IN (Pin 19) is selected by the mode control and input to the dbx-TV block.

The input signal then passes through the fixed de-emphasis circuit and is applied to the variable de-emphasis circuit. The signal output from the variable de-emphasis circuit passes through an external capacitor and is applied to VCA (voltage control amplifier). Finally, the VCA output is converted from a current to a voltage using an operational amplifier and then input to the matrix.

The variable de-emphasis circuit transmittance and VCA gain are respectively controlled by each of effective value detection circuits. Each of the effective value detection circuits passes the input signal through a predetermined filter for weighting before the effective value of the weighted signal is detected to provide the control signal.

### (6) Others

"MVCA" is a VCA which adjusts the input signal level to the standard level of this IC. In addition, the input signal enters the decoder without passing through MVCA by setting to ATTSW = 1.

The signals (L + R, L - R, SAP) input to "MATRIX" are selected according to the BUS data and whether there is ST or SAP discrimination, and any one of the ST-L, ST-R, MONO or SAP signals is output to LOUT and ROUT.

"Bias" supplies the reference voltage and reference current to the other blocks. The currents flowing to the resistors connecting IREF (Pin 6) and ITIME (Pin 27) with GND become the reference current.

# **Register Specifications**

# Slave address

| SAD pin | SLAVE RECEIVER | SLAVE TRANSMITTER |  |  |

|---------|----------------|-------------------|--|--|

| GND     | 80H            | 81H               |  |  |

| Vcc     | 8AH            | 8BH               |  |  |

# Register table

| SUB AD | DRESS | DATA  |            |                                      |                                        |             |          |      |      |  |

|--------|-------|-------|------------|--------------------------------------|----------------------------------------|-------------|----------|------|------|--|

| MSB    | LSB   | BIT7  | BIT6       | BIT5 BIT4 BIT3 BIT2 BIT1             |                                        |             |          | BIT1 | BIT0 |  |

| ****(  | 0000  | *     | ATTSW      | TEST-DA TEST1 ATT [4] INPUT LEVEL ac |                                        |             |          | ndj  |      |  |

| ****(  | 0001  |       | *          |                                      | ST\                                    | /CO [6] STI | EREO VCO | adj  |      |  |

| ****(  | 010   | (SAP) | /CO [4] SA | P VCO adj)                           | P VCO adj) (SAPLPF [4] SAP FILTER adj) |             |          |      |      |  |

| ****(  | 0011  |       | *          | STLPF [6] ST FILTER adj              |                                        |             |          |      |      |  |

| ****(  | 0100  |       | *          |                                      | SPECTRAL [6]                           |             |          |      |      |  |

| ****(  | )101  |       | *          | WIDEBAND [6]                         |                                        |             | 6]       |      |      |  |

| ****(  | )110  |       | *          |                                      |                                        | NRSW        | FOMO     | SAPC | M1   |  |

\*: Don't Care

# **Status Register**

When TEST1 = 0

| STA1              | STA2   | STA3 | STA4  | STA5 | STA6 | STA7     | STA8     |

|-------------------|--------|------|-------|------|------|----------|----------|

| BIT7              | BIT6   | BIT5 | BIT4  | BIT3 | BIT2 | BIT1     | BIT0     |

| POWER<br>ON RESET | STEREO | SAP  | NOISE | _    | _    | SAP VCO1 | SAP VCO2 |

# When TEST1 = 1

| STA1              | STA2   | STA3  | STA4   | STA5 | STA6 | STA7 | STA8 |

|-------------------|--------|-------|--------|------|------|------|------|

| BIT7              | BIT6   | BIT5  | BIT4   | BIT3 | BIT2 | BIT1 | BIT0 |

| POWER<br>ON RESET | STEREO | STLPF | SAPLPF | _    | _    | _    | _    |

# **Description of Registers**

# Control registers

| Register | Number of bits | Classifi-<br>cation* | Contents                                                                 |  |  |

|----------|----------------|----------------------|--------------------------------------------------------------------------|--|--|

| ATT      | 4              | Α                    | Input level adjustment                                                   |  |  |

| STVCO    | 6              | Α                    | STEREO VCO free running frequency adjustment                             |  |  |

| SAPVCO   | 4              | Α                    | SAP VCO free running frequency adjustment                                |  |  |

| SAPLPF   | 4              | Α                    | SAP filter adjustment                                                    |  |  |

| STLPF    | 6              | Α                    | STEREO and dbx filter adjustment                                         |  |  |

| SPECTRAL | 6              | Α                    | Adjustment of stereo separation (3 kHz)                                  |  |  |

| WIDEBAND | 6              | А                    | Adjustment of stereo separation (300 Hz)                                 |  |  |

| TECT DA  | 4              | _                    | Turn to DAC test mode and STVCO adjustment mode by means of              |  |  |

| TEST-DA  |                | Т                    | TEST-DA = 1.                                                             |  |  |

| TEST1    | 1              | Т                    | Turn to test mode by means of TEST = 1. (Adjustment of STLPF and SAPLPF) |  |  |

| NRSW     | 1              | U                    | Selection of the output signal (STEREO mode , SAP mode)                  |  |  |

| E0140    | 4              |                      | Turn to forced MONO by means of FOMO = 1. (LOUT only is                  |  |  |

| FOMO     | 1              | U                    | MONO during SAP output.)                                                 |  |  |

| M1       | 1              | U                    | Selection of mute ON/OFF (0: mute ON, 1: mute OFF)                       |  |  |

| CARC     | 4              | C                    | Selection of SAP mode or L + R mode according to the presence of         |  |  |

| SAPC     | 1              | S                    | SAP broadcasting                                                         |  |  |

| ATTSW    | 1              | S                    | Turns the input stage MVCA off when ATTSW = 1.                           |  |  |

\*Classification

U: User control

A: AdjustmentS: Proper to set

T: Test

# Status registers

| Register | Number of bits | Contents                                              |               |

|----------|----------------|-------------------------------------------------------|---------------|

| PONRES   | 1              | POWER ON RESET detection;                             | 1: RESET      |

| STEREO   | 1              | Stereo discrimination of the input signal;            | 1: Stereo     |

| SAP      | 1              | SAP discrimination of the input signal;               | 1: SAP        |

| NOISE    | 1              | Noise level discrimination of the input signal mode;  | 1: Noise      |

| STLPF    | 1              | Status of STEREO filter adjustment;                   | 1: OK range   |

| SAPLPF   | 1              | Status of SAP filter adjustment;                      | 1: OK range   |

| SAPVCO1  | 1              | Status 1 of SAP VCO free running frequency adjustment | ; 0: OK range |

| SAPVCO2  | 1              | Status 2 of SAP VCO free running frequency adjustment | ; 1: OK range |

### **Description of Control Registers**

ATT (4): Adjust the signal level input to COMPIN (Pin 11) to the reference level (245 mVrms).

Variable range of the input signal: 245 mVrms -5.0 dB to +3.0 dB

0 = Level min. F = Level max.

STVCO (6): Adjust STEREO VCO free running frequency (fo).

Variable range: fo ±20%

0 = Free running frequency min.3F = Free running frequency max.

SAPVCO (4): Adjust SAPVCO free running frequency (fo).

Variable range: fo ±20%

0 = Free running frequency min.F = Free running frequency max.

SAPLPF (4): Adjust the filter fo of the SAP block.

Variable range: fo ±20%

0 = Frequency min.F = Frequency max.

STLPF (6): Adjust the filter fo of the ST and dbx blocks.

Variable range: fo ±20%

0 = Frequency min.3F = Frequency max.

SPECTRAL (6): Perform high frequency (fs = 3 kHz) separation adjustment.

0 = Level max. 3F = Level min.

WIDEBAND (6): Perform low frequency (fs = 300 Hz) separation adjustment.

0 = Level min. 3F = Level max.

TEST1 (1): Set filter adjustment mode.

0 = Normal mode

1 = STLPF (STA3) and SAPLPF (STA4) adjustment mode In addition, the following outputs are present at Pins 28 and 29.

LOUT (Pin 29): SAP BPF OUT ROUT (Pin 28): NR BPF OUT

TEST-DA (1): Set DAC output test mode and STVCO adjustment mode.

0 = Normal mode

1 = DAC output test mode and STVCO adjustment mode

LOUT (Pin 29): DA control DC level

ROUT (Pin 28): STEREO VCO oscillation frequency (4 fH)

NRSW (1) Select stereo mode or SAP mode

0 = Stereo mode 1 = SAP mode

FOMO (1): Select forced MONO mode

0 = Normal mode

1 = Forced MONO mode

SAPC (1): Select the SAP signal output mode

When there is no SAP signal, the conditions for selecting SAP output are selected by SAPC.

0 = L + R output is selected 1 = SAP output is selected

ATTSW (1) MAIN VCA switch

0 = Normal mode

1 = MAIN VCA is passed.

M1 (1) Mute the LOUT and ROUT output

0 = Mute ON 1 = Mute OFF

# **Description of Mode Control**

Priority ranking: TEST-DA > TEST1 > M1 > (NRSW & FOMO & SAPC)

| Mode control | SAPC=0                                                                                           | )                                                                         | SAPC=1                                    |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

|              | "Select dbx input and LOU                                                                        | T & ROUT output"                                                          | "Select dbx input and LOUT & ROUT output" |  |  |  |  |  |

|              | Conditions: FOMO = 0                                                                             |                                                                           | Conditions: FOMO = 0                      |  |  |  |  |  |

|              | NRSW = 0 (MONO or ST o                                                                           | output)                                                                   | NRSW = 0 (MONO or ST output)              |  |  |  |  |  |

|              | During ST input:                                                                                 | LOUT : L,<br>ROUT : R                                                     | As on the left                            |  |  |  |  |  |

|              | During other input:                                                                              | LOUT : L + R,<br>ROUT : L + R                                             |                                           |  |  |  |  |  |

| NRSW         |                                                                                                  |                                                                           | NRSW = 1 (SAP output)                     |  |  |  |  |  |

|              | NRSW = 1 (SAP output)                                                                            |                                                                           | Regardless of the presence of SAP         |  |  |  |  |  |

|              | When there is "SAP" duri                                                                         | ng SAP                                                                    | discrimination,                           |  |  |  |  |  |

|              | discrimination                                                                                   |                                                                           | dbx input: "SAP"                          |  |  |  |  |  |

|              | LOUT: SAP, RO                                                                                    | UT: SAP                                                                   | LOUT: SAP, ROUT: SAP                      |  |  |  |  |  |

|              | • When there is "No SAP",                                                                        | output is the same                                                        | However, when there is no SAP, SAPLPF     |  |  |  |  |  |

|              | as when NRSW = 0.                                                                                |                                                                           | output is soft muted (–7 dB)              |  |  |  |  |  |

|              |                                                                                                  | "Forced                                                                   | MONO"                                     |  |  |  |  |  |

|              | FOMO = 1                                                                                         |                                                                           |                                           |  |  |  |  |  |

| FOMO         | During SAP output: LOUT: L + R, ROUT: SAP                                                        |                                                                           |                                           |  |  |  |  |  |

|              | During SAF output: LOUT: L + R, ROUT: SAF     During ST or MONO output: LOUT: L + R, ROUT: L + R |                                                                           |                                           |  |  |  |  |  |

|              | -                                                                                                | Change the selection conditions for "MONO or ST output" and "SAP output". |                                           |  |  |  |  |  |

|              | SAPC = 0: Switch to SAP output when there is SAP discrimination.                                 |                                                                           |                                           |  |  |  |  |  |

| SAPC         | Do not switch to SAP output when there is no SAP discrimination.                                 |                                                                           |                                           |  |  |  |  |  |

|              | SAPC = 1: Switch to SAP output regardless of whether there is SAP                                |                                                                           |                                           |  |  |  |  |  |

|              | discrimi                                                                                         |                                                                           |                                           |  |  |  |  |  |

|              |                                                                                                  | "MU                                                                       | TE"                                       |  |  |  |  |  |

| M1           | M1 = 0                                                                                           |                                                                           |                                           |  |  |  |  |  |

|              | Output is muted.                                                                                 |                                                                           |                                           |  |  |  |  |  |

|              |                                                                                                  | "TES                                                                      | ST1"                                      |  |  |  |  |  |

|              | TEST1 = 1                                                                                        |                                                                           |                                           |  |  |  |  |  |

| TEST1        | Return adjustment data                                                                           | with STATUS REGI                                                          | STER as an adjustment mode.               |  |  |  |  |  |

| 12011        | In addition, outputs are as follows.                                                             |                                                                           |                                           |  |  |  |  |  |

|              | LOUT: SAP BPF OUT                                                                                |                                                                           |                                           |  |  |  |  |  |

|              | ROUT: NR BPF OUT                                                                                 |                                                                           |                                           |  |  |  |  |  |

|              |                                                                                                  | "TES                                                                      | Γ-DA"                                     |  |  |  |  |  |

|              | TEST-DA = 1                                                                                      |                                                                           |                                           |  |  |  |  |  |

| TEST-DA      | Used to TEST of D/A.                                                                             |                                                                           |                                           |  |  |  |  |  |

|              | LOUT: D/A output                                                                                 |                                                                           |                                           |  |  |  |  |  |

|              | ROUT: STVCO oscilla                                                                              | ation frequency (4 f                                                      | 1)                                        |  |  |  |  |  |

Mode Control No. 1 (SAPC = 1)

| lanut signal made    | Мс | de detect | ion   | M    | lode contr | ol   | dbx   | Out   | put   |

|----------------------|----|-----------|-------|------|------------|------|-------|-------|-------|

| Input signal mode    | ST | SAP       | NOISE | NRSW | FOMO       | SAPC | input | Lch   | Rch   |

|                      | 0  | 0         | 0     | 0    | *          | 1    | MUTE  | L+R   | L+R   |

|                      | 0  | 0         | 0     | 1    | 0          | 1    | SAP   | SAP   | SAP   |

| MONO <sup>1)</sup>   | 0  | 0         | 0     | 1    | 1          | 1    | SAP   | L+R   | SAP   |

| MONO                 | 0  | *         | 1     | 0    | *          | 1    | MUTE  | L+R   | L+R   |

|                      | 0  | *         | 1     | 1    | 0          | 1    | (SAP) | (SAP) | (SAP) |

|                      | 0  | *         | 1     | 1    | 1          | 1    | (SAP) | L+R   | (SAP) |

|                      | 1  | 0         | *     | 0    | 0          | 1    | L-R   | L     | R     |

|                      | 1  | 0         | *     | 0    | 1          | 1    | MUTE  | L+R   | L+R   |

|                      | 1  | 1         | 1     | 0    | 0          | 1    | L-R   | L     | R     |

| STEREO <sup>1)</sup> | 1  | 1         | 1     | 0    | 1          | 1    | MUTE  | L+R   | L+R   |

| STEREO               | 1  | 0         | 0     | 1    | 0          | 1    | SAP   | SAP   | SAP   |

|                      | 1  | 0         | 0     | 1    | 1          | 1    | SAP   | L+R   | SAP   |

|                      | 1  | *         | 1     | 1    | 0          | 1    | (SAP) | (SAP) | (SAP) |

|                      | 1  | *         | 1     | 1    | 1          | 1    | (SAP) | L+R   | (SAP) |

|                      | 0  | 1         | *     | 0    | 0          | 1    | MUTE  | L+R   | L+R   |

|                      | 0  | 1         | *     | 0    | 1          | 1    | MUTE  | L+R   | L+R   |

| MONO & SAP           | 0  | 1         | 0     | 1    | 0          | 1    | SAP   | SAP   | SAP   |

| IVIONO & SAP         | 0  | 1         | 0     | 1    | 1          | 1    | SAP   | L+R   | SAP   |

|                      | 0  | 1         | 1     | 1    | 0          | 1    | (SAP) | (SAP) | (SAP) |

|                      | 0  | 1         | 1     | 1    | 1          | 1    | (SAP) | L+R   | (SAP) |

|                      | 1  | 1         | *     | 0    | 0          | 1    | L-R   | L     | R     |

|                      | 1  | 1         | *     | 0    | 1          | 1    | MUTE  | L+R   | L+R   |

| STEREO & SAP         | 1  | 1         | 0     | 1    | 0          | 1    | SAP   | SAP   | SAP   |

| SIEREU & SAP         | 1  | 1         | 0     | 1    | 1          | 1    | SAP   | L+R   | SAP   |

|                      | 1  | 1         | 1     | 1    | 0          | 1    | (SAP) | (SAP) | (SAP) |

|                      | 1  | 1         | 1     | 1    | 1          | 1    | (SAP) | L+R   | (SAP) |

### Note)

(SAP) : The SAPOUT output signal is soft muted (approximately -7 dB). The signal is soft muted when NOISE = 1.

- \* : Don't care.

- 1) : SAP or NOISE discrimination may be made during MONO or STEREO input when the noise is inputted in the weak electric field.

"NOISE" status rises earlier than "SAP" status when the amount of noise is increased to COMPIN.

Mode Control No. 2 (SAPC = 0)

| Innut signal made    | Mc | de detect | ion   | M    | lode contr | ol   | dbx   | Out   | put   |

|----------------------|----|-----------|-------|------|------------|------|-------|-------|-------|

| Input signal mode    | ST | SAP       | NOISE | NRSW | FOMO       | SAPC | input | Lch   | Rch   |

|                      | 0  | 0         | *     | *    | *          | 0    | MUTE  | L+R   | L+R   |

| MONO <sup>1)</sup>   | 0  | 1         | 1     | 0    | 0          | 0    | MUTE  | L+R   | L+R   |

| MONO                 | 0  | 1         | 1     | 0    | 1          | 0    | MUTE  | L+R   | L+R   |

|                      | 0  | 1         | 1     | 1    | 0          | 0    | (SAP) | (SAP) | (SAP) |

|                      | 0  | 1         | 1     | 1    | 1          | 0    | (SAP) | L+R   | (SAP) |

|                      | 1  | 0         | *     | 0    | 0          | 0    | L-R   | L     | R     |

|                      | 1  | 0         | *     | 0    | 1          | 0    | MUTE  | L+R   | L+R   |

|                      | 1  | 0         | *     | 1    | 0          | 0    | L-R   | L     | R     |

| STEREO <sup>1)</sup> | 1  | 0         | *     | 1    | 1          | 0    | MUTE  | L+R   | L+R   |

| STEREO               | 1  | 1         | 1     | 0    | 0          | 0    | L-R   | L     | R     |

|                      | 1  | 1         | 1     | 0    | 1          | 0    | MUTE  | L+R   | L+R   |

|                      | 1  | 1         | 1     | 1    | 0          | 0    | (SAP) | (SAP) | (SAP) |

|                      | 1  | 1         | 1     | 1    | 1          | 0    | (SAP) | L+R   | (SAP) |

|                      | 0  | 1         | 0     | 0    | 0          | 0    | MUTE  | L+R   | L+R   |

|                      | 0  | 1         | 0     | 0    | 1          | 0    | MUTE  | L+R   | L+R   |

|                      | 0  | 1         | 0     | 1    | 0          | 0    | SAP   | SAP   | SAP   |

| MONO & SAP           | 0  | 1         | 0     | 1    | 1          | 0    | SAP   | L+R   | SAP   |

| MONO & SAP           | 0  | 1         | 1     | 0    | 0          | 0    | MUTE  | L+R   | L+R   |

|                      | 0  | 1         | 1     | 0    | 1          | 0    | MUTE  | L+R   | L+R   |

|                      | 0  | 1         | 1     | 1    | 0          | 0    | MUTE  | L+R   | L+R   |

|                      | 0  | 1         | 1     | 1    | 1          | 0    | MUTE  | L+R   | L+R   |

|                      | 1  | 1         | 0     | 0    | 0          | 0    | L-R   | L     | R     |

|                      | 1  | 1         | 0     | 0    | 1          | 0    | MUTE  | L+R   | L+R   |

|                      | 1  | 1         | 0     | 1    | 0          | 0    | SAP   | SAP   | SAP   |

| STEREO & SAP         | 1  | 1         | 0     | 1    | 1          | 0    | SAP   | L+R   | SAP   |

| STEREU & SAP         | 1  | 1         | 1     | 0    | 0          | 0    | L-R   | L     | R     |

|                      | 1  | 1         | 1     | 0    | 1          | 0    | MUTE  | L+R   | L+R   |

|                      | 1  | 1         | 1     | 1    | 0          | 0    | L-R   | L     | R     |

|                      | 1  | 1         | 1     | 1    | 1          | 0    | MUTE  | L+R   | L+R   |

### Note)

(SAP) : The SAPOUT output signal is soft muted (approximately -7 dB). The signal is soft muted when NOISE = 1.

- \* : Don't care.

- 1) : SAP or NOISE discrimination may be made during MONO or STEREO input when the noise is inputted in the weak electric field.

"NOISE" status rises earlier than "SAP" status when the amount of noise is increased to COMPIN.

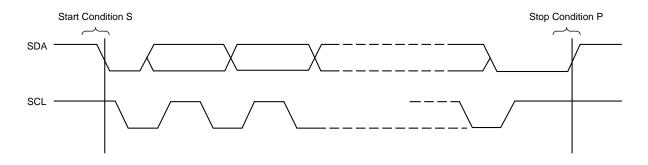

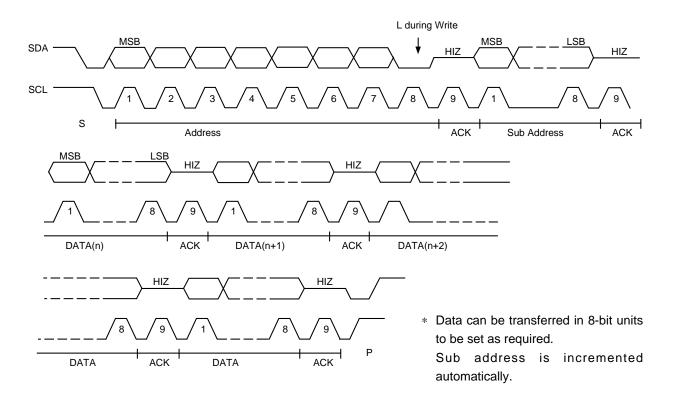

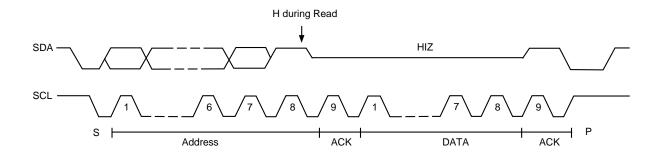

### I<sup>2</sup>C BUS Signal

There are two I<sup>2</sup>C signals, SDA (Serial DATA) and SCL (Serial CLOCK) signal. SDA is a bidirectional signal.

• Accordingly there are 3 values outputs, H, L and HIZ.

• I<sup>2</sup>C transfer begins with Start Condition and ends with Stop Condition.

• I<sup>2</sup>C data Write (Write from I2C controller to the IC)

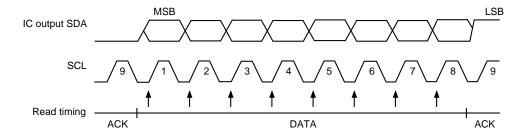

• I<sup>2</sup>C data Read (Read from the IC to I<sup>2</sup>C controller)

# • Read timing

\* Data Read is performed during SCL rise.

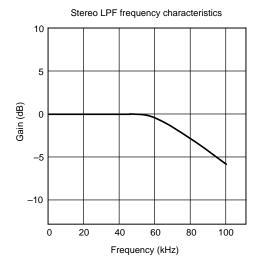

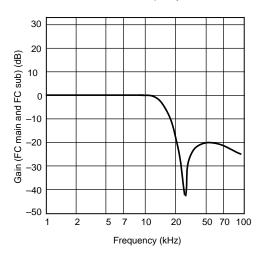

Main LPF and Sub LPF frequency characteristics

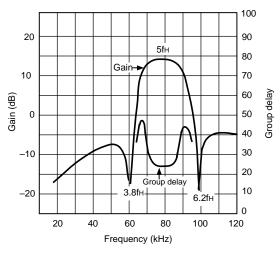

SAP frequency characteristics and group delay

# Package Outline Unit: mm

# 30PIN SDIP (PLASTIC)

# PACKAGE STRUCTURE

| SONY CODE  | SDIP-30P-01    |

|------------|----------------|

| EIAJ CODE  | SDIP030-P-0400 |

| JEDEC CODE |                |

| MOLDING COMPOUND | EPOXY / PHENOL RESIN        |

|------------------|-----------------------------|

| LEAD TREATMENT   | SOLDER/PALLADIUM<br>PLATING |

| LEAD MATERIAL    | COPPER ALLOY                |

| PACKAGE WEIGHT   | 1.8g                        |