# Digital RGB Encoder IC for Video CD and CD-G

### Overview

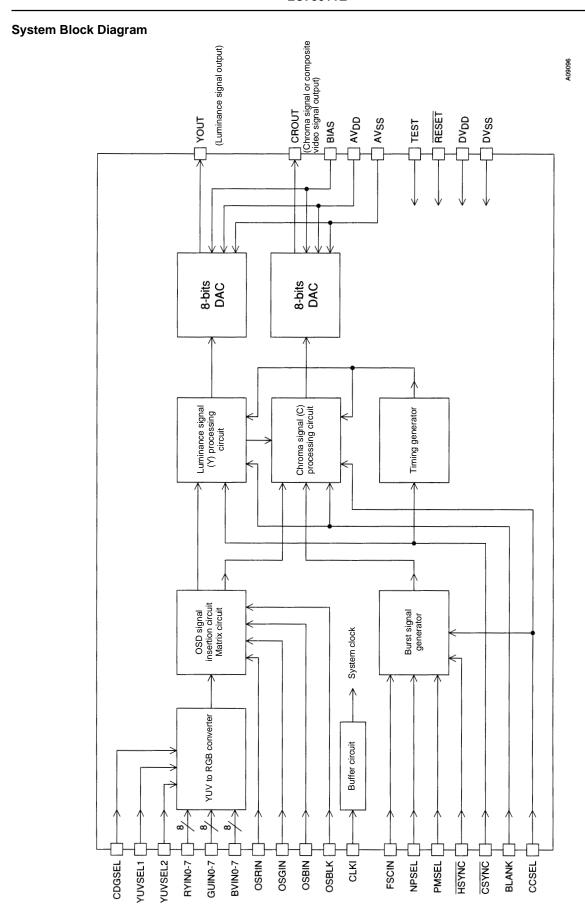

The LC78011E is a CMOS IC that integrates a digital RGB encoder and a synchronizing signal generation circuit on a single chip. A video CD or CD-G system can be formed using the LC78011E together with an MPEG video decoder or a CD-G decoder, respectively.

### **Features**

- · System structure

- Each system (Video CD or CD-G system) formed with an additional chip: MPEG decoder or CD-G decoder chip.

- · Video outputs

- 8-bit D/A converter outputs: 2 channels

- The LC78011E supports the following two video signal output formats:

- Luminance signal (Y) and chroma signal (C) outputs Composite video signal (C • VIDEO) output (Only one D/A converter channel operates in this mode.)

- · System clock

- External 4fsc clock

NTSC mode: 14.31818 MHz PAL mode: 17.734475 MHz PAL-M mode: 14.30244596 MHz

- External subcarrier input

- An external fsc clock is input and used for subcarrier synchronization timing.

- Video data input

- The LC78011E supports the following four input formats:

R, G, and B: 8 bits each Y, U, and V: 8 bits each

Y and UV: 8 bits each (The UV input is a

multiplexed input)

R, G, and B: 4 bits each (In CD-G input support

- · OSD input support

- R, G, and B + BLK 4-bit inputs (color support)

(BLK is an OSD display switching timing signal.)

- · External synchronizing signal input

- Horizontal synchronizing signal, composite synchronizing signal, and composite blanking signal inputs: HSYNC, CSYNC, and BLANK.

- Video signal formats

- The LC78011E supports the NTSC, PAL, and PAL-M formats.

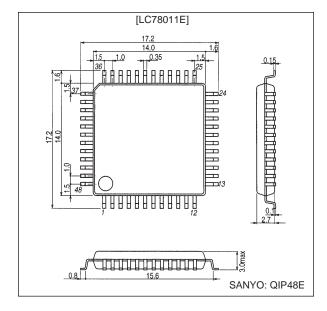

# **Package Dimensions**

unit: mm

### 3156-QIP48E

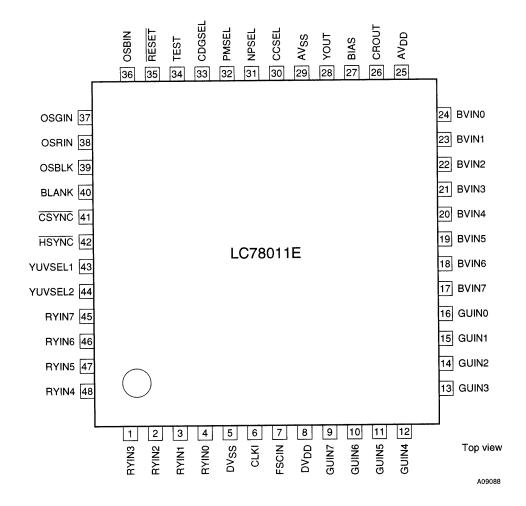

## **Pin Assignment**

## **Pin Functions**

| Pin No. | Symbol           | I/O | Polarity  |                                                                                |              | Func         | tion                                  |                       |

|---------|------------------|-----|-----------|--------------------------------------------------------------------------------|--------------|--------------|---------------------------------------|-----------------------|

| 1       | RYIN3            | IN  | Positive  | R/Y data input                                                                 |              |              |                                       | resistor is built in. |

| 2       | RYIN2            | IN  | Positive  | R/Y data input                                                                 |              |              | A pull-down                           | resistor is built in. |

| 3       | RYIN1            | IN  | Positive  | R/Y data input                                                                 |              |              | A pull-down                           | resistor is built in. |

| 4       | RYIN0            | IN  | Positive  | R/Y data input (LSB)                                                           |              |              | A pull-down                           | resistor is built in. |

| 5       | DV <sub>SS</sub> | _   | _         | Digital system ground                                                          |              |              |                                       |                       |

| 6       | CLKI             | IN  | _         | 4fsc clock input                                                               |              |              | A feedback                            | resistor is built in. |

| 7       | FSCIN            | IN  | _         | fsc clock input                                                                |              |              | A feedback                            | resistor is built in. |

| 8       | DV <sub>DD</sub> | _   | _         | Digital system power supply                                                    |              |              |                                       |                       |

| 9       | GUIN7            | IN  | Positive  | G/U data input (MSB)                                                           |              |              | A pull-down                           | resistor is built in. |

| 10      | GUIN6            | IN  | Positive  | G/U data input                                                                 |              |              | A pull-down                           | resistor is built in. |

| 11      | GUIN5            | IN  | Positive  | G/U data input                                                                 |              |              | A pull-down                           | resistor is built in. |

| 12      | GUIN4            | IN  | Positive  | G/U data input                                                                 |              |              | A pull-down                           | resistor is built in. |

| 13      | GUIN3            | IN  | Positive  | G/U data input                                                                 |              |              | A pull-down                           | resistor is built in. |

| 14      | GUIN2            | IN  | Positive  | G/U data input                                                                 |              |              | A pull-down                           | resistor is built in. |

| 15      | GUIN1            | IN  | Positive  | G/U data input                                                                 |              |              | A pull-down                           | resistor is built in. |

| 16      | GUIN0            | IN  | Positive  | G/U data input (LSB)                                                           |              |              | A pull-down                           | resistor is built in. |

| 17      | BVIN7            | IN  | Positive  | B/V/UV data input (MSB)                                                        |              |              | A pull-down                           | resistor is built in. |

| 18      | BVIN6            | IN  | Positive  | B/V/UV data input                                                              |              |              | A pull-down                           | resistor is built in. |

| 19      | BVIN5            | IN  | Positive  | B/V/UV data input                                                              |              |              | A pull-down                           | resistor is built in. |

| 20      | BVIN4            | IN  | Positive  | B/V/UV data input                                                              |              |              | A pull-down                           | resistor is built in. |

| 21      | BVIN3            | IN  | Positive  | B/V/UV data input                                                              |              |              | A pull-down                           | resistor is built in. |

| 22      | BVIN2            | IN  | Positive  | B/V/UV data input                                                              |              |              | A pull-down                           | resistor is built in. |

| 23      | BVIN1            | IN  | Positive  | B/V/UV data input A pull-down resistor is built in.                            |              |              |                                       |                       |

| 24      | BVIN0            | IN  | Positive  | B/V/UV data input (LSB)                                                        |              |              | A pull-down                           | resistor is built in. |

| 25      | AV <sub>DD</sub> | _   | _         | Analog system power supply (F                                                  | or the D/A   | converters   | i.) (+5 V)                            |                       |

| 26      | CROUT            | OUT | _         | Chroma signal/composite video                                                  | signal out   | put (8-bit D | /A converter output)                  |                       |

| 27      | BIAS             | OUT | _         | Ripple rejection capacitor conn                                                | ection (Use  | a 10 μF ca   | apacitor.)                            |                       |

| 28      | YOUT             | OUT | _         | Luminance signal output (8-bit                                                 | D/A conver   | ter output)  |                                       |                       |

| 29      | AV <sub>SS</sub> | _   | _         | Analog system ground (For the                                                  | D/A conve    | rters.)      |                                       |                       |

| 30      | CCSEL            | IN  | Positive  | D/A converter output control sig                                               | gnal input ( | Low: YC si   | gnal output, High: Composite video si | gnal output)          |

| 31      | NPSEL            | IN  | Positive  | Signal format selection input                                                  |              |              |                                       |                       |

|         |                  |     |           |                                                                                | NPSEL        | PMSEL        | D/A converter output signal mode      |                       |

|         |                  |     |           |                                                                                | 0            | 0            | NTSC                                  |                       |

| 32      | PMSEL            | IN  | Positive  |                                                                                | 1            | 0            | PAL                                   |                       |

| 02      |                  |     |           |                                                                                | 0            | 1            | PAL-M                                 |                       |

|         |                  |     |           |                                                                                | 1            | 1            | <ul><li>(Illegal setting)</li></ul>   |                       |

|         |                  |     |           |                                                                                |              |              |                                       |                       |

| 33      | CDGSEL           | IN  | Negative  | Video CD/CD-G selection input                                                  | t (Low: CD-  | G, High: Vi  | ideo-CD)                              |                       |

| 33      | CDGGEE           | 114 | ivegative | (The input digital data can be selected to be either 4-bit or 8-bit data.)     |              |              |                                       |                       |

| 34      | TEST             | IN  | Positive  | Test mode selection input (This pin must be tied low during normal operation.) |              |              |                                       |                       |

| 35      | RESET            | IN  | Negative  | Reset signal input                                                             |              |              |                                       |                       |

| 36      | OSBIN            | IN  | Positive  | OSD signal (B) input                                                           |              |              |                                       |                       |

| 37      | OSGIN            | IN  | Positive  | OSD signal (G) input                                                           |              |              |                                       |                       |

| 38      | OSRIN            | IN  | Positive  | OSD signal (R) input                                                           |              |              |                                       |                       |

| 39      | OSBLK            | IN  | Positive  | OSD switching signal input (Th                                                 | e OSD blar   | nking signa  | l input)                              |                       |

Continued on next page.

Continued from preceding page.

| Pin No. | Symbol  | I/O         | Polarity      |                     | Function                                         |              |                                        |                         |  |

|---------|---------|-------------|---------------|---------------------|--------------------------------------------------|--------------|----------------------------------------|-------------------------|--|

| 40      | BLANK   | IN          | Positive      | Composite blanking  | emposite blanking signal input (HBLANK + VBLANK) |              |                                        |                         |  |

| 41      | CSYNC   | IN          | Negative      | Composite synchro   | nizing signa                                     | al input (HS | YNC + VSYNC)                           |                         |  |

| 42      | HSYNC   | IN          | Negative      | Horizontal synchron | nizing signa                                     | l input (HS) | (NC)                                   |                         |  |

| 43      | YUVSEL1 | IN          | Positive      | Signal input setup  |                                                  |              |                                        |                         |  |

|         |         |             |               |                     | YUVSEL1                                          | YUVSEL2      | Video signal input signal mode         |                         |  |

|         |         |             |               |                     | 0                                                | 0            | RYIN = R in, GUIN = G in, BVIN = B in  |                         |  |

| 44      | YUVSEL2 | IN          | Positive      |                     | 1                                                | 0            | RYIN = Y in, GUIN = U in, BVIN = V in  |                         |  |

| "       | TOVOLLE | TOVOLLE IIV | iiv i ositive |                     | 0                                                | 1            | RYIN = Y in, GUIN = none, BVIN = UV in |                         |  |

|         |         |             |               |                     | 1                                                | 1            | — (Illegal setting)                    |                         |  |

|         |         |             |               |                     |                                                  |              |                                        |                         |  |

| 45      | RYIN7   | IN          | Positive      | R/Y data input (MS  | B)                                               |              | A pull-dow                             | n resistor is built in. |  |

| 46      | RYIN6   | IN          | Positive      | R/Y data input      | R/Y data input A pull-down resistor is built in. |              |                                        |                         |  |

| 47      | RYIN5   | IN          | Positive      | R/Y data input      | R/Y data input A pull-down resistor is built in. |              |                                        |                         |  |

| 48      | RYIN4   | IN          | Positive      | R/Y data input      |                                                  |              | A pull-dow                             | n resistor is built in. |  |

- Notes:1. The voltage applied as the digital system power supply voltage must not exceed the voltage applied as the analog system power supply voltage.

2. Unused input pins must be tied high or low. If the OSD inputs are not used, tie OSBLK (pin 39) low.

3. Note that the clock input frequencies (CLKI: pin 6, and FSCIN: pin 7) depend on the TV subcarrier pull-in range. The CLKI input clock and the FSCIN clock must be synchronized.

## **Specifications**

## **Absolute Maximum Ratings**

| Parameter                   | Symbol                | Conditions                                                                                                                                                                                  | Ratings                                         | Unit |

|-----------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> 1 max | $DV_{DD} (DV_{DD} \le AV_{DD})$                                                                                                                                                             | DV <sub>SS</sub> – 0.3 to DV <sub>SS</sub> +7.0 | V    |

| waximum supply voltage      | V <sub>DD</sub> 2 max | AV <sub>DD</sub>                                                                                                                                                                            | AV <sub>SS</sub> – 0.3 to AV <sub>SS</sub> +7.0 | V    |

| Input voltage               | V <sub>IN</sub>       | RYIN0 to RYIN7, GUIN0 to GUIN7,<br>BVIN0 to BVIN7, CLKI, FSCIN,<br>OSRIN, OSGIN, OSBIN, OSBLK,<br>BLANK, CSYNC, HSYNC, RESET,<br>CCSEL, NPSEL, PMSEL, CDGSEL,<br>YUVSEL1, YUVSEL2, and TEST | DV <sub>SS</sub> – 0.3 to DV <sub>DD</sub> +0.3 | V    |

| Output voltage              | V <sub>OUT</sub>      | CROUT, YOUT, and BIAS                                                                                                                                                                       | DV <sub>SS</sub> – 0.3 to DV <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation | Pd max                | Ta = 25°C                                                                                                                                                                                   | 500                                             | mW   |

| Operating temperature       | Topr                  |                                                                                                                                                                                             | –20 to +75                                      | °C   |

| Storage temperature         | Tstg                  |                                                                                                                                                                                             | -40 to +125                                     | °C   |

## Allowable Operating Ranges at Ta = -20 to $75^{\circ}$ C unless otherwise specified

| Parameter                   | Symbol Conditions |                                                                                      | Conditions                                                                           |                         | Unit       |                         |       |

|-----------------------------|-------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------|------------|-------------------------|-------|

| Farameter                   | Symbol            |                                                                                      | Conditions                                                                           |                         | typ        | max                     | Offic |

| Supply voltage              | V <sub>DD</sub> 1 | DV <sub>DD</sub> (DV <sub>DD</sub>                                                   | $\leq AV_{DD}$ )                                                                     | 3.0                     |            | 5.5                     | V     |

| Supply voltage              | V <sub>DD</sub> 2 | $AV_{DD}$                                                                            |                                                                                      | 4.5                     | 5.0        | 5.5                     | V     |

| Input high-level voltage    | V <sub>IH</sub> 1 | CCSEL, NPS                                                                           | OSRIN, OSGIN, OSBIN, OSBLK<br>CCSEL, NPSEL, PMSEL, CDGSEL,<br>YUVSEL1, YUVSEL2, TEST |                         |            | V <sub>DD</sub> 1 + 0.3 | V     |

| IIIput IIIgii-level voltage | V <sub>IH</sub> 2 | RYIN0 to RYIN7, GUIN0 to GUIN7,<br>BVIN0 to BVIN7, BLANK, CSYNC<br>HSYNC, RESET      |                                                                                      | 2.2                     |            | V <sub>DD</sub> 1 + 0.3 | V     |

|                             | V <sub>IL</sub> 1 | OSRIN, OSGIN, OSBIN, OSBLK<br>CCSEL, NPSEL, PMSEL, CDGSEL,<br>YUVSEL1, YUVSEL2, TEST |                                                                                      | V <sub>SS</sub> 1 - 0.3 |            | 0.3 V <sub>DD</sub> 1   | V     |

| Input low-level voltage     | V <sub>IL</sub> 2 | RYINO to RYIN7, GUINO to GUIN7,<br>BVINO to BVIN7, BLANK, CSYNC<br>HSYNC, RESET      |                                                                                      | V <sub>SS</sub> 1 – 0.3 |            | 0.8                     | V     |

|                             |                   |                                                                                      | NTSC                                                                                 |                         | 14.31818   |                         | MHz   |

|                             | f <sub>IN</sub> 1 | CLKI                                                                                 | PAL                                                                                  |                         | 17.734475  |                         | MHz   |

| Clock fraguency             |                   |                                                                                      | PAL-M                                                                                |                         | 14.3024459 |                         | MHz   |

| Clock frequency             | f <sub>IN</sub> 2 |                                                                                      | NTSC                                                                                 |                         | 3.579545   |                         | MHz   |

|                             |                   | FSCIN                                                                                | PAL                                                                                  |                         | 4.43361875 |                         | MHz   |

|                             |                   |                                                                                      | PAL-M                                                                                |                         | 3.57561149 |                         | MHz   |

Continued on next page.

## Continued from preceding page.

| Parameter         | Symbol            | Conditions                |     | Unit |                   |       |

|-------------------|-------------------|---------------------------|-----|------|-------------------|-------|

| Falanetei         | Symbol            | Conditions                | min | typ  | max               | Offic |

| Input amplitude   | V <sub>IN</sub> 1 | CLKI (capacitor coupled)  | 2.0 |      | V <sub>DD</sub> 1 | Vp-p  |

| Imput ampilitude  | V <sub>IN</sub> 2 | FSCIN (capacitor coupled) | 2.0 |      | V <sub>DD</sub> 1 | Vp-p  |

| Clock duty        | Fduty1            | CLKI, FSCIN               | 40  | 50   | 60                | %     |

| Reset pulse width | t <sub>wrst</sub> | RESET                     | 400 |      |                   | ns    |

# Electrical Characteristics at Ta = -20 to $75^{\circ}C$ , $DV_{DD} = 5.0$ V, $AV_{DD} = 5.0$ V unless otherwise specified

| Parameter                       | Symbol Conditions |                                                                    |                                                                                                                                                 | Ratings    |        | Unit |      |

|---------------------------------|-------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------|------|

| Parameter                       | Symbol            | Conditions                                                         |                                                                                                                                                 | min        | typ    | max  | Unit |

| Input high-level current        | I <sub>IH</sub> 1 | BLANK, CSYNC<br>CCSEL, NPSEL,                                      | OSRIN, OSGIN, OSBIN, OSBLK, BLANK, CSYNC, HSYNC, RESET, CCSEL, NPSEL, PMSEL, CDGSEL, YUVSEL1, YUVSEL2, TEST: V <sub>IN</sub> = DV <sub>DD</sub> |            |        | 5    | μА   |

|                                 | I <sub>IH</sub> 2 |                                                                    | , GUIN0 to GUIN7,<br>(Pull-down resistors<br>= DV <sub>DD</sub>                                                                                 | 25         | 50     | 75   | μA   |

| Input low-level current         | I <sub>IL</sub> 1 | BLANK, CSYNC<br>CCSEL, NPSEL,                                      | OSBIN, OSBLK,<br>HSYNC, RESET,<br>PMSEL, CDGSEL,<br>SEL2, TEST: V <sub>IN</sub> = DV <sub>SS</sub>                                              | <b>-</b> 5 |        |      | μА   |

|                                 | I <sub>IL</sub> 2 | RYIN0 to RYIN7<br>BVIN0 to BVIN7<br>are built in): V <sub>IN</sub> | -5                                                                                                                                              |            |        | μA   |      |

| Internal feedback resistance    | R <sub>BIAS</sub> | CLKI, FSCIN                                                        |                                                                                                                                                 |            | 1      |      | ΜΩ   |

| D/A converter resolution        |                   | YOUT, CROUT                                                        |                                                                                                                                                 |            | 8 bits |      |      |

| D/A converter output resistance | R <sub>DAC</sub>  | YOUT, CROUT                                                        |                                                                                                                                                 | 150        | 300    | 500  | Ω    |

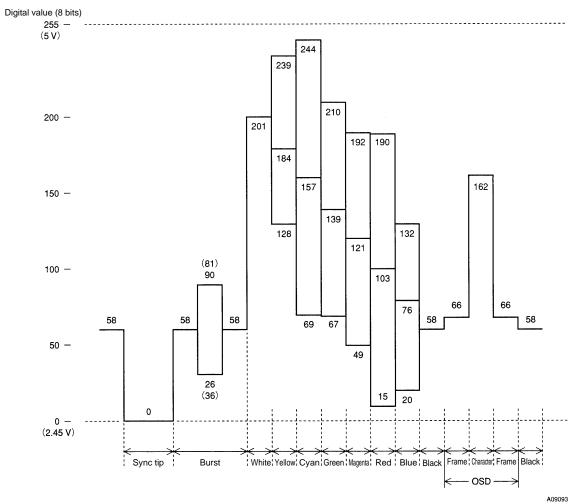

| D/A converter reference voltage | V <sub>REF</sub>  | YOUT, CROUT<br>(The output volta<br>data is zero)                  | ge when each bit of the 8-bit                                                                                                                   | 2.40       | 2.45   | 2.50 | V    |

|                                 |                   |                                                                    | (DV <sub>DD</sub> = 5.0 V : NTSC)                                                                                                               |            | 37     | 56   | mA   |

|                                 |                   | $DV_DD$                                                            | (DV <sub>DD</sub> = 5.0 V : PAL)                                                                                                                |            | 45     | 68   | mA   |

|                                 | I <sub>DD</sub> 1 | $(AV_{DD} = 5.0 V)$                                                | (DV <sub>DD</sub> = 3.3 V : NTSC)                                                                                                               |            | 15     | 23   | mA   |

|                                 |                   |                                                                    | (DV <sub>DD</sub> = 3.3 V : PAL)                                                                                                                |            | 18     | 27   | mA   |

| Operating current drain         |                   |                                                                    | (DV <sub>DD</sub> = 5.0 V : When 2 channels are used)                                                                                           |            | 21     | 37   | mA   |

|                                 |                   | AV <sub>DD</sub>                                                   | (DV <sub>DD</sub> = 5.0 V : When 1 channel is used)                                                                                             |            | 12     | 21   | mA   |

|                                 | I <sub>DD</sub> 2 | $(AV_{DD} = 5.0 \text{ V})$                                        | (DV <sub>DD</sub> = 3.3 V :When 2 channels are used)                                                                                            |            | 22     | 39   | mA   |

|                                 |                   |                                                                    | (DV <sub>DD</sub> = 3.3 V : When 1 channel is used)                                                                                             |            | 13     | 23   | mA   |

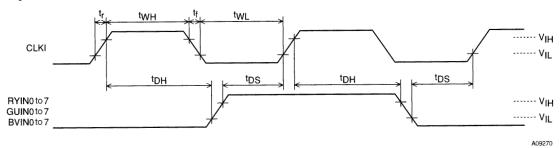

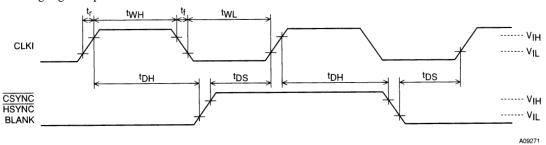

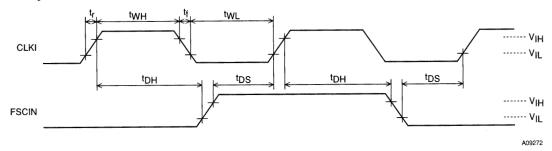

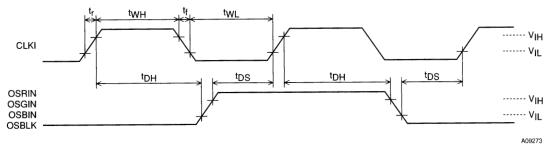

# Timing Characteristics at Ta = 25 °C, DV<sub>DD</sub> = 5.0 V, AV<sub>DD</sub> = 5.0 V, $t_r$ = $t_f$ = 3 ns unless otherwise specified

| Davassatas                  | Symbol Conditions - |                                                                                                                                                                                                                                                                                                                                                                                                      |          | - Unit |     |          |

|-----------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|-----|----------|

| Parameter                   |                     |                                                                                                                                                                                                                                                                                                                                                                                                      | min      | typ    | max | Offit    |

| Data setup time             | t <sub>DS</sub>     | RYIN0 to 7, GUIN0 to 7, BVIN0 to 7 $\rightarrow$ CLKI BLANK, CSYNC, HSYNC $\rightarrow$ CLKI OSRIN, OSGIN, OSBIN, OSBLK $\rightarrow$ CLKI FSCIN $\rightarrow$ CLKI : DV <sub>DD</sub> = 5.0 V : DV <sub>DD</sub> = 3.3 V                                                                                                                                                                            | 0        |        |     | ns<br>ns |

| Data hold time              | t <sub>DH</sub>     | $ \begin{split} & \text{CLKI} \rightarrow \text{RYIN0 to } 7, \text{GUIN0 to } 7, \text{BVIN0 to } 7 \\ & \text{CLKI} \rightarrow \text{BLANK, } \overline{\text{CSYNC, }} \overline{\text{HSYNC}} \\ & \text{CLK} \rightarrow \text{OSRIN, OSGIN, OSBIN, OSBLK} \\ & \text{CLKI} \rightarrow \text{FSCIN} \\ & : \text{DV}_{DD} = 5.0 \text{ V} \\ & : \text{DV}_{DD} = 3.3 \text{ V} \end{split} $ | 10<br>12 |        |     | ns<br>ns |

| Minimum clock pulse width   | t <sub>WL</sub>     | CLKI (For a square wave input)                                                                                                                                                                                                                                                                                                                                                                       | 18       |        |     | ns       |

| Willimian clock paise width | t <sub>WH</sub>     | CLKI (For a square wave input)                                                                                                                                                                                                                                                                                                                                                                       | 18       |        |     | ns       |

| Input clock duty            | tduty               | CLKI, FSCIN (For a sine wave input)                                                                                                                                                                                                                                                                                                                                                                  | 40       |        | 60  | %        |

## **Timing Charts**

Data Input

Synchronizing Signal Input

## Subcarrier Input

## OSD Input

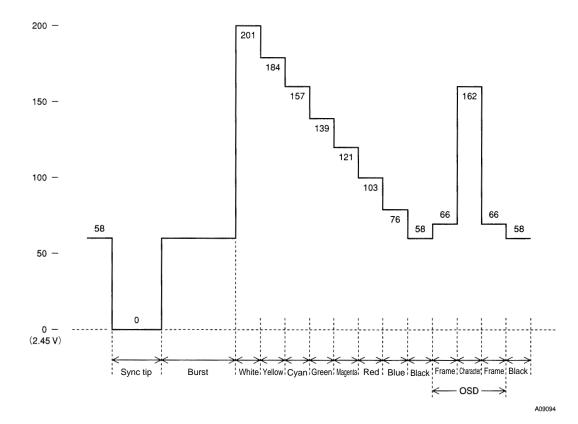

# Composite Video Signal (C • VIDEO) Output

Note: The value in parentheses is the burst amplitude for PAL and PAL-M modes.

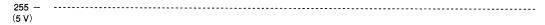

# **Luminance Signal Output (Y)**

# Chroma Signal (C) Output

Note: The value in parentheses is the burst amplitude for PAL and PAL-M modes.

A09095

### **Functional Description**

#### 1. Clocks

The system clock operates at 4fsc and is input to the CLKI pin (pin 6). A feedback (bias) resistor is built in. Input clock frequencies:

NTSC mode: 14.31818 MHz PAL mode: 17.734475 MHz PAL-M mode: 14.30244596 MHz

### 2. Video signal output formats

The LC78011E can provide either a Y/C (luminance signal/chrominance signal) separated signal output or a composite video signal output.

The CCSEL pin (pin 30) selects the output format.

| CCSEL (pin 30) setting | High = 1                                               | Low = 0              |

|------------------------|--------------------------------------------------------|----------------------|

| CROUT (pin 26) output  | Composite video signal                                 | Chroma signal (C)    |

| YOUT (pin 28) output   | Fixed low-level output (The D/A converter is stopped.) | Luminance signal (Y) |

### 3. Digital video input switching

The LC78011E supports both input from an MPEG decoder (24 bits, 8 bits each of R, G, and B data) and a 12-bit CD-G input (4 bits each of R, G, and B data). The CDGSEL pin (pin 33) switches the input.

| CDGSEL (pin 33)         | Low = 0             | High = 1                |

|-------------------------|---------------------|-------------------------|

| Digital input selection | 12-bit input (CD-G) | 24-bit input (Video CD) |

### • Sample CD-G (LC7874E) connection

|   | LC78011E                                                             | LC7874E                                                              |

|---|----------------------------------------------------------------------|----------------------------------------------------------------------|

| R | RYIN7 (pin 45)<br>RYIN6 (pin 46)<br>RYIN5 (pin 47)<br>RYIN4 (pin 48) | ROUT3 (pin 36)<br>ROUT2 (pin 37)<br>ROUT1 (pin 38)<br>ROUT0 (pin 39) |

| G | GUIN7 (pin 9)<br>GUIN6 (pin 10)<br>GUIN5 (pin 11)<br>GUIN4 (pin 12)  | GOUT3 (pin 42)<br>GOUT2 (pin 43)<br>GOUT1 (pin 44)<br>GOUT0 (pin 45) |

| В | BVIN7 (pin 17)<br>BVIN6 (pin 18)<br>BVIN5 (pin 19)<br>BVIN4 (pin 20) | BOUT3 (pin 46)<br>BOUT2 (pin 47)<br>BOUT1 (pin 48)<br>BOUT0 (pin 49) |

### 4. Digital video input format selection

The LC78011E supports both RGB and YUV formats. The YUVSEL1 and YUVSEL2 pins (pins 43 and 44) are used to select the input video format.

| YUVSEL2 (pin 44) | YUVSEL1 (pin 43) | Input format  |

|------------------|------------------|---------------|

| Low = 0          | Low = 0          | RGB input     |

| Low = 0          | High = 1         | YUV input     |

| High = 1         | Low = 0          | Y/UV input*   |

| High = 1         | High = 1         | Illegal value |

Note: \* GUIN0 to GUIN7 are not used in the Y/UV input mode.

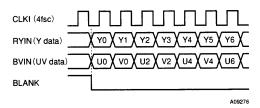

The U/V discrimination for the UV input is performed by starting acquisition of the U input data with a timing referenced to the falling edge of the BLANK pin (pin 40) input signal. In this mode, the input pins GUIN0 to GUIN7 must be left open or tied to DVSS. (These inputs include built-in pull-down resistors.)

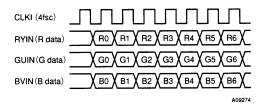

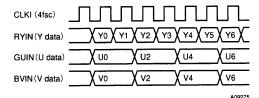

### • Data input timing

RGB input (24 bits)

YCbCr (YUV) input (24 bits)

Y (8 bits), CbCr (8 bits) multiplexed input

### 5. OSD input (on-screen display data input)

The LC78011E provides an OSD signal RGB input function. Four input signals are required: the 3 bits of R, G, and B data and the BLANK pin input signal, which is used for OSD switching.

| R (OSRIN: pin 38) | G (OSGIN: pin 37) | B (OSBIN: pin 36) | OSBLK (pin 39) | OSD display color |

|-------------------|-------------------|-------------------|----------------|-------------------|

| L = 0             | L = 0             | L = 0             | L = 0          | Display off       |

| L = 0             | L = 0             | L = 0             | H = 1          | Black             |

| H = 1             | L = 0             | L = 0             | H = 1          | Red               |

| L = 0             | H = 1             | L = 0             | H = 1          | Green             |

| L = 0             | L = 0             | H = 1             | H = 1          | Blue              |

| H = 1             | L = 0             | H = 1             | H = 1          | Magenta           |

| H = 1             | H = 1             | L = 0             | H = 1          | Yellow            |

| L = 0             | H = 1             | H = 1             | H = 1          | Cyan              |

| H = 1             | H = 1             | H = 1             | H = 1          | White             |

Note: The white luminance level is 162, and the black and framing luminance level is 66. (When converted from the As 8-bit data values.)

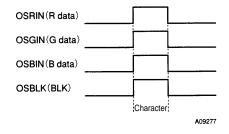

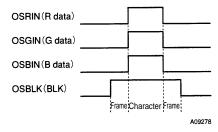

### • OSD timing

When no framing is used

When a frame is used (Frame color: black)

# 6. Signal format switching (NTSC, PAL, or PAL-M)

The NPSEL and PMSEL pin (pin 31 and 32) are used to switch the signal format.

| NPSEL (pin 31) | PMSEL (pin 32) | Signal format |

|----------------|----------------|---------------|

| L = 0          | L = 0          | NTSC          |

| H = 1          | L = 0          | PAL           |

| L = 0          | H = 1          | PAL-M         |

| H = 1          | H = 1          | Illegal value |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of March, 1998. Specifications and information herein are subject to change without notice.