CMOS LSI

©3158A

# Digital Signal Processor for Compact Disc Players

#### Overview

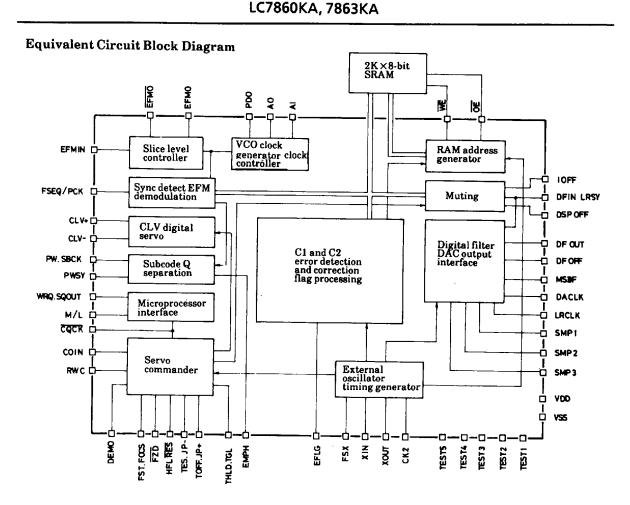

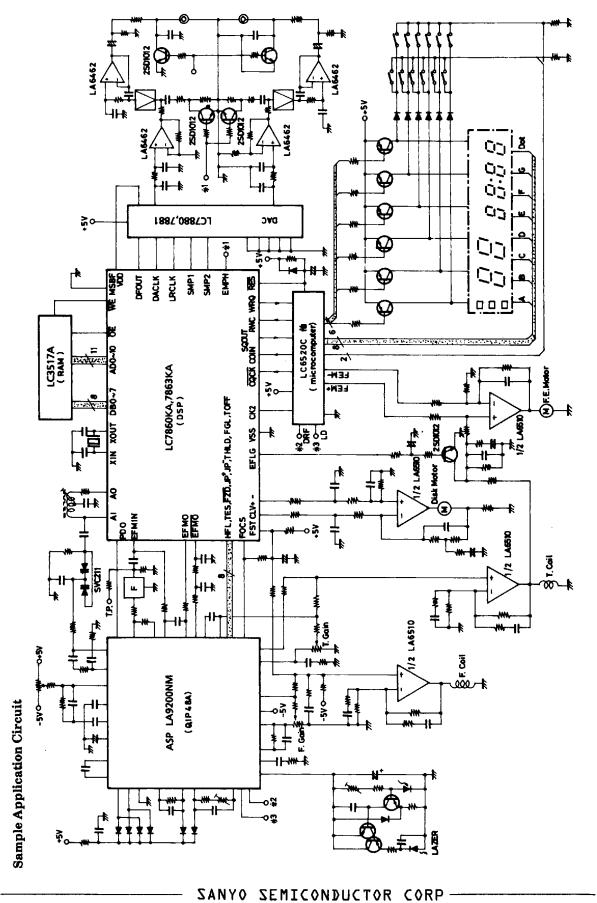

The Sanyo LC7860KA and LC7863KA CMOS Digital Signal Processing LSIs provide servo control and signal processing for the digital audio sections of compact disk and laser disk players. Available in surface-mount 80-pin plastic flat package, the LC7860KA and LC7863KA integrate several Compact Disk player functions into a single chip for reduced system costs. Both devices perform several signal processing functions, including demodulation of the EFM signal from the optical pickup, de-interleave, detection and correction of error signals, and digital filtering for sound quality improvement. In addition, they can process control commands from a microprocessor for the servo system. Both the LC7860KA and LC7863KA can be direct interfaced to the Sanyo LC7880 Serial I/O Digital-to Analog Converter LSI. The difference between LC7860KA and LC7863KA lies in the conditions for reading subcode Q as well as track jumping and the LRCLK timing. For further details, see Notes 1 and 2 (page 9, 10).

#### **Functions**

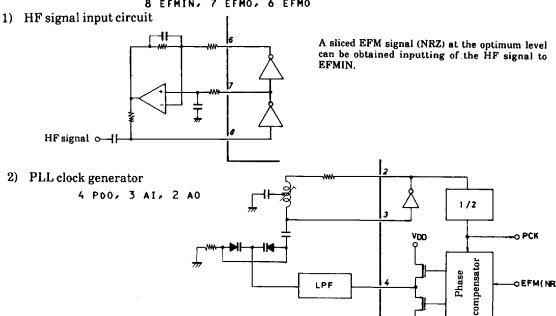

- · When an HF signal is input, it is sliced at the proper level and converted to an EFM signal. Phase comparison with VCO is carried out and a 4.3218MHz (average) phase-locked loop playback clock signal is generated.

- · A 4.3218MHz standard clock and necessary internal timing can be generated by connecting an external crystal oscillator.

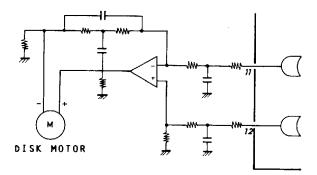

- · Disk motor rotation speed is controlled by the frame phase differential signal generated using the playback and standard clocks.

- · Detection, protection, and interpolation of the frame sync signal ensures stable data reading.

- · The EFM signal is demodulated and converted to 8-bit symbol data.

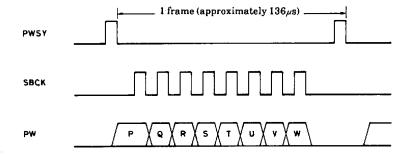

- · Subcodes are separated from the EFM modulation signal and output to an external microprocessor.

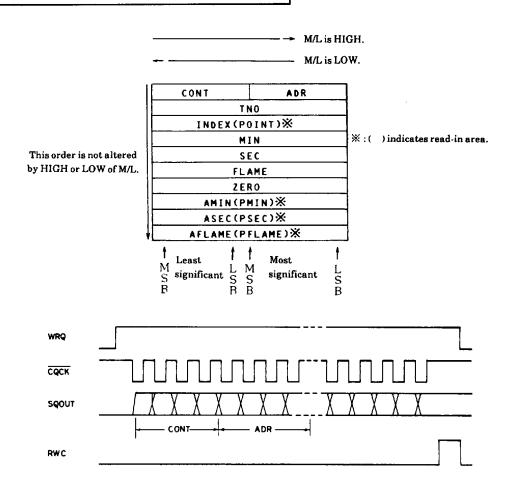

- · The subcode Q signal is output to the microprocessor using serial I/O after cyclical redundancy checking. (SLB first out order can be selected.)

- · Using external RAM, the EFM modulated signal is buffered to absorb jitter (up to  $\pm 4$  frames) caused by fluctuations in the disk rotation speed.

Continued on next page.

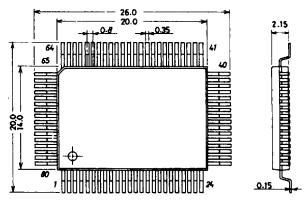

# Case Outline 3044B (unit: mm)

SANYO: QIP80A

D101JN/8210TA No.3158-1/18

#### Continued from preceding page.

# SANYO SEMICONDUCTOR CORF

- Unscrambling and de-interleaving is performed by arranging EFM demodulated signal in required order.

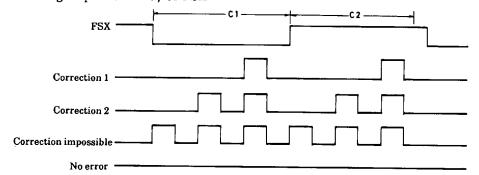

- · Detection, correction and flag processing for error signals using C1, two-level C2, two-level correction method.

- · C2 flag is set by reference to C1 flag and C2 ckeck results, and signal interpolation and previous value hold is performed by C2 flag.

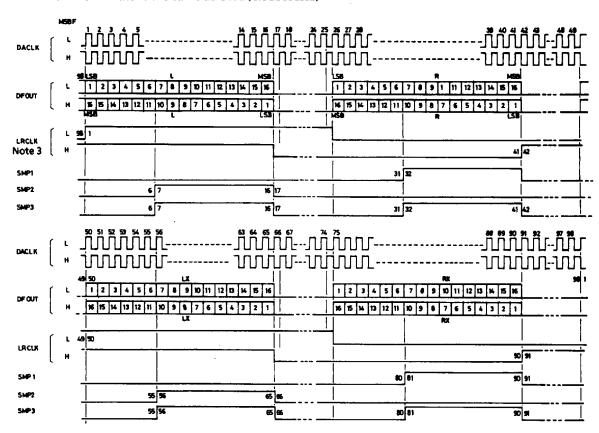

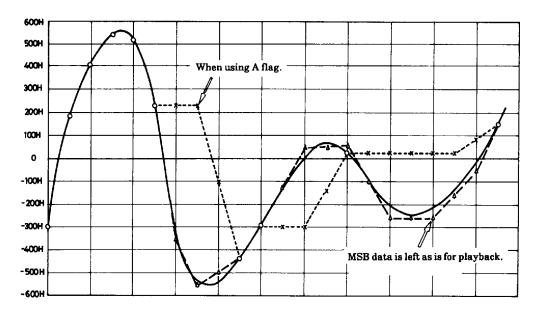

- DAC signal with improved output data continuity is obtained by over-sampling  $(2\times)$  and digital filtering.

- · Functions such as track jump, focus start, disk motor start/stop and muting ON/OFF can be performed using commands from a microprocessor (8-bit serial input).

#### **Features**

- Compact surface-mount 80-pin plastic flat pack

- · Low-power silicon-gate CMOS technology

- · Single +5V power supply

- · Easily calibrated using DEMO pin

| Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS} = 0V$ unit |                     |                                   |                                |                      |       |  |  |  |

|---------------------------------------------------------------------|---------------------|-----------------------------------|--------------------------------|----------------------|-------|--|--|--|

| Maximum Supply Voltage                                              | V <sub>DD</sub> 1   |                                   | $V_{SS} - 0$                   |                      |       |  |  |  |

| Input Voltage                                                       | V <sub>IN</sub>     |                                   | $V_{SS} = 0.3 \text{ to } V_D$ |                      |       |  |  |  |

|                                                                     | V <sub>OUT</sub>    |                                   | $V_{SS} = 0.3 \text{ to } V_D$ | <i>D</i>             |       |  |  |  |

| Output Voltage                                                      |                     |                                   | VSS-0.5 to VD                  | 300 mW               |       |  |  |  |

| Allowable Power Dissipation                                         |                     | XX                                | 20.6                           |                      |       |  |  |  |

| Operating Temperature                                               | Topg                |                                   |                                |                      |       |  |  |  |

| Storage Temperature                                                 | Tstg                |                                   | - 40 to                        | + 125 °C             |       |  |  |  |

| Allowable Operating Conditi                                         | ons at Ta           | $a = 25$ °C, $V_{SS} = 0$ V       | min                            | typ max              | unit  |  |  |  |

| Supply Voltage                                                      | $V_{DD}$            | $V_{DD}$                          | 4.5                            | 5.5                  | V     |  |  |  |

| Input 'H'-Level Voltage                                             | $V_{IH}(1)$         | (TEST1 to 5)Al, FZD, HFL,         | $0.7V_{ m DD}$                 | $V_{ m DD}$          | V     |  |  |  |

|                                                                     |                     | DEMO,IOFF,DFOFF,                  |                                |                      |       |  |  |  |

|                                                                     |                     | DSPOFF,M/L,MSBF,RES               |                                |                      |       |  |  |  |

|                                                                     | $V_{IH}(2)$         | DFIN, DB0 to 7, SBCK, RWC         | . 2.2                          | $V_{\mathrm{DD}}$    | V     |  |  |  |

|                                                                     | 111                 | COIN, CQCK                        | ,                              | 55                   |       |  |  |  |

|                                                                     | $V_{IH}(3)$         | EFMIN                             | $0.6  m V_{DD}$                | $V_{\mathrm{DD}}$    | V     |  |  |  |

|                                                                     | $V_{IH}(4)$         | TES                               | $0.8V_{\mathrm{DD}}$           | $v_{DD}^{}$          |       |  |  |  |

| Input 'L'-Level Voltage                                             | $V_{IL}(1)$         | (TEST1 to 5)AI,FZD,HFL,           | $V_{SS}$                       | $0.3V_{\mathrm{DD}}$ | V     |  |  |  |

|                                                                     | 1000                | DEMO,IOFF,DFOFF,                  | . 56                           | DD.                  |       |  |  |  |

|                                                                     |                     | DSPOFF,M/L,MSBF,RES               |                                |                      |       |  |  |  |

|                                                                     | $V_{IL}(2)$         | DFIN, DB0 to 7, SBCK, RWC         | , $V_{SS}$                     | 0.8                  | V     |  |  |  |

|                                                                     |                     | COIN, CQCK                        |                                |                      |       |  |  |  |

|                                                                     | $V_{IL}(3)$         | EFMIN                             | $V_{SS}$                       | $0.4V_{ m DD}$       | V     |  |  |  |

|                                                                     | $V_{IL}(4)$         | TES                               | $V_{SS}$                       | $0.2V_{ m DD}$       | V     |  |  |  |

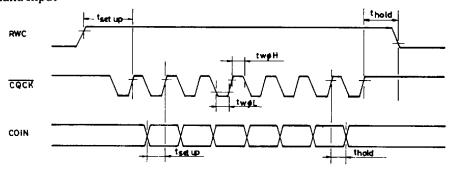

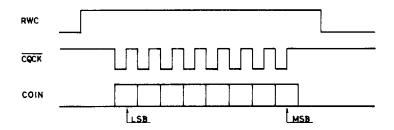

| Data Setup Time                                                     | t <sub>set up</sub> | COIN,RWC,Fig.1                    | 400                            |                      | ns    |  |  |  |

| Data Hold Time                                                      | $t_{hold}$          | RWC,Fig.1                         | 400                            |                      | ns    |  |  |  |

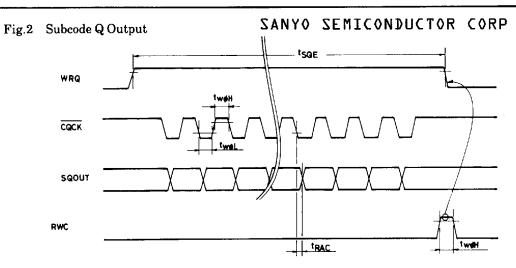

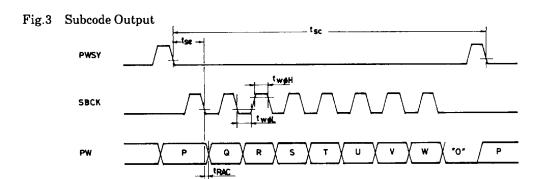

| 'H'-Level Clock Pulse Width                                         | $t_{w\phi H}$       | SBCK, CQCK, RWC, Figs. 1,2        | 2,3 400                        |                      | ns    |  |  |  |

| 'L'-Level Clock Pulse Width                                         | twøL                | CQCK,SBCK,Figs.1,2,3              | 400                            |                      | ns    |  |  |  |

| Data Read Access Time                                               | trac                | Figs.2,3                          | 0                              | 400                  | ns    |  |  |  |

| Subcode Q Signal                                                    | $t_{SQE}$           | Fig.2, without RWC signal         |                                | 11.2                 | ms    |  |  |  |

| Read Enable Time                                                    | DQD                 | <i>5</i> ,                        |                                |                      |       |  |  |  |

| Subcode Read Cycle                                                  | $t_{SC}$            | Fig.3                             |                                | 136                  | μS    |  |  |  |

| Subcode Read Enable                                                 | $\mathbf{t_{SE}}$   | Fig.3                             | 400                            |                      | ns    |  |  |  |

| Reset Pulse Width                                                   | twres               | RES                               | 400                            |                      | ns    |  |  |  |

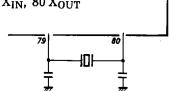

| X'tal OSC Frequency                                                 | f <sub>x'tal</sub>  | X <sub>IN</sub> ,X <sub>OUT</sub> | , -00                          | 8.6436               | MHz   |  |  |  |

| Operating Frequency Range                                           | fop (1)             | AI                                | 2.0                            |                      | MHz   |  |  |  |

| o Porture & roducinoj mange                                         | fop (2)             | EFMIN, $V_{IN} \ge 1V_{p-p}$      | 2.0                            | 10                   | MHz   |  |  |  |

|                                                                     | 10P (2)             | Strate, tild = 1 th.h             |                                | 10                   | ***** |  |  |  |

# LAZT 📰 TOS P451100 4707PP7 📰 🗷 3E4

# LC7860KA, 7863KA

| Electrical Characteristics at | Ta = 25°C       | $V_{SS} = 0V, V_{DD} = 5V$                                                                            | min        | typ   | max  | unit     |

|-------------------------------|-----------------|-------------------------------------------------------------------------------------------------------|------------|-------|------|----------|

| Current Dissipation           | $I_{DD}$        |                                                                                                       |            | 15    | 30   | mA       |

| Input 'H'-Level Current       | $l_{IH}(1)$     | AI,EFMIN, <del>FZD</del> ,TES,MSBF,                                                                   |            |       | 5    | $\mu A$  |

|                               |                 | SBCK,COIN,CQCK,RES,HFL,                                                                               |            |       |      |          |

|                               |                 | $RWC,M/L:V_{IN}=V_{DD}$                                                                               |            |       |      |          |

|                               | $I_{IH}(2)$     | (TEST1 to 5)DEMO,DFOFF,                                                                               | 20         |       | 75   | $\mu A$  |

|                               |                 | DSPOFF, IOFF: $V_{IN} = V_{DD} = 5.5V$                                                                |            |       |      |          |

| Input 'L'-Level Current       | $I_{IL}(1)$     | AI,EFMIN, <del>FZD,TE</del> S,MSBF,                                                                   | <b>-</b> 5 |       |      | $\mu$ A  |

|                               |                 | $SBCK,COIN,\overline{CQCK},\overline{RES},HFL,$                                                       |            |       |      |          |

|                               |                 | $RWC,M/L:V_{IN}=V_{SS}$                                                                               |            |       |      |          |

| Output 'H'-Level Voltage      | $V_{OH}(1)$     |                                                                                                       | $V_{DD}-1$ |       |      | V        |

|                               |                 | CLV - ,FOCS,FSEQ/PCK,TOFF,                                                                            |            |       |      |          |

|                               |                 | TGL,THLD,JP+,JP-,EMPH,                                                                                |            |       |      |          |

|                               |                 | $EFLG: I_{OH} = -1mA$                                                                                 |            |       |      |          |

|                               | $V_{OH}(2)$     |                                                                                                       | $V_{DD}-1$ |       |      | V        |

|                               |                 | $\underline{DACLK}$ , $\underline{DFIN}$ , $\underline{LRSY}$ , $\underline{CK2}$ , $\overline{OE}$ , |            |       |      |          |

|                               |                 | WE,AD0 to 10,DB0 to 7,PW,PWS                                                                          |            |       |      |          |

|                               |                 | $FSX,WRQ,SQOUT:I_{OH} = -0.5m$                                                                        | A          |       |      |          |

| Output 'L'-Level Voltage      | $V_{OL}(1)$     | AO,PDO,EFMO,EFMO,CLV+,                                                                                |            |       | 1    | V        |

|                               |                 | CLV-,FOCS,FSEQ/PCK,TOFF,                                                                              |            |       |      |          |

|                               |                 | TGL,THLD,JP+,JP-,EMPH,                                                                                |            |       |      |          |

|                               |                 | $EFLG: I_{OL} = 1mA$                                                                                  |            |       |      |          |

|                               | $V_{OL}(2)$     | SMP1,2,3,LRCLK,DFOUT,DACL                                                                             |            |       | 0.4  | V        |

|                               |                 | DFIN,LRSY,CK2,OE,WE,AD0 to                                                                            | 10,        |       |      |          |

|                               |                 | DB0 to 7,PW,PWSY,FSX,WRQ,                                                                             |            |       |      |          |

|                               | X7 (0)          | SQOUT: I <sub>OL</sub> =2mA                                                                           |            |       | 0.75 | **       |

| O OPP I I O                   | $V_{OL}(3)$     |                                                                                                       |            |       | 0.75 | V        |

| Output OFF-Leak Current       | $I_{OFF}(1)$    |                                                                                                       |            |       | 5    | $\mu$ A  |

|                               | I (0)           | DB0 to 7: V <sub>OH</sub> = V <sub>DD</sub>                                                           | _          |       |      |          |

|                               | $I_{OFF}(2)$    | PDO,FST,DFIN,AD0 to 6,                                                                                | -5         |       |      | $\mu$ A  |

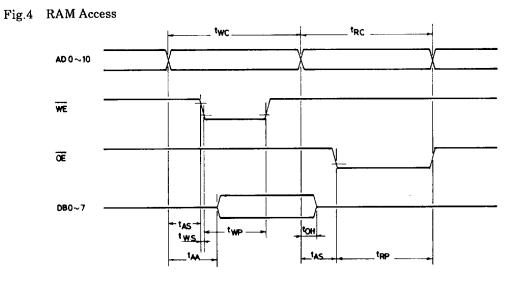

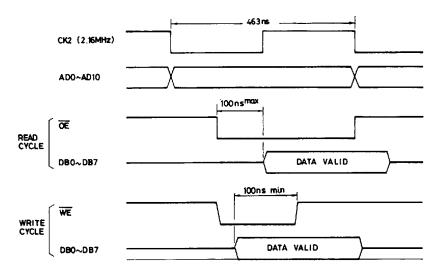

| Write Cycle Time              | tura            | DB0 to 7: $V_{OL} = V_{SS}$<br>Fig.4                                                                  |            | 462.8 |      | nc       |

| Read Cycle Time               | ${ m t_{RC}}$   | Fig.4                                                                                                 |            | 462.8 |      | ns<br>ns |

| Address Setup Time            | t <sub>AS</sub> | Fig.4                                                                                                 | 80         | 402.0 | 150  | ns       |

| Write Pulse Width             | twp             | Fig.4                                                                                                 | 00         | 231.4 | 100  | ns       |

| Read Pulse Width              | t <sub>RP</sub> | Fig.4                                                                                                 |            | 347.1 |      | ns       |

| Address Access Time           | t <sub>AA</sub> | Fig.4                                                                                                 | 80         | UT1.1 | 170  | ns       |

| Output Hold Time              | t <sub>OH</sub> | Fig.4                                                                                                 | <b>–10</b> |       | 80   | ns       |

| Read/Write Setup Time         | tws             | Fig.4                                                                                                 | 0          |       | 20   | ns       |

| <u> </u>                      | 110             | •                                                                                                     | -          |       |      |          |

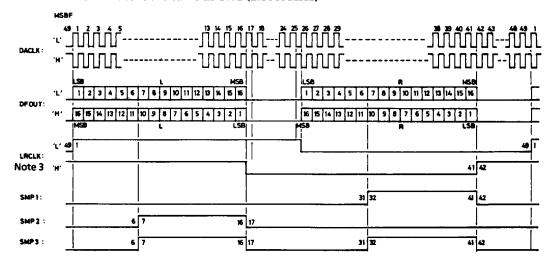

Fig.1 Command Input

# LAZT M 84P LTSLLOO 4FOFPFF M G 3E4

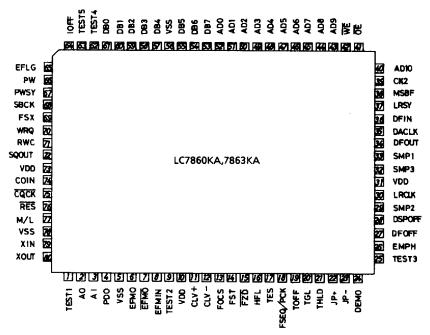

#### Pin Assignment

# LAZT ■ 4T8 5754400 4707PP7 ■ 4 3E4

# SANYO SEMICONDUCTOR CORP LC7860KA, 7863KA

| Pin Des  | Pin Description |               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|----------|-----------------|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No.  | Pin Name        | I/O           | *        | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|          | TEST1           | I             | -        | Test pin. Normally not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

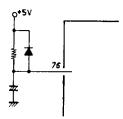

| 2        | AO              | 0             | -        | VCO is generated by connecting resonance circuit between AI and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 3        | AI              | 1             |          | AO. (8.6436MHz) is phase output with EFM signal, and is set to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 4        | PDO             | 0             |          | increase frequency when +.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 5        | V <sub>SS</sub> | -             | -        | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6        | EFMO            | 0             | _        | 1 to 2Vpp HF signal is input to EFMIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 7        | <b>EFMO</b>     | 0             | -        | Output from EFMO and BFMO passes through amplitude limiter and reverse phase EFM signal is obtained from both. This performs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 8        | EFMIN           | I             | -        | slice level control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 9        | TEST2           | I             | -        | Test pin: Normally not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 10       | $V_{DD}$        | -             | -        | +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 11       | CLV+            | 0             | -        | Disk motor control output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 12       | CLV-            | 0             | -        | TOTAL TRANSPORT OF THE PROPERTY OF THE PROPERT |  |  |

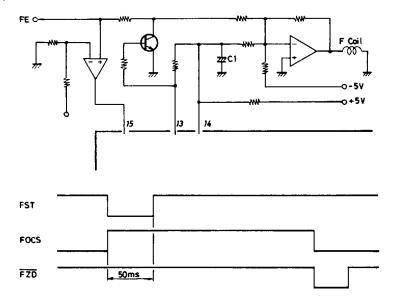

| 13       | FOCS            | 0             |          | Focus servo is off when FOCS is HIGH. The lens is lowered by FST and then FST is HIGH, the lens is gradually pulled up. FOCS is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 14<br>15 | FST<br>FZD      | 0<br>I        | -        | reset when FZD is generated. For focus-in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

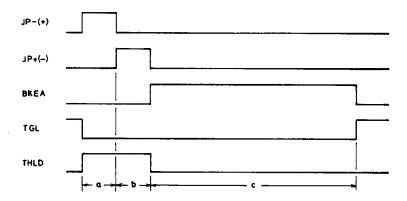

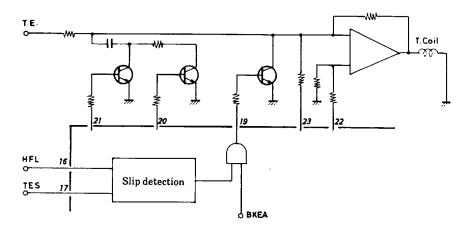

| 16       | HFL             | I             | *1       | *1 Kick pulses, JP+ and JP-, are generated according to track                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 17       | TES             | Ī             | *1       | jump command. A jump of the prescribed number of tracks is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 18       | FSEQ/PCK        | 0             | *2       | (1,4,16,64).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 19       | TOFF            | 0             | *1       | *2 When 4.3218MHz PCK monitor terminal/DEMO is HIGH both                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 20       | TGL<br>THLD     | 0             | *1       | SYNC detected from EFM signal and SYNC of counter are the same at HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 21 22    | JP+             | 0             | *1       | Same at mun.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 23       | JP-             | ŏ             | *1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 24       | DEMO            | I             | -        | Set and sound output adjustment pin function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 25       | TEST3           | I             | -        | Test pin. Normally not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 26       | ЕМРН            | 0             | -        | De-emphasis is necessary when HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 27       | DFOFF           | I             | -        | ON/OFF switch for digital filter. No filtering when HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 28       | DSPOFF          | I             | -        | Test pin. Normally not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |