### Overview

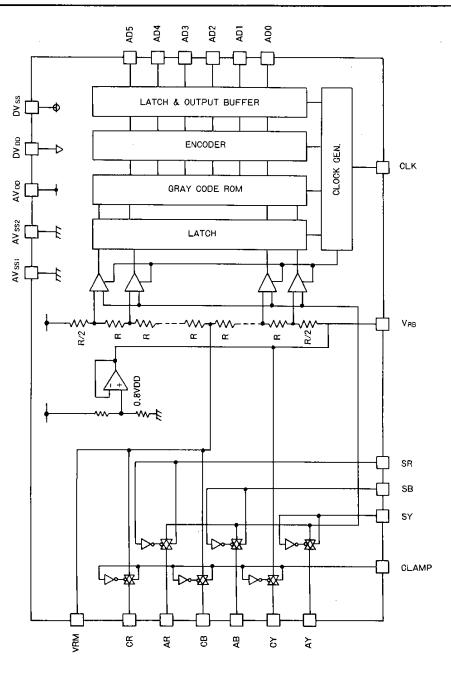

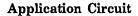

The LC7480 is a video 6-bit flash type A/D converter implemented in CMOS process technology. It has an internal clamp voltage generation circuit for video component signals (Y, R-Y, and B-Y) and a multiplexer.

#### **Functions**

SANYO Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

O1494TH/6012JN/1090TA/8239TA,TS №.3270-1/5

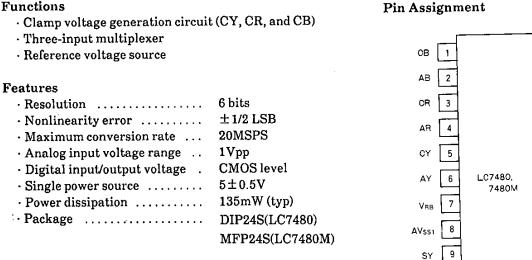

10 SR

SB 11 24 VRM

23

22

21

20 CLK

19

18

17 AD1

15 AD3

AVod

AVss2

DVoo

DVss

AD2 16

AD4 14

AD0 (LSB)

## **Pin Functions**

| Pin<br>No. | Symbol             | Function                            | Pin<br>No. | Symbol             | Function              |

|------------|--------------------|-------------------------------------|------------|--------------------|-----------------------|

| 1          | СВ                 | Clamp voltage output for B-Y signal | 13         | AD5                | Digital output [MSB]  |

| 2          | AB                 | B-Y signal input                    | 14         | AD4                | Digital output        |

| 3          | CR                 | Clamp voltage output for R-Y signal | 15         | AD3                | Digital output        |

| 4          | AR                 | R-Y signal input                    | 16         | AD2                | Digital output        |

| 5          | CY                 | Clamp voltage output for Y signal   | 17         | AD1                | Digital output        |

| 6          | AY                 | Y signal input                      | 18         | AD0                | Digital output [LSB]  |

| 7          | V <sub>RB</sub>    | Reference voltage (B)               | 19         | DV <sub>SS</sub>   | Digital GND           |

| 8          | AV <sub>SS</sub> 1 | Analog GND                          | 20         | CLK                | Clock input           |

| 9          | SY                 | Multiplexer SW (for Y signal)       | 21         | DV <sub>DD</sub>   | Digital power supply  |

| 10         | SR                 | Multiplexer SW (for R-Y signal)     | 22         | AV <sub>SS</sub> 2 | Analog GND            |

| 11         | SB                 | Multiplexer SW (for B-Y signal)     | 23         | AV <sub>DD</sub>   | Analog power supply   |

| 12         | CLAMP              | Clamp SW                            | 24         | V <sub>RM</sub>    | Reference voltage (M) |

**№.3270-2/5**

| Absolute Maximum Ratings at $Ta = 25 \pm 2^{\circ}C$ , $V_{SS}$ (= $DV_{SS}$ , $AV_{SS}1$ , $AV_{SS}2$ ) = 0V                            |                                                                            |                                                       |              |                                      |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|--------------|--------------------------------------|--|--|--|--|

| Secondar Malta an                                                                                                                        |                                                                            |                                                       | uni          | •• •                                 |  |  |  |  |

| Supply Voltage                                                                                                                           | $V_{DD}$<br>(=AV <sub>DD</sub> ,DV <sub>DD</sub> )                         | -0.3 to $+7$                                          | 7.0 V        | / AV <sub>DD</sub> ,DV <sub>DD</sub> |  |  |  |  |

| I/O Pin Voltage                                                                                                                          | $V_{\rm IN}, V_{\rm OUT}$                                                  | $-0.3$ to $V_{DD}$ + (                                | ).3 V        | / I/O pins                           |  |  |  |  |

| Analog Reference Voltage                                                                                                                 | $V_{\rm RM}, V_{\rm RB}$                                                   | -0.3 to V <sub>DD</sub> +0                            |              | -                                    |  |  |  |  |

| Allowable Power Dissipation                                                                                                              | Pd max Ta≦70°C                                                             |                                                       | ,0 mW        |                                      |  |  |  |  |

| Operating Temperature                                                                                                                    | Topr                                                                       | -30  to  +                                            |              |                                      |  |  |  |  |

| Storage Temperature                                                                                                                      | Tstg                                                                       | - 55 to + 1                                           |              |                                      |  |  |  |  |

| (Note) The LSI should be used                                                                                                            | l on the condition that ${f AV}_{ m I}$                                    | $_{\rm D} = {\rm DV}_{\rm DD}$ and ${\rm AV}_{\rm S}$ | $s_1 = AV_S$ | $_{S2} = DV_{SS}.$                   |  |  |  |  |

| Allowable Operating Conditions at $Ta = -30$ to $+70^{\circ}$ C, $V_{SS} = 0$ V                                                          |                                                                            |                                                       |              |                                      |  |  |  |  |

|                                                                                                                                          |                                                                            | min typ max                                           | unit         | Applicable pins                      |  |  |  |  |

| Supply Voltage                                                                                                                           | V <sub>DD</sub>                                                            | 4.5 5.0 5.5                                           | V            | AV <sub>DD</sub> ,DV <sub>DD</sub>   |  |  |  |  |

| Analog Input Voltage                                                                                                                     | VINA                                                                       | $V_{DD} - V_{RB}$                                     |              | AY,AR,AB                             |  |  |  |  |

| Digital Input Voltage                                                                                                                    |                                                                            | .7V <sub>DD</sub>                                     | V            | CLK,SY,SR,                           |  |  |  |  |

|                                                                                                                                          | V <sub>ILD</sub>                                                           | 0.3V)                                                 |              | SB,CLAMP                             |  |  |  |  |

| Sampling Clock                                                                                                                           | fCLK                                                                       |                                                       | MHz          | CLK                                  |  |  |  |  |

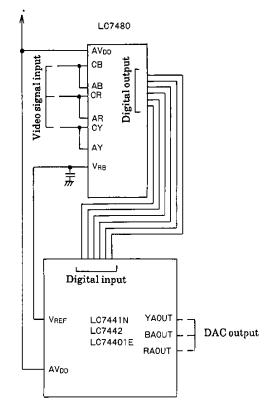

| Sampling Clock Pulse Width                                                                                                               | t <sub>CLKH</sub> (H level)                                                | 25.0                                                  | ns           | CLK                                  |  |  |  |  |

| Clamp Pulse Width                                                                                                                        | t <sub>CLKL</sub> (L level)                                                | 25.0                                                  | ns           | CLK                                  |  |  |  |  |

| MPX Set up                                                                                                                               | t <sub>CLPH</sub> (H level)                                                | 2.0<br>25.0                                           | μs           | CLAMP<br>SY,SR,SB                    |  |  |  |  |

| MPX Hold                                                                                                                                 | t <sub>MSU</sub><br>t <sub>MHD</sub>                                       | 0.0                                                   | ns<br>ns     | SY,SR,SB                             |  |  |  |  |

| MPX Off                                                                                                                                  | t <sub>MOFF</sub>                                                          | 0.0                                                   | ns           | SY,SR,SB                             |  |  |  |  |

|                                                                                                                                          |                                                                            |                                                       |              |                                      |  |  |  |  |

| Electrical Characteristics at 7                                                                                                          | $Ta = 25 \pm 2^{\circ}C, V_{DD} = 5V \pm 10^{\circ}$                       | $0\%, V_{\rm SS} = 0V$                                |              |                                      |  |  |  |  |

| •                                                                                                                                        |                                                                            | min typ max                                           | unit         | Applicable pins .                    |  |  |  |  |

| Power Dissipation (Analog)                                                                                                               | $I_{DD}A V_{DD} = 5V$ ,                                                    | 20.0                                                  | mA           | AV <sub>DD</sub>                     |  |  |  |  |

| Power Dissipation (Digital)                                                                                                              | $I_{DD}D$ $f_{CLK} = 14.3 MHz$ ,                                           | 7.0                                                   | mA           | DV <sub>DD</sub>                     |  |  |  |  |

|                                                                                                                                          | input signal = 3.5                                                         | BMHz                                                  |              |                                      |  |  |  |  |

|                                                                                                                                          | (sine wave)                                                                |                                                       | •••          |                                      |  |  |  |  |

| Resolution                                                                                                                               | CINI                                                                       | 6.0                                                   |              |                                      |  |  |  |  |

| Linearity Error                                                                                                                          | SINL                                                                       | $\pm 1/2$                                             |              |                                      |  |  |  |  |

| Differential Linearity Error<br>Reference Voltage (M)                                                                                    | SDNL                                                                       | ± 1/2                                                 | LSB<br>V     | V                                    |  |  |  |  |

| Reference Voltage (B)                                                                                                                    | V <sub>RM</sub>                                                            | 0.9V <sub>DD</sub><br>0.8V <sub>DD</sub>              | v<br>V       | V <sub>RM</sub>                      |  |  |  |  |

| Digital Output Voltage                                                                                                                   | V <sub>RB</sub>                                                            |                                                       | v<br>V       | V <sub>RB</sub><br>[AD0 to AD5       |  |  |  |  |

| Digital Output Voltage                                                                                                                   | $V_{OH}$ $I_0 = -1.6 \text{mA}$ $V_{I}$<br>$V_{OL}$ $I_0 = +1.6 \text{mA}$ | 0.4                                                   |              |                                      |  |  |  |  |

|                                                                                                                                          |                                                                            |                                                       |              |                                      |  |  |  |  |

| Switching Characteristics at $Ta = 25 \pm 2^{\circ}C$ , $V_{DD} = 5V \pm 10^{\circ}$ , $V_{SS} = 0V$<br>min typ max unit Applicable pins |                                                                            |                                                       |              |                                      |  |  |  |  |

| Digital Output Delay Time                                                                                                                | t <sub>Pd</sub> Load capacitance                                           | - V I                                                 |              | Applicable pins                      |  |  |  |  |

|                                                                                                                                          | -La mana onhacionico                                                       |                                                       | 115          |                                      |  |  |  |  |

|                                                                                                                                          |                                                                            |                                                       |              |                                      |  |  |  |  |

|                                                                                                                                          |                                                                            |                                                       |              |                                      |  |  |  |  |

.

### **Output Code Example**

| STEP | Analog Input<br>Voltage (V) |               | Digital I/O Code | AOUT<br>(V) |

|------|-----------------------------|---------------|------------------|-------------|

| 0    | 3.992                       | 4.000         | 000000           | 3.992       |

| 1    | 4.000                       | 4.016         | 000001           | 4.008       |

| 2    | 4.016                       | 4.032         | 000010           | 4.024       |

|      |                             |               |                  |             |

| 31   | 4.480                       | 4.496         | 011111           | 4.488       |

| 32   | 4.496                       | 4.512         | 100000           | 4.504       |

| 33   | 33 4.512 4.                 |               | 100001           | 4.520       |

|      |                             |               |                  |             |

| 61   | 4.960                       | 4.976         | 111101           | 4.968       |

| 62   | 4.976                       | <b>4.9</b> 92 | 111110           | 4.984       |

| 63   | 4.992                       | 5.000         | 111111           | 5.000       |

$V_{DD} = 5.000V, V_{RB} = V_{REF} = 3.992V$

1LSB = 16mV

# **Timing Chart**

.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- This catalog provides information as of June, 1996. Specifications and information herein are subject to change without notice.