## **INTEGRATED CIRCUITS**

# DATA SHEET

For a complete data sheet, please also download:

- The IC04 LOCMOS HE4000B Logic Family Specifications HEF, HEC

- The IC04 LOCMOS HE4000B Logic Package Outlines/Information HEF, HEC

# HEF4000B gates Dual 3-input NOR gate and inverter

Product specification

File under Integrated Circuits, IC04

January 1995

## **Dual 3-input NOR gate and inverter**

HEF4000B gates

## **DESCRIPTION**

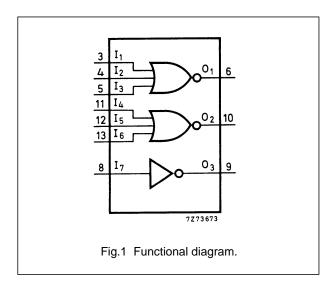

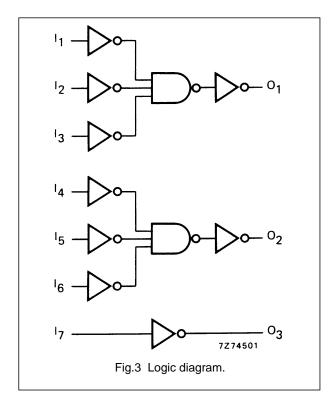

The HEF4000B provides the positive dual 3-input NOR function. A single stage inverting function with standard output performance is also accomplished. The outputs are fully buffered for highest noise immunity and pattern insensitivity of output impedance.

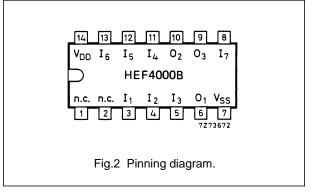

HEF4000BP(N): 14-lead DIL; plastic

(SOT27-1)

HEF4000BD(F): 14-lead DIL; ceramic (cerdip)

(SOT73)

HEF4000BT(D): 14-lead SO; plastic

(SOT108-1)

(): Package Designator North America

#### FAMILY DATA, IDD LIMITS category GATES

See Family Specifications

Philips Semiconductors Product specification

# Dual 3-input NOR gate and inverter

HEF4000B gates

## DC CHARACTERISTICS

For the single inverter stage  $(I_7/O_3)$ :

see Family Specifications for input voltages HIGH and LOW (unbuffered stages only).

## **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                                     | V <sub>DD</sub> | SYMBOL                              | TYP. | MAX. |    | TYPICAL EXTRAPOLATION FORMULA       |

|-------------------------------------|-----------------|-------------------------------------|------|------|----|-------------------------------------|

| Propagation delays                  | 5               |                                     | 70   | 140  | ns | 43 ns + (0,55 ns/pF) C <sub>L</sub> |

| $I_1$ to $I_6 \rightarrow O_1, O_2$ | 10              | t <sub>PHL</sub> ; t <sub>PLH</sub> | 35   | 70   | ns | 24 ns + (0,23 ns/pF) C <sub>L</sub> |

|                                     | 15              |                                     | 30   | 55   | ns | 22 ns + (0,16 ns/pF) C <sub>L</sub> |

|                                     | 5               |                                     | 45   | 90   | ns | 18 ns + (0,55 ns/pF) C <sub>L</sub> |

| $I_7 \rightarrow O_3$               | 10              | t <sub>PHL</sub> ; t <sub>PLH</sub> | 25   | 50   | ns | 14 ns + (0,23 ns/pF) C <sub>L</sub> |

| (unbuffered output)                 | 15              |                                     | 20   | 40   | ns | 12 ns + (0,16 ns/pF) C <sub>L</sub> |

| Output transition times             | 5               |                                     | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |

| HIGH to LOW                         | 10              | t <sub>THL</sub>                    | 30   | 60   | ns | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |

|                                     | 15              |                                     | 20   | 40   | ns | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |

|                                     | 5               |                                     | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |

| LOW to HIGH                         | 10              | t <sub>TLH</sub>                    | 30   | 60   | ns | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |

|                                     | 15              |                                     | 20   | 40   | ns | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |

|                 | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P (μW)                    |                                         |

|-----------------|----------------------|-----------------------------------------------|-----------------------------------------|

| Dynamic power   | 5                    | 1 000 $f_i + \sum (f_o C_L) \times V_{DD}^2$  | where                                   |

| dissipation per | 10                   | $7 700 f_i + \sum (f_o C_L) \times V_{DD}^2$  | $f_i$ = input freq. (MHz)               |

| package (P)     | 15                   | 28 700 $f_i + \sum (f_o C_L) \times V_{DD}^2$ | $f_0$ = output freq. (MHz)              |

|                 |                      |                                               | C <sub>L</sub> = load capacitance (pF)  |

|                 |                      |                                               | $\sum (f_0C_L) = \text{sum of outputs}$ |

|                 |                      |                                               | V <sub>DD</sub> = supply voltage (V)    |

## Dual 3-input NOR gate and inverter

**HEF4000B** gates

## **APPLICATION INFORMATION**

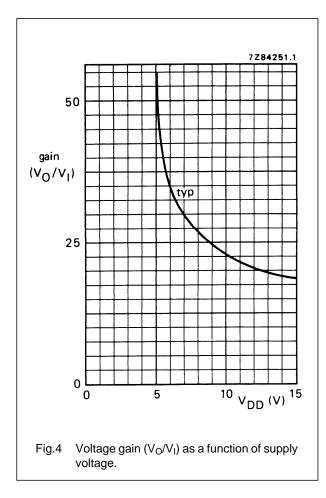

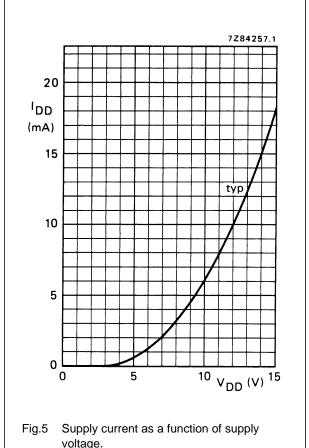

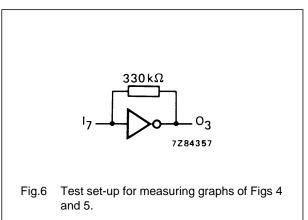

The following information (Figs 4 to 7) is only for the single inverter stage (I<sub>7</sub>/O<sub>3</sub>).

voltage.

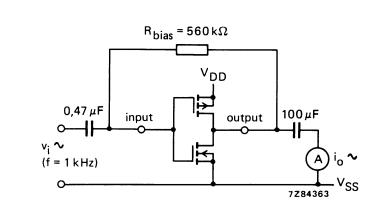

This is also an example of an analogue amplifier using the single inverter stage (I<sub>7</sub>/O<sub>3</sub>) of the HEF4000B.

## Dual 3-input NOR gate and inverter

HEF4000B gates

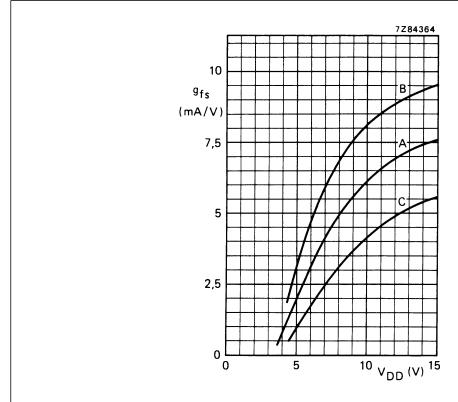

Fig.7 Test set-up for measuring forward transconductance  $g_{fs} = di_0/dv_i$  at  $v_0$  is constant (see also graph Fig.8).

A: average

B: average + 2 s,

C: average -2 s, in where 's' is the observed standard deviation.

Fig.8 Typical forward transconductance  $g_{fs}$  as a function of the supply voltage at  $T_{amb}$  = 25 °C.