# S1D13305 Series Technical Manual

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

- \* In this manual, Zilog's Z80-CPU or its equivalent shall be called Z80, Intel's 8085A or its equivalent shall be called 8085 and Motorola's MC6809 and MC6802 or their equivalents shall be called 6809 and 6802, respectively.

- ® stands for registered trade mark.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective owners.

© Seiko Epson Corporation 2001 All rights reserved.

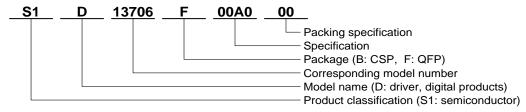

# The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

# Configuration of product number

#### Devices

#### Evaluation Board

# Comparison table between new and previous number

#### • S1D13305 Series

| Previous No.   | New No.         |

|----------------|-----------------|

| SED1335 Series | S1D13305 Series |

| SED1335D0A     | S1D13305D00A    |

| SED1335F0A     | S1D13305F00A    |

| SED1335F0B     | S1D13305F00B    |

#### • S1D1350x Series

| Previous No.   | New No.         |

|----------------|-----------------|

| SED135x Series | S1D1350x Series |

| SED1353D0A     | S1D13503D00A    |

| SED1353F0A     | S1D13503F00A    |

| SED1353F1A     | S1D13503F01A    |

| SED1354F0A     | S1D13504F00A    |

| SED1354F1A     | S1D13504F01A    |

| SED1354F2A     | S1D13504F02A    |

| SED1355F0A     | S1D13505F00A    |

| SED1356F0A     | S1D13506F00A    |

#### • S1D1370x Series

| Previous No.                 | New No.                         |  |

|------------------------------|---------------------------------|--|

| SED137x Series<br>SED1374F0A | S1D1370x Series<br>S1D13704F00A |  |

| SED1375F0A                   | S1D13705F00A                    |  |

| SED1376B0A<br>SED1376F0A     | S1D13706B00A<br>S1D13706F00A    |  |

| SED1378 Series               | S1D13708 Series                 |  |

#### • S1D13A0x Series

| Previous No.                               | New No.                                         |

|--------------------------------------------|-------------------------------------------------|

| SED13Ax Series<br>SED13A3F0A<br>SED13A3B0B | S1D13A0x Series<br>S1D13A03F00A<br>S1D13A03B00B |

| SED13A4B0B                                 | S1D13A04B00B                                    |

#### • S1D1380x Series

| New No.                         |

|---------------------------------|

| S1D1380x Series<br>S1D13806F00A |

|                                 |

# Comparison table between new and previous number of Evaluation Boards

#### • S1D1350x Series

| Previous No. | New No.      |

|--------------|--------------|

| SDU1353#0C   | S5U13503P00C |

| SDU1354#0C   | S5U13504P00C |

| SDU1355#0C   | S5U13505P00C |

| SDU1356#0C   | S5U13506P00C |

#### • S1D1370x Series

| Previous No.             | New No.                      |

|--------------------------|------------------------------|

| SDU1374#0C               | S5U13704P00C                 |

| SDU1375#0C               | S5U13705P00C                 |

| SDU1376#0C<br>SDU1376BVR | S5U13706P00C<br>S5U13706B32R |

| SDU1378#0C               | S5U13708P00C                 |

#### • S1D13A0x Series

| Previous No. | New No.      |

|--------------|--------------|

| SDU13A3#0C   | S5U13A03P00C |

| SDU13A4#0C   | S5U13A04P00C |

#### • S1D1380x Series

| Previous No. | New No.      |

|--------------|--------------|

| SDU1386#0C   | S5U13806P00C |

# **CONTENTS**

| 1.         | OVE               | RVIEW                                    | 1  |  |  |

|------------|-------------------|------------------------------------------|----|--|--|

| 2.         | FEATURES          |                                          |    |  |  |

| 3.         | BLOCK DIAGRAM     |                                          |    |  |  |

| 4. PINOUTS |                   |                                          |    |  |  |

| 5.         | PIN DESCRIPTION   |                                          |    |  |  |

|            | 5.1.              | S1D13305F00A/00B Pin Summary             | 4  |  |  |

|            | 5.2.              | Pin Functions                            |    |  |  |

|            |                   | 5.2.1. Power supply                      |    |  |  |

|            |                   | 5.2.2. Oscillator                        |    |  |  |

|            |                   | 5.2.3. Microprocessor interface          |    |  |  |

|            |                   | 5.2.5. LCD drive signals                 |    |  |  |

| 6          | SPEC              | CIFICATIONS                              |    |  |  |

| 0.         |                   | Absolute Maximum Ratings                 |    |  |  |

|            |                   | S1D13305                                 |    |  |  |

|            | 6.3.              | S1D13305F Timing Diagrams                |    |  |  |

|            | 0.0.              | 6.3.1. 8080 family interface timing      |    |  |  |

|            |                   | 6.3.2. 6800 family interface timing      |    |  |  |

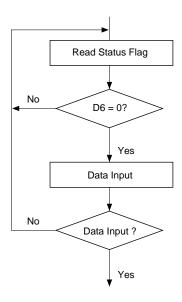

|            |                   | 6.3.3. Display memory read timing        |    |  |  |

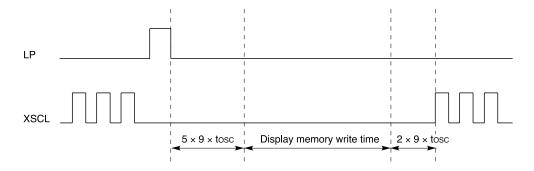

|            |                   | 6.3.4. Display memory write timing       |    |  |  |

|            |                   | 6.3.6. External oscillator signal timing |    |  |  |

|            |                   | 6.3.7. LCD output timing                 |    |  |  |

| 7.         | PAC               | (AGE DIMENSIONS                          | 19 |  |  |

|            | 7.1. S1D13305F00A |                                          |    |  |  |

|            | 7.2.              | S1D13305F00B                             | 19 |  |  |

| 8.         | INSTRUCTION SET   |                                          |    |  |  |

|            | 8.1.              | The Command Set                          | 20 |  |  |

|            | 8.2.              | System Control Commands                  | 21 |  |  |

|            |                   | 8.2.1. SYSTEM SET                        |    |  |  |

|            |                   | 8.2.1.1. C                               |    |  |  |

|            |                   | 8.2.1.2. M0<br>8.2.1.3. M1               |    |  |  |

|            |                   | 8.2.1.4. M2                              |    |  |  |

|            |                   | 8.2.1.5. W/S                             |    |  |  |

|            |                   | 8.2.1.6. IV                              |    |  |  |

|            |                   | 8.2.1.7. FX<br>8.2.1.8. WF               |    |  |  |

|            |                   | 8.2.1.9. FY                              |    |  |  |

|            |                   | 8.2.1.10. C/R                            | 25 |  |  |

|            |                   | 8.2.1.11. TC/R                           |    |  |  |

|            |                   | 8.2.1.12. L/F<br>8.2.1.13. AP            |    |  |  |

|            |                   | 8.2.2. SLEEP IN                          |    |  |  |

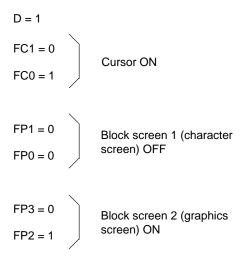

|            | 8.3.              | Display Control Commands                 | 28 |  |  |

|            |                   | 8.3.1. DISP ON/OFF                       |    |  |  |

|            | ;                 | 8.3.1.1. D                               | _  |  |  |

|            |                   | 8.3.1.2. FC                              |    |  |  |

|            |                   | 8.3.2. SCROLL                            |    |  |  |

|            |                   | 8.3.2.1. C                               | 29 |  |  |

|            |                   | 8.3.2.2. SL1, SL2                        | 30 |  |  |

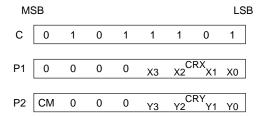

|    |       | 8.3.3.  | CSRFORM                          |    |

|----|-------|---------|----------------------------------|----|

|    |       |         | 8.3.3.1. CRX                     |    |

|    |       |         | 8.3.3.3. CM                      |    |

|    |       | 8.3.4.  | CSRDIR                           |    |

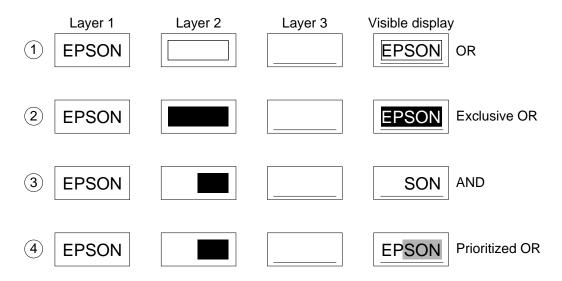

|    |       | 8.3.5.  | OVLAY                            |    |

|    |       |         | 8.3.5.1. MX0, MX1                |    |

|    |       |         | 8.3.5.2. DM1, DM2                |    |

|    |       | 8.3.6.  | CGRAM ADR                        |    |

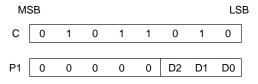

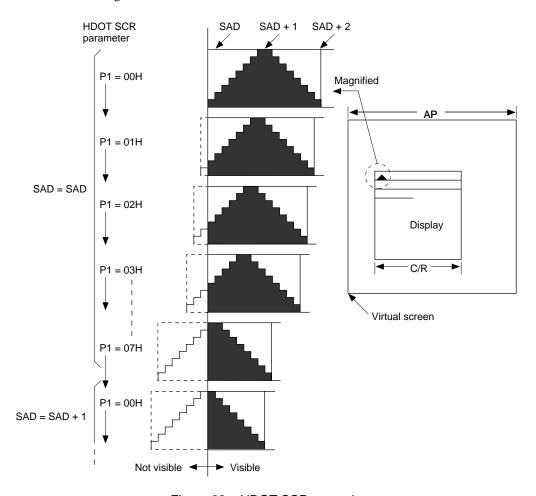

|    |       | 8.3.7.  | HDOT SCR                         | 37 |

|    |       |         | 8.3.7.1. D0 to D2                |    |

|    | 8.4.  |         | g Control Commands               |    |

|    |       |         | CSRW                             |    |

|    | 8.5.  |         | y Control Commands               |    |

|    | 0.0.  |         | MWRITE                           |    |

|    |       | 8.5.2   | MREAD                            | 39 |

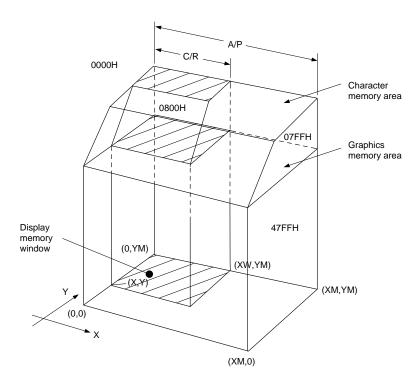

| 9. | DISP  | LAY CO  | NTROL FUNCTIONS                  | 40 |

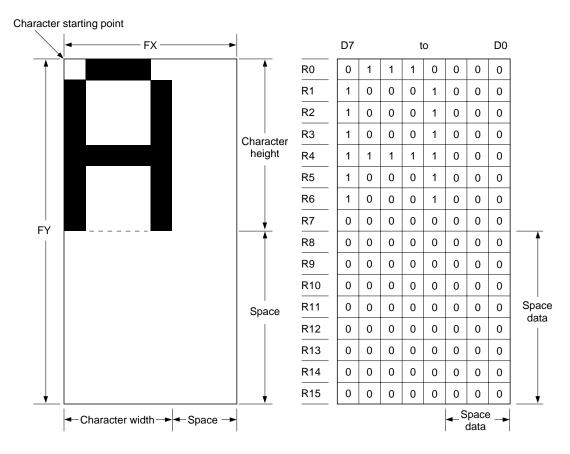

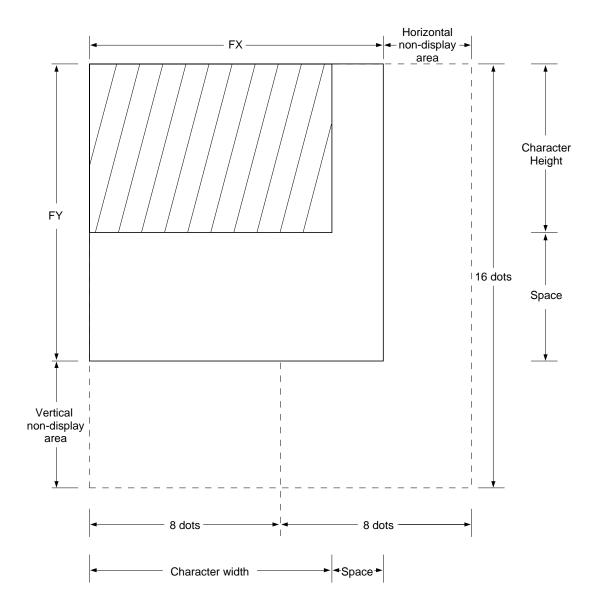

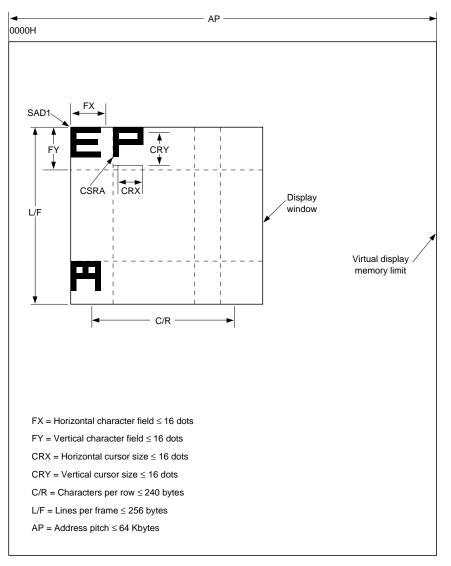

|    | 9.1.  | Charac  | ter Configuration                | 40 |

|    | 9.2.  |         | Configuration                    |    |

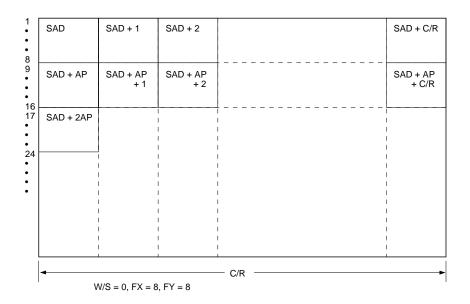

|    |       |         | Screen configuration             |    |

|    |       |         | Display address scanning         |    |

|    | 9.3   |         | Control                          |    |

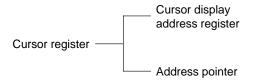

|    | 0.0.  |         | Cursor register function         |    |

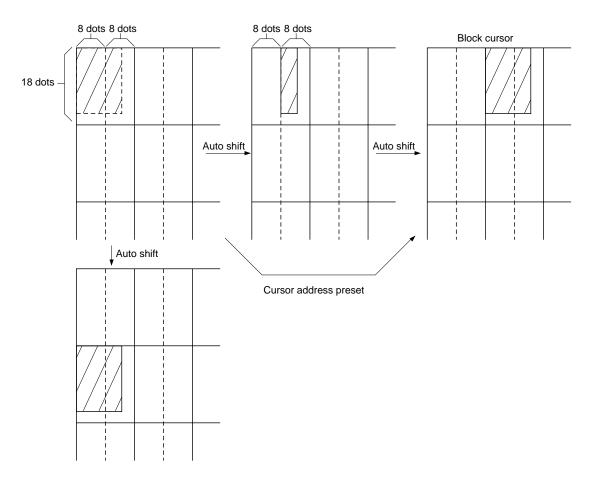

|    |       |         | Cursor movement                  |    |

|    |       |         | Cursor display layers            |    |

|    | 9.4.  |         | y to Display Relationship        |    |

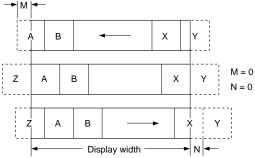

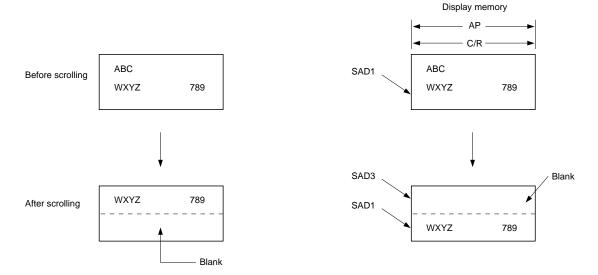

|    | 9.5.  |         | ogOn-page scrolling              |    |

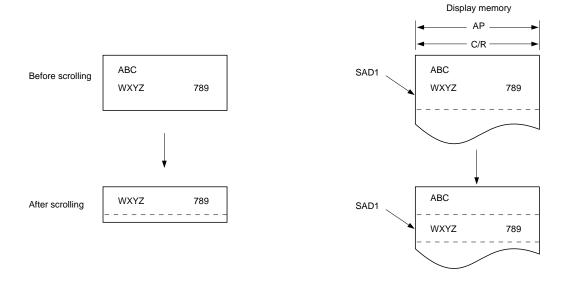

|    |       |         | Inter-page scrolling             |    |

|    |       |         | Horizontal scrolling             |    |

|    |       |         | Bidirectional scrolling          |    |

|    |       |         | Scroll units                     |    |

|    |       |         | R GENERATOR                      |    |

|    | 10.1. |         | aracteristics                    |    |

|    |       |         | Internal character generator     |    |

|    |       |         | Character generator RAM          |    |

|    | 10.2. | CG Me   | mory Allocation                  | 55 |

|    | 10.3. | Setting | the Character Generator Address  | 56 |

|    |       |         | M1 = 1                           |    |

|    |       |         | CG RAM addressing example        |    |

|    |       |         | ter Codes                        |    |

|    |       |         | CESSOR INTERFACE                 |    |

|    | 11.1. | •       | Bus Interface                    |    |

|    |       |         | 8080 series                      |    |

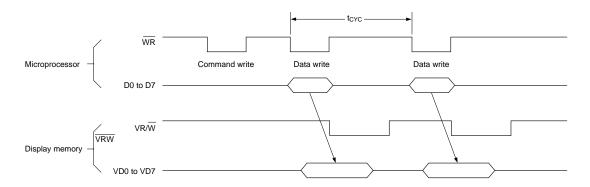

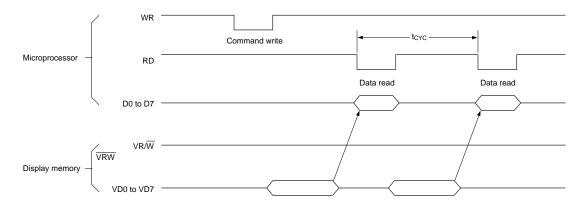

|    | 11 2  |         | rocessor Synchronization         |    |

|    |       | -       | Display status indication output |    |

|    |       |         | Internal register access         |    |

|    |       |         | Display memory access            |    |

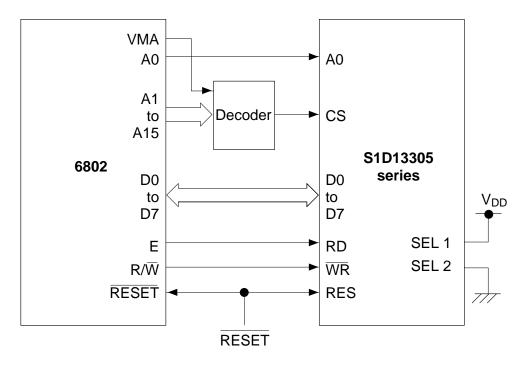

|    | 11.3. |         | ce Examples                      |    |

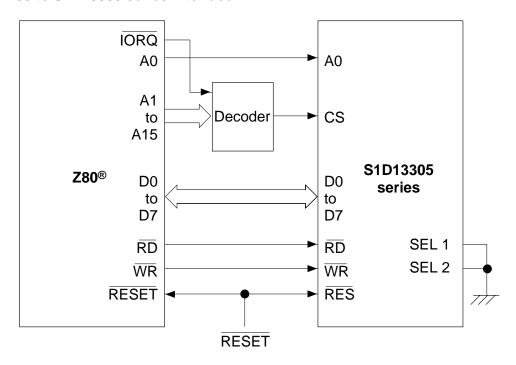

|    |       |         | Z80 to S1D13305 series interface | 61 |

ii

$Downloaded \ from \ \underline{Elcodis.com} \ \ electronic \ components \ distributor$

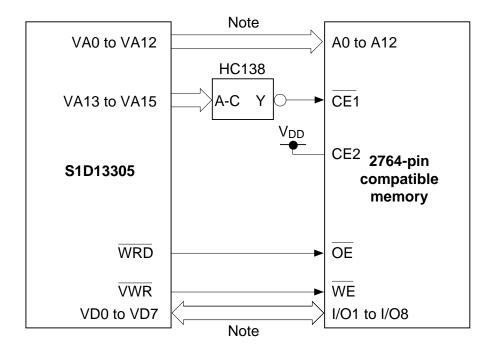

| 12. DISPLAY MEMORY INTERFACE                                            | 62 |

|-------------------------------------------------------------------------|----|

| 12.1. Static RAM                                                        |    |

| 12.2. Supply Current during Display Memory Access                       |    |

| 13. OSCILLATOR CIRCUIT                                                  | 63 |

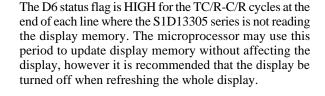

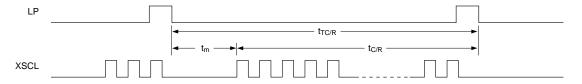

| 14. STATUS FLAG                                                         | 63 |

| 15. RESET                                                               | 65 |

| 16. APPLICATION NOTES                                                   | 65 |

| 16.1. Initialization Parameters                                         |    |

| 16.1.1. SYSTEM SET instruction and parameters                           |    |

| 16.1.2. Initialization example                                          |    |

| 16.1.3. Display mode setting example 1: combining text and graphics     |    |

| 16.1.4. Display mode setting example 2: combining graphics and graphics |    |

| 16.1.5. Display mode setting example 3: combining three graphics layers | 75 |

| 16.2. System Overview                                                   | 76 |

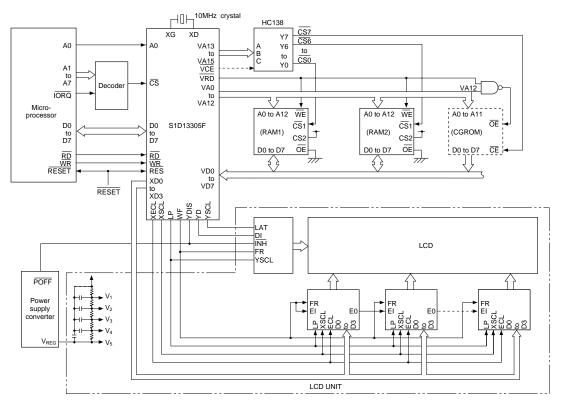

| 16.3 System Interconnection                                             | 77 |

| 16.3.1. S1D13305F                                                       | 77 |

| 16.4. Smooth Horizontal Scrolling                                       | 79 |

| 16.5. Layered Display Attributes                                        | 80 |

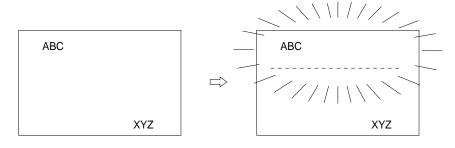

| 16.5.1. Inverse display                                                 | 80 |

| 16.5.2. Half-tone display                                               | 80 |

| 16.5.2.1. Menu pad display                                              |    |

| 16.5.2.2. Graph display                                                 |    |

| 16.5.3. Flashing areas                                                  |    |

| 16.5.3.1. Small area                                                    |    |

| 16.5.3.2. Large area                                                    |    |

| 16.6. 16 × 16-dot Graphic Display                                       |    |

| 16.6.1. Command usage                                                   |    |

| 16.6.2. Kanji character display                                         |    |

| 17. INTERNAL CHARACTER GENERATOR FONT                                   |    |

| 18. GLOSSARY OF TERMS                                                   |    |

| Request for Information on S1D13305 Series                              | 86 |

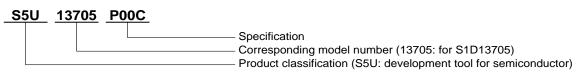

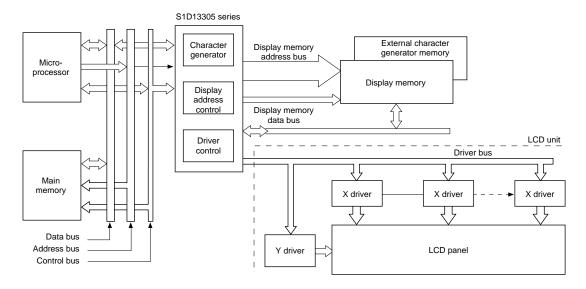

#### 1. OVERVIEW

The S1D13305 series is a controller IC that can display text and graphics on LCD panel.

The S1D13305 series can display layered text and graphics, scroll the display in any direction and partition the display into multiple screens.

The S1D13305 series stores text, character codes and bitmapped graphics data in external frame buffer memory. Display controller functions include transferring data from the controlling microprocessor to the buffer memory, reading memory data, converting data to display pixels and generating timing signals for the buffer memory, LCD panel.

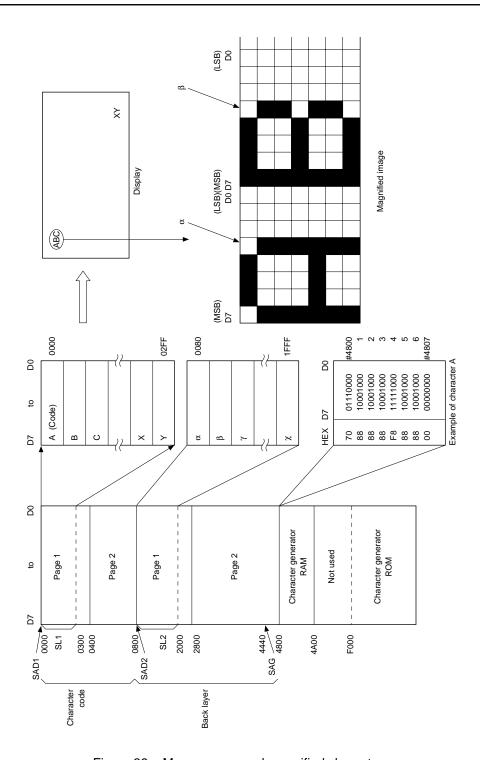

The S1D13305 series has an internal character generator with 160,  $5 \times 7$  pixel characters in internal mask ROM. The character generators support up to 64,  $8 \times 16$  pixel characters in external character generator RAM and up to 256,  $8 \times 16$  pixel characters in external character generator ROM.

#### 2. FEATURES

- Text, graphics and combined text/graphics display modes

- Three overlapping screens in graphics mode

- Up to  $640 \times 256$  pixel LCD panel display resolution

- Programmable cursor control

- Smooth horizontal and vertical scrolling of all or part of the display

- 1/2-duty to 1/256-duty LCD drive

- Up to 640 × 256 pixel LCD panel display resolution memory

- 160, 5 × 7 pixel characters in internal mask-programmed character generator ROM

- Up to 64, 8 × 16 pixel characters in external character generator RAM

- Up to 256, 8 × 16 pixel characters in external character generator ROM

- 6800 and 8080 family microprocessor interfaces

- Low power consumption—3.5 mA operating current (VDD = 3.5V), 0.05 μA standby current

- Package

| line-up      | Package     |

|--------------|-------------|

| S1D13305F00A | QFP5-60 pin |

| S1D13305F00B | QFP6-60 pin |

• 2.7 to 5.5 V (S1D13305F)

# 3. BLOCK DIAGRAM

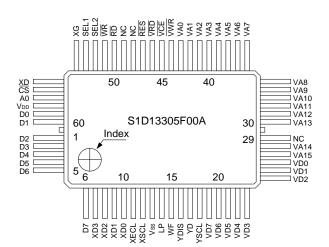

# 4. PINOUTS

♦S1D13305F00A

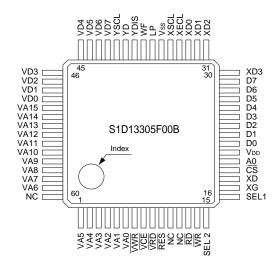

#### ♦S1D13305F00B

# 5. PIN DESCRIPTION

# 5.1. S1D13305F00A/00B Pin Summary

| Name        | Nun                  | nber               | <b>T</b>     | Description                                               |  |  |

|-------------|----------------------|--------------------|--------------|-----------------------------------------------------------|--|--|

| Name        | S1D13305F00A         | S1D13305F00B       | Туре         | Description                                               |  |  |

| VA0 to VA15 | 27 to 28<br>30 to 43 | 1 to 6<br>50 to 59 | Output       | VRAM address bus                                          |  |  |

| VWR         | 44                   | 7                  | Output       | VRAM write signal                                         |  |  |

| VCE         | 45                   | 8                  | Output       | Memory control signal                                     |  |  |

| VRD         | 46                   | 9                  | Output       | VRAM read signal                                          |  |  |

| RES         | 47                   | 10                 | Input        | Reset                                                     |  |  |

| NC          | 28, 48, 49           | 11, 12, 60         | _            | No connection                                             |  |  |

| RD          | 50                   | 13                 | Input        | 8080 family: Read signal<br>6800 family: Enable clock (E) |  |  |

| WR          | 51                   | 14                 | Input        | 8080 family: Write signal 6800 family: R/W signal         |  |  |

| SEL2        | 52                   | 15                 | Input        | 8080 or 6800 family interface select                      |  |  |

| SEL1        | 53                   | 16                 | Input        | 8080 or 6800 family interface select                      |  |  |

| XG          | 54                   | 17                 | Input        | Oscillator connection                                     |  |  |

| XD          | 55                   | 18                 | Output       | Oscillator connection                                     |  |  |

| CS          | 56                   | 19                 | Input        | Chip select                                               |  |  |

| A0          | 57                   | 20                 | Input        | Data type select                                          |  |  |

| VDD         | 58                   | 21                 | Supply       | 2.7 to 5.5V supply                                        |  |  |

| D0 to D7    | 59 to 60<br>1 to 6   | 22 to 29           | Input/output | Data bus                                                  |  |  |

| XD0 to XD3  | 7 to 10              | 30 to 33           | Output       | X-driver data                                             |  |  |

| XECL        | 11                   | 34                 | Output       | X-driver enable chain clock                               |  |  |

| XSCL        | 12                   | 35                 | Output       | X-driver data shift clock                                 |  |  |

| Vss         | 13                   | 36                 | Supply       | Ground                                                    |  |  |

| LP          | 14                   | 37                 | Output       | Latch pulse                                               |  |  |

| WF          | 15                   | 38                 | Output       | Frame signal                                              |  |  |

| YDIS        | 16                   | 39                 | Output       | Power-down signal when display is blanked                 |  |  |

| YD          | 17                   | 40                 | Output       | Scan start pulse                                          |  |  |

| YSCL        | 18                   | 41                 | Output       | Y-driver shift clock                                      |  |  |

| VD0 to VD7  | 19 to 26             | 42 to 49           | Input/output | VRAM data bus                                             |  |  |

### 5.2. Pin Functions

# 5.2.1. Power supply

| Pin Name | Function                                                                            |

|----------|-------------------------------------------------------------------------------------|

| VDD      | 2.7 to 5.5V supply.  This may be the same supply as the controlling microprocessor. |

| Vss      | Ground                                                                              |

Note: The peak supply current drawn by the S1D13305 series may be up to ten times the average supply current. The power supply impedance must be kept as low as possible by ensuring that supply lines are sufficiently wide and by placing 0.47 μF decoupling capacitors that have good high-frequency response near the device's supply pins.

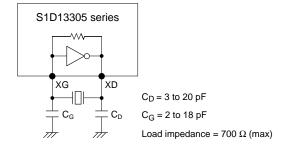

#### 5.2.2. Oscillator

| Pin Name | Function                                                                                                                                                                                                 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XG       | Crystal connection for internal oscillator (See section 13). This pin can be driven by an external clock source that satisfies the timing specifications of the EXT $\phi$ 0 signal (See section 6.3.6). |

| XD       | Crystal connection for internal oscillator. Leave this pin open when using an external clock source.                                                                                                     |

#### 5.2.3. Microprocessor interface

| Pin Name   | Function                    |                                                                                                                                                                                   |           |    |    |     |    |  |  |  |  |

|------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----|----|-----|----|--|--|--|--|

| D0 to D7   | Tristate input/c            | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus.                                                                                             |           |    |    |     |    |  |  |  |  |

| 0514 0510  |                             | Microprocessor interface select pin. The S1D13305 series supports both 8080 family processors (such as the 8085 and Z80®) and 6800 family processors (such as the 6802 and 6809). |           |    |    |     |    |  |  |  |  |

| SEL1, SEL2 | SEL1                        | SEL2*                                                                                                                                                                             | Interface | A0 | RD | WR  | CS |  |  |  |  |

|            | 0 0 8080 family A0 RD WR CS |                                                                                                                                                                                   |           |    |    |     |    |  |  |  |  |

|            | 1 0 6800 family A0 E R/W    |                                                                                                                                                                                   |           |    |    | R/W | CS |  |  |  |  |

|            | "                           |                                                                                                                                                                                   |           |    |    |     |    |  |  |  |  |

**Note:** SEL1 should be tied directly to VDD or Vss to prevent noise. If noise does appear on SEL1, decouple it to ground using a capacitor placed as close to the pin as possible.

| Pin Name  | Function                                                                                                                                                                                                                  |                                                                                                                                                                                                                                       |     |                                      |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------|--|--|--|

|           | 8080 fam                                                                                                                                                                                                                  | ily interfa                                                                                                                                                                                                                           | ice |                                      |  |  |  |

|           | A0                                                                                                                                                                                                                        | RD                                                                                                                                                                                                                                    | WR  | Function                             |  |  |  |

|           | 0                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                     | 1   | Status flag read                     |  |  |  |

|           | 1                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                     | 1   | Display data and cursor address read |  |  |  |

|           | 0                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                     | 0   | Display data and parameter write     |  |  |  |

| A0        | 1                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                     | 0   | Command write                        |  |  |  |

|           |                                                                                                                                                                                                                           | nily interfa                                                                                                                                                                                                                          |     |                                      |  |  |  |

|           | A0                                                                                                                                                                                                                        | R/W                                                                                                                                                                                                                                   | Е   | Function                             |  |  |  |

|           | 0                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                     | 1   | Status flag read                     |  |  |  |

|           | 1                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                     | 1   | Display data and cursor address read |  |  |  |

|           | 0                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                     | 1   | Display data and parameter write     |  |  |  |

|           | 1                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                     | 1   | Command write                        |  |  |  |

| RD or E   | When the 8080 family interface is selected, this signal acts as the active-LOW read strobe. The S1D13305 series output buffers are enabled when this signal is active.                                                    |                                                                                                                                                                                                                                       |     |                                      |  |  |  |

| KD 01 E   | When the 6800 family interface is selected, this signal acts as the active-HIGH enable clock. Data is read from or written to the S1D13305 series when this clock goes HIGH.                                              |                                                                                                                                                                                                                                       |     |                                      |  |  |  |

|           | When the 8080 family interface is selected, this signal acts as the active-LOW write strobe. The bus data is latched on the rising edge of this signal.                                                                   |                                                                                                                                                                                                                                       |     |                                      |  |  |  |

| WR or R/W | When the 6800 family interface is selected, this signal acts as the read/write control signal. Data is read from the S1D13305 series if this signal is HIGH, and written to the S1D13305 series if it is LOW.             |                                                                                                                                                                                                                                       |     |                                      |  |  |  |

| CS        | Chip select. This active-LOW input enables the S1D13305 series. It is usually connected to the output of an address decoder device that maps the S1D13305 series into the memory space of the controlling microprocessor. |                                                                                                                                                                                                                                       |     |                                      |  |  |  |

| RES       | Schmitt-ti                                                                                                                                                                                                                | This active-LOW input performs a hardware reset on the S1D13305 series. It is a Schmitt-trigger input for enhanced noise immunity; however, care should be taken to ensure that it is not triggered if the supply voltage is lowered. |     |                                      |  |  |  |

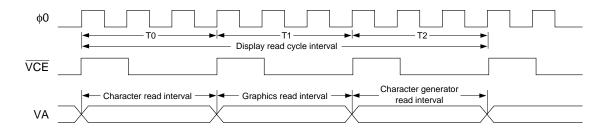

# 5.2.4. Display memory control

The S1D13305 series can directly access static RAM and PROM. The designer may use a mixture of these two

types of memory to achieve an optimum trade-off between low cost and low power consumption.

| Pin Name    | Function                                                                                                                                                 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| VA0 to VA15 | 16-bit display memory address. When accessing character generator RAM or ROM, VA0 to VA3, reflect the lower 4 bits of the S1D13305 series's row counter. |

| VD0 to VD7  | 8-bit tristate display memory data bus. These pins are enabled when $VR/\overline{W}$ is LOW.                                                            |

| VWR         | Active-LOW display memory write control output.                                                                                                          |

| VRD         | Active-LOW display memory read control output.                                                                                                           |

| VCE         | Active-LOW static memory standby control signal. $\overline{\text{VCE}}$ can be used with $\overline{\text{CS}}$ .                                       |

#### 5.2.5. LCD drive signals

In order to provide effective low-power drive for LCD matrixes, the S1D13305 series can directly control both the X- and Y-drivers using an enable chain.

| Pin Name   | Function                                                                                                                                                                                                                                                                                                                                                           |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XD0 to XD3 | 4-bit X-driver (column drive) data outputs. Connect these outputs to the inputs of the X-driver chips.                                                                                                                                                                                                                                                             |

| XSCL       | The falling edge of XSCL latches the data on XD0 to XD3 into the input shift registers of the X-drivers. To conserve power, this clock halts between LP and the start of the following display line (See section 6.3.7).                                                                                                                                           |

| XECL       | The falling edge of XECL triggers the enable chain cascade for the X-drivers.  Every 16th clock pulse is output to the next X-driver.                                                                                                                                                                                                                              |

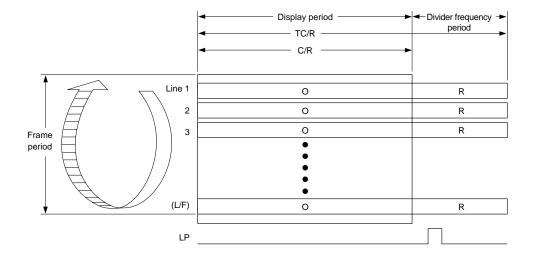

| LP         | LP latches the signal in the X-driver shift registers into the output data latches. LP is a falling-edge triggered signal, and pulses once every display line.                                                                                                                                                                                                     |

|            | Connect LP to the Y-driver shift clock on modules.                                                                                                                                                                                                                                                                                                                 |

| WF         | LCD panel AC drive output. The WF period is selected to be one of two values with SYSTEM SET command.                                                                                                                                                                                                                                                              |

| YSCL       | The falling edge of YSCL latches the data on YD into the input shift registers of the Y-drivers. YSCL is not used with driver ICs which use LP as the Y-driver shift clock.                                                                                                                                                                                        |

| YD         | YD is the data pulse output for the Y drivers. It is active during the last line of each frame, and is shifted through the Y drivers one by one (by YSCL), to scan the display's common connections.                                                                                                                                                               |

|            | Power-down output signal. YDIS is HIGH while the display drive outputs are active.                                                                                                                                                                                                                                                                                 |

| YDIS       | YDIS goes LOW one or two frames after the sleep command is written to the S1D13305 series. All Y-driver outputs are forced to an intermediate level (de-selecting the display segments) to blank the display. In order to implement power-down operation in the LCD unit, the LCD power drive supplies must also be disabled when the display is disabled by YDIS. |

# 6. SPECIFICATIONS

# 6.1. Absolute Maximum Ratings

| Parameter                                       | Symbol  | Rating            | Unit |

|-------------------------------------------------|---------|-------------------|------|

| Supply voltage range                            | VDD     | -0.3 to 7.0       | V    |

| Input voltage range                             | Vin     | -0.3 to VDD + 0.3 | V    |

| Power dissipation                               | PD      | 300               | mW   |

| Operating temperature range                     | Topg    | –20 to 75         | °C   |

| Storage temperature range                       | Tstg    | -65 to 150        | °C   |

| Soldering temperature (10 seconds). See note 1. | Tsolder | 260               | °C   |

#### Notes:

- 1. The humidity resistance of the flat package may be reduced if the package is immersed in solder. Use a soldering technique that does not heatstress the package.

- 2. If the power supply has a high impedance, a large voltage differential can occur between the input and supply voltages. Take appropriate care with the power supply and the layout of the supply lines. (See section 6.2.)

- 3. All supply voltages are referenced to Vss = 0V.

#### 6.2. S1D13305

$VDD = 4.5 \text{ to } 5.5V, VSS = 0V, Ta = -20 \text{ to } 75^{\circ}C$

| Davamatav                       | Cumbal | Condition                                                                  |           | Rating |           | l lmi4 |

|---------------------------------|--------|----------------------------------------------------------------------------|-----------|--------|-----------|--------|

| Parameter                       | Symbol | Condition                                                                  | Min.      | Тур.   | Max.      | Unit   |

| Supply voltage                  | VDD    |                                                                            | 4.5       | 5.0    | 5.5       | V      |

| Register data retention voltage | Voн    |                                                                            | 2.0       | _      | 6.0       | V      |

| Input leakage current           | ILI    | VI = VDD. See note 5.                                                      | _         | 0.05   | 2.0       | μΑ     |

| Output leakage current          | ILO    | VI = VSS. See note 5.                                                      | _         | 0.10   | 5.0       | μΑ     |

| Operating supply current        | lopr   | See note 4.                                                                | _         | 11     | 15        | mA     |

| Quiescent supply current        | IQ     | Sleep mode,<br>$V_{OSC1} = V_{\overline{CS}} = V_{\overline{RD}} = V_{DD}$ | _         | 0.05   | 20.0      | μΑ     |

| Oscillator frequency            | fosc   | Measured at crystal,                                                       | 1.0       | _      | 10.0      | MHz    |

| External clock frequency        | fCL    | 47.5% duty cycle.                                                          | 1.0       | _      | 10.0      | MHz    |

| Oscillator feedback resistance  | Rf     | See note 6.                                                                | 0.5       | 1.0    | 3.0       | МΩ     |

| TTL                             |        |                                                                            | '         |        | 1         |        |

| HIGH-level input voltage        | VIHT   | See note 1.                                                                | 0.5VDD    | _      | VDD       | V      |

| LOW-level input voltage         | VILT   | See note 1.                                                                | Vss       | _      | 0.2VDD    | V      |

| HIGH-level output voltage       | Vонт   | Iон = -5.0 mA.<br>See note 1.                                              | 2.4       | _      | _         | V      |

| LOW-level output voltage        | VOLT   | IoL = 5.0 mA. See note 1.                                                  | _         | _      | Vss + 0.4 | V      |

| CMOS                            |        |                                                                            |           |        |           |        |

| HIGH-level input voltage        | VIHC   | See note 2.                                                                | 0.8VDD    | _      | VDD       | V      |

| LOW-level input voltage         | VILC   | See note 2.                                                                | Vss       | _      | 0.2VDD    | V      |

| HIGH-level output voltage       | Vohc   | Iон = −2.0 mA. See note 2.                                                 | VDD - 0.4 | _      | _         | V      |

| LOW-level output voltage        | Volc   | Iон = 1.6 mA. See note 2.                                                  | _         | _      | Vss + 0.4 | V      |

| Open-drain                      |        |                                                                            |           |        |           |        |

| LOW-level output voltage        | VOLN   | IoL = 6.0 mA.                                                              | _         | _      | Vss + 0.4 | V      |

| Schmitt-trigger                 |        |                                                                            | '         |        |           |        |

| Rising-edge threshold voltage   | VT+    | See note 3.                                                                | 0.5VDD    | 0.7VDD | 0.8VDD    | V      |

| Falling-edge threshold voltage  | VT-    | See note 3.                                                                | 0.2VDD    | 0.3VDD | 0.5VDD    | V      |

#### Notes:

- 1. D0 to D7, A0,  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , VD0 to VD7, VA0 to VA15,  $\overline{VRD}$ ,  $\overline{VWR}$  and  $\overline{VCE}$  are TTL-level inputs.

- 2. SEL1 is CMOS-level inputs. YD, XD0 to XD3, XSCL, LP, WF, YDIS are CMOS-level outputs.

- 3. RES is a Schmitt-trigger input. The pulsewidth on RES must be at least 200 μs. Note that pulses of more than a few seconds will cause DC voltages to be applied to the LCD panel.

- 4. fosc = 10 MHz, no load (no display memory), internal character generator, 256 × 200 pixel display. The operating supply current can be reduced by approximately 1 mA by setting both CLO and the display OFF.

- 5. VD0 to VD7 and D0 to D7 have internal feedback circuits so that if the inputs become high-impedance, the input state immediately prior to that is held. Because of the feedback circuit, input current flow occurs when the inputs are in an intermediate state.

- 6. Because the oscillator circuit input bias current is in the order of  $\mu A$ , design the printed circuit board so as to reduce leakage currents.

VDD = 2.7 to 4.5 V, Vss = 0 V, Ta = -20 to 75°C unless otherwise noted

| Demonstra                       | 0h - l                                        | O an dition                            |           | Rating  |                     | Unit   |

|---------------------------------|-----------------------------------------------|----------------------------------------|-----------|---------|---------------------|--------|

| Parameter                       | Symbol                                        | Condition                              | Min.      | Тур.    | Max.                | Unit   |

| Supply voltage                  | VDD                                           |                                        | 2.7       | 3.5     | 4.5                 | V      |

| Register data retention voltage | Voн                                           |                                        | 2.0       | _       | 6.0                 | V      |

| Input leakage current           | lu                                            | VI = VDD. See note 5.                  | _         | 0.05    | 2.0                 | μΑ     |

| Output leakage current          | ILO                                           | Vı = Vss. See note 5.                  | _         | 0.10    | 5.0                 | μΑ     |

| Operating supply current        | lopr                                          | V <sub>DD</sub> = 3.5 V. See note 4.   | _         | 3.5     | _                   | mA     |

| Operating Supply Surrent        | ΙΟΡΙ                                          | See note 4.                            | _         | _       | 7.0                 | 1117 ( |

| Quiescent supply current        | ΙQ                                            | Sleep mode,<br>Vosc1 = Vcs = VRD = VDD | _         | 0.05    | 20.0                | μΑ     |

| Oscillator frequency            | fosc                                          | Measured at crystal,                   | 1.0       | _       | 8.0                 | MHz    |

| External clock frequency        | fcL                                           | 47.5% duty cycle.                      | 1.0       | _       | 8.0                 | MHz    |

| Oscillator feedback resistance  | Oscillator feedback resistance Rf See note 6. |                                        | 0.7       | _       | 3.0                 | MΩ     |

| TTL                             | 1                                             |                                        |           |         |                     |        |

| HIGH-level input voltage        | VIHT                                          | See note 1.                            | 0.5 VDD   | _       | VDD                 | V      |

| LOW-level input voltage         | VILT                                          | See note 1.                            | Vss       | _       | 0.2 VDD             | V      |

| HIGH-level output voltage       | Vонт                                          | IOH = -3.0  mA. See note 1.            | 2.4       | _       | _                   | ٧      |

| LOW-level output voltage        | Volt                                          | IoL = 3.0 mA. See note 1.              | _         | _       | Vss + 0.4           | V      |

| CMOS                            | 1                                             |                                        |           |         |                     |        |

| HIGH-level input voltage        | Vihc                                          | See note 2.                            | 0.8 VDD   | _       | VDD                 | V      |

| LOW-level input voltage         | VILC                                          | See note 2.                            | Vss       | _       | 0.2 VDD             | V      |

| HIGH-level output voltage       | Vонс                                          | IOH = -2.0  mA. See note 2.            | VDD - 0.4 | _       | _                   | V      |

| LOW-level output voltage        | Volc                                          | Iон = 1.6 mA. See note 2.              |           | _       | Vss + 0.4           | V      |

| Open-drain                      | 1                                             |                                        |           | ı       |                     |        |

| LOW-level output voltage        | Voln                                          | IoL = 6.0 mA.                          | _         | _       | Vss + 0.4           | V      |

| Schmitt-trigger                 | l                                             | ı                                      |           |         |                     |        |

| Rising-edge threshold voltage   | VT+                                           | See note 3.                            | 0.5 Vdd   | 0.7 Vdd | 0.8 V <sub>DD</sub> | V      |

| Falling-edge threshold voltage  | VT-                                           | See note 3.                            | 0.2 VDD   | 0.3 Vdd | 0.5 VDD             | V      |

#### **Notes**

- 1. D0 to D7, A0,  $\overline{\text{CS}}$ ,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , VD0 to VD7, VA0 to VA15,  $\overline{\text{VRD}}$ ,  $\overline{\text{VWR}}$  and  $\overline{\text{VCE}}$  are TTL-level inputs.

- 2. SEL1 is CMOS-level inputs. YD, XD0 to XD3, XSCL, LP, WF, YDIS are CMOS-level outputs.

- 3. RES is a Schmitt-trigger input. The pulsewidth on RES must be at least 200 μs. Note that pulses of more than a few seconds will cause DC voltages to be applied to the LCD panel.

- 4. fosc = 10 MHz, no load (no display memory), internal character generator, 256 × 200 pixel display. The operating supply current can be reduced by approximately 1 mA by setting both CLO and the display OFF.

- 5. VD0 to VD7 and D0 to D7 have internal feedback circuits so that if the inputs become high-impedance, the input state immediately prior to that is held. Because of the feedback circuit, input current flow occurs when the inputs are in an intermediate state.

- 6. Because the oscillator circuit input bias current is in the order of  $\mu A$ , design the printed circuit board so as to reduce leakage currents.

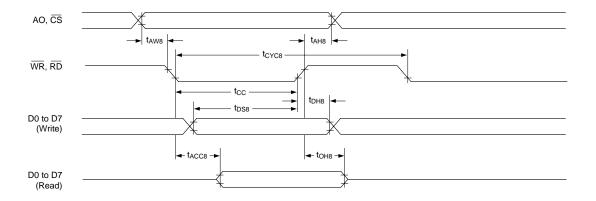

# 6.3. S1D13305F Timing Diagrams

# 6.3.1. 8080 family interface timing

$Ta = -20 \text{ to } 75^{\circ}C$

| Cianal     | Symbol | Symbol Parameter    |           | VDD = 4.5 to 5.5V |           | VDD = 2.7 to 4.5V |      | Condition  |

|------------|--------|---------------------|-----------|-------------------|-----------|-------------------|------|------------|

| Signal     |        | Parameter           | Min.      | Max.              | Min.      | Max.              | Unit | Condition  |

| A0, CS     | tAH8   | Address hold time   | 10        |                   | 10        |                   | ns   |            |

| A0, C3     | tAW8   | Address setup time  | 0         |                   | 0         | _                 | ns   |            |

| WR, RD     | tCYC8  | System cycle time   | See note. |                   | See note. | _                 | ns   |            |

| VVK, KD    | tCC    | Strobe pulsewidth   | 120       | _                 | 150       |                   | ns   | CL = 100pF |

|            | tDS8   | Data setup time     | 120       | <del>-</del>      | 120       | _                 | ns   | OL = 100pi |

| D0 to D7   | tDH8   | Data hold time      | 5         | _                 | 5         | _                 | ns   |            |

| ולט טו טען | tACC8  | RD access time      | _         | 50                | _         | 80                | ns   |            |

|            | tOH8   | Output disable time | 10        | 50                | 10        | 55                | ns   |            |

**Note:** For memory control and system control commands:

$t_{CYC8} = 2t_C + t_{CC} + t_{CEA} + 75 > t_{ACV} + 245$

For all other commands:

$t_{\rm CYC8} = 4t_{\rm C} + t_{\rm CC} + 30$

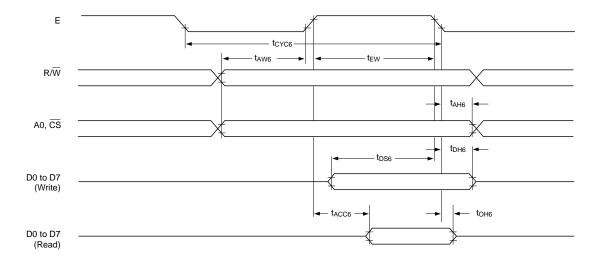

# 6.3.2. 6800 family interface timing

Note: tcyc6 indicates the interval during which CS is LOW and E is HIGH.

$Ta = -20 \text{ to } 75^{\circ}C$

| Signal            | Symbol   | Parameter           | VDD = 4.5 | 5 to 5.5V | VDD = 2.7 | 7 to 4.5V | Unit | Condition |

|-------------------|----------|---------------------|-----------|-----------|-----------|-----------|------|-----------|

| Signal            | Syllibol | Min. Max            |           | Max.      | Min. Max. |           | Onit | Condition |

| A0,               | tCYC6    | System cycle time   | See note. | _         | See note. |           | ns   |           |

| A0,<br>CS,<br>R/W | tAW6     | Address setup time  | 0         | _         | 10        | _         | ns   |           |

| R/W               | tAH6     | Address hold time   | 0         | _         | 0         | _         | ns   |           |

|                   | tDS6     | Data setup time     | 100       | _         | 120       | _         | ns   | CL =      |

| D0 to D7          | tDH6     | Data hold time      | 0         | _         | 0         | _         | ns   | 100 pF    |

| וט וט טו          | tOH6     | Output disable time | 10        | 50        | 10        | 75        | ns   |           |

|                   | tACC6    | Access time         | _         | 85        | _         | 130       | ns   |           |

| Е                 | tEW      | Enable pulsewidth   | 120       |           | 150       | _         | ns   |           |

Note: For memory control and system control commands:

$t_{CYC6} = 2t_{C} + t_{EW} + t_{CEA} + 75 > t_{ACV} + 245$

For all other commands:

$t_{CYC6} = 4t_{C} + t_{EW} + 30$

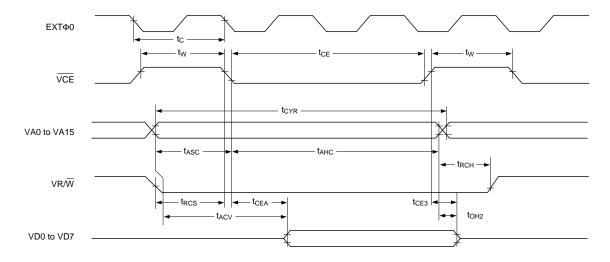

# 6.3.3. Display memory read timing

$Ta = -20 \text{ to } 75^{\circ}C$

| Cianal         | Cumbal | Doromotor                                                        | VDD = 4. | 5 to 5.5V | VDD = 2. | 7 to 4.5V | l lmi4 | Condition      |

|----------------|--------|------------------------------------------------------------------|----------|-----------|----------|-----------|--------|----------------|

| Signal         | Symbol | Parameter                                                        | Min.     | Max.      | Min.     | Max.      | Unit   | Condition      |

| EXT $\phi 0$   | tC     | Clock period                                                     | 100      | _         | 125      | _         | ns     |                |

| VCE            | tw     | VCE HIGH-level pulsewidth                                        | tc - 50  | _         | tc - 50  | _         | ns     |                |

| VCE tce        |        | VCE LOW-level pulsewidth                                         | 2tc - 30 | _         | 2tc - 30 | _         | ns     |                |

|                | tCYR   | Read cycle time                                                  | 3tC      | _         | 3tC      | _         | ns     |                |

| VA0 to<br>VA15 | tASC   | Address setup time to falling edge of VCE                        | tc - 70  | _         | tc - 100 | _         | ns     |                |

| 77110          | tAHC   | Address hold time from falling edge of VCE                       | 2tc - 30 | _         | 2tc - 40 | _         | ns     | CL = 100<br>pF |

| VRD            | tRCS   | Read cycle setup time to falling edge of VCE                     | tc - 45  | _         | tc - 60  | _         | ns     |                |

| VICE           | tRCH   | Read cycle hold time from rising edge of $\overline{\text{VCE}}$ | 0.5tC    |           | 0.5tC    | _         | ns     |                |

|                | tACV   | ACV Address access time                                          |          | 3tc - 100 | _        | 3tC - 115 | ns     |                |

| VD0 to         | tCEA   | VCE access time                                                  | _        | 2tC - 80  | _        | 2tC - 90  | ns     |                |

| VD7            | tOH2   | H2 Output data hold time                                         |          | _         | 0        |           | ns     |                |

|                | tCE3   | VCE to data off time                                             | 0        | _         | 0        | _         | ns     |                |

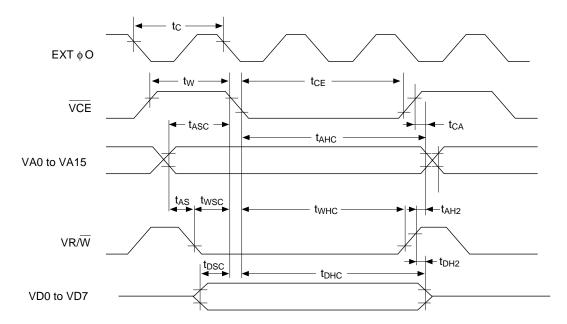

# 6.3.4. Display memory write timing

$Ta = -20 \text{ to } 75^{\circ}C$

| Signal         | Symbol | Doromotor                                                     | VDD = 4.5 | 5 to 5.5V | VDD = 2.7 | 7 to 4.5V | Unit | Condition |

|----------------|--------|---------------------------------------------------------------|-----------|-----------|-----------|-----------|------|-----------|

| Signal         | Symbol | Parameter                                                     | Min.      | Max.      | Min.      | Max.      | Onit | Condition |

| EXT $\phi 0$   | tC     | Clock period                                                  | 100       | _         | 125       | _         | ns   |           |

| VCE            | tw     | VCE HIGH-level pulsewidth                                     | tc - 50   |           | tc - 50   |           | ns   |           |

| VCE            | tCE    | VCE LOW-level pulsewidth                                      | 2tc - 30  |           | 2tc - 30  | _         | ns   |           |

|                | tcyw   | Write cycle time                                              | 3tC       | _         | 3tC       | _         | ns   |           |

|                | tAHC   | Address hold time from falling edge of VCE                    | 2tc - 30  | _         | 2tC - 40  | _         | ns   |           |

| .,,,           | tASC   | Address setup time to falling edge of $\overline{\text{VCE}}$ | tc - 70   | _         | tc - 110  | _         | ns   |           |

| VA0 to<br>VA15 | tCA    | tCA Address hold time from rising edge of VCE                 |           |           | 0         |           | ns   | CL = 100  |

|                | tAS    | Address setup time to falling edge of VWR                     | 0         | _         | 0         | _         | ns   | pF        |

|                | tAH2   | Address hold time from rising edge of VWR                     | 10        |           | 10        | _         | ns   |           |

| VWR            | twsc   | Write setup time to falling edge of VCE                       | tc - 80   | _         | tc – 115  | _         | ns   |           |

| VVVK           | twnc   | Write hold time from falling edge of VCE                      | 2tc - 20  | _         | 2tc - 20  | _         | ns   |           |

|                | tDSC   | Data input setup time to falling edge of VCE                  | tc - 85   |           | tc – 125  | _         | ns   |           |

| VD0 to<br>VD7  | tDHC   | Data input hold time from falling edge of VCE                 | 2tc - 30  | _         | 2tc - 30  | _         | ns   |           |

|                | tDH2   | Data hold time from rising edge of VWR                        | 5         | 50        | 5         | 50        | ns   |           |

Note: VD0 to VD7 are latching input/outputs. While the bus is high impedance, VD0 to VD7 retain the write data until the data read from the memory is placed on the bus.

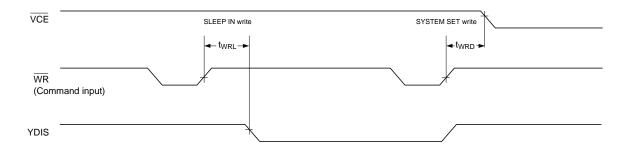

# 6.3.5. SLEEP IN command timing

$Ta = -20 \text{ to } 75^{\circ}C$

| Signal Symbo |        | Parameter                    | VDD = 4.                | 5 to 5.5V   | VDD = 2.    | 7 to 4.5V   | Unit | Condition |  |

|--------------|--------|------------------------------|-------------------------|-------------|-------------|-------------|------|-----------|--|

| Signal       | Symbol | Parameter                    | Parameter Min. Max. Min |             | Min.        | Max.        | Onit | Condition |  |

| WR           | tWRD   | VCE falling-edge delay time  | See note 1.             | _           | See note 1. | _           | ns   | CL = 100  |  |

| VVK          | tWRL   | YDIS falling-edge delay time | _                       | See note 2. | _           | See note 2. | ns   | pF        |  |

#### Notes:

- 1.  $t_{WRD} = 18t_{C} + t_{OSS} + 40$  (toss is the time delay from the sleep state until stable operation)

- 2.  $t_{WRL} = 36t_C \times [TC/R] \times [L/F] + 70$

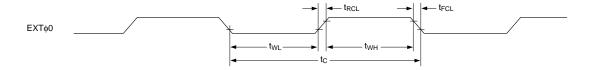

# 6.3.6. External oscillator signal timing

$Ta = -20 \text{ to } 75^{\circ}\text{C}$

| Signal       | Symbol   | Parameter                               | VDD = 4.    | 5 to 5.5V   | VDD = 2.7   | 7 to 4.5V   | Unit | Condition |

|--------------|----------|-----------------------------------------|-------------|-------------|-------------|-------------|------|-----------|

| Signal       | Syllibol | Faranietei                              | Min.        | Max.        | Min. Max    |             | Onit | Condition |

|              | tRCL     | External clock rise time                | _           | 15          | _           | 15          | ns   |           |

|              | tFCL     | External clock fall time                | _           | 15          | _           | 15          | ns   |           |

| EXT $\phi 0$ | twH      | External clock<br>HIGH-level pulsewidth | See note 1. | See note 2. | See note 1. | See note 2. | ns   |           |

|              | tWL      | External clock<br>LOW-level pulsewidth  | See note 1. | See note 2. | See note 1. | See note 2. | ns   |           |

|              | tC       | External clock period                   | 100         | _           | 125         | _           | ns   |           |

#### Notes:

1.

$$(tc - t_{RCL} - t_{FCL}) \times \frac{475}{1000} < t_{WH}, t_{WL}$$

2.

$$(tc - t_{RCL} - t_{FCL}) \times \frac{525}{1000} > t_{WH}, t_{WL}$$

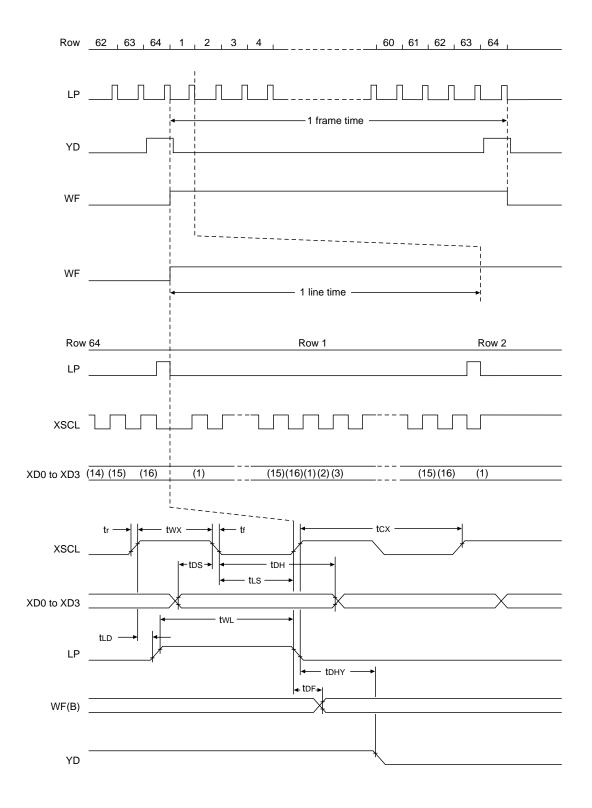

# 6.3.7. LCD output timing

The following characteristics are for a 1/64 duty cycle.

$Ta = -20 \text{ to } 75^{\circ}\text{C}$

| Signal | Symbol   | Parameter               | VDD = 4.5 | 5 to 5.5V | VDD = 2.7 | 7 to 4.5V | Unit | Condition |  |

|--------|----------|-------------------------|-----------|-----------|-----------|-----------|------|-----------|--|

| Signal | Syllibol | Faranietei              | Min.      | Max.      | Min.      | Max       | Onit | Condition |  |

|        | tr       | Rise time               | _         | 30        | _         | 40        | ns   |           |  |

|        | tf       | Fall time               | _         | 30        | _         | 40        | ns   |           |  |

| XSCL   | tcx      | Shift clock cycle time  | 4tC       | _         | 4tC       | _         | ns   |           |  |

| ASCL   | twx      | XSCL clock pulsewidth   | 2tc - 60  | _         | 2tc - 60  | _         | ns   |           |  |

| XD0 to | tDH      | X data hold time        | 2tc - 50  | _         | 2tc - 50  |           | ns   | CL=       |  |

| XD3    | tDS      | X data setup time       | 2tC - 100 | _         | 2tc - 105 | _         | ns   | 100 pF    |  |

|        | tLS      | Latch data setup time   | 2tc - 50  | _         | 2tc - 50  | _         | ns   |           |  |

| LP     | tWL      | LP pulsewidth           | 4tc - 80  | _         | 4tc - 120 | _         | ns   |           |  |

|        | tLD      | LP delay time from XSCL | 0         | _         | 0         | _         | ns   |           |  |

| WF     | tDF      | Permitted WF delay      | _         | 50        | _         | 50        | ns   | 1         |  |

| YD     | tDHY     | Y data hold time        | 2tc - 20  | _         | 2tc - 20  | _         | ns   |           |  |

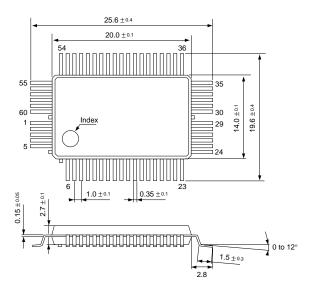

# 7. PACKAGE DIMENSIONS

Unit: mm

# 7.1. S1D13305F00A

#### ♦QFP5-60 pin

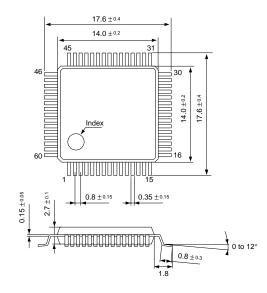

# 7.2. S1D13305F00B

# ♦QFP6-60 pin

#### 8. INSTRUCTION SET

#### 8.1. The Command Set

Table 1. Command set

| Class          | Command     |    |    |    |    | (  | Cod | е  |    |    |         |         | Hex            | Command Description                             | Command<br>Read<br>Parameters |              |

|----------------|-------------|----|----|----|----|----|-----|----|----|----|---------|---------|----------------|-------------------------------------------------|-------------------------------|--------------|

|                |             | RD | WR | A0 | D7 | D6 | D5  | D4 | D3 | D2 | D1      | D0      |                | -                                               | No. of<br>Bytes               | Sec-<br>tion |

| System control | SYSTEM SET  | 1  | 0  | 1  | 0  | 1  | 0   | 0  | 0  | 0  | 0       | 0       | 40             | Initialize device and display                   | 8                             | 8.2.1        |

| CONTROL        | SLEEP IN    | 1  | 0  | 1  | 0  | 1  | 0   | 1  | 0  | 0  | 1       | 1       | 53             | Enter standby mode                              | 0                             | 8.2.2        |

|                | DISP ON/OFF | 1  | 0  | 1  | 0  | 1  | 0   | 1  | 1  | 0  | 0       | D       | 58,<br>59      | Enable and disable display and display flashing | 1                             | 8.3.1        |

|                | SCROLL      | 1  | 0  | 1  | 0  | 1  | 0   | 0  | 0  | 1  | 0       | 0       | 44             | Set display start address and display regions   | 10                            | 8.3.2        |

|                | CSRFORM     | 1  | 0  | 1  | 0  | 1  | 0   | 1  | 1  | 1  | 0       | 1       | 5D             | Set cursor type                                 | 2                             | 8.3.3        |

| Display        | CGRAM ADR   | 1  | 0  | 1  | 0  | 1  | 0   | 1  | 1  | 1  | 0       | 0       | 5C             | Set start address of character generator RAM    | 2                             | 8.3.6        |

| control        | CSRDIR      | 1  | 0  | 1  | 0  | 1  | 0   | 0  | 1  | 1  | CD<br>1 | CD<br>0 | 4C<br>to<br>4F | Set direction of cursor movement                | 0                             | 8.3.4        |

|                | HDOT SCR    | 1  | 0  | 1  | 0  | 1  | 0   | 1  | 1  | 0  | 1       | 0       | 5A             | Set horizontal scroll position                  | 1                             | 8.3.7        |

|                | OVLAY       | 1  | 0  | 1  | 0  | 1  | 0   | 1  | 1  | 0  | 1       | 1       | 5B             | Set display overlay format                      | 1                             | 8.3.5        |

| Drawing        | CSRW        | 1  | 0  | 1  | 0  | 1  | 0   | 0  | 0  | 1  | 1       | 0       | 46             | Set cursor address                              | 2                             | 8.4.1        |

| control        | CSRR        | 1  | 0  | 1  | 0  | 1  | 0   | 0  | 0  | 1  | 1       | 1       | 47             | Read cursor address                             | 2                             | 8.4.2        |

| Memory         | MWRITE      | 1  | 0  | 1  | 0  | 1  | 0   | 0  | 0  | 0  | 1       | 0       | 42             | Write to display memory                         | 1                             | 8.5.1        |

| control        | MREAD       | 1  | 0  | 1  | 0  | 1  | 0   | 0  | 0  | 0  | 1       | 1       | 43             | Read from display memory                        | _                             | 8.5.2        |

#### Notes:

2-byte parameters (where two bytes are treated as 1 data item) are handled as follows:

- a. CSRW, CSRR: Each byte is processed individually. The microprocessor may read or write just the low byte of the cursor address

- b. SYSTEM SET, SCROLL, CGRAM ADR: Both parameter bytes are processed together. If the command is changed after half of the parameter has been input, the single byte is ignored.

- 2. APL and APH are 2-byte parameters, but are treated as two 1-byte parameters.

<sup>1.</sup> In general, the internal registers of the S1D13305 series are modified as each command parameter is input. However, the microprocessor does not have to set all the parameters of a command and may send a new command before all parameters have been input. The internal registers for the parameters that have been input will have been changed but the remaining parameter registers are unchanged.

# 8.2. System Control Commands

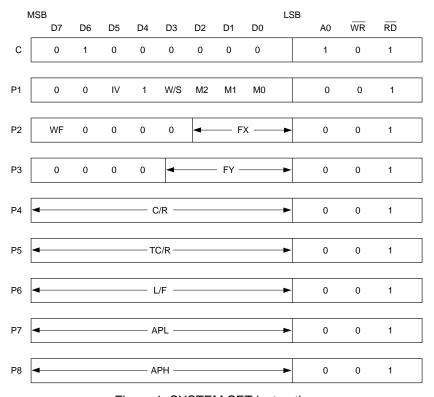

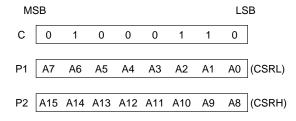

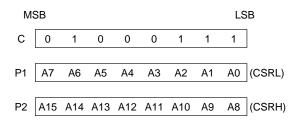

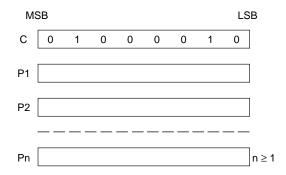

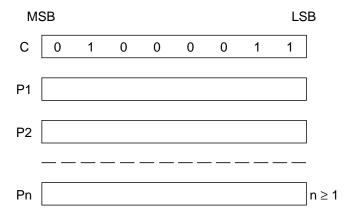

#### 8.2.1. SYSTEM SET

Initializes the device, sets the window sizes, and selects the LCD interface format. Since this command sets the basic operating parameters of the S1D13305 series, an incorrect SYSTEM SET command may cause other commands to operate incorrectly.

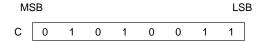

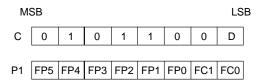

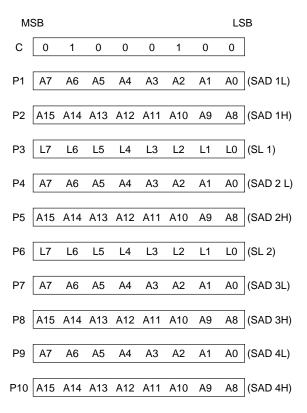

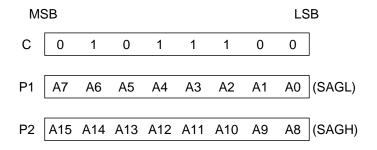

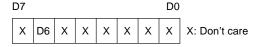

Figure 1. SYSTEM SET instruction

#### 8.2.1.1. C

This control byte performs the following:

- 1. Resets the internal timing generator

- 2. Disables the display

- 3. Cancels sleep mode

Parameters following P1 are not needed if only canceling sleep mode.

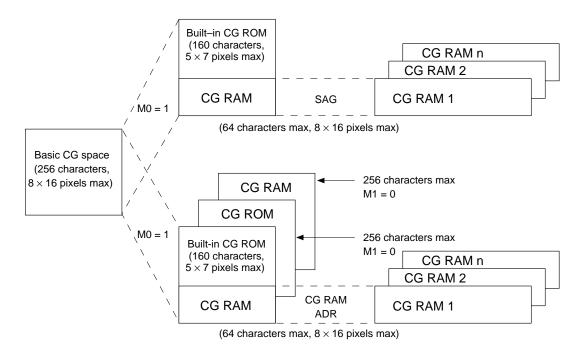

#### 8.2.1.2. M0

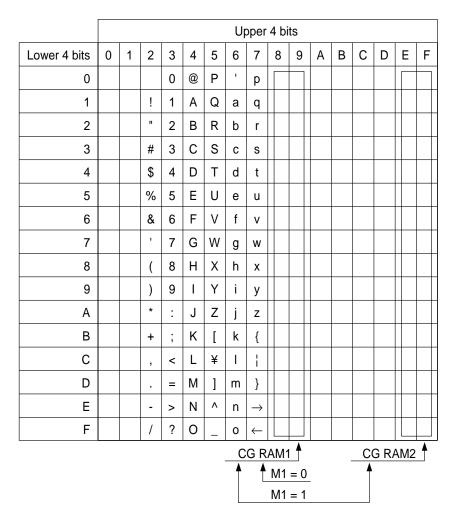

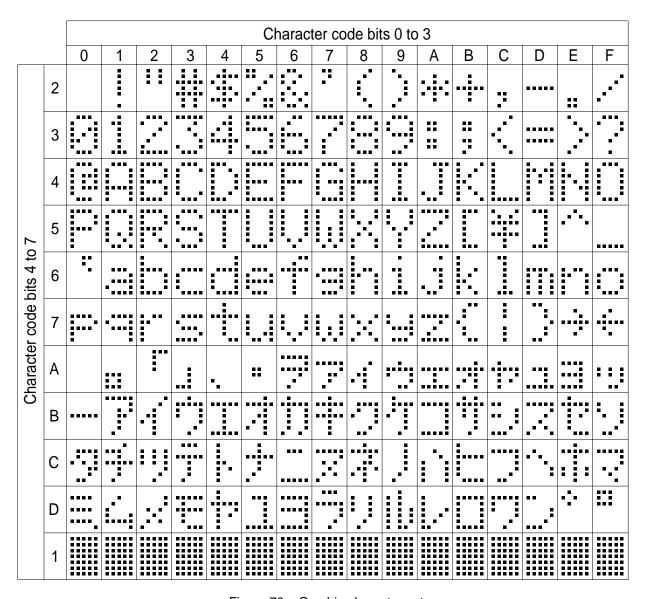

Selects the internal or external character generator ROM. The internal character generator ROM contains 160,  $5 \times 7$  pixel characters, as shown in figure 70. These characters are fixed at fabrication by the metallization mask. The external character generator ROM, on the other hand, can contain up to 256 user-defined characters.

M0 = 0: Internal CG ROM

M0 = 1: External CG ROM

Note that if the CG ROM address space overlaps the display memory address space, that portion of the display memory cannot be written to.

#### 8.2.1.3. M1

Selects the memory configuration for user-definable characters. The CG RAM codes select one of the 64 codes shown in figure 46.

M1 = 0: No D6 correction.

The CG RAM1 and CG RAM2 address spaces are not contiguous, the CG RAM1 address space is treated as character generator RAM, and the CG RAM2 address space is treated as character generator ROM.

M1 = 1: D6 correction.

The CG RAM1 and CG RAM2 address spaces are contiguout and are both treated as character generator RAM.

#### 8.2.1.4. M2

Selects the height of the character bitmaps. Characters more than 16 pixels high can be displayed by creating a bitmap for each portion of each character and using the S1D13305 series graphics mode to reposition them.

M2 = 0: 8-pixel character height (2716 or equivalent ROM)

M2 = 1: 16-pixel character height (2732 or equivalent ROM)

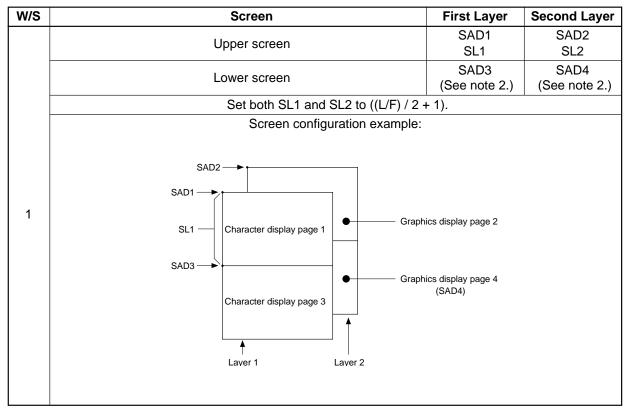

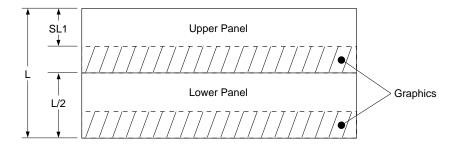

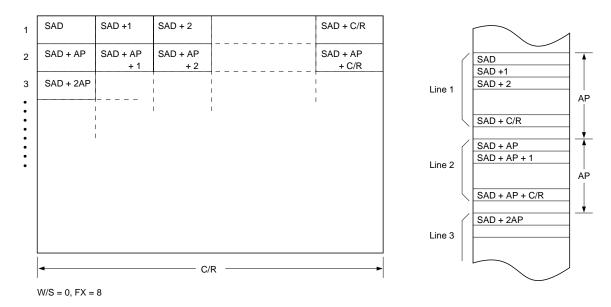

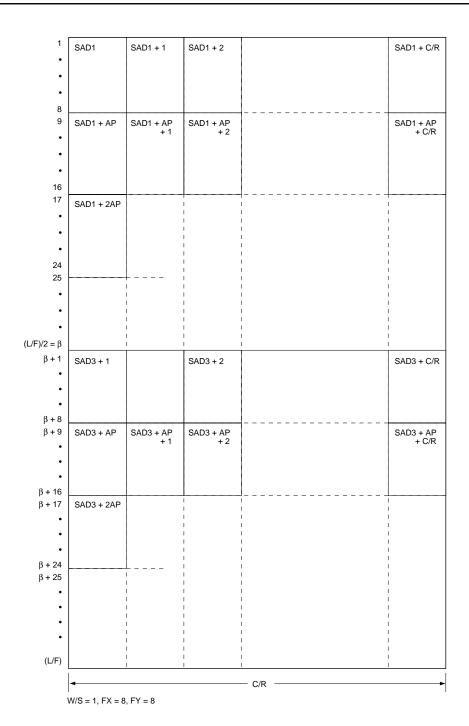

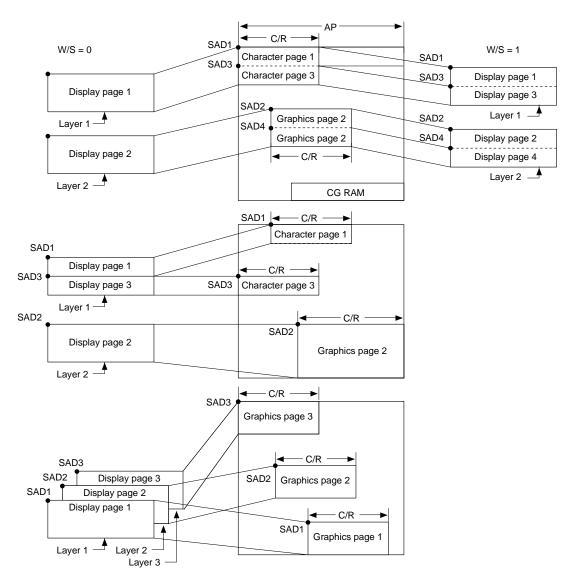

#### 8.2.1.5. W/S

Selects the LCD drive method.

W/S = 0: Single-panel drive

W/S = 1: Dual-panel drive

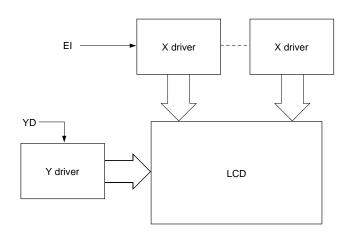

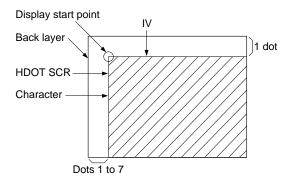

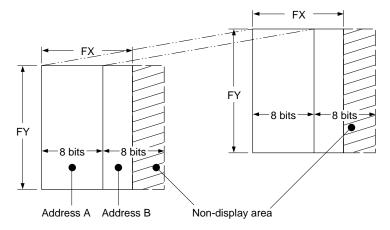

Figure 2. Single-panel display

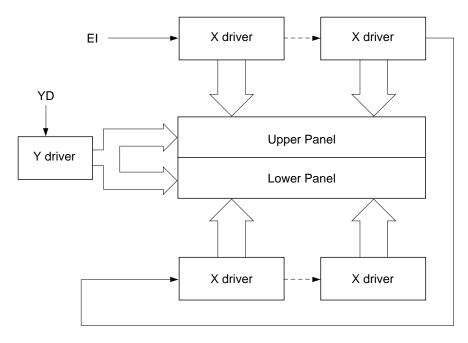

Figure 3. Above and below two-panel display

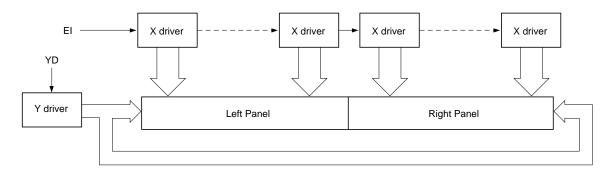

Figure 4. Left-and-right two-panel display

#### Note

There are no Seiko Epson LCD units in the configuration shown in Figure 4.

Table 2. LCD parameters

| Parameter                  | W/S                 | 5 = 0                           | W/S                                                                  | S = 1               |  |

|----------------------------|---------------------|---------------------------------|----------------------------------------------------------------------|---------------------|--|

| Parameter                  | IV = 1              | IV = 0                          | IV = 1                                                               | IV = 0              |  |

| C/R                        | C/R                 | C/R                             | C/R                                                                  | C/R                 |  |

| TC/R                       | TC/R                | TC/R (See note 1.)              | TC/R                                                                 | TC/R                |  |

| L/F                        | L/F                 | L/F                             | L/F                                                                  | L/F                 |  |

| SL1                        | 00H to L/F          | 00H to L/F + 1<br>(See note 2.) | (L/F) / 2                                                            | (L/F) / 2           |  |

| SL2                        | 00H to L/F          | 00H to L/F + 1<br>(See note 2.) | (L/F) / 2                                                            | (L/F) / 2           |  |

| SAD1                       | First screen block  | First screen block              | First screen block                                                   | First screen block  |  |

| SAD2                       | Second screen block | Second screen block             | Second screen block                                                  | Second screen block |  |

| SAD3                       | Third screen block  | Third screen block              | Third screen block                                                   | Third screen block  |  |

| SAD4                       | Invalid             | Invalid                         | Fourth screen block                                                  | Fourth screen block |  |

| Cursor move-<br>ment range | Continuous moveme   | nt over whole screen            | Above-and-below configuration: continuous movement over whole screen |                     |  |

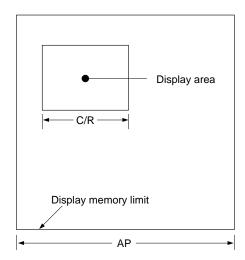

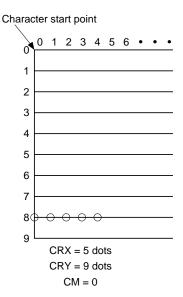

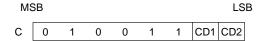

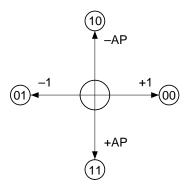

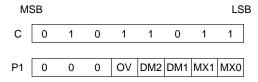

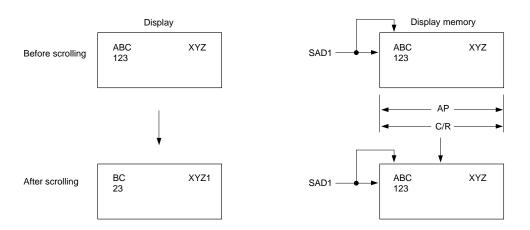

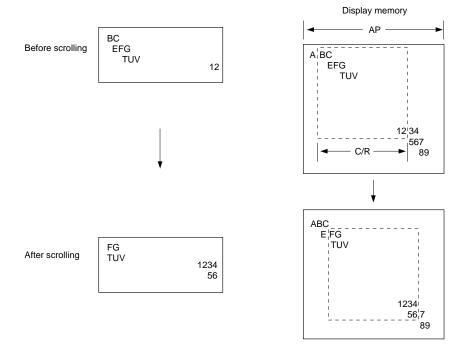

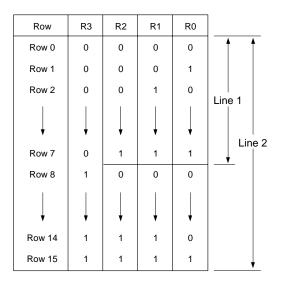

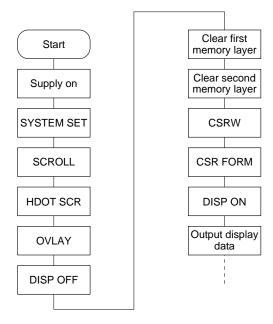

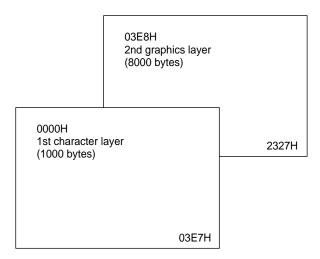

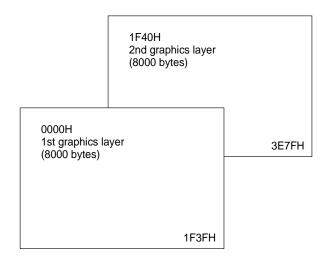

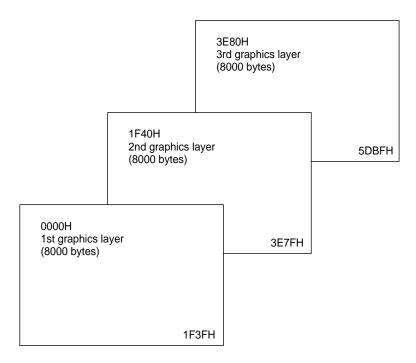

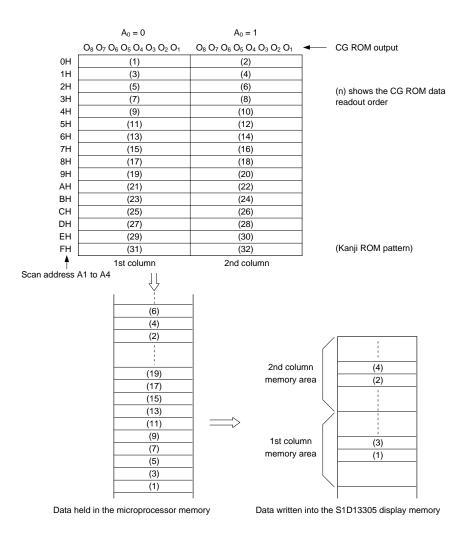

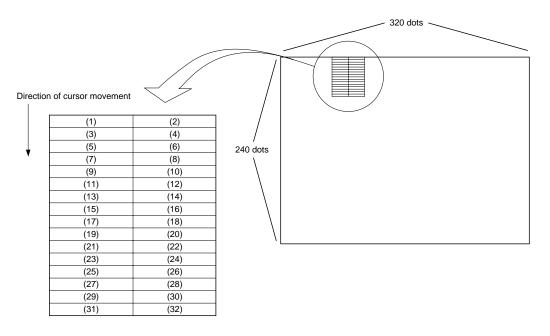

#### Notes: