# RENESAS

# **M52791SP/FP** AV Switch with I<sup>2</sup>C Bus Control

REJ03F0188-0200 Rev.2.00 Sep 14 2006

## Description

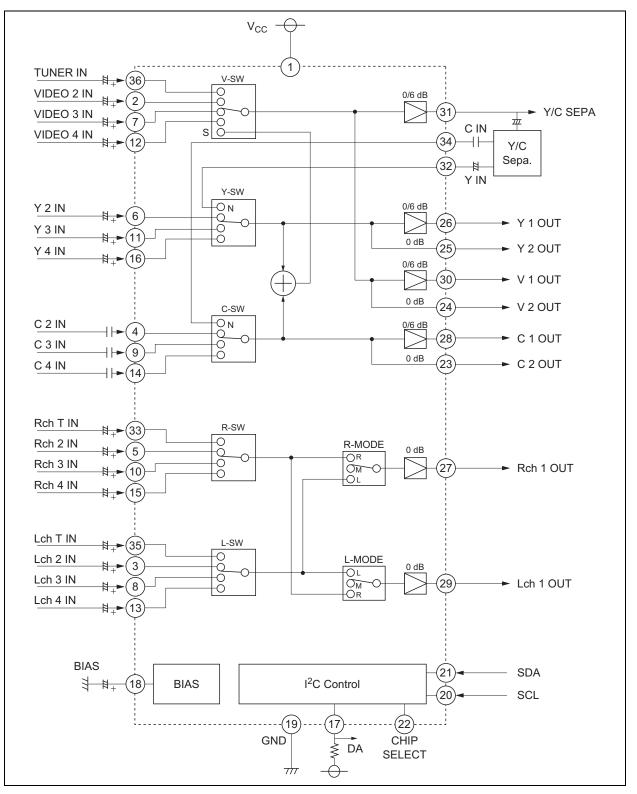

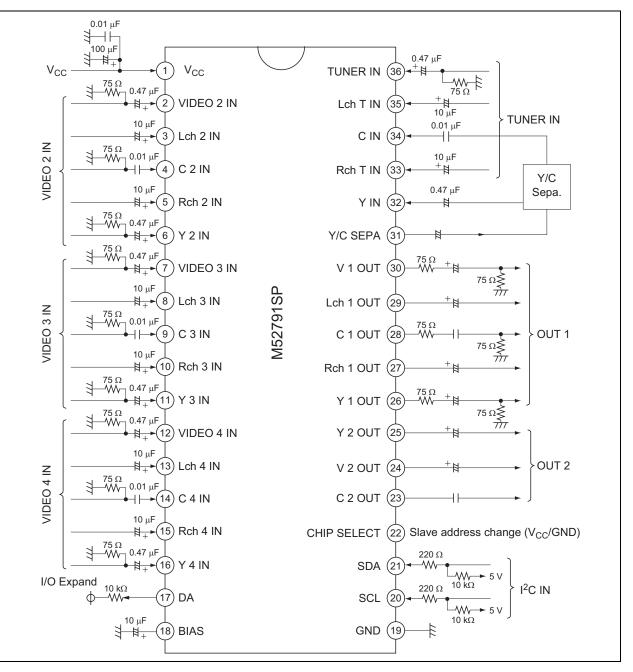

The M52791 is AV switch semiconductor integrated circuit with I<sup>2</sup>C bus control.

This IC contains 1-channels of 4-input audio switches and 1-channels of 4-input video switches. Each audio switches and video switches can be controlled independently.

The video switches contain amplifiers can be controlled a gain of output 0 dB or 6 dB.

## Features

- Video and stereo sound switches in one package

- Wide frequency range (video switch): DC to 20 MHz

- High separation (video switch): Crosstalk –60 dB (Typ) at 1 MHz

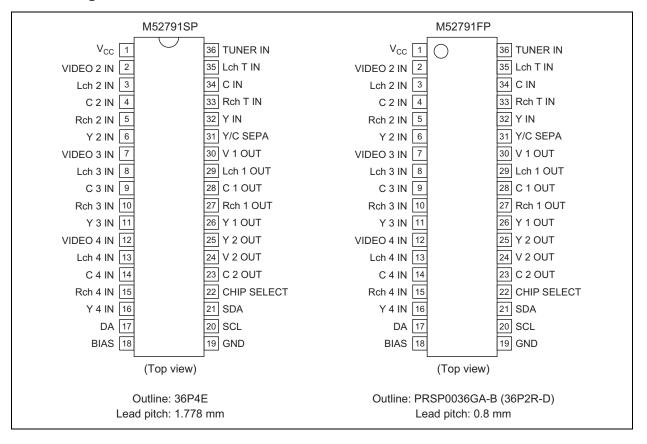

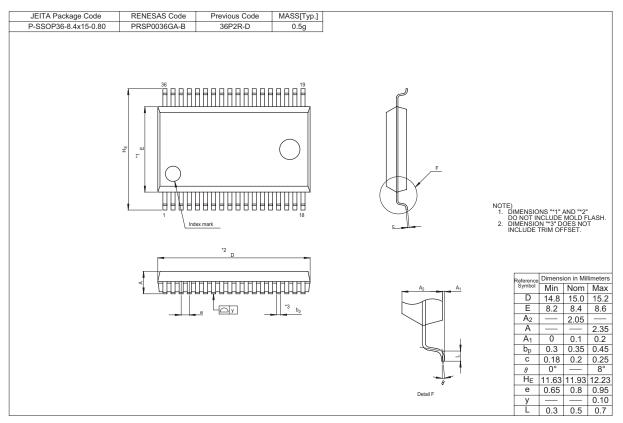

- Two types of packages are provided: SDIP with a lead pitch of 1.778 mm (M52791SP); and SSOP with a lead pitch of 0.8 mm (M52791FP).

## Application

Video equipment

## **Recommended Operating Condition**

Supply voltage:4.7 V to 9.3 VRated supply voltage:5 V, 9 VMaximum output current:49 mA (at 9 V)

## **Block Diagram**

Rev.2.00 Sep 14, 2006 page 2 of 13

RENESAS

### **Pin Arrangement**

## **Pin Description**

| Pin<br>No.                                | Name                                                                                         | Peripheral Circuit Pins | DC Voltage (V)                                                  | Remarks       |

|-------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------|---------------|

| 1                                         | V <sub>CC</sub>                                                                              | _                       | 9 V                                                             | 5 to 9 V      |

| 2<br>6<br>7<br>11<br>12<br>16<br>32<br>36 | VIDEO 2 IN<br>Y 2 IN<br>VIDEO 3 IN<br>Y 3 IN<br>VIDEO 4 IN<br>Y 4 IN<br>Y IN<br>TUNER IN     |                         | 3.6 V                                                           | Clamp in      |

| 3<br>5<br>8<br>10<br>13<br>15<br>33<br>35 | Lch 2 IN<br>Rch 2 IN<br>Lch 3 IN<br>Rch 3 IN<br>Lch 4 IN<br>Rch 4 IN<br>Rch T IN<br>Lch T IN |                         | 4.7 ∨                                                           |               |

| 4<br>9<br>14<br>34                        | C 2 IN<br>C 3 IN<br>C 4 IN<br>C IN                                                           |                         | 4.7 V                                                           |               |

| 17                                        | DA                                                                                           |                         | V <sub>OL</sub> max = 0.4 V                                     | At lin = 1 mA |

| 18                                        | BIAS                                                                                         |                         | 4.2 V                                                           |               |

| 19<br>20                                  | GND<br>SCL                                                                                   |                         | —<br>V <sub>IL</sub> max = 1.5 V<br>V <sub>IH</sub> min = 3.0 V |               |

| Pin<br>No.     | Name                          | Peripheral Circuit Pins | DC Voltage (V)                                                                               | Remarks       |

|----------------|-------------------------------|-------------------------|----------------------------------------------------------------------------------------------|---------------|

| 21             | SDA                           |                         | V <sub>IL</sub> max. = 1.5 V<br>V <sub>IH</sub> min. = 3.0 V<br>V <sub>OL</sub> max. = 0.4 V | At lin = 3 mA |

| 22             | CHIP SELECT                   |                         | SLAVE ADDRESS<br>0 to 1.5 V: 90H<br>2.5 to V <sub>CC</sub> : 92H<br>OPEN: 90H                |               |

| 26<br>28<br>30 | Y 1 OUT<br>C 1 OUT<br>V 1 OUT |                         | C OUT 4.0 V<br>V OUT<br>Y OUT<br>SYNC CHIP<br>DC = 2.9 V                                     |               |

| 23<br>24<br>25 | C 2 OUT<br>V 2 OUT<br>Y 2 OUT |                         | C OUT 3.3 V<br>V OUT<br>Y OUT<br>SYNC CHIP<br>DC = 2.2 V                                     |               |

| 27<br>29       | Rch 1 OUT<br>Lch 1 OUT        |                         | 4.0 V                                                                                        |               |

| 31             | Y/C SEPA                      |                         | SYNC CHIP<br>DC = 2.9 V                                                                      |               |

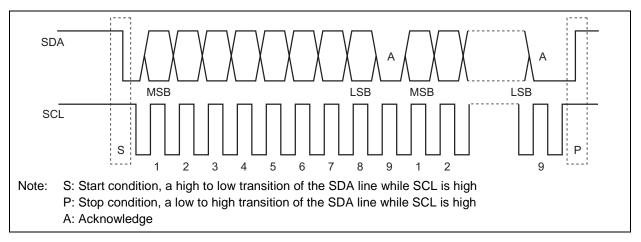

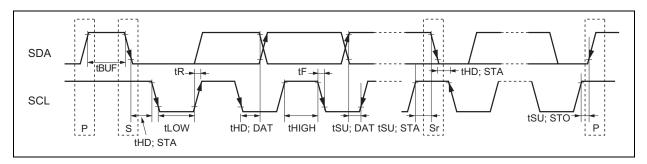

## I<sup>2</sup>C Bus

$I^2C$  Bus (Inter IC Bus) is multi master bus system developed by PHILIPS. Two wires (SDA-serial data, SCL-serial clock) realize functions of start, stop, transferring data, synchronization and arbitration. The output stages of device connected to the bus must have an open drain or open collector in order to perform the wired-AND function.

Every byte put on the SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first. The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW.

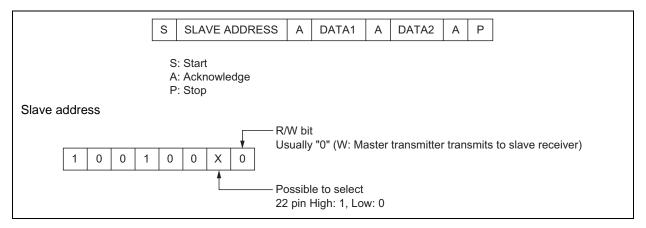

## Control

This IC controls 2-channel switches with 2-byte data (DATA1 and DATA2). Video switches are controlled by DATA1. Audio switches are controlled by DATA2.

## Data Byte Format

## **M52791 FUNCTION TABLE**

| S SLAVE ADDRESS A DATA (D7 to D0) A DATA (DF to D8) A P |

|---------------------------------------------------------|

|---------------------------------------------------------|

## SLAVE ADDRESS

| SLAVE ADDRESS | A6 | A5 | A4 | A3 | A2 | A1 | A0  | R/W |

|---------------|----|----|----|----|----|----|-----|-----|

|               | 1  | 0  | 0  | 1  | 0  | 0  | 0/1 | 0   |

## DATA1 (D7 to D0) CONT

| DATA CONT | D7    | D6    | D5       | D4      | D3     | D3 D2 |         | D0     |

|-----------|-------|-------|----------|---------|--------|-------|---------|--------|

|           | 0 FIX | 0 FIX | SEPA AMP | Y/C AMP | V AMP1 | S/N   | VIDEO S | W CONT |

## VIDEO SW CONT

|           | DATA |    | OUT       |        |        |  |  |

|-----------|------|----|-----------|--------|--------|--|--|

| S/N (S:1) | V-   | SW | V OUT     |        |        |  |  |

| D2        | D1   | D0 | Y/C SEPA  | Y OUT  | C OUT  |  |  |

| 0         | 0    | 0  | T IN      | Y IN   | C IN   |  |  |

| 0         | 0    | 1  | V 2 IN    | Y IN   | C IN   |  |  |

| 0         | 1    | 0  | V 3 IN    | Y IN   | C IN   |  |  |

| 0         | 1    | 1  | V 4 IN    | Y IN   | C IN   |  |  |

| 1         | 0    | 0  | Y/C MIX T | Y IN   | C IN   |  |  |

| 1         | 0    | 1  | Y/C MIX 2 | Y 2 IN | C 2 IN |  |  |

| 1         | 1    | 0  | Y/C MIX 3 | Y 3 IN | C 3 IN |  |  |

| 1         | 1    | 1  | Y/C MIX4  | Y 4 IN | C 4 IN |  |  |

## AMP GAIN CONT

| DATA | AMP      | DATA | AMP     | DATA | AMP   |

|------|----------|------|---------|------|-------|

| D5   | SEPA AMP | D4   | Y/C AMP | D3   | V AMP |

| 0    | 0 dB     | 0    | 0 dB    | 0    | 0 dB  |

| 1    | 6 dB     | 1    | 6 dB    | 1    | 6 dB  |

## DATA2 (DF to D8) CONT

| DATA CONT | DF    | DE   | DD    | DC    | DB    | DA  | D9      | D8     |

|-----------|-------|------|-------|-------|-------|-----|---------|--------|

|           | AUDIO | MODE | 0 FIX | 0 FIX | 0 FIX | I/O | AUDIO S | W CONT |

## AUDIO SW CONT

| МО   | DE | MU        | ITE       | R/R       |           | L/L       |           | NORMAL    |           |   |    |

|------|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---|----|

| DATA |    | OUT       |           | OUT       |           | OUT       |           | 0         | JT        | 0 | JT |

| D9   | D8 | Lch OUT 1 | Rch OUT 1 |   |    |

| 0    | 0  | MUTE      | MUTE      | Rch T IN  | Rch T IN  | Lch T IN  | Lch T IN  | Lch T IN  | Rch T IN  |   |    |

| 0    | 1  | MUTE      | MUTE      | Rch 2 IN  | Rch 2 IN  | Lch 2 IN  | Lch 2 IN  | Lch 2 IN  | Rch 2 IN  |   |    |

| 1    | 0  | MUTE      | MUTE      | Rch 3 IN  | Rch 3 IN  | Lch 3 IN  | Lch 3 IN  | Lch 3 IN  | Rch 3 IN  |   |    |

| 1    | 1  | MUTE      | MUTE      | Rch 4 IN  | Rch 4 IN  | Lch 4 IN  | Lch 4 IN  | Lch 4 IN  | Rch 4 IN  |   |    |

### I/O CONT

| DATA | OUT    |

|------|--------|

| DA   | DA OUT |

| 0    | HIGH   |

| 1    | LOW    |

## AUDIO MODE CONT

| DA | ТА |        |

|----|----|--------|

| DF | DE | MODE   |

| 0  | 0  | MUTE   |

| 0  | 1  | R/R    |

| 1  | 0  | L/L    |

| 1  | 1  | NORMAL |

## **Electrical Characteristics**

| Item                                            | Symbol                | Min  | Тур  | Max  | Unit | Test Condition                                                                                                                           |

|-------------------------------------------------|-----------------------|------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| Supply voltage                                  | V <sub>cc</sub>       | 4.7  | _    | 9.3  | V    |                                                                                                                                          |

| Circuit current                                 | I <sub>CC</sub>       |      | 49   | 64   | mA   | $V_{CC} = 9 V$ , Vin = 0 Vp-p, RI = $\infty \Omega$                                                                                      |

|                                                 |                       |      | 42   | 55   |      | $V_{CC} = 5 \text{ V}, \text{ Vin} = 0 \text{ Vp-p}, \text{ RI} = \infty \Omega$                                                         |

| Video                                           |                       | 1    | 1    | 1    | 1    |                                                                                                                                          |

| Voltage gain                                    | G                     | -0.5 | 0    | 0.5  | dB   | f = 100 kHz, 1 Vp-p (0 dB) (T→V <sub>10UT</sub> )                                                                                        |

|                                                 |                       | 5.5  | 6    | 6.5  |      | f = 100 kHz, 1 Vp-p (6 dB) (T→V <sub>10UT</sub> )                                                                                        |

|                                                 |                       | -0.5 | 0    | 0.5  |      | f = 100 kHz, 1 Vp-p (0 dB) (Y→V <sub>10UT</sub> )                                                                                        |

|                                                 |                       | 5.5  | 6    | 6.5  |      | f = 100 kHz, 1 Vp-p (6 dB) (Y→V <sub>10UT</sub> )                                                                                        |

| Frequency characteristics                       | F                     | -2.0 | 0    | 2.0  | dB   | f = 10 MHz/100 kHz, 1 Vp-p (0 dB) (T→V <sub>10UT</sub> )                                                                                 |

|                                                 |                       | -2.0 | 0    | 2.0  |      | f = 10 MHz/100 kHz, 1 Vp-p (6 dB) (T→V <sub>10UT</sub> )                                                                                 |

|                                                 |                       | -2.0 | 0    | 2.0  |      | f = 10 MHz/100 kHz, 1 Vp-p (0 dB) (Y→V <sub>10UT</sub> )                                                                                 |

|                                                 |                       | -2.0 | 0    | 2.0  |      | f = 10 MHz/100 kHz, 1 Vp-p (6 dB) (Y→V <sub>10UT</sub> )                                                                                 |

| Dynamic range                                   | D                     | 4    | _    | —    | Vp-p | $V_{CC} = 9 V (0 \text{ dB}) (T \rightarrow V_{1OUT})$ f = 100 kHz                                                                       |

|                                                 |                       | 2    |      | _    |      | $V_{CC} = 5 V (0 \text{ dB}) (T \rightarrow V_{1OUT})$ Maximum with                                                                      |

|                                                 |                       | 4    |      | _    |      | $V_{CC} = 9 V (0 \text{ dB}) (Y \rightarrow V_{1OUT})$ distortion                                                                        |

|                                                 |                       | 2    |      | _    |      | $V_{CC} = 5 V (0 \text{ dB}) (Y \rightarrow V_{10UT})$ <1.0%                                                                             |

| Input impedance                                 | Z <sub>IC</sub>       | 14   | 20   | 26   | kΩ   | (C, C <sub>2</sub> , C <sub>3</sub> , C <sub>4</sub> )                                                                                   |

|                                                 | Z <sub>IV</sub>       | —    | —    | —    |      | Clamp in (T, V <sub>2</sub> , V <sub>3</sub> , V <sub>4</sub> )                                                                          |

|                                                 | Z <sub>IY</sub>       | _    | _    |      |      | Clamp in (Y, Y <sub>2</sub> , Y <sub>3</sub> , Y <sub>4</sub> )                                                                          |

| Crosstalk                                       | СТ                    |      | -60  | -54  | dB   | $f = 1 \text{ MHz}, 1 \text{ Vp-p } T \rightarrow V_{1OUT} \text{ (at } V_2 \text{ mode)}$                                               |

| Audio                                           |                       |      |      |      |      |                                                                                                                                          |

| Voltage gain                                    | G                     | -0.5 | 0    | 0.5  | dB   | $f = 1 \text{ kHz}, 1 \text{ Vp-p} (V_{CC} 9 \text{ V}) (R_T \rightarrow R_{1OUT})$                                                      |

|                                                 |                       | -0.5 | 0    | 0.5  |      | $f = 1 \text{ kHz}, 1 \text{ Vp-p} (V_{CC} 5 \text{ V}) (R_T \rightarrow R_{1OUT})$                                                      |

| Frequency characteristics                       | F                     | -1   | 0    | 1    | dB   | f = 100 kHz/1 kHz, 1 Vp-p ( $R_T \rightarrow R_{1OUT}$ )                                                                                 |

| Total harmonic distortion                       | THD                   | —    | 0.01 | 0.05 | %    | f = 1 kHz, 2 Vp-p, at 400 Hz HPE + 30 kHz                                                                                                |

|                                                 |                       |      |      |      |      | LPF ( $R_T \rightarrow R_{1OUT}$ )                                                                                                       |

| Dynamic range                                   | D                     | 5.5  | 6.0  | —    | Vр-р | f = 1  kHz, Maximum with distortion < 0.5%                                                                                               |

|                                                 |                       |      |      |      |      | $(R_T \rightarrow R_{1OUT})$                                                                                                             |

| Output DC offset voltage                        | VOFF                  | -20  | 0    | 20   | mV   | (MODE: $R_T$ , $R_2$ , $R_3$ , $R_4 \rightarrow R_{10UT}$ )                                                                              |

| Input impedance                                 | Z1                    | 22   | 30   | 38   | kΩ   | (R <sub>T</sub> , R <sub>2</sub> , R <sub>3</sub> , R <sub>4</sub> , L <sub>T</sub> , L <sub>2</sub> , L <sub>3</sub> , L <sub>4</sub> ) |

| Crosstalk                                       | CT                    | —    | -90  | -84  | dB   | 1 kHz, 1 Vp-p $R_T \rightarrow R_{1OUT}$ (at $R_2$ mode)                                                                                 |

| I <sup>2</sup> C Bus control signal             | T                     | 1    | 1    | 1    | 1    |                                                                                                                                          |

| Max. input high voltage                         | VIH                   | 3.0  | —    | 5.0  | V    |                                                                                                                                          |

| Min. input low voltage                          | VIL                   | 0.0  | —    | 1.5  |      |                                                                                                                                          |

| Low level output voltage                        | V <sub>OL</sub>       | 0.0  |      | 0.4  |      | SDA = 3 mA                                                                                                                               |

| (SDA)                                           |                       | 40   |      | 10   | •    |                                                                                                                                          |

| High level input current                        | IIH                   | -10  |      | 10   | μA   | SDA, SCL = $4.5$ V                                                                                                                       |

| Low level input current                         | l <sub>IL</sub>       | -10  | —    | 10   | 60-  | SDA, SCL = 0.4 V                                                                                                                         |

| SCL clock frequency<br>Time of bus must be free | f <sub>SCL</sub>      | 0.0  | —    | 100  | kHz  |                                                                                                                                          |

| before a new transmission                       | t <sub>BUF</sub>      | 4.7  | _    | _    | μS   |                                                                                                                                          |

| can start                                       |                       |      |      |      |      |                                                                                                                                          |

| Hold time at start condition                    | t <sub>HD</sub> ; STA | 4.0  | _    |      |      |                                                                                                                                          |

| The low period of the clock                     | t <sub>LOW</sub>      | 4.7  |      |      |      |                                                                                                                                          |

| The high period of the                          | t <sub>HIGH</sub>     | 4.0  |      |      |      |                                                                                                                                          |

| clock                                           |                       |      |      |      |      |                                                                                                                                          |

| Step-up time for start                          | t <sub>SU</sub> ; STA | 4.7  | —    | —    |      |                                                                                                                                          |

| condition                                       | 1                     |      |      |      |      |                                                                                                                                          |

## **Electrical Characteristics (cont.)**

|                                    |                       |     |     |      |      | (Ta = $25^{\circ}$ C, V <sub>CC</sub> = 9 V, unless otherwise noted) |

|------------------------------------|-----------------------|-----|-----|------|------|----------------------------------------------------------------------|

| ltem                               | Symbol                | Min | Тур | Max  | Unit | Test Condition                                                       |

| Hold time DATA                     | t <sub>HD</sub> ; DAT | 5.0 | —   | —    | ns   |                                                                      |

| Setup time DATA                    | t <sub>SU</sub> ; DAT | 250 | —   | —    |      |                                                                      |

| Rise time of both SDA and SCL line | t <sub>R</sub>        | —   | —   | 1000 |      |                                                                      |

| Fall time of both SDA and SCL line | t <sub>F</sub>        | —   | —   | 300  |      |                                                                      |

| Setup time for stop condition      | t <sub>su</sub> ; STO | 4.0 | _   | _    | μS   |                                                                      |

## I<sup>2</sup>C Bus Control Signal

## **Application Circuit Example**

## Note How To Use This IC

- Input signal with sufficient low impedance to input terminal.

- The capacitance of output terminal as small as possible.

- Set the capacitance between  $V_{CC}$  and GND near the pins if possible.

- Assign an area as large as possible for grounding.

### **Power-on Reset**

- The M52791 has an internal power-on reset function that sets each control register to "0" during IC power ON.

- The power-on reset VTH has 2.5 V.

## **Package Dimensions**

## Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs! 1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

### Notes regarding these materials

- Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. Sumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- A second product on the information published by Refress Technology Corp. by Various means, including the Refress Technology Corp. Semiconductor home page (http://www.renessa.com).

When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use

- product contained herein for any specific purposes, such as apparatus or systems for transportation, venicular, metricar, acrospace, nector, or analysis of specific use. 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials. 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited. 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

### RENESAS SALES OFFICES

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com