## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

## SYNCHRONOUS BURST SRAM FLOW-THROUGH

#### FEATURES

- Fast access times: 7.5, 8, 8.5, and 10ns

- Fast clock speed: 117, 100, 90, and 50 MHz

- Provide high performance 2-1-1-1 access rate

- Fast OE# access times: 4.0ns

- 3.3V -5% and +10% core power supply

- 2.5V or 3.3V I/O supply

- 5V tolerant inputs except I/O's

- Clamp diodes to VSSQ at all inputs and outputs

- Common data inputs and data outputs

- BYTE WRITE ENABLE and GLOBAL WRITE control

- Three chip enables for depth expansion and address pipeline

- Address, data and control registers

- Internally self-timed WRITE CYCLE

- Burst control pins (interleaved or linear burst sequence)

- Automatic power-down for portable applications

- High density, high speed packages

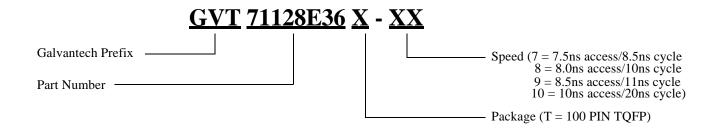

#### **OPTIONS**

### MARKING

| Timing                   |     |

|--------------------------|-----|

| 7.5ns access/8.5ns cycle | -7  |

| 8ns access/10ns cycle    | -8  |

| 8.5ns access/11ns cycle  | -9  |

| 10ns access/20ns cycle   | -10 |

| • | Packages     |   |

|---|--------------|---|

|   | 100-pin TQFP | Т |

## 128K x 36 SRAM

+3.3V CORE SUPPLY, +2.5V I/O SUPPLY REGISTERED INPUTS, BURST COUNTER

#### **GENERAL DESCRIPTION**

The Galvantech Synchronous Burst SRAM family employs high-speed, low power CMOS designs using advanced triple-layer polysilicon, double-layer metal technology. Each memory cell consists of four transistors and two high valued resistors.

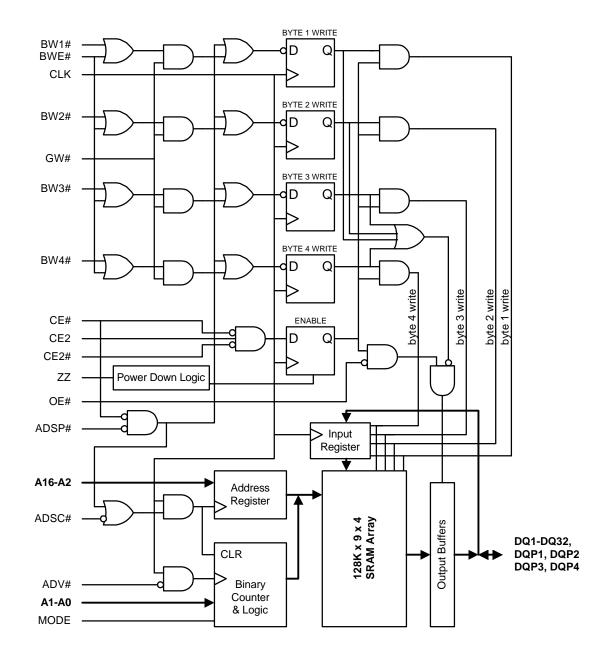

The GVT71128E36 SRAM integrates 131,072x36 SRAM cells with advanced synchronous peripheral circuitry and a 2-bit counter for internal burst operation. All synchronous inputs are gated by registers controlled by a positive-edge-triggered clock input (CLK). The synchronous inputs include all addresses, all data inputs, address-pipelining chip enable (CE#), depth-expansion chip enables (CE2# and CE2), burst control inputs (ADSC#, ADSP#, and ADV#), write enables (BW1#, BW2#, BW3#, BW4#,and BWE#), and global write (GW#).

Asynchronous inputs include the output enable (OE#), burst mode control (MODE), and sleep mode control (ZZ). The data outputs (Q), enabled by OE#, are also asynchronous.

Addresses and chip enables are registered with either address status processor (ADSP#) or address status controller (ADSC#) input pins. Subsequent burst addresses can be internally generated as controlled by the burst advance pin (ADV#).

Address, data inputs, and write controls are registered onchip to initiate self-timed WRITE cycle. WRITE cycles can be one to four bytes wide as controlled by the write control inputs. Individual byte write allows individual byte to be written. BW1# controls DQ1-DQ8 and DQP1. BW2# controls DQ9-DQ16 and DQP2. BW3# controls DQ17-DQ24 and DQP3. BW4# controls DQ25-DQ32 and DQP4. BW1#, BW2# BW3#, and BW4# can be active only with BWE# being LOW. GW# being LOW causes all bytes to be written.

The GVT71128E36 operates from a +3.3V core power supply and all outputs operate on a +2.5V supply. All inputs and outputs are JEDEC standard JESD8-5 compatible. The device is ideally suited for 486, Pentium<sup>TM</sup>, 680x0, and PowerPC<sup>TM</sup> systems and for systems that are benefited from a wide synchronous data bus.

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

#### FUNCTIONAL BLOCK DIAGRAM

**NOTE:** The Functional Block Diagram illustrates simplified device operation. See Truth Table, pin descriptions and timing diagrams for detailed information.

February 27, 1997 Rev. 2/97

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

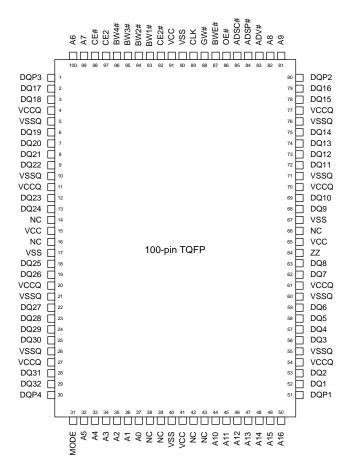

#### PIN ASSIGNMENT (Top View)

### **PIN DESCRIPTIONS**

| TQFP PINS                                                                   | SYMBOL                          | TYPE                  | DESCRIPTION                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------|---------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37, 36, 35, 34, 33,<br>32, 100, 99, 82, 81,<br>44, 45, 46, 47, 48,<br>49,50 | A0-A16                          | Input-<br>Synchronous | Addresses: These inputs are registered and must meet the setup and hold times around the rising edge of CLK. The burst counter generates internal addresses associated with A0 and A1, during burst cycle and wait cycle.                                                                                       |

| 93,94,95,96                                                                 | BW1#,<br>BW2#,<br>BW3#,<br>BW4# | Input-<br>Synchronous | Byte Write: A byte write is LOW for a WRITE cycle and HIGH for a READ cycle. BW1# controls DQ1-DQ8 and DQP1. BW2# controls DQ9-DQ16 and DQP2. BW3# controls DQ17-DQ24 and DQP3. BW4# controls DQ25-DQ32 and DQP4. Data I/O are high impedance if either of these inputs are LOW, conditioned by BWE# being LOW. |

| 87                                                                          | BWE#                            | Input-<br>Synchronous | Write Enable: This active LOW input gates byte write operations and must meet the setup and hold times around the rising edge of CLK.                                                                                                                                                                           |

| 88                                                                          | GW#                             | Input-<br>Synchronous | Global Write: This active LOW input allows a full 36-bit WRITE to occur independent of the BWE# and BWn# lines and must meet the setup and hold times around the rising edge of CLK.                                                                                                                            |

| 89                                                                          | CLK                             | Input-<br>Synchronous | Clock: This signal registers the addresses, data, chip enables, write control and burst control inputs on its rising edge. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                |

| 98                                                                          | CE#                             | Input-<br>Synchronous | Chip Enable: This active LOW input is used to enable the device and to gate ADSP#.                                                                                                                                                                                                                              |

| 92                                                                          | CE2#                            | Input-<br>Synchronous | Chip Enable: This active LOW input is used to enable the device.                                                                                                                                                                                                                                                |

Downloaded from Elcodis.com electronic components distributor

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

## PIN DESCRIPTIONS (continued)

| TQFP PINS                                                                                                | SYMBOL                    | TYPE                   | DESCRIPTION                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------|---------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 97                                                                                                       | CE2                       | input-<br>Synchronous  | Chip enable: This active HIGH input is used to enable the device.                                                                                                                                                      |

| 86                                                                                                       | OE#                       | Input                  | Output Enable: This active LOW asynchronous input enables the data output drivers.                                                                                                                                     |

| 83                                                                                                       | ADV#                      | Input-<br>Synchronous  | Address Advance: This active LOW input is used to control the internal burst counter. A HIGH on this pin generates wait cycle (no address advance).                                                                    |

| 84                                                                                                       | ADSP#                     | Input-<br>Synchronous  | Address Status Processor: This active LOW input, along with CE# being LOW, causes<br>a new external address to be registered and a READ cycle is initiated using the new<br>address.                                   |

| 85                                                                                                       | ADSC#                     | Input-<br>Synchronous  | Address Status Controller: This active LOW input causes device to be de-selected or selected along with new external address to be registered. A READ or WRITE cycle is initiated depending upon write control inputs. |

| 31                                                                                                       | MODE                      | Input-<br>Static       | Mode: This input selects the burst sequence. A LOW on this pin selects LINEAR BURST. A NC or HIGH on this pin selects INTERLEAVED BURST.                                                                               |

| 64                                                                                                       | ZZ                        | Input-<br>Asynchronous | Snooze: This active HIGH input puts the device in low power consumption standby mode. For normal operation, this input has to be either LOW or NC (No Connect).                                                        |

| 52, 53, 56, 57, 58, 59,<br>62, 63, 68, 69, 72-75,<br>78, 79, 2, 3, 6-9, 12, 13,<br>18, 19, 22-25, 28, 29 | DQ1-DQ32                  | Input/<br>Output       | Data Inputs/Outputs: First Byte is DQ1-DQ8. Second Byte is DQ9-DQ16. Third Byte is DQ17-DQ24. Fourth Byte is DQ25-DQ32. Input data must meet setup and hold times around the rising edge of CLK.                       |

| 51, 80, 1, 30                                                                                            | DQP1, DQP2,<br>DQP3, DQP4 | Input/<br>Output       | Parity Inputs/Outputs: DQP1 is parity bit for DQ1-DQ8 and DQP2 is parity bit for DQ9-DQ16. DQP3 is parity bit for DQ17-DQ24 and DQP4 is parity bit for DQ25-DQ32.                                                      |

| 15, 41,65, 91                                                                                            | VCC                       | Supply                 | Core power Supply: +3.3V -5% and +10%                                                                                                                                                                                  |

| 17, 40, 67, 90                                                                                           | VSS                       | Ground                 | Ground: GND.                                                                                                                                                                                                           |

| 4, 11, 20, 27, 54, 61, 70,<br>77                                                                         | VCCQ                      | I/O Supply             | Output Buffer Supply: +2.5V (from 2.375V to VCC)                                                                                                                                                                       |

| 5, 10, 21, 26, 55, 60, 71,<br>76                                                                         | VSSQ                      | I/O Ground             | Output Buffer Ground: GND                                                                                                                                                                                              |

| 14, 16, 38, 39, 42, 43,66                                                                                | NC                        | -                      | No Connect: These signals are not internally connected.                                                                                                                                                                |

## **BURST ADDRESS TABLE (MODE = NC/VCCQ)**

| First Address<br>(external) | Second Address<br>(internal) | Third Address<br>(internal) | Fourth Address<br>(internal) |  |  |  |

|-----------------------------|------------------------------|-----------------------------|------------------------------|--|--|--|

| AA00                        | AA01                         | AA10                        | AA11                         |  |  |  |

| AA01                        | AA00                         | AA11                        | AA10                         |  |  |  |

| AA10                        | AA11                         | AA00                        | AA01                         |  |  |  |

| AA11                        | AA10                         | AA01                        | AA00                         |  |  |  |

#### **BURST ADDRESS TABLE (MODE = GND)**

| First Address<br>(external) | Second Address<br>(internal) | Third Address<br>(internal) | Fourth Address<br>(internal) |

|-----------------------------|------------------------------|-----------------------------|------------------------------|

| AA00                        | AA01                         | AA10                        | AA11                         |

| AA01                        | AA10                         | AA11                        | AA00                         |

| AA10                        | AA11                         | AA00                        | AA01                         |

| AA11                        | AA00                         | AA01                        | AA10                         |

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

### **TRUTH TABLE**

| OPERATION                    | ADDRESS<br>USED | CE# | CE2# | CE2 | ADSP# | ADSC# | ADV# | WRITE# | OE# | CLK | DQ     |

|------------------------------|-----------------|-----|------|-----|-------|-------|------|--------|-----|-----|--------|

| Deselected Cycle, Power Down | None            | Н   | Х    | Х   | Х     | L     | Х    | Х      | Х   | L-H | High-Z |

| Deselected Cycle, Power Down | None            | L   | Х    | L   | L     | Х     | Х    | Х      | Х   | L-H | High-Z |

| Deselected Cycle, Power Down | None            | L   | Н    | Х   | L     | Х     | Х    | Х      | Х   | L-H | High-Z |

| Deselected Cycle, Power Down | None            | L   | Х    | L   | Н     | L     | Х    | Х      | Х   | L-H | High-Z |

| Deselected Cycle, Power Down | None            | L   | Н    | Х   | Н     | L     | Х    | Х      | Х   | L-H | High-Z |

| READ Cycle, Begin Burst      | External        | L   | L    | Н   | L     | Х     | Х    | Х      | L   | L-H | Q      |

| READ Cycle, Begin Burst      | External        | L   | L    | Н   | L     | Х     | Х    | Х      | Н   | L-H | High-Z |

| WRITE Cycle, Begin Burst     | External        | L   | L    | Н   | Н     | L     | Х    | L      | Х   | L-H | D      |

| READ Cycle, Begin Burst      | External        | L   | L    | Н   | Н     | L     | Х    | Н      | L   | L-H | Q      |

| READ Cycle, Begin Burst      | External        | L   | L    | Н   | Н     | L     | Х    | Н      | Н   | L-H | High-Z |

| READ Cycle, Continue Burst   | Next            | Х   | Х    | Х   | Н     | Н     | L    | Н      | L   | L-H | Q      |

| READ Cycle, Continue Burst   | Next            | Х   | Х    | Х   | Н     | Н     | L    | Н      | Н   | L-H | High-Z |

| READ Cycle, Continue Burst   | Next            | н   | Х    | Х   | Х     | Н     | L    | Н      | L   | L-H | Q      |

| READ Cycle, Continue Burst   | Next            | н   | Х    | Х   | Х     | Н     | L    | Н      | Н   | L-H | High-Z |

| WRITE Cycle, Continue Burst  | Next            | Х   | Х    | Х   | Н     | Н     | L    | L      | Х   | L-H | D      |

| WRITE Cycle, Continue Burst  | Next            | н   | Х    | Х   | Х     | Н     | L    | L      | Х   | L-H | D      |

| READ Cycle, Suspend Burst    | Current         | Х   | Х    | Х   | Н     | Н     | Н    | Н      | L   | L-H | Q      |

| READ Cycle, Suspend Burst    | Current         | Х   | Х    | Х   | Н     | Н     | Н    | Н      | Н   | L-H | High-Z |

| READ Cycle, Suspend Burst    | Current         | Н   | Х    | Х   | Х     | Н     | Н    | Н      | L   | L-H | Q      |

| READ Cycle, Suspend Burst    | Current         | Н   | Х    | Х   | Х     | Н     | Н    | Н      | Н   | L-H | High-Z |

| WRITE Cycle, Suspend Burst   | Current         | Х   | Х    | Х   | Н     | Н     | Н    | L      | Х   | L-H | D      |

| WRITE Cycle, Suspend Burst   | Current         | Н   | Х    | Х   | Х     | Н     | Н    | L      | Х   | L-H | D      |

Note: 1. X means "don't care." H means logic HIGH. L means logic LOW. WRITE# = L means [BWE# + BW1#\*BW2#\*BW3#\*BW4#]\*GW# equals LOW. WRITE# = H means [BWE# + BW1#\*BW2#\*BW3#\*BW4#]\*GW# equals HIGH.

2. BW1# enables write to DQ1-DQ8 and DQP1. BW2# enables write to DQ9-DQ16 and DQP2. BW3# enables write to DQ17-DQ24 and DQP3. BW4# enables write to DQ25-DQ32 and DQP4.

- 3. All inputs except OE# must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

- 4. Suspending burst generates wait cycle.

- 5. For a write operation following a read operation, OE# must be HIGH before the input data required setup time plus High-Z time for OE# and staying HIGH throughout the input data hold time.

- 6. This device contains circuitry that will ensure the outputs will be in High-Z during power-up.

- ADSP# LOW along with chip being selected always initiates an READ cycle at the L-H edge of CLK. A WRITE cycle can be

performed by setting WRITE# LOW for the CLK L-H edge of the subsequent wait cycle. Refer to WRITE timing diagram for

clarification.

| FUNCTION        | GW# | BWE# | BW1# | BW2# | BW3# | BW4# |

|-----------------|-----|------|------|------|------|------|

| READ            | Н   | Н    | Х    | Х    | Х    | Х    |

| READ            | Н   | L    | Н    | Н    | Н    | Н    |

| WRITE one byte  | Н   | L    | L    | Н    | Н    | Н    |

| WRITE all bytes | Н   | L    | L    | L    | L    | L    |

| WRITE all bytes | L   | Х    | Х    | Х    | Х    | Х    |

### PARTIAL TRUTH TABLE FOR READ/WRITE

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on VCC Supply Relative to VSS. | 0.5V to +4.6V     |

|----------------------------------------|-------------------|

| V <sub>IN</sub>                        | 0.5V to VCC+0.5V  |

| Storage Temperature (plastic)          | 55°C to +125°     |

| Junction Temperature                   | +125 <sup>o</sup> |

| Power Dissipation                      | 1.6W              |

| Short Circuit Output Current (per I/O) | 20mA              |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### DC ELECTRICAL CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS

$(0^{\circ}C \le T_a \le 70^{\circ}C; VCC = 3.3V - 5\% \text{ and } +10\% \text{ unless otherwise noted})$

| DESCRIPTION                  | CONDITIONS                                     | SYMBOL           | MIN   | МАХ     | UNITS | NOTES |

|------------------------------|------------------------------------------------|------------------|-------|---------|-------|-------|

| Input High (Logic 1) Voltage | Data Inputs (DQxx)                             | V <sub>IHD</sub> | 1.7   | VCC+0.3 | V     | 1,2   |

|                              | All Other Inputs                               | V <sub>IH</sub>  | 1.7   | 4.6     | V     | 1,2   |

| Input Low (Logic 0) Voltage  |                                                | V <sub>II</sub>  | -0.3  | 0.7     | V     | 1, 2  |

| Input Leakage Current        | $0V \le V_{IN} \le VCC$                        | IL <sub>I</sub>  | -2    | 2       | uA    | 14    |

| Output Leakage Current       | Output(s) disabled, $0V \leq V_{OUT} \leq VCC$ | ΙL <sub>O</sub>  | -2    | 2       | uA    |       |

| Output High Voltage          | I <sub>OH</sub> = -2.0mA                       | V <sub>OH</sub>  | 1.7   |         | V     | 1, 11 |

| Output Low Voltage           | I <sub>OL</sub> = 2.0mA                        | V <sub>OL</sub>  |       | 0.7     | V     | 1, 11 |

| Supply Voltage               |                                                | VCC              | 3.135 | 3.6     | V     | 1     |

| I/O Supply Voltage           |                                                | VCCQ             | 2.375 | VCC     | V     | 1     |

| DESCRIPTION                        | CONDITIONS                                                                                                                                  | SYM              | TYP | -7  | -8  | -9  | -10 | UNITS | NOTES     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|-----|-----|-------|-----------|

| Power Supply<br>Current: Operating | Device selected; all inputs $\leq V_{IL}$ or $\geq V_{IH}$ ; cycle time $\geq {}^{t}$ KC MIN; VCC =MAX; outputs open                        | Icc              | 150 | 370 | 320 | 290 | 200 | mA    | 3, 12, 13 |

| CMOS Standby                       | Device deselected; VCC = MAX;<br>all inputs $\leq$ VSS +0.2 or $\geq$ VCC -0.2;<br>all inputs static; CLK frequency = 0                     | I <sub>SB2</sub> | 5   | 10  | 10  | 10  | 10  | mA    | 12,13     |

| TTL Standby                        | Device deselected; all inputs $\leq V_{IL}$<br>or $\geq V_{IH}$ ; all inputs static;<br>VCC = MAX; CLK frequency = 0                        | I <sub>SB3</sub> | 10  | 20  | 20  | 20  | 20  | mA    | 12,13     |

| Clock Running                      | Device deselected;<br>all inputs $\leq$ V <sub>IL</sub> or $\geq$ V <sub>IH</sub> ; VCC = MAX;<br>CLK cycle time $\geq$ <sup>t</sup> KC MIN | I <sub>SB4</sub> | 40  | 80  | 70  | 60  | 40  | mA    | 12,13     |

Downloaded from Elcodis.com electronic components distributor

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

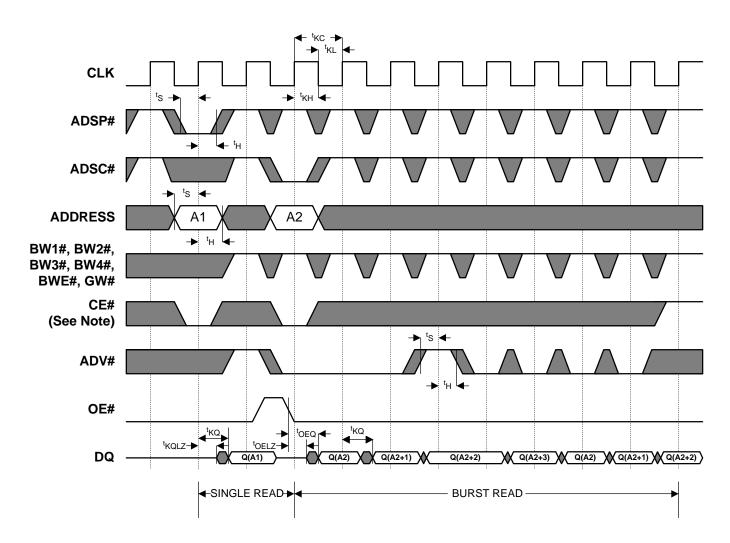

## AC ELECTRICAL CHARACTERISTICS

(Note 5) ( $0^{\circ}C \leq T_{A} \leq 70^{\circ}C$ ; VCC = 3.3V -5% and +10%)

| DESCRIPTION                   |                   | - 7 |     | - 8 |     | - 9 |     | - 10 |     |       |        |

|-------------------------------|-------------------|-----|-----|-----|-----|-----|-----|------|-----|-------|--------|

| DESCRIPTION                   | SYM               | MIN | МАХ | MIN | МАХ | MIN | MAX | MIN  | MAX | UNITS | NOTES  |

| Clock                         |                   |     | *   |     | •   |     |     |      |     |       |        |

| Clock cycle time              | <sup>t</sup> KC   | 8.5 |     | 10  |     | 11  |     | 20   |     | ns    |        |

| Clock HIGH time               | <sup>t</sup> KH   | 3   |     | 4   |     | 4.5 |     | 4.5  |     | ns    |        |

| Clock LOW time                | <sup>t</sup> KL   | 3   |     | 4   |     | 4.5 |     | 4.5  |     | ns    |        |

| Output Times                  |                   |     |     |     |     |     |     |      |     |       |        |

| Clock to output valid         | <sup>t</sup> KQ   |     | 7.5 |     | 8   |     | 8.5 |      | 10  | ns    |        |

| Clock to output invalid       | <sup>t</sup> KQX  | 2   |     | 2   |     | 2   |     | 2    |     | ns    |        |

| Clock to output in Low-Z      | <sup>t</sup> KQLZ | 0   |     | 0   |     | 0   |     | 0    |     | ns    | 4, 6,7 |

| Clock to output in High-Z     | <sup>t</sup> KQHZ | 2   | 3.5 | 2   | 3.5 | 2   | 3.5 | 2    | 3.5 | ns    | 4, 6,7 |

| OE to output valid            | <sup>t</sup> OEQ  |     | 4.0 |     | 4.0 |     | 4.0 |      | 4.0 | ns    | 9      |

| OE to output in Low-Z         | <sup>t</sup> OELZ | 0   |     | 0   |     | 0   |     | 0    |     | ns    | 4, 6,7 |

| OE to output in High-Z        | <sup>t</sup> OEHZ |     | 3.5 |     | 3.5 |     | 3.5 |      | 3.5 | ns    | 4, 6,7 |

| Setup Times                   |                   |     |     |     |     |     |     |      |     |       |        |

| Address, Controls and Data In | <sup>t</sup> S    | 1.5 |     | 2.0 |     | 2.0 |     | 2.0  |     | ns    | 10     |

| Hold Times                    |                   |     |     |     |     |     |     |      |     |       |        |

| Address, Controls and Data In | tH                | 0.5 |     | 0.5 |     | 0.5 |     | 0.5  |     | ns    | 10     |

## CAPACITANCE

| DESCRIPTION                   | CONDITIONS                     | SYMBOL         | ТҮР | МАХ | UNITS | NOTES |

|-------------------------------|--------------------------------|----------------|-----|-----|-------|-------|

| Input Capacitance             | $T_A = 25^{\circ}C; f = 1 MHz$ | CI             | 4   | 5   | pF    | 4     |

| Input/Output Capacitance (DQ) | VCC = 3.3V                     | C <sub>O</sub> | 7   | 8   | pF    | 4     |

### THERMAL CONSIDERATION

| DESCRIPTION                              | CONDITIONS                    | SYMBOL          | TQFP TYP | UNITS | NOTES |

|------------------------------------------|-------------------------------|-----------------|----------|-------|-------|

| Thermal Resistance - Junction to Ambient | Still air, soldered on 4.25 x | $\Theta_{JA}$   | 25       | °C/W  |       |

| Thermal Resistance - Junction to Case    | 1.125 inch 4-layer PCB        | Θ <sub>JC</sub> | 9        | °C/W  |       |

## **TYPICAL OUTPUT BUFFER CHARACTERISTICS**

| OUTPUT HIGH<br>VOLTAGE | PULL-UP CURRENT |             | OUTPUT LOW<br>VOLTAGE | PULL-DOWN CURRE |             |

|------------------------|-----------------|-------------|-----------------------|-----------------|-------------|

| VOH (V)                | IOH(mA) Min     | IOH(mA) Max | VOL (V)               | IOL(mA) Min     | IOL(mA) Max |

| -0.5                   | -38             | -105        | -0.5                  | 0               | 0           |

| 0                      | -38             | -105        | 0                     | 0               | 0           |

| 0.8                    | -38             | -105        | 0.4                   | 10              | 20          |

| 1.25                   | -26             | -83         | 0.8                   | 20              | 40          |

| 1.5                    | -20             | -70         | 1.25                  | 31              | 63          |

| 2.3                    | 0               | -30         | 1.6                   | 40              | 80          |

| 2.7                    | 0               | -10         | 2.8                   | 40              | 80          |

| 2.9                    | 0               | 0           | 3.2                   | 40              | 80          |

| 3.4                    | 0               | 0           | 3.4                   | 40              | 80          |

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

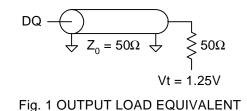

#### AC TEST CONDITIONS

| Input pulse levels              | 0V to 2.5V    |  |  |

|---------------------------------|---------------|--|--|

| Input slew rate                 | 1.0V/ns       |  |  |

| Output rise and fall times(max) | 1.8ns         |  |  |

| Input timing reference levels   | 1.25V         |  |  |

| Output reference levels         | 1.25V         |  |  |

| Output load                     | See Figures 1 |  |  |

#### **OUTPUT LOADS**

#### NOTES

- 1. All voltages referenced to VSS (GND).

- 2. Overshoot:  $V_{IH} \le +6.0V$  for  $t \le {}^{t}KC/2$ . Undershoot:  $V_{IL} \le -2.0V$  for  $t \le {}^{t}KC/2$

- 3.  $I_{cc}$  is given with no output current.  $I_{cc}$  increases with greater output loading and faster cycle times.

- 4. This parameter is sampled.

- 5. Test conditions as specified with the output loading as shown in Fig. 1 unless otherwise noted.

- 6. Measured at  $\pm$  200mV from steady state.

- At any given temperature and voltage condition, <sup>t</sup>KQHZ is less than <sup>t</sup>KQLZ and <sup>t</sup>OEHZ is less than <sup>t</sup>OELZ.

- A READ cycle is defined by byte write enables all HIGH or ADSP# LOW along with chip enables being active for the required setup and hold times. A WRITE cycle is defined by at one byte or all byte WRITE per READ/WRITE TRUTH TABLE.

- 9. OE# is a "don't care" when a byte write enable is sampled LOW.

- 10. This is a synchronous device. All synchronous inputs must meet specified setup and hold time, except for "don't care" as defined in the truth table.

- 11. AC I/O curves are available upon request.

- 12. "Device Deselected" means the device is in POWER -DOWN mode as defined in the truth table. "Device Selected" means the device is active.

- 13. Typical values are measured at 3.3V, 25°C and 20ns cycle time.

- 14. MODE pin has an internal pull-up and ZZ pin has an internal pull-down. These two pins exhibit an input leakage current of  $\pm 30 \ \mu$ A.

February 27, 1997 Rev. 2/97 15. Capacitance derating applies to capacitance different from the load capacitance shown in Fig. 1.

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

## **READ TIMING**

Note: CE# active in this timing diagram means that all chip enables CE#, CE2, and CE2# are active.

February 27, 1997 Rev. 2/97

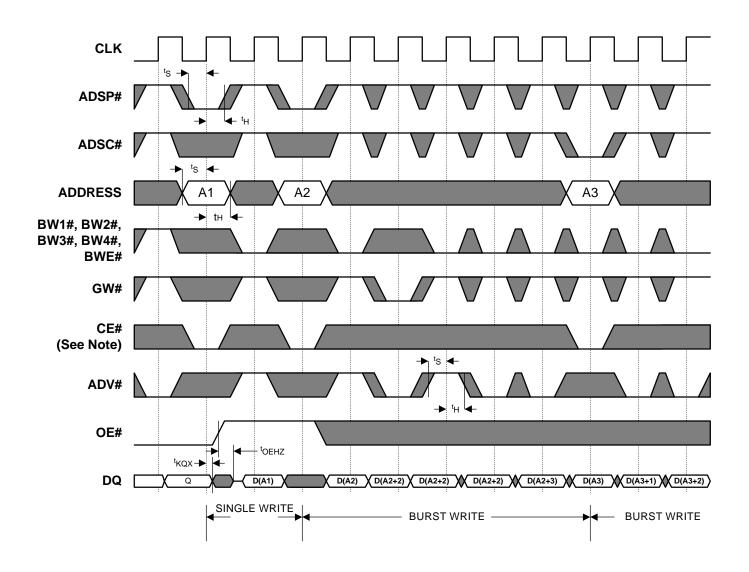

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

## WRITE TIMING

Note: CE# active in this timing diagram means that all chip enables CE#, CE2, and CE2# are active.

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

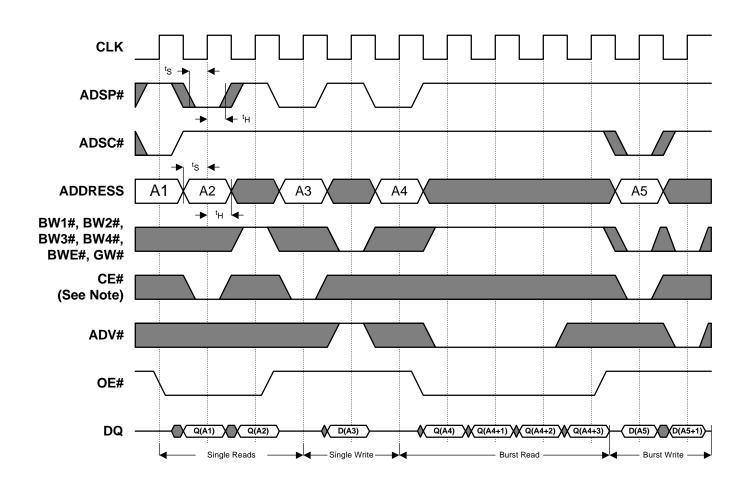

## **READ/WRITE TIMING**

Note: CE# active in this timing diagram means that all chip enables CE#, CE2, and CE2# are active.

## GVT71128E36 128K X 36 SYNCHRONOUS BURST SRAM

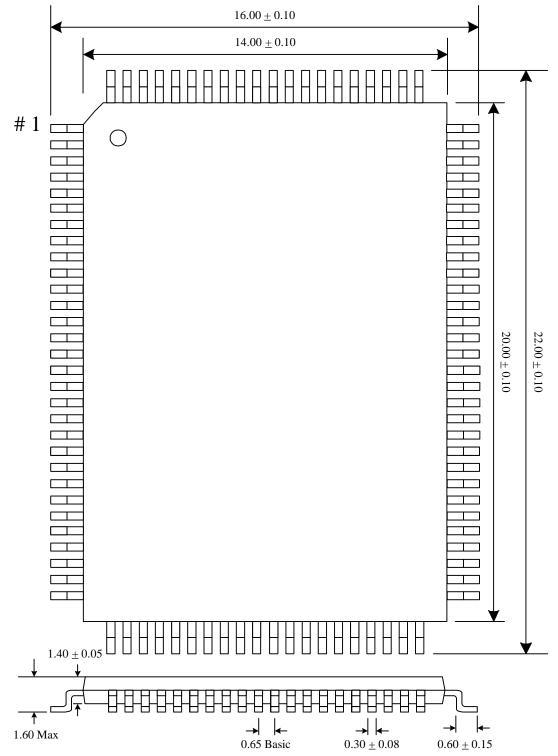

### **100 Pin TQFP Package Dimensions**

Note: All dimensions in Millimeters

February 27, 1997 Rev. 2/97

## **Ordering Information**

Downloaded from Elcodis.com electronic components distributor