# HA1630S08

# Single CMOS High Drive Operational Amplifier

REJ03D0908-0100 Rev.1.00 Feb 22, 2008

### **Description**

HA1630S08 is a low power single CMOS operational amplifier featuring high output current with typical current supply of 170  $\mu$ A (2.7 - 5.5 V). This IC designed to operate from a single power supply and have full swing outputs. Available in CMPAK-5 and MPAK-5 package, the miniature size of this IC not only allows compact integration in portable devices but also minimizes distance of signal sources (sensors), thus reducing external noise pick up prior to amplification. This IC exhibit excellent current drive-power ratio capable of 600  $\Omega$  load driving and yet resistant to oscillation for capacitive loads up to 400 pF.

#### **Features**

• Low supply current  $I_{DD} = 170 \mu A \text{ Typ } (V_{DD} = 3 \text{ V}, R_L = \text{No load})$

Low voltage operation V<sub>DD</sub> = 2.7 V to 5.5 V

Low input offset voltage V<sub>IO</sub> = 6 mV Max

Low input bias current I<sub>IB</sub> = 1 pA Typ

• High output current  $I_{OSOURCE} = 30 \text{ mA Typ } (V_{DD} = 3.0 \text{ V}, V_{OH} = 2.5 \text{ V})$

$I_{OSINK} = 30 \text{ mA Typ } (V_{DD} = 3.0 \text{ V}, V_{OL} = 0.5 \text{ V})$

• Input common voltage range includes ground

## **Ordering Information**

| Part No.    | Package Name | Package Code |

|-------------|--------------|--------------|

| HA1630S08CM | CMPAK-5      | PTSP0005ZC-A |

| HA1630S08LP | MPAK-5       | PLSP0005ZB-A |

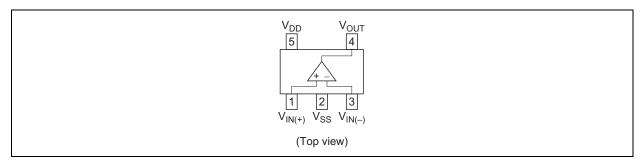

# **Pin Arrangement**

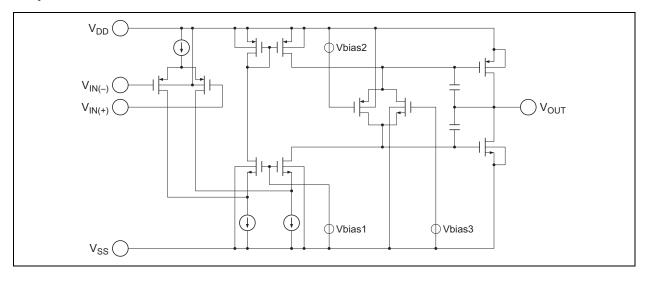

# **Equivalent Circuit**

# **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C)$

| Item                       | Symbol           | Ratings                  | Unit | Note |

|----------------------------|------------------|--------------------------|------|------|

| Supply voltage             | $V_{DD}$         | 7.0                      | V    |      |

| Differential input voltage | $V_{IN(diff)}$   | $-V_{DD}$ to $+V_{DD}$   | V    | 1    |

| Input voltage              | V <sub>IN</sub>  | -0.1 to +V <sub>DD</sub> | V    |      |

| Output current             | I <sub>OUT</sub> | 70                       | mA   |      |

| Power dissipation          | P <sub>T</sub>   | 80 (CMPAK-5)             | mW   | 2    |

|                            |                  | 120 (MPAK-5)             |      |      |

| Operating temperature      | Topr             | -40 to +85               | °C   |      |

| Storage temperature        | Tstg             | -55 to +125              | °C   |      |

Note: 1. Do not apply input voltage exceeding  $V_{DD}$  or 7 V.

2. If Ta > 25°C,

CMPAK-5: -0.8 mW/°C MPAK-5: -1.2 mW/°C

### **Electrical Characteristics**

#### **DC Characteristics**

$(Ta = 25^{\circ}C, V_{DD} = 3.0 \text{ V}, V_{SS} = 0 \text{ V})$

| Item                            | Symbol               | Min  | Тур | Max | Unit | Test Conditions                                    |

|---------------------------------|----------------------|------|-----|-----|------|----------------------------------------------------|

| Input offset voltage            | V <sub>IO</sub>      | _    | _   | 6   | mV   | $V_{IN} = 1.5 \text{ V}, R_L = 1 \text{ M}\Omega$  |

| Input bias current              | I <sub>IB</sub>      | _    | (1) | _   | pА   | V <sub>IN</sub> = 1.5 V                            |

| Input offset current            | I <sub>IO</sub>      | _    | (1) | _   | pА   | V <sub>IN</sub> = 1.5 V                            |

| Common mode input voltage range | V <sub>CM</sub>      | -0.1 | _   | 1.8 | V    |                                                    |

| Supply current                  | I <sub>DD</sub>      | _    | 170 | 500 | μΑ   | $V_{IN(+)} = 1.0 \text{ V}, R_L = \infty$          |

| Output source current           | I <sub>OSOURCE</sub> | 15   | 30  | _   | mA   | Vout = 2.5 V                                       |

| Output sink current             | I <sub>OSINK</sub>   | 15   | 30  | _   | mA   | Vout = 0.5 V                                       |

| Open loop voltage gain          | A <sub>V</sub>       | 55   | 80  | _   | dB   | $R_L = 100 \text{ k}\Omega$                        |

| Common mode rejection ratio     | CMRR                 | 50   | 80  | _   | dB   | $V_{IN1} = 0 \text{ V}, V_{IN2} = 1.8 \text{ V}$   |

| Power supply rejection ratio    | PSRR                 | 55   | 80  | _   | dB   | $V_{DD1} = 2.7 \text{ V}, V_{DD2} = 5.5 \text{ V}$ |

| Output high voltage             | V <sub>OH</sub>      | 2.9  | _   |     | V    | $R_L = 600 \Omega$ to $V_{SS}$                     |

| Output low voltage              | V <sub>OL</sub>      | _    | _   | 0.1 | V    | $R_L = 600 \Omega$ to $V_{DD}$                     |

Note: (): Design specification

#### **AC Characteristics**

$(Ta = 25^{\circ}C, V_{DD} = 3.0 \text{ V}, V_{SS} = 0 \text{ V})$

| Item                   | Symbol | Min | Тур   | Max | Unit | Test Conditions                                      |

|------------------------|--------|-----|-------|-----|------|------------------------------------------------------|

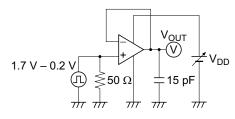

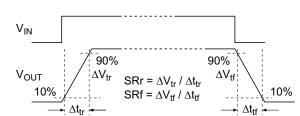

| Slew rate              | SRr    |     | (1.5) | 1   | V/μs | $V_{IN} = 1.5 \text{ V}, C_L = 15 \text{ pF}$        |

|                        | SRf    |     | (1.5) |     |      | $(V_{INL} = 0.2 \text{ V}, V_{INH} = 1.7 \text{ V})$ |

| Gain bandwidth product | GBW    | _   | (2.0) | _   | MHz  | $V_{IN} = 1.5 \text{ V}, C_L = 15 \text{ pF}$        |

Note: (): Design specification

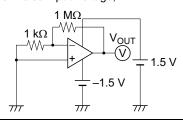

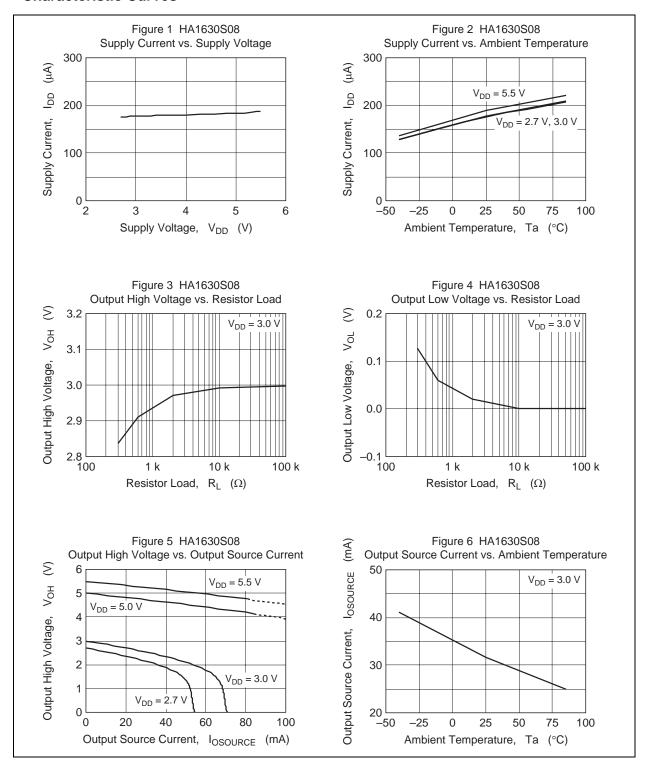

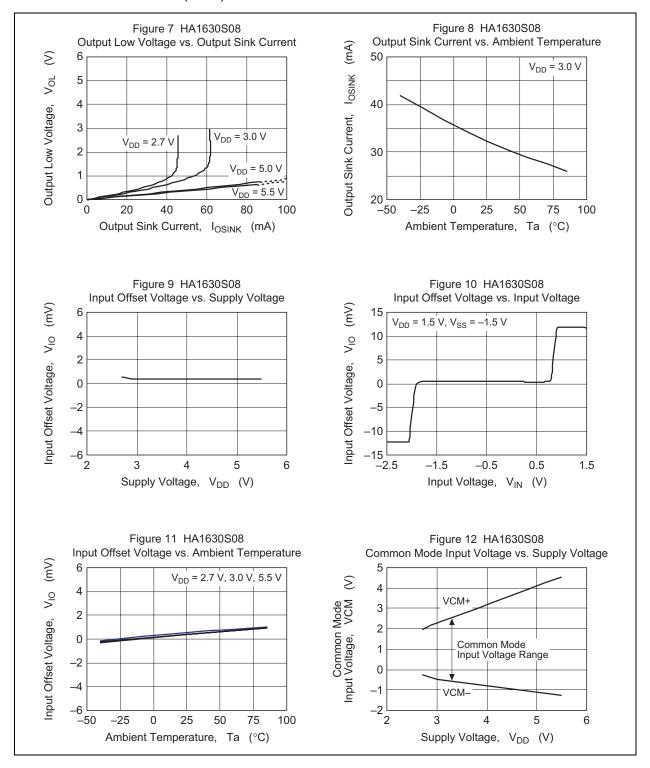

# **Table of Graphs**

| Electrical Cl                   | naracteristics       |                         | Characteristic Curves | Test<br>Circuit No. |

|---------------------------------|----------------------|-------------------------|-----------------------|---------------------|

| Supply current                  | I <sub>DD</sub>      | vs. Supply voltage      | 1                     | 1                   |

|                                 |                      | vs. Temperature         | 2                     | 1                   |

| Output high voltage             | V <sub>OH</sub>      | vs. Rload               | 3                     | 2                   |

| Output low voltage              | V <sub>OL</sub>      | vs. Rload               | 4                     | 3                   |

| Output source current           | I <sub>OSOURCE</sub> | vs. Output high voltage | 5                     | 4                   |

|                                 |                      | vs. Temperature         | 6                     | 4                   |

| Output sink current             | I <sub>OSINK</sub>   | vs. Output low voltage  | 7                     | 5                   |

|                                 |                      | vs. Temperature         | 8                     | 5                   |

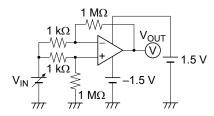

| Input offset voltage            | V <sub>IO</sub>      | vs. Supply voltage      | 9                     | 6                   |

|                                 |                      | vs. Input voltage       | 10                    | 6                   |

|                                 |                      | vs. Temperature         | 11                    | 7                   |

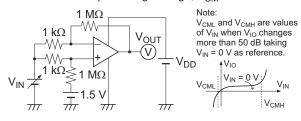

| Common mode input voltage range | V <sub>CM</sub>      | vs. Supply voltage      | 12                    | 8                   |

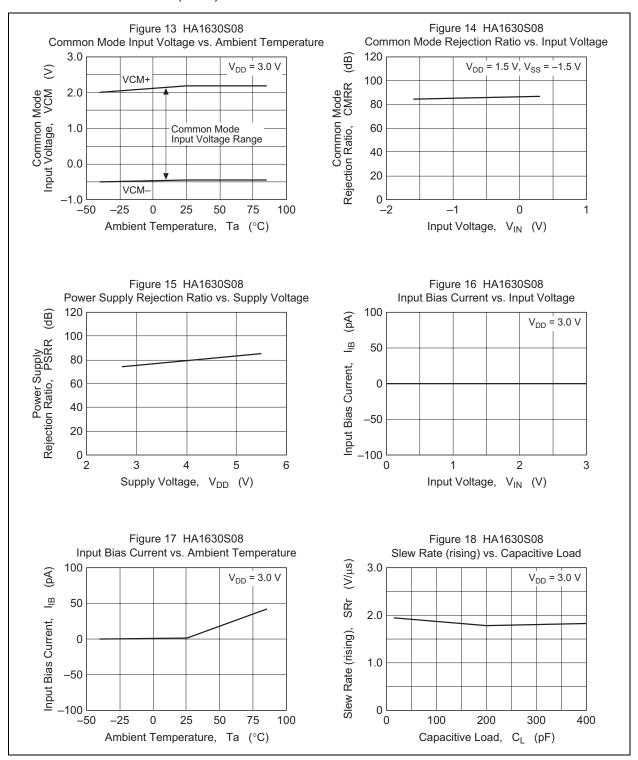

|                                 |                      | vs. Temperature         | 13                    | 8                   |

| Common mode rejection ratio     | CMRR                 | vs. Input voltage       | 14                    | 9                   |

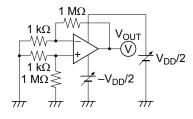

| Power supply rejection ratio    | PSRR                 | vs. Supply voltage      | 15                    | 10                  |

| Input bias current              | I <sub>IB</sub>      | vs. Input voltage       | 16                    | 11, 12              |

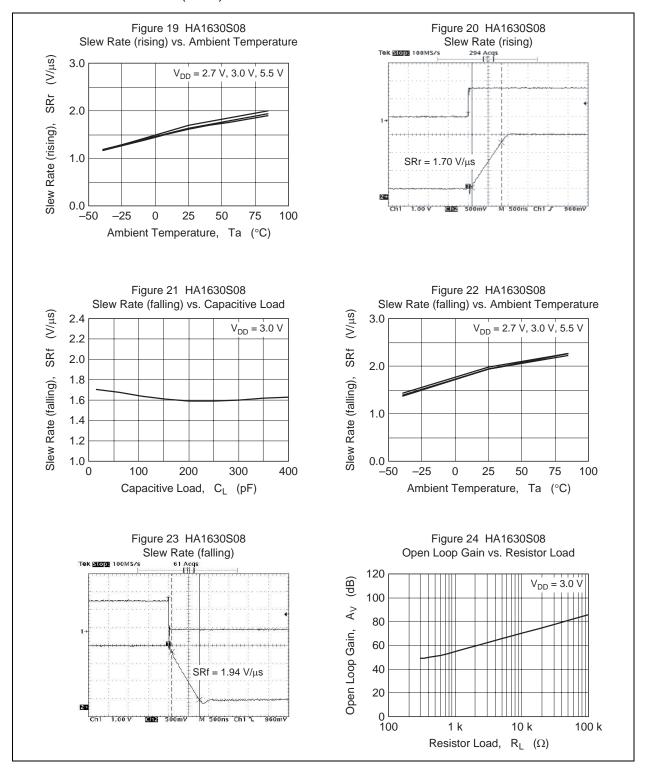

|                                 |                      | vs. Temperature         | 17                    | 11, 12              |

| Slew rate (rising)              | SRr                  | vs. Cload               | 18                    | 13                  |

|                                 |                      | vs. Temperature         | 19                    | 13                  |

|                                 |                      | Time waveform           | 20                    | 13                  |

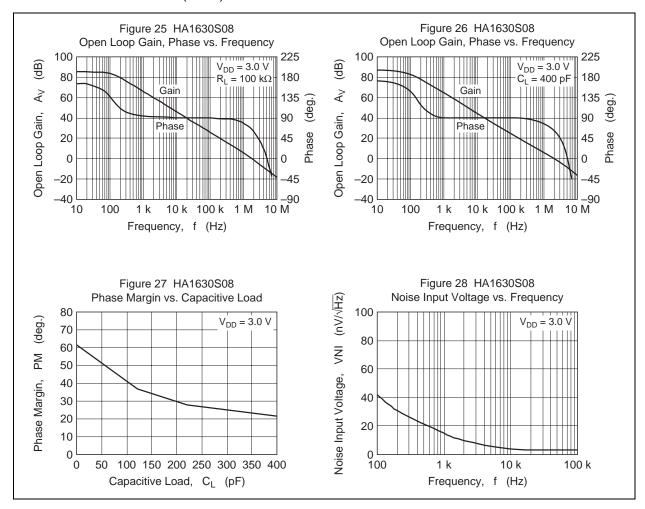

| Slew rate (falling)             | SRf                  | vs. Cload               | 21                    | 13                  |

|                                 |                      | vs. Temperature         | 22                    | 13                  |

|                                 |                      | Time waveform           | 23                    | 13                  |

| Open loop gain                  | A <sub>V</sub>       | vs. Rload               | 24                    | 14                  |

|                                 |                      | vs. Frequency           | 25, 26                | 14                  |

| Phase margin                    | PM                   | vs. Cload               | 27                    | 14                  |

| Noise input voltage             | VNI                  | vs. Frequency           | 28                    | 15                  |

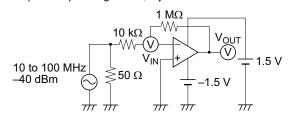

# **Test Circuits**

(Unless otherwise noted,  $V_{DD} = 3 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $Ta = 25^{\circ}\text{C}$ )

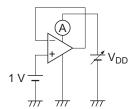

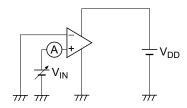

1. Supply Current, I<sub>DD</sub>

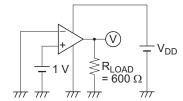

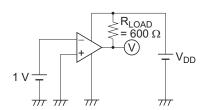

2. Output High Voltage,  $V_{OH}$  (Output High)

3. Output Low Voltage, V<sub>OL</sub> (Output Low)

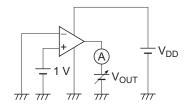

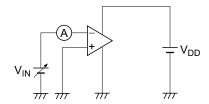

4. Output Source Current,  $I_{OSOURCE}$

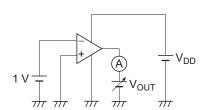

5. Output Sink Current, I<sub>OSINK</sub>

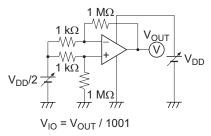

6. Input Offset Voltage vs. Operating Voltage

7. Input Offset Voltage,  $V_{IO}$

8. Common Mode Input Voltage Range, V<sub>CM</sub>

# Test Circuits (cont.)

(Unless otherwise noted,  $V_{DD} = 3 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $Ta = 25^{\circ}\text{C}$ )

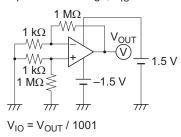

## 9. Common Mode Rejection Ratio, CMRR

| V <sub>IN</sub> | Measure<br>Point  | Calculate<br>V <sub>IO</sub>                | CMRR Calculation                                                                           |

|-----------------|-------------------|---------------------------------------------|--------------------------------------------------------------------------------------------|

| –1.5 V          | V <sub>OUT1</sub> | V <sub>IO1</sub> = V <sub>OUT1</sub> / 1001 | [V <sub>IO2</sub> – V <sub>IO1</sub> ]]                                                    |

| 0.3 V           | V <sub>OUT2</sub> | $V_{IO2} = V_{OUT2} / 1001$                 | CMRR = $\left  20 \log_{10} \frac{  V _{O2} - V_{ O1J } }{0.3 - (-1.5 \text{ V})} \right $ |

#### 10. Power Supply Rejection Ratio, PSRR

| V <sub>DD</sub> | Measure<br>Point  | Calculate<br>V <sub>IO</sub>                | CMRR Calculation                                                                                   |

|-----------------|-------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------|

| 2.7 V           | V <sub>OUT1</sub> | V <sub>IO1</sub> = V <sub>OUT1</sub> / 1001 |                                                                                                    |

| 5.5 V           | V <sub>OUT2</sub> | V <sub>IO2</sub> = V <sub>OUT2</sub> / 1001 | $PSRR = \left  20 \log_{10} \frac{  V _{102} - V _{101}  }{5.5 \text{ V} - 2.7 \text{ V}} \right $ |

#### 11. Input Bias Current, I<sub>IB+</sub>

### 12. Input Bias Current, I<sub>IB</sub>\_

#### 13. Slew Rate (Large Signal Input)

# Test Circuits (cont.)

(Unless otherwise noted,  $V_{DD} = 3 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $Ta = 25^{\circ}\text{C}$ )

# 14. Open Loop Voltage Gain, $A_V$

$$A_{V} = \left| 20log_{10} \frac{101 \times |V_{OUT}|}{|V_{IN}|} \right|$$

## 15. Noise Input Voltage, VNI

$$VNI = \frac{V_{OUT}}{1001}$$

### **Characteristic Curves**

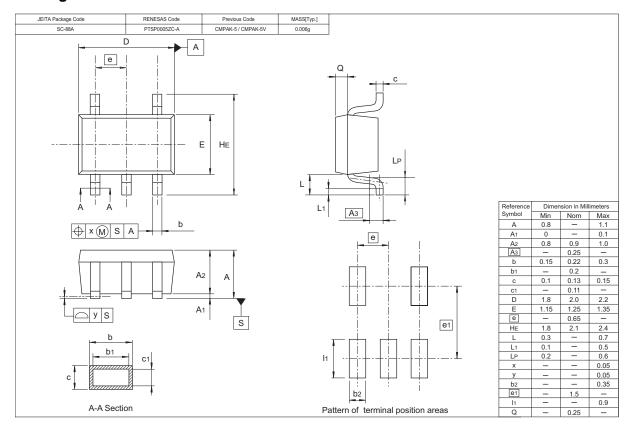

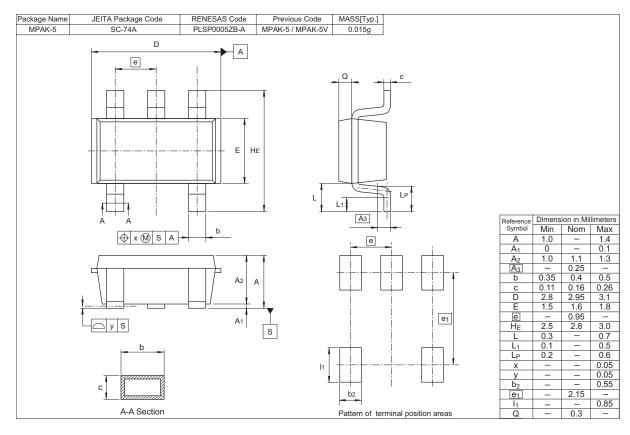

## **Package Dimensions**

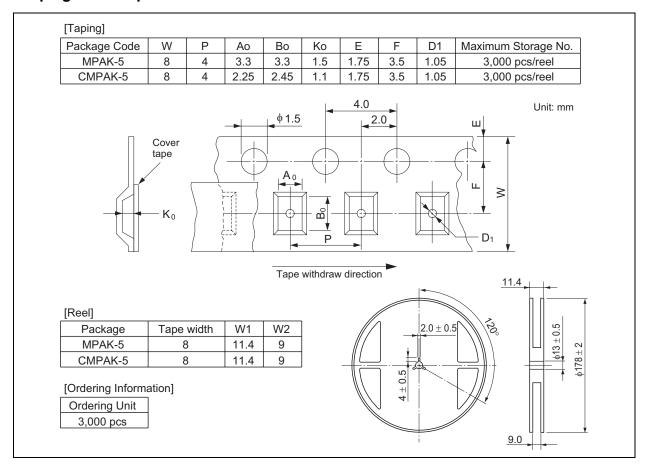

# **Taping & Reel Specification**

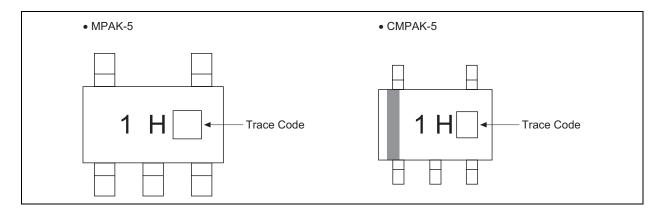

### **Mark Indication**

Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Notes:

1. This document is provided for reference purposes only so that Penesas customers may select the appropriate Renesas products for their use. Renesas neither makes in the respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of waspons of mass and included in this document such as product data, diagrams, and regulations, and procedures required by such law and regulations and procedures required by such law and regulations and procedures required by such law and regulations, and procedures required by such law and regulations and procedures required by such law and regulations and procedures required by such law and regulations and procedures required by such law and regulations, and procedures required to such as a few such as a s

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510