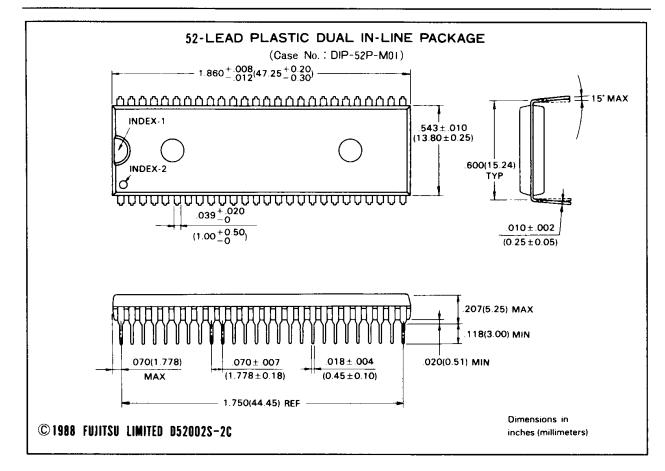

DIP-52P-M01

(MB8431)

of any voltage higher than maximum rated voltages to this high impedance circuit.

# MB8431/32-90/-90L/-90LL/-12/-12L/-12LL CMOS 16K-BIT DUAL-PORT SRAM

DATA SHEET =

## 2K x 8 Bits CMOS Dual-Port Static Random Access Memory

The Fujitsu MB8431 and MB8432 are 2,048 words x 8 bits dual-port static high performance, random access memories fabricated with CMOS technology. MB8431 and MB8432 provide the user with two separately controlled I/O ports with independent addresses, Chip Select (CS), Write Enable (WE), Output Enable (OE), and I/O functions. This arrangement permits independent access to any memory location for either a Read or Write operation - a useful feature for shared data processing applications. These devices have an automatic power-down feature controlled by CS.

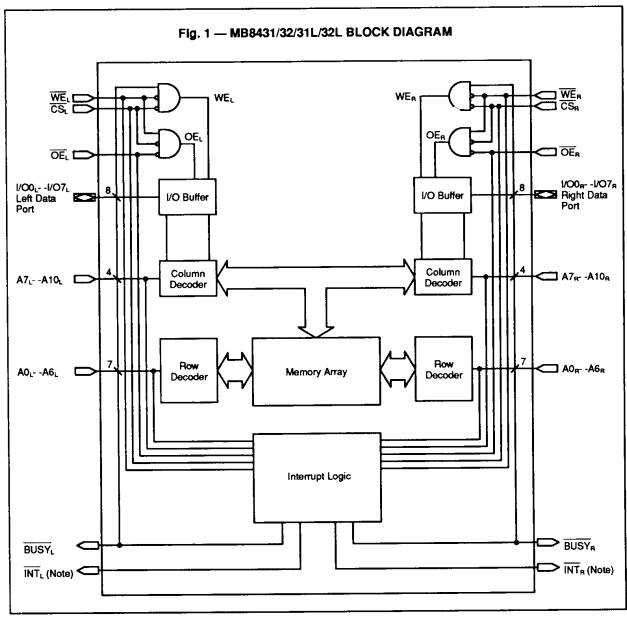

To avoid data contention on the same address, a BUSY input is provided for address arbitration; in addition, MB8431 utilizes an interrupt (INT) flag which allows communication between systems on either side of the RAM. Both devices use a single +5 V power supply and all pins are TTL-compatible. A simplified block diagram of the SRAM is shown in Figure 1.

Some typical applications for these memory devices are multiprocessing systems,

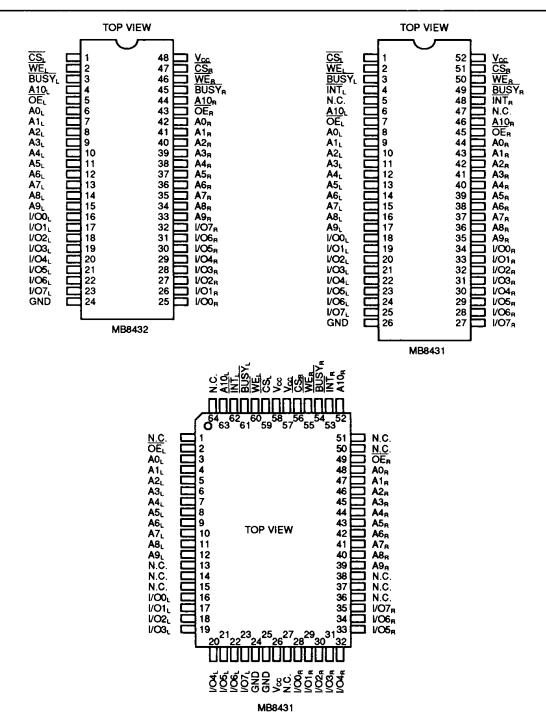

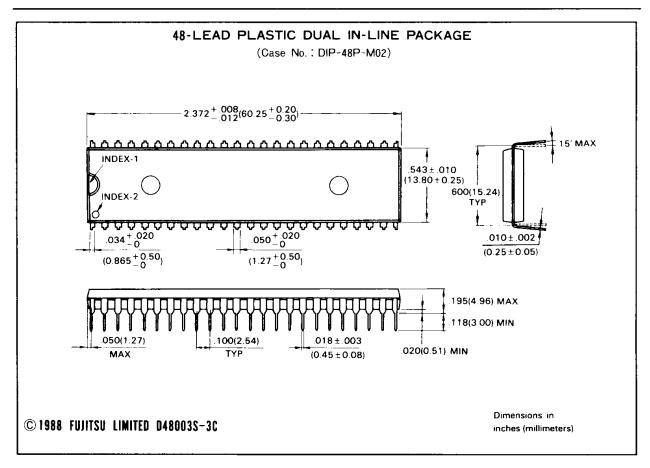

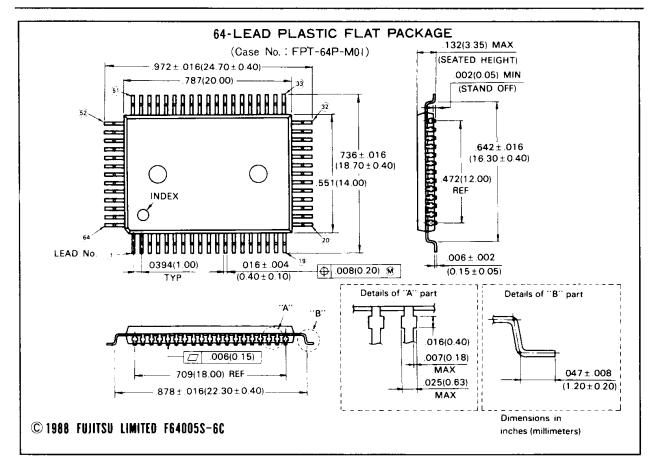

FPT--64P--M01 (MB8431) distributed networks, external register files, and peripheral controllers. 2,048 words x 8 bits Organization: WHIM WHIM WHIM Static operation: no clocks or timing strobe required t<sub>AA</sub> = t<sub>ACS</sub> = 90 ns max. (MB8431/32-90) Access time: (MB8431/32-90L/-90LL) t<sub>AA</sub> = t<sub>ACS</sub> = 120 ns max. (MB8431/32-12) (MB8431/32-12L/-12LL) DIP-48P-M02 Power consumption for the standard version: (MB8432) 660 mW max. (Both ports active) 385 mW max. (One port active) **Pin Assignment** 38.5 mW max. (Both ports standby, TTL) 11 mW max. (Both ports standby, CMOS) Power consumption for the L and LL-versions: 495 mW max. (Both ports active) 275 mW max. (One port active) 27.5 mW max. (Both ports standby, TTL) 1.1 mW max. (Both ports standby, CMOS) Single +5 V supply ±10% tolerance TTL compatible inputs and outputs See page 4-81 Three-state outputs with OR-tie capacity Electrostatic protection for all inputs and outputs Data retention voltage: 2 V min. Address arbitration function: BUSY input Interrupt function for communication between systems (MB8431 only): INT flag Expansion capability using MB8421/22 (Master) and MB8431/32 (Slave) Standard Plastic Packages: MB8432-xx(L/LL)P 48-pin DIP 52-pin DIP MB8431-xx(L/LL)P 64-pin QFP MB8431-xx(L/LL)PFQ This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application

Copyright C 1990 by FUJITSU LIMITED and Fujitau Microelectronics, Inc.

# www.DataSheet.in

## ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating                                                 | Symbol           | Value                           | Unit |

|--------------------------------------------------------|------------------|---------------------------------|------|

| Supply Voltage                                         | Vcc              | -0.5 to +7                      | v    |

| Input Voltage on any pin with respect to $V_{ss}$      | ViN              | -0.5 to<br>V <sub>cc</sub> +0.5 | v    |

| Output Voltage on any I/O pin with respect to $V_{ss}$ | Vour             | -0.5 to<br>V <sub>CC</sub> +0.5 | v    |

| Output Current                                         | Ιουτ             | ±20                             | mA   |

| Power dissipation                                      | Po               | 1.0                             | w    |

| Temperature Under Bias                                 | TBIAS            | -10 to +85                      | ℃    |

| Storage Temperature                                    | Т <sub>ята</sub> | -40 to +125                     | °C   |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PIN NAMES

| LEFT PORT                              | RIGHT PORT                             | NAMES                      |  |

|----------------------------------------|----------------------------------------|----------------------------|--|

| CS                                     | CS <sub>R</sub>                        | Chip<br>Select Input       |  |

| WEL                                    | WE <sub>R</sub>                        | Write<br>Enable Input      |  |

| OEL                                    | ŌĒŖ                                    | Output<br>Enable Input     |  |

| INT                                    |                                        | Interrupt *<br>Flag Output |  |

| BUSY                                   | BUSYR                                  | Busy<br>Flag Input         |  |

| AOL to A10L                            | A0 <sub>R</sub> to A10 <sub>R</sub>    | Address<br>Input           |  |

| 1/00 <sub>L</sub> to 1/07 <sub>L</sub> | 1/00 <sub>R</sub> to 1/07 <sub>R</sub> | Data<br>Input/Output       |  |

| l l                                    | V <sub>cc</sub>                        |                            |  |

| G                                      | GND                                    |                            |  |

\*: Applies to MB8431 only.

Note: MB8431 only.

# CAPACITANCE (T<sub>A</sub> = 25° C, f = 1MHz)

| Parameter                  | Symbol          | Тур | Max | Unit |

|----------------------------|-----------------|-----|-----|------|

| Input Capacitance (VIN=0V) | CIN             |     | 10  | pF   |

| I/O Capacitance (VI/O=0V)  | C <sub>vo</sub> |     | 10  | рF   |

# **RECOMMENDED OPERATING CONDITIONS**

(Referenced to VSS)

| Parameter             | Symbol          | Min | Тур | Max | Unit |

|-----------------------|-----------------|-----|-----|-----|------|

| Supply Voltage        | V <sub>cc</sub> | 4.5 | 5.0 | 5.5 | v    |

| Operating Temperature | TA              | 0   |     | 70  | Ŷ    |

# **DC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

| Parameter                                                                         | Symbol             | Symbol Condition                                                                                                     |        | 1/<br>2 <del>-90</del> /12 | MB8431/<br>MB8432-90L/ | Unit                 |    |

|-----------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------|--------|----------------------------|------------------------|----------------------|----|

|                                                                                   |                    |                                                                                                                      | Min    | Max                        | Min                    | Max                  |    |

| Operating<br>Supply Current<br>(Both ports Active)                                | lcc                | Cycle=Min.<br>Duty=100%<br>I <sub>out</sub> ≃0mA                                                                     |        | 120                        |                        | 90                   | mA |

|                                                                                   | I <sub>SB1</sub>   | Both ports≑Standby<br>CS <sub>L</sub> & CS <sub>R</sub> =V <sub>IH</sub>                                             |        | 7                          |                        | 5                    | mA |

| Standby                                                                           | 1982               | <u>One port=Standby</u><br>CS <sub>L</sub> or CS <sub>R</sub> =V <sub>IH</sub> ,<br>I <sub>OUT</sub> =OmA            |        | 70                         |                        | 50                   | mA |

| Supply Current                                                                    | I <sub>583</sub>   | <u>Bot</u> h ports=Full standby<br>CS <sub>L</sub> & CS <sub>R</sub> ≥V <sub>cc</sub> =0.2V                          |        | 2                          |                        | 0.2                  | mA |

| I <sub>SB4</sub><br>One port=F<br>CSL or CS <sub>R</sub><br>I <sub>out</sub> =0mA |                    | <u>One port</u> =Full standby<br>CS <sub>L</sub> or CS <sub>R</sub> ≥V <sub>cc</sub> =0.2V,<br>I <sub>ouT</sub> =0mA |        | 70                         |                        | 50                   | mA |

| Input Leakage Current                                                             | lu l               | $V_{IN}=0V$ to $V_{CC}$                                                                                              | -10    | 10                         | -10                    | 10                   | μA |

| Output Leakage Current                                                            | ۱ <sub>LO</sub>    | $\overline{\text{CS}}$ =V <sub>IH</sub> , I/O=0V to V <sub>CC</sub>                                                  | -10    | 10                         | -10                    | 10                   | μA |

| Input High Voltage                                                                | ViH                |                                                                                                                      | 2.2    | V <sub>cc</sub> +0.3       | 2.2                    | V <sub>cc</sub> +0.3 | v  |

| Input Low Voltage                                                                 | VıL                |                                                                                                                      | 0.3 *1 | 0.8                        | -0.3 *1                | 0.8                  | v  |

| Output High Voltage                                                               | V <sub>он</sub> *2 | lour=-1.0mA                                                                                                          | 2.4    |                            | 2.4                    |                      | v  |

| Output Low Voltage                                                                | Var                | I <sub>out</sub> =3.2mA                                                                                              |        | 0.4                        |                        | 0.4                  | v  |

| Output Low Voltage for<br>Open–Drain                                              | VoL                | I <sub>out</sub> =8mA                                                                                                |        | 0.4                        |                        | 0.4                  | v  |

\*1 Undershoot -3.0V min at less than 20ns pulse width.

\*2 The INT pins require pull-up resistors because they are open-drain outputs.

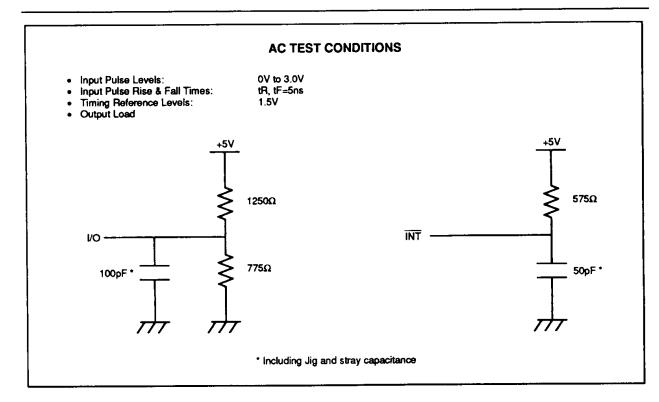

# **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted)

READ CYCLE

| Parameter                         | Symbol | MB8431-90/901/90LL<br>MB8432-90/901/90LL |     |     |     | Unit |

|-----------------------------------|--------|------------------------------------------|-----|-----|-----|------|

|                                   |        | Min                                      | Max | Min | Mex |      |

| Read Cycle Time                   | tac    | 90                                       | 1   | 120 |     | ns   |

| Address Access Time               | tu     |                                          | 90  |     | 120 | ns   |

| Chip Select Access Time           | tucs   |                                          | 90  |     | 120 | ns   |

| Output Enable Access Time         | thoe   |                                          | 40  |     | 50  | ns   |

| Output Hold from Address Change   | tон    | 10                                       |     | 10  |     | ns   |

| Chip Select to Output Low-Z *2    | lc.z   | 5                                        |     | 5   |     | ns   |

| Output Enable to Output Low-Z *2  | touz   | 5                                        |     | 5   |     | ns   |

| Chip Select to Output High-Z *2   | tснz   |                                          | 40  |     | 50  | ns   |

| Output Enable to Output High-Z *2 | tонz   |                                          | 40  |     | 50  | ns   |

| Power up from Chip Select         | teυ    | 0                                        |     | 0   |     | ns   |

| Power down from Chip Select       | teo    |                                          | 50  |     | 60  | ns   |

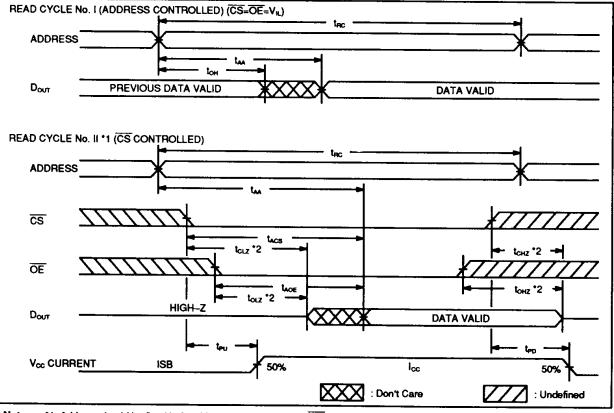

# READ CYCLE TIMING DIAGRAMS (WE=VIH)

Note: 1 Address should be fixed before high-to-low transition of CS.

\*2 This parameter is specified at the point of ±500mV from steady state voltage with output capacitance 5pF.

#### WRITE CYCLE

| Parameter                        | Symbol          | MB8431-90/90L/90LL<br>MB8432-90/90L/90LL |     | MB8431-12/12L/12LL<br>MB8432-12/12L/12LL |     | Unit |  |

|----------------------------------|-----------------|------------------------------------------|-----|------------------------------------------|-----|------|--|

|                                  |                 | Min                                      | Max | Min                                      | Max |      |  |

| Write Cycle Time                 | łwc             | 90                                       |     | 120                                      |     | ns   |  |

| Address Valid to End of Write    | taw             | 85                                       |     | 100                                      |     | ns   |  |

| Chip Select to End of Write      | tow             | 85                                       |     | 100                                      |     | ns   |  |

| Address Setup Time               | tas             | 0                                        |     | 0                                        |     | ns   |  |

| Write Pulse Width                | ₿w₽             | 60                                       |     | 70                                       |     | ns   |  |

| Write Recovery Time              | twn.            | 0                                        |     | 0                                        |     | ns   |  |

| Data Valid to End of Write       | tow             | 40                                       |     | 40                                       |     | ns   |  |

| Data Hold Time                   | t <sub>DH</sub> | 0                                        |     | 0                                        |     | ns   |  |

| Write Enable to Output Low-Z *4  | tow             | 0                                        |     | 0                                        |     | ns   |  |

| Write Enable to Output High-Z *4 | twz             |                                          | 40  |                                          | 50  | ns   |  |

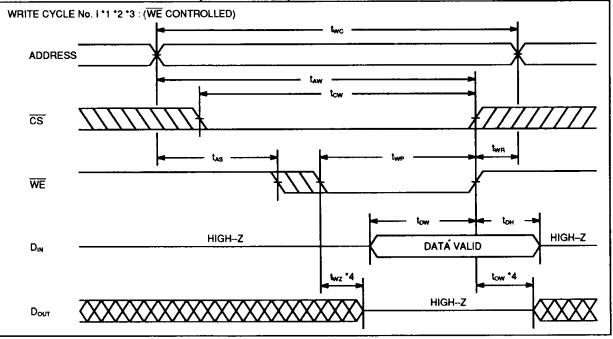

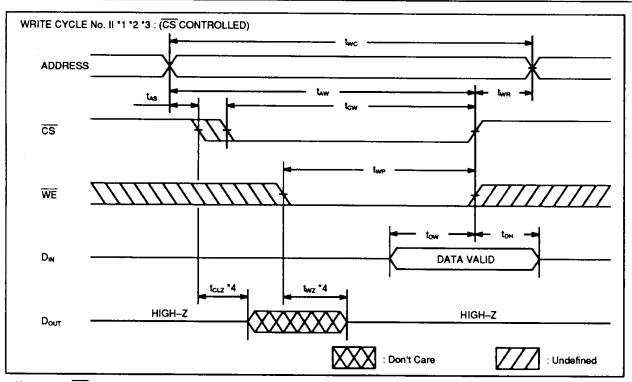

### WRITE CYCLE TIMING DIAGRAMS (DE=Don't care)

\*1 WE must be high during address transition. Note:

\*2 If OE, CS are in the READ Mode, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

\*3 If CS goes high prior to or coincident with WE transition to high, the output remains in high impedance state.

- \*4 Transition is measured at the point of  $\pm$ 500mV from steady state voltage with C<sub>L</sub>=5pF.

- Note:

- 1 WE must be high during address transition.

1 If OE, CS are in the READ Mode, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

\*3 If CS goes high prior to or coincident with WE transition to high, the output remains in high impedance state.

\*4 This parameter is specified at the point of ±500mV from steady state voltage with output capacitance 5pF.

#### **SLAVE BUSY TIMING**

| Parameter                 |     |     | MB8431-00/90L/90LL MB8431-12/12L/12LL<br>MB8432-00/90L/90LL MB8432-12/12L/12LL |     |     |    |

|---------------------------|-----|-----|--------------------------------------------------------------------------------|-----|-----|----|

|                           |     | Min | Max                                                                            | Min | Max |    |

| Busy Access Time          | teo |     | 0                                                                              | -   | 0   | ns |

| Write Set Up Time To Busy | tws | -10 |                                                                                | -10 |     | ns |

| Write Hold Time From Busy | twн | 20  |                                                                                | 25  |     | ns |

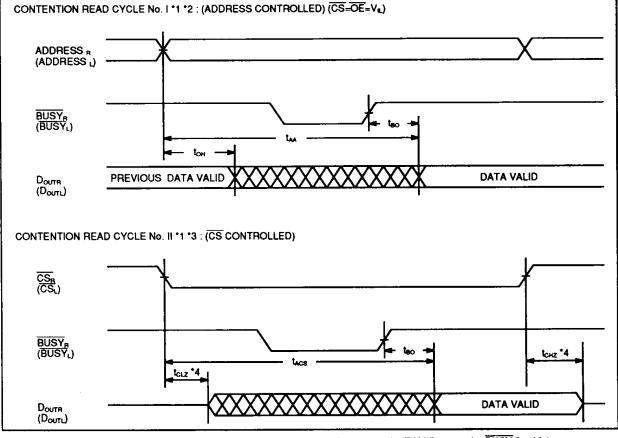

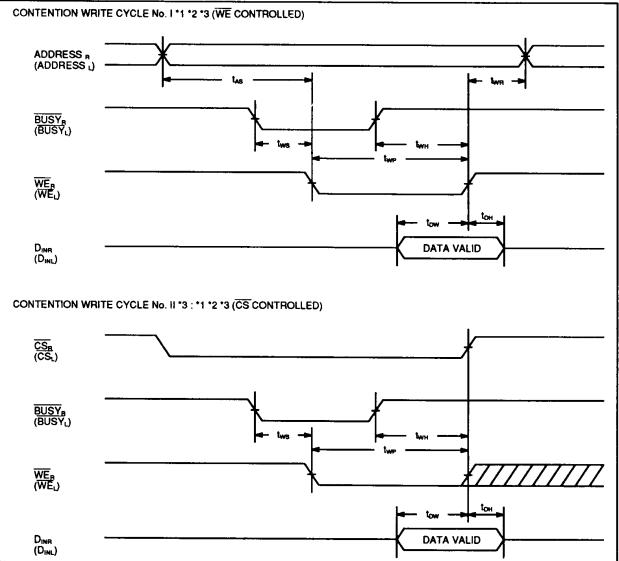

### CONTENTION CYCLE TIMING DIAGRAMS (WE=VIH)

Note:

\*1 In case of dualaccess at the same memory location, the port that access the RAM first sets the BUSY flag high.

\*2 CS must be low before or coincident with transition of address.

\*3 Address is valid prior to cincident with high-to-low transition of CS.

\*4 This parameter is specified at the point of ±500mV from steady state voltage with output capacitance 5pF.

Note:

\*1 WE must be high during address transition. \*2 I/O pins are in the output state, so the input signals of opposite phase must not be applied.

\*3 During BUSY input is low, write operation can not be excuted even if WE is low.

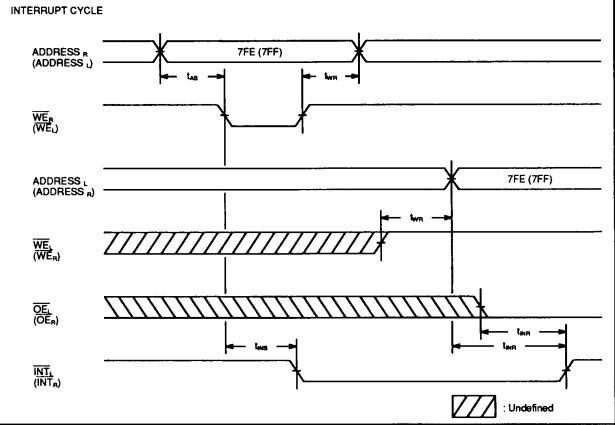

#### **INTERRUPT TIMING \*1**

| Parameter      |        | MB8431-90/90L/90LL<br>MB8432-90/90L/90LL |     |     |     |     |

|----------------|--------|------------------------------------------|-----|-----|-----|-----|

|                |        | Min                                      | Max | Min | Max |     |

| INT Set Time   | LINS   |                                          | 80  |     | 100 | n\$ |

| INT Reset Time | Lina . |                                          | 80  |     | 100 | ns  |

### INTERRUPT CYCLE TIMING DIAGRAMS \*1

Note: \*1 Applies to MB8431 only.

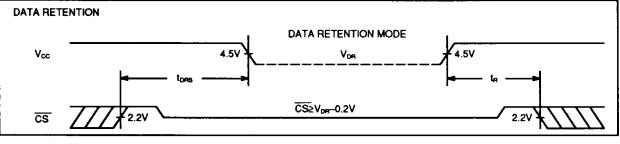

# **DATA RETENTION CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

| Parameter Data Retention Supply Voltage |               | Symbol | Min | Тур | Max | Unit |

|-----------------------------------------|---------------|--------|-----|-----|-----|------|

|                                         |               | VDR    | 2.0 |     | 5.5 | v    |

|                                         | Standard      |        |     |     | 0.2 | mA   |

| Data Retention Supply Current *1        | L-Version     | IDA    |     |     | 20  | μΑ   |

|                                         | LL-Version *2 |        |     |     | 2   | μА   |

| Data Retention Setup Time               |               | lons   | 0   |     |     | ns   |

| Operation Recovery Time                 |               | ta.    | tac |     |     | ns   |

Note: \*1

$$V_{CC}=V_{OR}=3V$$

,  $\overline{CS}_L \triangleq \overline{CS}_R \ge V_{CC}=0.2V$

\*2  $V_{OR}=3V$ ,  $T_A=0^{\circ}C$  to  $40^{\circ}C$

#### DATA RETENTION TIMING

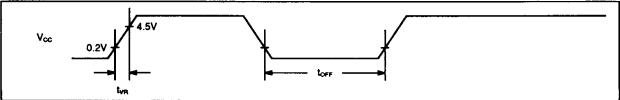

# **POWER ON/RESET CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

| Parameter         | Symbol          | MB8431-00/90L/90LL<br>MB8432-00/90L/90LL |     |      |     |    |

|-------------------|-----------------|------------------------------------------|-----|------|-----|----|

|                   |                 | Min                                      | Max | Min  | Max |    |

| Power Up Time *1  | t <sub>va</sub> | 0.05                                     | 50  | 0.05 | 50  | ms |

| Power Off Time *2 | <b>t</b> OFF    | 1                                        |     | 1    |     | S  |

\*1 This is required to keep normal operation for power on/reset circuit which initialize INT output to "H" automatically when V<sub>cc</sub> is applied.

\*2 This is required to keep normal operation for power on/reset circuit which V<sub>cc</sub> is repeatly turn on/off.

#### **POWER ON/RESET TIMING**

#### Function Description:

1. ORGANIZATION:

MB8431/32 are 2K words x 8 bit Dual port Static Random Access Memory. Each port has independent addresses, chip select (CS), write enable (WE), output enable (OE) and data input/output (I/O) functions.

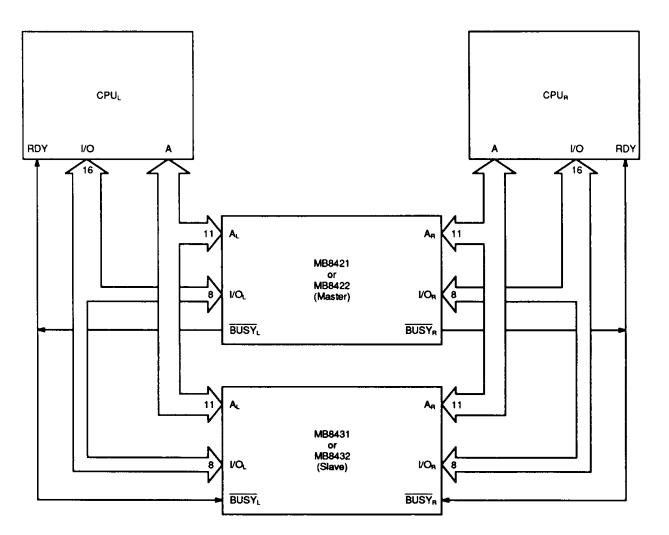

#### 2. SLAVE BUSY FUNCTION:

In order to do bit expansion using 8 bit width dual port RAM such as MB8421/22, two or more parts should be connected paralel. But such case, there is a possibility, which depends on arbitration timing, of outputting BUSY signal to different ports and put both CPUs in waiting state. This causes a trouble. Using MB8431/32 which have slave busy function (busy input) is one of the solutaion for such trouble. Bit expansion is easily achievable to pair-use slave type dual port RAM such as MB8431/32 and master type dual port RAM such as MB8421/22.

#### (Example)

#### As an example, Fig1 shows 16 bit dual port memory system.

In this system, master type Dual port RAM (MB8421/22) judge arbitration for address contention and output result of the judgement from BUSY pin. This output returned to CPU and make the CPU in waiting state and also the output is applied to slave type dual port RAM (MB8431/32). Though slave type dual port RAM (MB8431/32) do not judge for arbitration, they have BUSY input pin and inhibit write operation of the correspondent port during "L" signal form BUSY output of master type dual port RAM (MB8421/22) is applied to the BUSY input. A system consists of one master dual port RAM (MB8421/22) and three slave dual port RAMs (MB8431/32) is harmonized for 32 bit application.

#### 3. INTERRUPT FUNCTION:

The interrupt function  $(\overline{INT})$  is provided to allow communication between the systems on either sides of the dual-port RAM.  $\overline{INT}_{L}$  is set to low, when the processor on the right port writes to address 7FE (A0=L and A1 to A10=H).  $\overline{INT}_{L}$  is then reset to High, when the left port acknowledges by reading the same address 7FE. Thus the address 7FE is like a 8 bit word mail-box transferring information from the right-port to the left-port.

$\overline{INT}_R$  on the other hand is set to low, when processor on the left port writes to the address 7FF (A=0 to A10=H).  $\overline{INT}_R$  is reset to High, when the right port acknowledges by reading this address. Hence, the address 7FF is a second 8 bit word mail—box transferring information form the left port to the right port.

The INT<sub>L</sub> and INT<sub>R</sub> are set to High on power-up. If the port is in the standby mode, it can still get interrupted by the processor on the other side.

In case he BUSY flag is set to low, then the pertinent port can not set or reset the INT flag.