# MOS 65536-BIT DYNAMIC RANDOM ACCESS MEMORY

MB 8264A-10 MB 8264A-12 MB 8264A-15

### 65,536-BIT DYNAMIC RANDOM ACCESS MEMORY

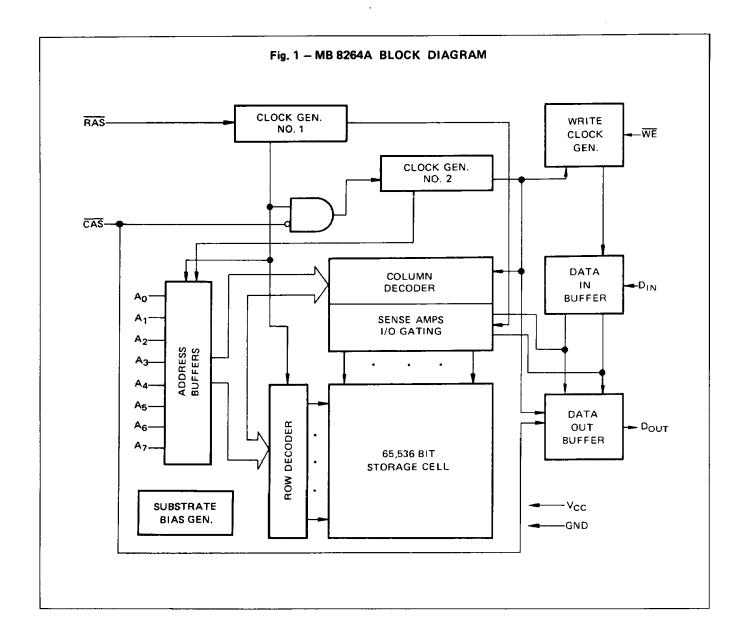

The Fujitsu MB 8264A is a fully decoded, dynamic random access memory organized as 65,536 one-bit words. The design is optimized for high-speed, high performance applications such as mainframe memory, buffer memory, peripheral storage and environments where low power dissipation and compact layout is required.

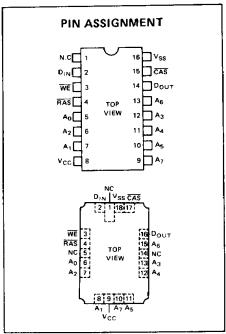

Multiplexed row and column address inputs permit the MB 8264A to be housed in a standard 16 pin DIP and 18 pad LCC. Pin-outs conform to the JEDEC approved pin out.

The MB 8264A is fabricated using silicon gate NMOS and Fujitsu's advanced Double-Layer Polysilicon process. This process, coupled with single-transistor memory storage cells, permits maximum circuit density and minimal chip size. Dynamic circuitry is employed in the design, including the sense amplifiers.

Clock timing requirements are non-critical, and power supply tolerance is very wide. All inputs and output are TTL compatible.

- 65,536 x 1 RAM, 16 pin DIP/18 pad LCC

- Silicon-gate, Double Poly NMOS, single transistor cell

- Row access time, 100 ns max (MB 8264A-10) 120 ns max (MB 8264A-12) 150 ns max (MB 8264A-15)

- Cycle time, 190 ns min (MB 8264A-10)

230 ns min (MB 8264A-12)

260 ns min (MB 8264A-15)

- Single +5V Supply, ±10% tolerance

- Low power (active)

275 mW max (MB 8264A-10)

248 mW max (MB 8264A-12)

220 mW max (MB 8264A-15)

22 mW Standby (max)

• 2ms/128 refresh cycles

- RAS-only and Hidden refresh capability

- Read-Modify-Write and Page-Mode capability

- Common I/O capability using Early Write operation

- Output unlatched at cycle end allows extended page boundary and two-dimensional chip select

- On-chip latches for Addresses and Data-in

- t<sub>AR</sub>, t<sub>WCR</sub>, t<sub>DHR</sub> are eliminated

- Standard 16-pin Ceramic (Cerdip) DIP: Surfix-Z

Standard 16-pin Plastic

DIP: Surfix-P

Standard 18-pad Ceramic

LCC: Surfix-TV

### ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating  Voltage on any pin relative to V <sub>SS</sub> |         | Symbol         | Value       | Unit |  |

|--------------------------------------------------------|---------|----------------|-------------|------|--|

|                                                        |         | VIN. VOUT      | -1 to +7    |      |  |

| Voltage on V <sub>CC</sub> supply                      |         | Vcc            | -1 to +7    | V    |  |

| Storage temperature                                    | Ceramic | <del>-</del> - | -55 to +150 | °c   |  |

|                                                        | Pastic  | TSTG           | -55 to +125 | 1    |  |

| Power dissipation                                      |         | PD             | 1.0         | w    |  |

| Short circuit output current                           |         |                | 50          | mA   |  |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

## CAPACITANCE (T<sub>A</sub> = 25°C)

| Parameter                                                          | Symbol           | Тур | Max | Unit |

|--------------------------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance A <sub>0</sub> ∼A <sub>7</sub> , D <sub>IN</sub> | C <sub>IN1</sub> |     | 5   | pF   |

| Input Capacitance RAS, CAS, WE                                     | C <sub>IN2</sub> |     | 8   | pF   |

| Output Capacitance D <sub>OUT</sub>                                | C <sub>OUT</sub> |     | 7   | pF   |

## RECOMMENDED OPERATING CONDITIONS

(Referenced to VSS)

| Parameter                      | Symbol                             | Min      | Тур      | Max      | Unit | Operating<br>Temperature |

|--------------------------------|------------------------------------|----------|----------|----------|------|--------------------------|

| Supply Voltage                 | V <sub>cc</sub><br>V <sub>ss</sub> | 4.5<br>0 | 5.0<br>0 | 5.5<br>0 | V    |                          |

| Input High Voltage, all inputs | V <sub>IH</sub>                    | 2.4      |          | 6.5      | V    | 0°C to +70°C             |

| Input Low Voltage, all inputs  | V1L*                               | -1.0     |          | 0.8      | V    |                          |

Note \*: The device can withstand undershoots to the -2V level with a pulse width of 20 ns.

## DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter                                                                                                                                 | 1              | Symbol                             | Min | Max | Unit    |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------|-----|-----|---------|

| OPERATING CURRENT *                                                                                                                       | MB 8264A-10    |                                    |     | 50  |         |

| Average power supply current                                                                                                              | MB 8264A-12    | l <sub>CC1</sub>                   |     | 45  | mA      |

| (RAS, CAS cycling; t <sub>RC</sub> = min)                                                                                                 | MB 8264A-15    |                                    |     | 40  |         |

| STANDBY CURRENT Standby Power supply current $\{\overline{RAS} = \overline{CAS} = V_1\}$                                                  | <sub>H</sub> ) | I <sub>CC2</sub>                   |     | 4   | mA      |

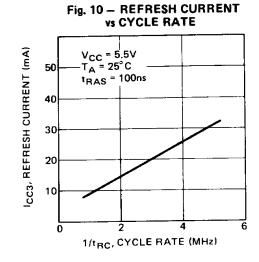

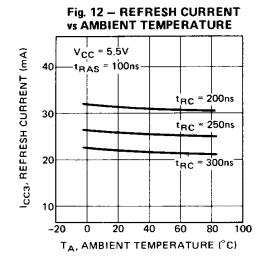

| REFRESH CURRENT *                                                                                                                         | MB 8264A-10    |                                    |     | 38  |         |

| Average power supply current                                                                                                              | MB 8264A-12    | lccs                               |     | 35  | mA      |

| $(\overline{CAS} = V_{1H}, \overline{RAS} \text{ cycling}; t_{RC} = \min)$                                                                | MB 8264A-15    |                                    |     | 31  |         |

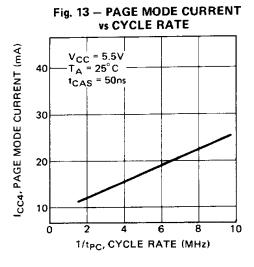

| PAGE MODE CURRENT*                                                                                                                        | MB 8264A-10    |                                    |     | 35  |         |

| Average power supply current                                                                                                              | MB 8264A-12    | I <sub>CC4</sub>                   |     | 32  | mA      |

| $(\overline{RAS} = V_{1L}, \overline{CAS} \text{ cycling; } t_{PC} = \min)$                                                               | MB 8264A-15    | ······                             |     | 28  | <u></u> |

| INPUT LEAKAGE CURRENT Input leakage current, any input $(0V \le V_{1N} \le 5.5V, V_{CC} = 5.5V, V_{SS} = 0V, all other pins not test=0V)$ |                | l <sub>i(L)</sub>                  | -10 | 10  | μΑ      |

| OUTPUT LEAKAGE CURRENT<br>(Data out is disabled, OV≦V <sub>OUT</sub> ≤5.5)                                                                |                | l <sub>O(L)</sub>                  | -10 | 10  | μΑ      |

| OUTPUT LEVELS  Output high voltage (I <sub>O H</sub> = -5mA)  Output low voltage (I <sub>O L</sub> = 4.2mA)                               |                | V <sub>OH</sub><br>V <sub>OL</sub> | 2.4 | 0.4 | V<br>V  |

Note \*: I<sub>CC</sub> is dependent on output loading and cycle rates. Specified values are obtained with the output open.

AC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

NOTES 1.2.3

| Parameter NOTES                                   | Symbol            | M8 8264A-10 |       | MB 8264A-12 |       | MB 8264A-15 |       |     |

|---------------------------------------------------|-------------------|-------------|-------|-------------|-------|-------------|-------|-----|

| Parameter NOTES                                   | Symbol            | Min         | Max   | Min         | Max   | Min         | Max   | Uni |

| Time between Refresh                              | t <sub>REF</sub>  |             | 2     |             | 2     |             | 2     | ms  |

| Random Read/Write Cycle Time                      | t <sub>RC</sub>   | 190         |       | 230         |       | 260         |       | ns  |

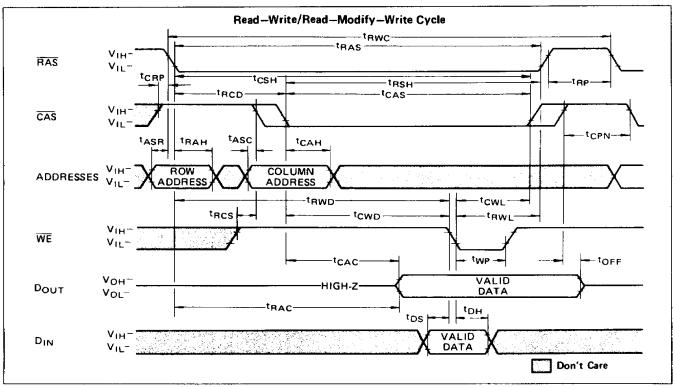

| Read-Write Cycle Time                             | t <sub>RWC</sub>  | 230         |       | 265         |       | 280         |       | ns  |

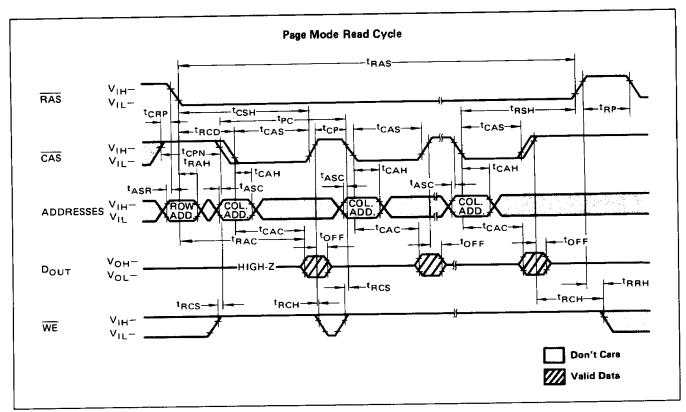

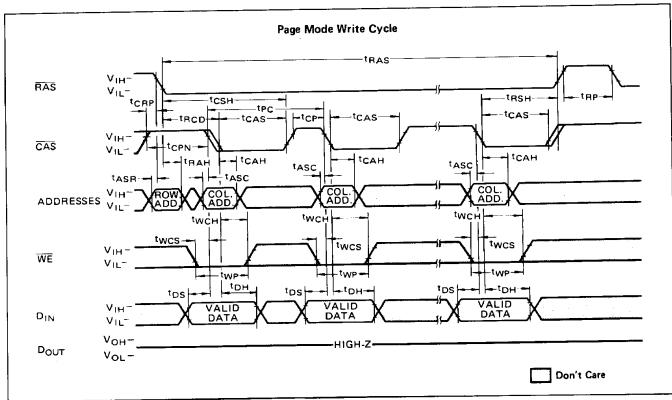

| Page Mode Cycle Time                              | t <sub>PC</sub>   | 105         |       | 120         |       | 145         |       | ns  |

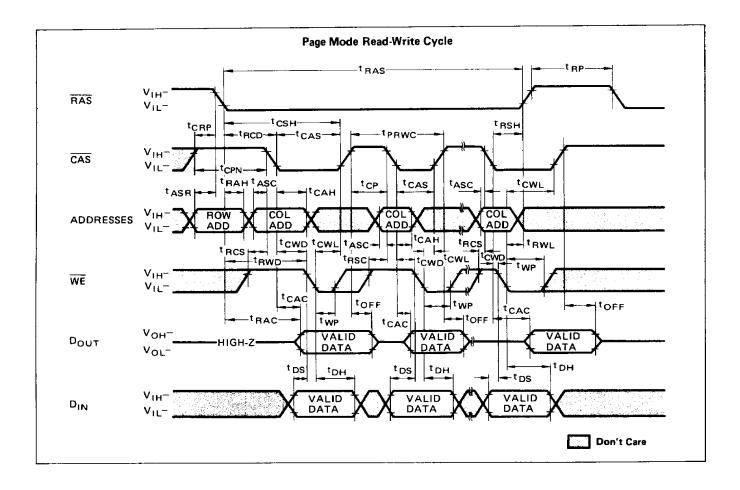

| Page Mode Read-Write Cycle Time                   | t <sub>PRWC</sub> | 135         |       | 155         |       | 180         |       | ns  |

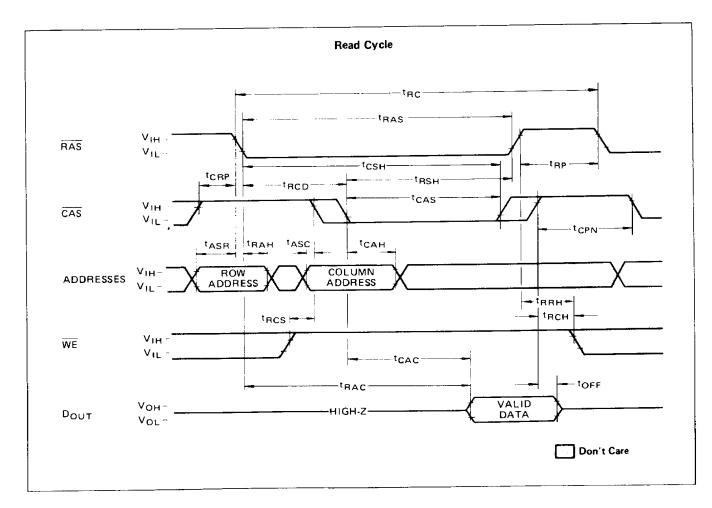

| Access Time from RAS                              | tRAC              |             | 100   |             | 120   |             | 150   | ns  |

| Access Time from CAS 5 6                          | t <sub>CAC</sub>  |             | 50    |             | 60    |             | 75    | ns  |

| Output Buffer Turn Off Delay                      | toff              | 0           | 30    | 0           | 35    | 0           | 40    | ns  |

| Transition Time                                   | t <sub>T</sub>    | 3           | 50    | 3           | 50    | 3           | 50    | ns  |

| RAS Precharge Tim                                 | t <sub>RP</sub>   | 80          |       | 100         |       | 100         |       | ns  |

| RAS Pulse Width                                   | t <sub>RAS</sub>  | 100         | 10000 | 120         | 10000 | 150         | 10000 | ns  |

| RAS Hold Time                                     | t <sub>RSH</sub>  | 50          |       | 60          |       | 75          |       | ns  |

| CAS Precharge Time (Page mode only)               | t <sub>CP</sub>   | 45          |       | 50          |       | 60          |       | ns  |

| CAS Precharge Time (All cycles except page mode)  | t <sub>CPN</sub>  | 20          |       | 20          |       | 25          |       | ns  |

| CAS Pulse Width                                   | t <sub>CAS</sub>  | 50          | 10000 | 60          | 10000 | 75          | 10000 | ns  |

| CAS Hold Time                                     | t <sub>CSH</sub>  | 100         |       | 120         |       | 150         |       | ns  |

| RAS to CAS Delay Tim                              | t <sub>RCD</sub>  | 20          | 50    | 20          | 60    | 25          | 75    | ns  |

| CAS to RAS Precharge Time                         | t <sub>CRP</sub>  | 0           |       | 0           |       | 0           |       | ns  |

| Row Address Set Up Time                           | t <sub>ASR</sub>  | 0           |       | 0           |       | 0           |       | ns  |

| Row Address Hold Time                             | t <sub>RAH</sub>  | 10          |       | 10          |       | 15          |       | ns  |

| Column Address Set Up Time                        | t <sub>ASC</sub>  | 0           |       | 0           |       | 0           |       | ns  |

| Column Address Hold Time                          | t <sub>CAH</sub>  | 15          |       | 15          |       | 20          |       | ns  |

| Read Command Set Up Time                          | t <sub>RCS</sub>  | 0           |       | 0           |       | 0           |       | ns  |

| Read Command Hold Time Referenced to CAS 10       | t <sub>RCH</sub>  | 0           |       | 0           |       | 0           |       | ns  |

| Read Command Hold Time Referenced to RAS          | t <sub>RRH</sub>  | 20          |       | 20          |       | 20          |       | ns  |

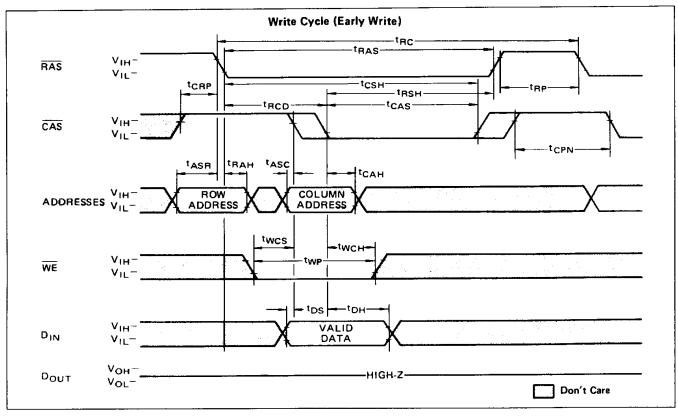

| Write Command Set Up Time                         | t <sub>wcs</sub>  | 0           |       | 0           |       | 0           |       | ns  |

| Write Command Hold Time                           | twch              | 20          |       | 25          |       | 30          |       | ns  |

| Write Command Pulse Width                         | t <sub>WP</sub>   | 20          |       | 25          |       | 30          |       | ns  |

| Write Command to RAS Lead Time                    | t <sub>RWL</sub>  | 35          |       | 40          |       | 45          |       | ns  |

| Write Command to CAS Lead Time                    | t <sub>CWL</sub>  | 35          |       | 40          |       | 45          |       | ns  |

| Data In Set Up Time                               | t <sub>DS</sub>   | 0           |       | 0           |       | 0           |       | ns  |

| Data In Hold Time                                 | t□H               | 20          |       | 25          |       | 30          |       | ns  |

| CAS to WE Delay                                   | t <sub>CWD</sub>  | 40          |       | 50          |       | 60          |       | ns  |

| RAS to WE Delay                                   | t <sub>RWD</sub>  | 90          |       | 110         |       | 120         |       | ns  |

| RAS Precharge to CAS Hold Time (RAS-only refresh) | t <sub>RPC</sub>  | 20          |       | 20          |       | 20          |       | ns  |

#### Notes:

- An initial pause of 200 μs is required after power-up followed by any 8 RAS cycles before proper device operation is achieved.

- 2 AC characteristics assume  $t_T = 5$ ns.

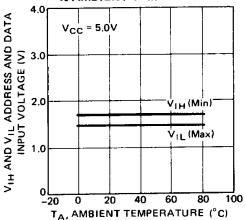

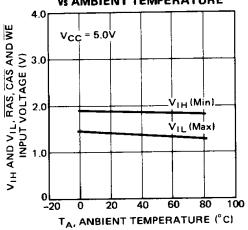

- V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IH</sub> (min) and V<sub>IL</sub> (max).

- Assumes that  $t_{RCD} \le t_{RCD}$  (max). If  $t_{RCD}$  is greater than the maximum recommended value shown in this table,  $t_{RAC}$  will increase by the amount that  $t_{RCD}$  exceeds the value shown.

- 5 Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- Measured with a load equivalent to 2 TTL loads and 100 pF.

- Operation within the  $t_{RCD}$  (max) limit insures that  $t_{RAC}$  (max) can be met.  $t_{RCD}$  (max) is specified as a

- reference point only; if  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (max) limit, then access time is controlled exclusively by  $t_{CAC}$ .

- $8 t_{RCD}$  (min) =  $t_{RAH}$  (min) +  $2t_T$  ( $t_T$ =5ns) +  $t_{ASC}$  (min)

- $t_{WCS}$ ,  $t_{CWD}$  and  $t_{RWD}$  are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If  $t_{WCS} \ge t_{WCS}$  (min) the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout entire cycle.

If  $t_{CWD} \ge t_{CWD}$  (min) and  $t_{RWD} \ge t_{RWD}$  (min), the cycle is a read-write cycle and data out will contain data read from the selected cell. If neither of the above sets of conditions is satisfied the condition of the data out is indeterminate.

Either t<sub>RRH</sub> or t<sub>RCH</sub> must be satisfied for a read cycle.

## **DESCRIPTION**

#### Address Inputs:

A total of sixteen binary input address bits are required to decode any 1 of 65536 storage cell locations within the MB 8264A. Eight row-address bits are established on the input pins (A<sub>0</sub> through A<sub>7</sub>) and latched with the Row Address Strobe (RAS). The eight column-address bits are established on the input pins and latched with the Column Address Strobe (CAS). All input addresses must be stable on or before the falling edge of RAS. CAS is internally inhibited (or "gated") by RAS to permite triggering of CAS as soon as the Row Address Hold Time

(t<sub>RAH</sub>) specification has been satisfied and the address inputs have been changed from row-addresses to columnaddresses.

#### Write Enable:

The read mode or write mode is selected with the WE input. A high on WE selects read mode and low selects write mode. Data input is disabled when read mode is selected.

### Data Input:

Data is written into the MB 8264A during a write or read-write cycle. The later falling edge of  $\overline{\text{WE}}$  or  $\overline{\text{CAS}}$  is a strobe for

the Data In (D<sub>IN</sub>) register. In a write cycle, if WE is brought low (write mode) before CAS, D<sub>IN</sub> is strobed by CAS, and the set-up and hold times are referenced to CAS. In a read-write cycle, WE can be low after CAS has been low and CAS to WE Delay Time (t<sub>CWD</sub>) has been satisfied. Thus D<sub>IN</sub> is strobed by WE, and set-up and hold times are referenced to WE.

#### **Data Output:**

The output buffer is three-state TTL compatible with a fan-out of two standard TTL loads. Data-out is the same polarity as data-in. The output is in a

high impedance state until CAS is brought low. In a read cycle, or readwrite cycle, the output is valid after t<sub>RAC</sub> from the falling edge of RAS when t<sub>RCD</sub> (max) is satisfied, or after t<sub>CAC</sub> from the falling edge of CAS when the transition occurs after t<sub>RCD</sub> (max). Data remains valid until CAS is returned to a high. In a write cycle the indentical sequence occurs, but data is not valid.

#### Page Mode:

Page-mode operation permits strobing the row-address into the MB 8264A while maintaining RAS at a low throughout all successive memory operations in which the row addresses don't change. Thus the power dissipated by the falling edge of RAS is saved. Further, access and cycle times are decreased because the time normally required to strobe a new row addresses are eliminated.

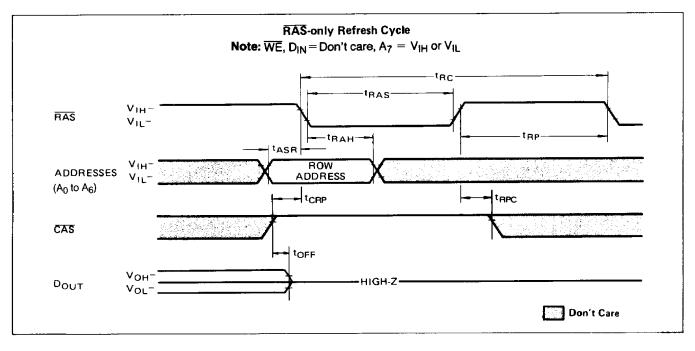

#### **RAS**-only Refresh

Refresh of the dynamic memory cells is accomplished by performing a memory cycle at each of the 128 row-addresses ( $A_0 \sim A_6$ ) at least every two milliseconds. During refresh, either  $V_{IL}$  or  $V_{IH}$  is permitted for  $A_7$ . RAS-only refresh avoids any output during refresh

because the output buffer is in a high impedance state unless  $\overline{CAS}$  is brought low. Strobing each of 128 row-addresses with  $\overline{RAS}$  will cause all bits in each row to be refreshed. Further  $\overline{RAS}$ -only refresh results in a substantial reduction in power dissipation.

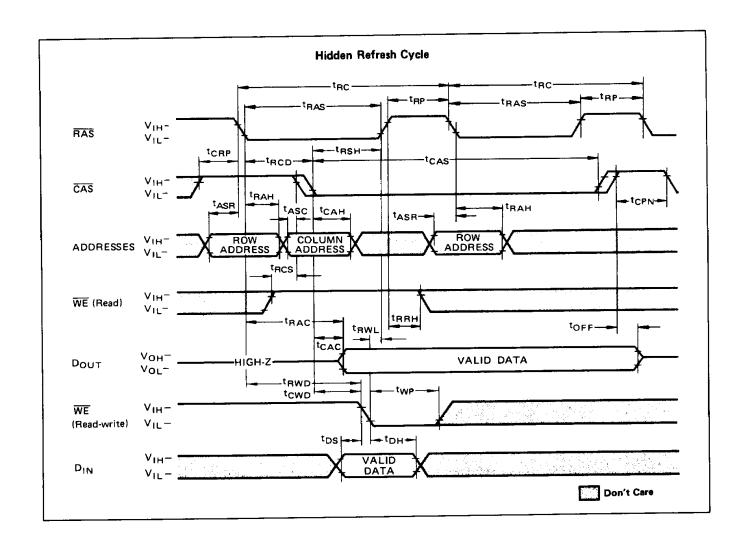

#### Hidden Refresh:

RAS-only refresh cycle may take place while maintaining valid output data. This feature is referred to as Hidden Refresh.

Hidden Refresh is performed by holding CAS as V<sub>IL</sub> from a previous memory read cycle.

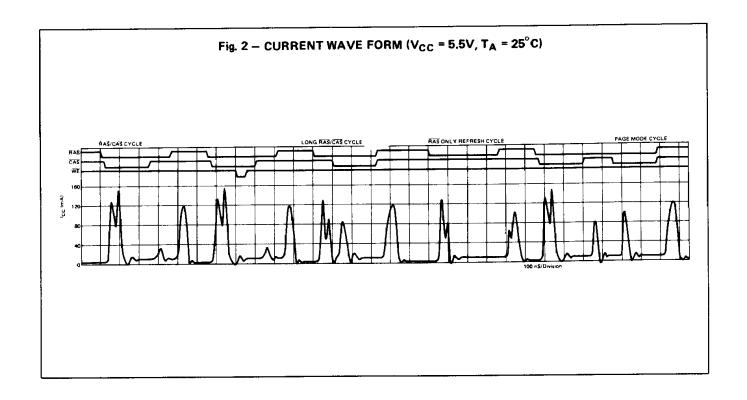

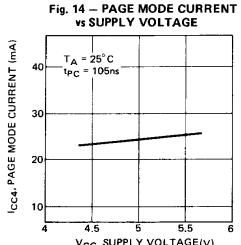

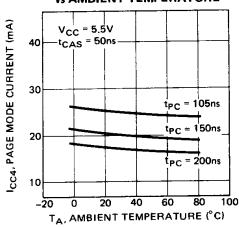

## TYPICAL CHARACTERISTICS CURVES

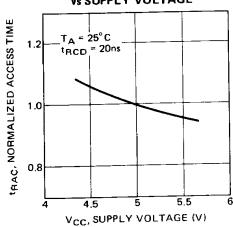

Fig. 3 — NORMALIZED ACCESS TIME vs SUPPLY VOLTAGE

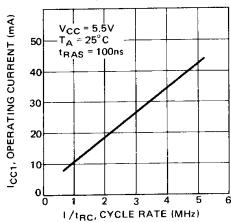

Fig. 5 — OPERATING CURRENT vs CYCLE RATE

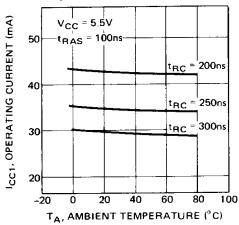

Fig. 7 — OPERATING CURRENT vs AMBIENT TEMPERATURE

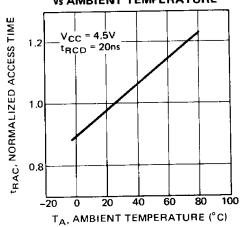

Fig. 4 — NORMALIZED ACCESS TIME vs AMBIENT TEMPERATURE

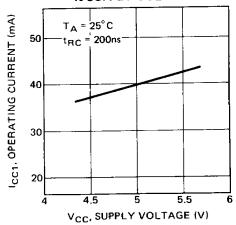

Fig. 6 — OPERATING CURRENT vs SUPPLY VOLTAGE

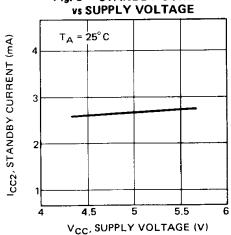

Fig. 8 - STANDBY CURRENT

Fig. 9 - STANDBY CURRENT VS AMBIENT TEMPERATURE V<sub>CC</sub> = 5.5V 1<sub>CC2</sub>, STANDBY CURRENT (mA) 40 60 80 -20 TA, AMBIENT TEMPERATURE (°C)

Fig. 11 — REFRESH CURRENT **vs SUPPLY VOLTAGE**  $T_A = 25^{\circ}C$ ICC3, REFRESH CURRENT (mA) T<sub>RC</sub> = 200ns 30 20 10 5 5.5 V<sub>CC</sub>, SUPPLY VOLTAGE(V)

Fig. 15 — PAGE MODE CURRENT vs AMBIENT TEMPERATURE

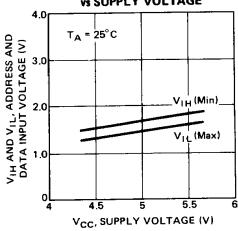

Fig. 17 — ADDRESS AND DATA INPUT VOLTAGE

vs AMBIENT TEMPERATURE

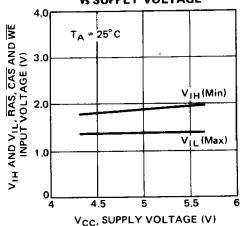

Fig. 19 – RAS, CAS AND WE VOLTAGE VS AMBIENT TEMPERATURE

Fig. 16 — ADDRESS AND DATA INPUT VOLTAGE

vs SUPPLY VOLTAGE

Fig. 18 — RAS, CAS AND WE INPUT VOLTAGE

vs SUPPLY VOLTAGE

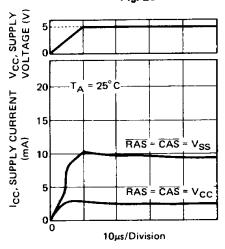

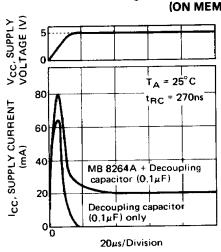

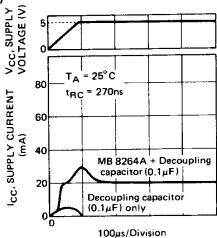

Fig. 20 — CURRENT WAVE FORM DURING POWER UP

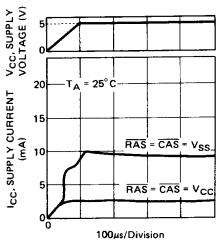

Fig. 21 — CURRENT WAVE FORM DURING POWER UP (ON MEMORY BOARD)

Fig. 22 — SUBSTRATE VOLTATE vs SUPPLY VOLTAGE (DURING POWER UP)

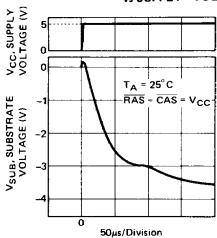

## PACKAGE DIMENSIONS

Standard 16-pin Ceramic DIP (Surfix : -Z)

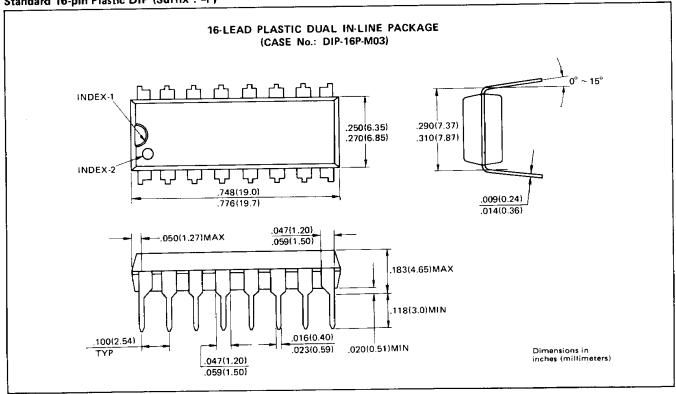

Standard 16-pin Plastic DIP (Surfix : -P)

### PACKAGE DIMENSIONS

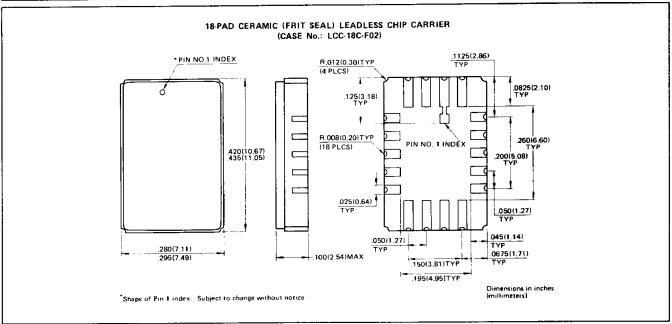

Standard 18-pad Ceramic LCC (Surfix: -TV)