# M62303FP

# High Precision Double Integration Type A/D Converter

REJ03D0862-0201 Rev.2.01 Dec 27, 2007

### **Description**

M62303FP is a double integration type A/D converter support system, and is a semiconductor integrated circuit which can work as A/D converter of 14 bits or more by being used with MCU and by inputting SI, SCK1, CS, and CONTIN.

High precision A/D translation system can be realized without using high precision external parts by proofreading A/D acquired values with two or more known conversion values such as reference voltage, grounding (zero) voltage and so forth.

### **Features**

- High precision (14 bits or more) double integration type A/D converter

- Positive/negative constant voltage source built-in (+6.3 V, -6.0 V Typ)

- Positive/negative constant current source built-in (Isource = 2 mA, Isink = 0.2 mA Max)

- Independent 2ch operational amplifier built-in

- System reset built-in (4.5 V Typ)

### **Application**

High precision control systems, such as temperature control and speed control

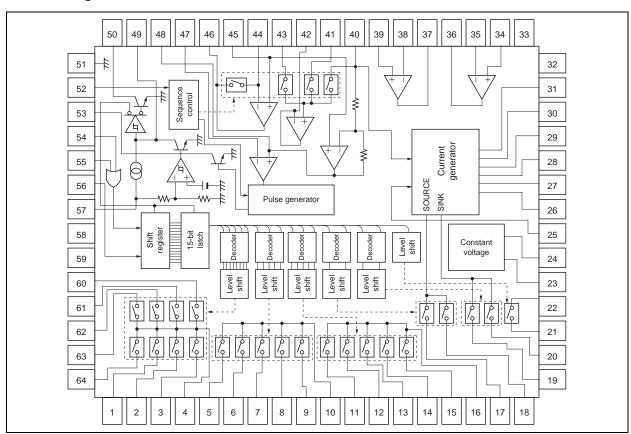

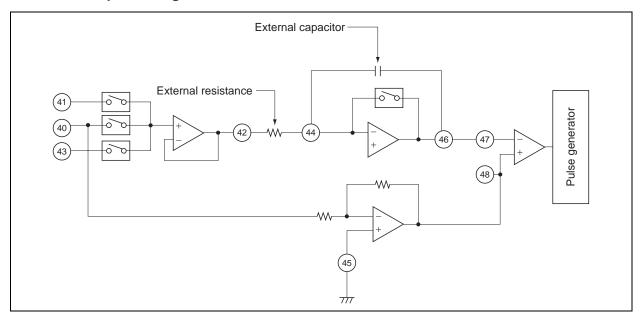

### **Block Diagram**

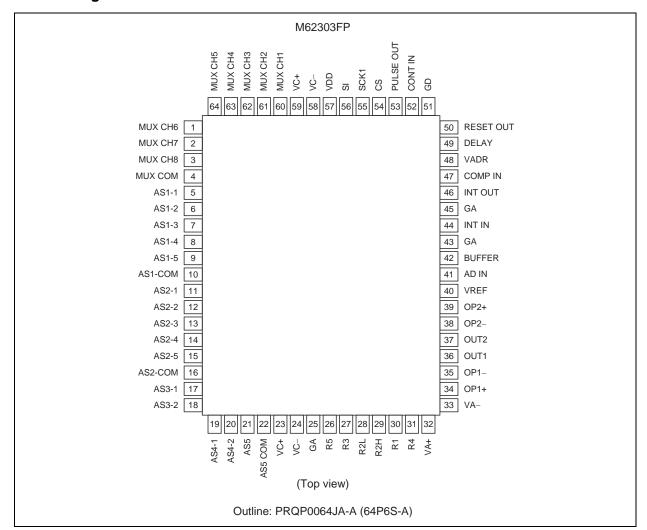

## **Pin Arrangement**

# **Pin Description**

| Pin No.                        | Pin Name            | Function                                                                                                                                                                                                                                                             |

|--------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56                             | SI                  | Serial data input terminal. Serial data of 15 bits data length is input.                                                                                                                                                                                             |

| 55                             | SCK1                | Shift clock input terminal. Signal from SI terminal is input into 15-bit shift register at the rise of a clock.                                                                                                                                                      |

| 54                             | CS                  | "L" level of this terminal enables shift clock, and "H" level makes shift register contents stored into multiplexer control register (analog switches) and unenables clock input.                                                                                    |

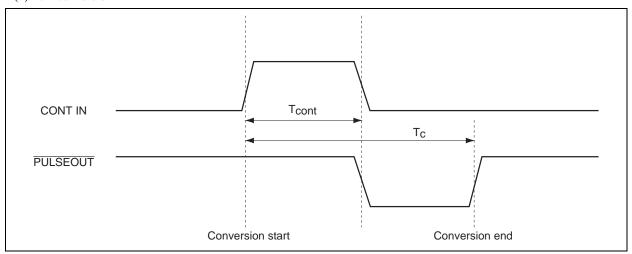

| 52                             | CONT IN             | A pulse is input. Double integration type A/D converter is started synchronizing with this pulse. Moreover, the optimal full scale can be set up by setting up with C and R so that it may be set to TCONT ≤ 2.14 CR.                                                |

| 57                             | VDD                 | Digital part power supply terminal                                                                                                                                                                                                                                   |

| 51                             | GD                  | Digital part GND terminal. This terminal is externally connected to analog ground terminal when IC is operative.                                                                                                                                                     |

| 50                             | RESET OUT           | Output terminal of reset circuit supervising the fall of a digital part power supply.                                                                                                                                                                                |

| 49                             | DERAY               | Reset output rise is delayed by adding capacitor.                                                                                                                                                                                                                    |

| 60, 61, 62, 63,<br>64, 1, 2, 3 | MUX1 to 8           | Input side terminal of multiplexer (analog switch group) MUX.                                                                                                                                                                                                        |

| 4                              | MUXCOM              | Output side COMMON terminal of multiplexer MUX.                                                                                                                                                                                                                      |

| 5, 6, 7, 8, 9                  | AS1-1 to 5          | Input side terminal of multiplexer (analog switch group) AS1.                                                                                                                                                                                                        |

| 10                             | AS1COM              | Output side COMMON terminal of multiplexer AS1.                                                                                                                                                                                                                      |

| 11, 12, 13, 14,<br>15          | AS2-1 to 5          | Input side terminal of multiplexer (analog switch group) AS2                                                                                                                                                                                                         |

| 16                             | AS2COM              | Output side COMMON terminal of multiplexer AS2                                                                                                                                                                                                                       |

| 17, 18                         | AS3-1 to 2          | Source type constant current source output terminal                                                                                                                                                                                                                  |

| 19, 20                         | AS4-1 to 2          | Sink type constant current source output terminal                                                                                                                                                                                                                    |

| 21                             | AS5                 | Analog switch AS5 input side terminal                                                                                                                                                                                                                                |

| 22                             | AS5COM              | Analog switch AS5 output side terminal                                                                                                                                                                                                                               |

| 23, 59                         | VC+                 | Positive power supply output terminal for analog switch drive                                                                                                                                                                                                        |

| 24, 58                         | VC-                 | Negative power supply output terminal for analog switch drive                                                                                                                                                                                                        |

| 25                             | GA                  | Analog part GND terminal                                                                                                                                                                                                                                             |

| 26, 27,<br>28, 29              | R5, R3,<br>R2L, R2H | Reference current setting terminal for constant current source                                                                                                                                                                                                       |

| 30                             | R1                  | Source type output current setting terminal for constant current source                                                                                                                                                                                              |

| 31                             | R4                  | Sink type output current setting terminal for constant current source                                                                                                                                                                                                |

| 32                             | VA+                 | Analog part positive power supply terminal                                                                                                                                                                                                                           |

| 33                             | VA-                 | Analog part negative power supply terminal                                                                                                                                                                                                                           |

| 34                             | OP1+                | Operational amplifier 1 non-inverting input terminal                                                                                                                                                                                                                 |

| 35                             | OP1-                | Operational amplifier 1 inverting input terminal                                                                                                                                                                                                                     |

| 36                             | OUT1                | Operational amplifier 1 output terminal                                                                                                                                                                                                                              |

| 37                             | OUT2                | Operational amplifier 2 output terminal                                                                                                                                                                                                                              |

| 38                             | OP2-                | Operational amplifier 2 inverting input terminal                                                                                                                                                                                                                     |

| 39                             | OP2+                | Operational amplifier 2 non-inverting input terminal                                                                                                                                                                                                                 |

| 40                             | VREF                | Standard voltage input for standard integration, and constant standard voltage input terminal for source current source setup                                                                                                                                        |

| 41                             | ADIN                | A/D conversion input terminal. Analog signal into ADIN terminal is converted into pulse width proportional to the input voltage.                                                                                                                                     |

| 42                             | BUFFER              | Output terminal of buffer amplifier which receives VREF, ADIN, and GA input. Internal analog switch for A/D conversion is switched by the CONTIN signal, and the voltage of three types of VREF, ADIN, and GA is output to BUFFER terminal through buffer amplifier. |

| 43, 45                         | GA                  | Analog part GND terminal                                                                                                                                                                                                                                             |

| 44                             | INTIN               | Input terminal of integration amplifier                                                                                                                                                                                                                              |

| 46                             | INTOUT              | Output terminal of integration amplifier                                                                                                                                                                                                                             |

| 47                             | COMPIN              | Input terminal of the comparator part of a double integration type A/D converter                                                                                                                                                                                     |

| 48                             | VADR                | Power supply output terminal used for reference terminal of comparator                                                                                                                                                                                               |

| 53                             | PULSEOUT            | A/D translation output terminal. Input analog signal is changed into pulse to be output.                                                                                                                                                                             |

## **Absolute Maximum Ratings**

(Ta = 25°C, unless otherwise noted)

| Item                               | Symbol            | Ratings                  | Unit | Conditions                              |

|------------------------------------|-------------------|--------------------------|------|-----------------------------------------|

| Analog power supply voltage        | VA+ VA-           | 22                       | V    |                                         |

| Switch part power supply voltage   | Vc+ Vc-           | 13.2                     | V    |                                         |

| Digital section supply voltage     | $V_{DD}$          | -0.3 to +7               | V    |                                         |

| A/D converter analog input voltage | V <sub>AIN</sub>  | -4 to +4                 | V    |                                         |

| PULSE OUT output current           | Isink (PO)        | 10                       | mA   |                                         |

| Reset output current               | Isink (RE)        | 10                       | mA   |                                         |

| Switch input voltage               | V <sub>SWIN</sub> | Vc- to Vc+               | V    |                                         |

|                                    |                   | VA- to VA+ *1            |      | At the line of fault voltage impression |

| Switch input current               | I <sub>SWIN</sub> | ±20*1                    | mA   | (Per one pin)                           |

|                                    |                   | ±100*1                   |      | (All the switch sum totals)             |

| Digital input voltage              | $V_{DIN}$         | $-0.3$ to $V_{DD} + 0.3$ | V    |                                         |

| Power dissipation                  | Pd                | 740                      | mW   |                                         |

| Operating temperature              | Topr              | -20 to +75               | °C   |                                         |

| Storage temperature                | Tstg              | -40 to +125              | °C   |                                         |

Note: 1. Represents the protection level at the time of abnormalities.

# **Operating Conditions**

$(Ta = 25^{\circ}C)$

| Block    | Item                                  | Symbol              | Min                | Тур   | Max       | Unit | Test Conditions |

|----------|---------------------------------------|---------------------|--------------------|-------|-----------|------|-----------------|

|          | Power supply voltage (positive side)  | VA+                 | +8.1               | +12   | +13       | V    |                 |

|          | Power supply voltage (negative side)  | VA-                 | 9                  | -8    | -7.2      | >    |                 |

|          | Power supply current (positive side)  | IA+                 |                    | 13    | 17        | mA   |                 |

| Analog   | Power supply current (negative side)  | IA-                 | _                  | 12    | 17        | mA   |                 |

|          | A/D converter analog standard voltage | $V_{REF}$           | 1.0                | 2.5   | 3.0       | ٧    |                 |

|          | A/D converter analog input voltage    | V <sub>AIN</sub>    | -V <sub>REF</sub>  | _     | $V_{REF}$ | ٧    |                 |

|          | Switch input voltage                  | V <sub>SWIN</sub>   | -6                 | _     | +6        | V    |                 |

|          | Input integration time                | T <sub>CONT</sub>   | 2                  | _     | 20        | ms   |                 |

|          | Power supply voltage                  | $V_{DD}$            | 4.80* <sup>2</sup> | 5.0   | 5.5       | V    |                 |

|          | Power supply current                  | I <sub>DD</sub>     |                    | 1.8   | 3         | mA   |                 |

|          | High-level input voltage              | $V_{\text{IN}}$     | 2.4                | _     | _         | V    |                 |

|          | Low-level input voltage               | $V_{IL}$            |                    | _     | 0.8       | V    |                 |

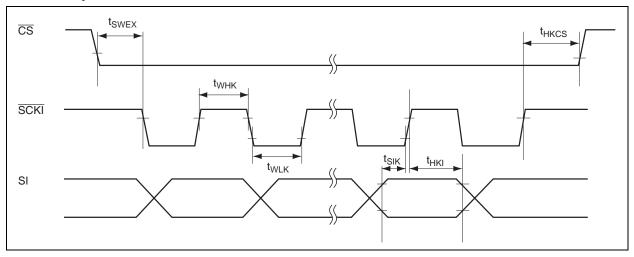

| Digital  | Serial clock waiting time             | t <sub>SCSK</sub>   | 250                |       | _         | ns   | CS↓→SCKI↓       |

| Dig      | Serial input setup time               | t <sub>SIK</sub>    | 100                |       | _         | ns   | SI→SCKI↑        |

|          | Serial input hold time                | t <sub>HKI</sub>    | 50                 |       | _         | ns   | SCKI↑→SI        |

|          | Serial clock low level time           | t <sub>WLK</sub>    | 200                |       | _         | ns   |                 |

|          | Serial clock high level time          | t <sub>WHK</sub>    | 200                | _     | _         | ns   |                 |

|          | Chip selection hold time              | t <sub>HKCS</sub>   | 50                 | _     | _         | ns   | SCKI↑→CS↑       |

| nal      | Integration capacitance               | C <sub>INT</sub> *3 | ı                  | 0.015 |           | μF   |                 |

| External | Voltage current conversion resistor   | R <sub>INT</sub>    | 56                 | 230   | 500       | kΩ   |                 |

Notes: 2. Represents the reset release voltage.

3. Set up as in 2.14  $R_{\text{INT}} - C_{\text{INT}} \ T_{\text{CONT}}.$

## **Electrical Characteristics**

$(Ta = 25^{\circ}C, unless otherwise noted)$  $VA+ = 12 \text{ V}, VA- = -SV, V_{REF} = 2.5 \text{ V}, V_{DD} = 5.0 \text{ V}, T_{CONT} = 7.3 \text{ ms}$

| Block                  | Item                                          | Symbol                   | Min  | Тур   | Max  | Unit | Test Cond                           | litions                    |

|------------------------|-----------------------------------------------|--------------------------|------|-------|------|------|-------------------------------------|----------------------------|

| d)                     | Analog input current                          | I <sub>I</sub>           | _    | 20    | 80   | nA   |                                     |                            |

| hine                   | Resolution                                    | ER                       | 14   | _     | _    | Bit  |                                     |                            |

| /ac                    | Linearity error*1                             | N, L                     | _    | 0.012 | _    | %FS  |                                     |                            |

| A/D Conversion Machine | Conversion range of fluctuation*2             | _                        | _    | 0.006 | _    | %FS  |                                     |                            |

| uve                    | Conversion time                               | Tc                       |      | 8.28  | _    | ms   | $C_{INT} = 0.015 \mu F$             | $V_{AIN} = 2.5 V$          |

| Con                    |                                               |                          |      | 15.58 | _    |      | $R_{INT} = 230 \text{ k}\Omega$     | $V_{AIN} = 0 V$            |

| 9                      |                                               |                          |      | 22.88 | _    |      |                                     | $V_{AIN} = -2.5 \text{ V}$ |

| 1                      | Saturation voltage                            | Vpo (sat)                |      | _     | 0.4  | V    | Isink (PO) = 6 mA                   |                            |

|                        | Conversion standard voltage                   | $V_{ADR}$                | -6.3 | -6.0  | -5.7 | V    |                                     |                            |

| Supply                 | Output voltage for switch part power supplies | Vc+                      | +6.0 | +6.3  | +6.6 | V    |                                     |                            |

| Power Supply           | Output voltage for switch part power supplies | Vc-                      | -6.6 | -6.3  | -6.6 | V    |                                     |                            |

|                        | Input voltage fluctuation                     | ΔVc                      | _    | _     | 100  | mV   | VA+: 8.1 to 13 V, VA-: -9 to -7.2 V |                            |

|                        | ON resistance                                 | R <sub>ON</sub>          |      | 100   | 200  | Ω    | –6 V Vds 6 V                        | Ta = 25°C                  |

|                        |                                               |                          |      | _     | 200  |      | Id = 1 mA                           | Ta = −40°C                 |

|                        |                                               |                          |      | _     | 300  |      |                                     | Ta = 85°C                  |

|                        | RON match                                     |                          | _    | 10    | 30   | %    |                                     |                            |

|                        | RON drift                                     | $\Delta R_{ON}/\Delta T$ | _    | 0.5   | _    | %/°C |                                     |                            |

|                        | Input off-leak                                | I <sub>Soff</sub>        | _    | ±0.1  | ±100 | nA   | Vd = -6 V, Vs = 6 V                 | Ta = 25°C                  |

| är                     | current                                       |                          |      | _     | ±100 |      | and                                 | Ta = 0°C                   |

| ج ۔                    |                                               |                          |      | _     | ±100 |      | Vs = -6 V, Vd = 6 V                 | Ta = 50°C                  |

| Switch Part            | Output off-leak                               | I <sub>Doff</sub>        |      | ±0.1  | ±100 | nA   | Vd = -6 V, Vs = 6 V                 | Ta = 25°C                  |

| Š                      | current                                       |                          |      |       | ±100 |      | and                                 | Ta = 0°C                   |

|                        |                                               |                          |      |       | ±100 |      | Vs = -6 V, Vd = 6 V                 | Ta = 50°C                  |

|                        | On-channel leak                               | I <sub>Don</sub>         |      | ±0.1  | ±100 | nA   | Vs = Vd = 6 V                       | Ta = 25°C                  |

|                        | current                                       | ent                      | _    | _     | ±100 |      | and                                 | Ta = 0°C                   |

|                        |                                               |                          |      |       | ±100 |      | Vs = Vd = -6 V                      | Ta = 50°C                  |

|                        | Off isolation                                 | OIRR                     | 70   | 80    |      | dB   | Vs = 2 Vp-p, f = 1 kHz              | $z, R_L = 100 \Omega$      |

|                        | Cross talk                                    | CCRR                     | 70   | 90    | _    | dB   | Vs = 2 Vp-p, f = 1 kHz              | z, $R_L = 100 \Omega$      |

Notes: 1. -V<sub>REF</sub> to 0 and 0 to V<sub>REF</sub> is made into full scale.

2. Tolerance width at the time of repeated conversion.

# **Electrical Characteristics (cont.)**

| Block                 | Item                                | Symbol                  | Min    | Тур     | Max  | Unit   | Test Conditions                     |

|-----------------------|-------------------------------------|-------------------------|--------|---------|------|--------|-------------------------------------|

|                       | Output source current               | I <sub>CS1</sub>        | 0.1    | _       | 2    | mA     | RL1 = 0 to 3000 Ω                   |

|                       | Output source current accuracy      | Δl <sub>CS1</sub>       | _      | _       | ±0.2 | %      | RL1 = 0 to 3000 Ω                   |

| urrent                | Output source current drift         |                         | _      | ±10     | _    | ppM/°C |                                     |

| The Source of Current | Permissible load resistance         | RL1                     | _      | _       | 3000 | Ω      | With the sauce current maximum      |

| Jinc                  | Output sink current                 | I <sub>CS2</sub>        | _      | _       | -0.2 | mA     | RL2 = 0 to 1000 $\Omega$            |

| The S                 | Output sink current accuracy        | $\Delta I_{CS2}$        | _      | _       | ±0.2 | %      | RL2 = 0 to 1000 $\Omega$            |

|                       | Output sink current drift           |                         | _      | ±10     | _    | ppM/°C |                                     |

|                       | Permissible load resistance         | RL2                     | _      | _       | 1000 | Ω      | With the sink current maximum       |

|                       | Reset detection voltage             | Vs                      | 4.3    | 4.5     | 4.7  | V      |                                     |

| Reset                 | Hysteresis (upper side)             | Vhys                    | 40     | 70      | 100  | mV     |                                     |

|                       | Delay time                          | t <sub>D</sub>          | 0.6    | 1       | 1.5  | ms     | C <sub>DELAY</sub> = 0.01 μF        |

|                       | Saturation voltage                  | VR (sat)                | _      | _       | 0.4  | V      | Isink = 6 mA                        |

|                       | Input offset voltage                | VIo                     | _      | 1.0     | 6.0  | mV     | $Rs = 10 \text{ k}\Omega$           |

|                       | Input offset voltage drift          | ΔVm/ΔT                  | _      | 3       | _    | μV/°C  | $Rs = 10 \text{ k}\Omega$           |

|                       | Input offset current                | IIo                     | _      | 20      | 200  | nA     |                                     |

|                       | Input offset current drift          | Δlm/ΔT                  | _      | 1       | _    | nA/°C  |                                     |

| _                     | Input bias current                  | I <sub>B</sub>          | _      | 80      | 500  | nA     |                                     |

| Operational Amplifier | Input bias current drift            | $\Delta I_{B}/\Delta T$ | _      | 2       | _    | nA/°C  |                                     |

| \rightarrow           | Open loop gain                      | AV                      | 20000  | 100000  |      | Ω      | $R_L = 2 k\Omega, V_O = +8 V, -4 V$ |

| ration                | Open loop gain rejection ratio      | CMR                     | 70     | 90      | _    | dB     | $Rs = 10 \text{ k}\Omega$           |

| odo                   | Power supply change rejection ratio | SVR                     | _      | 30      | 150  | μV/V   | Rs = 10 kΩ                          |

|                       | Maximum output voltage              | Vom                     | +9, -5 | +11, -7 | _    | V      | $R_L = 10 \text{ k}\Omega$          |

| 1                     | Slew rate                           | S. R.                   | 0.4    | 0.8     | _    | V/μs   | AV = 1                              |

|                       | Maximum output current              | Іор                     | 5      | 10      | _    | mA     |                                     |

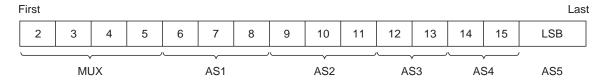

## **Digital Format**

1. Multiplexer (MUX)

|         | 5th | 4th | 3rd | 2nd |

|---------|-----|-----|-----|-----|

| ALL OFF | 0   | 0   | 0   | 0   |

| CH1 ON  | 1   | 0   | 0   | 0   |

| CH2 ON  | 0   | 1   | 0   | 0   |

| CH3 ON  | 1   | 1   | 0   | 0   |

| CH4 ON  | 0   | 0   | 1   | 0   |

| CH5 ON  | 1   | 0   | 1   | 0   |

| CH6 ON  | 0   | 1   | 1   | 0   |

| CH7 ON  | 1   | 1   | 1   | 0   |

| CH8 ON  | 0   | 0   | 0   | 1   |

| ALL OFF | 1   | 0   | 0   | 1   |

| ALL OFF | 0   | 1   | 0   | 1   |

| ALL OFF | 1   | 1   | 0   | 1   |

| ALL OFF | 0   | 0   | 1   | 1   |

| ALL OFF | 1   | 0   | 1   | 1   |

| ALL OFF | 0   | 1   | 1   | 1   |

| ALL OFF | 1   | 1   | 1   | 1   |

2. Analog switch 1 (AS1)

|         | 8th | 7th | 6th |

|---------|-----|-----|-----|

| ALL OFF | 0   | 0   | 0   |

| AS1-10N | 1   | 0   | 0   |

| 1-2ON   | 0   | 1   | 0   |

| 1-3ON   | 1   | 1   | 0   |

| 1-40N   | 0   | 0   | 1   |

| 1-5ON   | 1   | 0   | 1   |

| ALL OFF | 0   | 1   | 1   |

| ALL OFF | 1   | 1   | 1   |

3. Analog switch 2 (AS2)

|         | 11th | 10th | 9th |

|---------|------|------|-----|

| ALL OFF | 0    | 0    | 0   |

| AS2-1ON | 1    | 0    | 0   |

| 2-2ON   | 0    | 1    | 0   |

| 2-30N   | 1    | 1    | 0   |

| 2-40N   | 0    | 0    | 1   |

| 2-50N   | 1    | 0    | 1   |

| ALL OFF | 0    | 1    | 1   |

| ALL OFF | 1    | 1    | 1   |

4. Analog switch 3 (AS3)

|         | 13th | 12th |

|---------|------|------|

| ALL OFF | 0    | 0    |

| AS3-1ON | 1    | 0    |

| 3-2ON   | 0    | 1    |

| ALL OFF | 1    | 1    |

5. Analog switch 4 (AS4)

| •       | ` '  |      |

|---------|------|------|

|         | 15th | 14th |

| ALL OFF | 0    | 0    |

| AS4-1ON | 1    | 0    |

| 4-20N   | 0    | 1    |

| ALL OFF | 1    | 1    |

6. Analog switch 5 (AS5)

|       | LSB |

|-------|-----|

| OFF   | 0   |

| AS5ON | 1   |

# **Sequence Timing Chart**

## (1) A/D conversion

## (2) DATA Input

## About the Input Voltage VX

Given the applied voltage into 41 pin is VX in the diagram above,

$$VX = \frac{TGND - TX}{TGND - TR} \bullet VR \qquad T = Pulse width$$

TGND, TR, and TX can be respectively expressed with nGND/f, nR/f, and nX/f, (f is clock frequency; nGND, nR, nX is count values for clock frequency f.)

If these are substituted for an upper formula,

$$VX = \frac{nGND - nX}{nGND - nR} \bullet VR$$

VX can be expressed in this way for the number of counters.

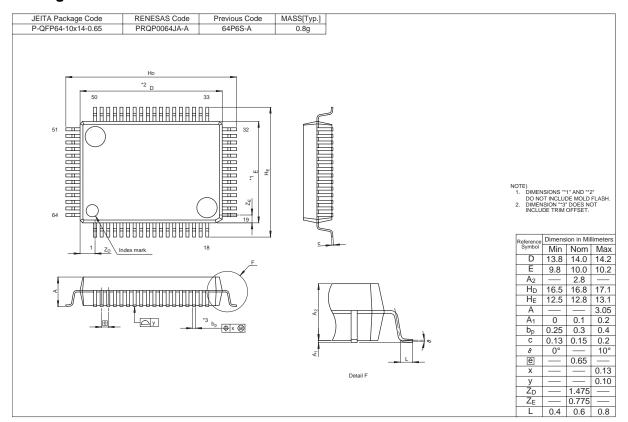

## **Package Dimensions**

### Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Notes:

1. This document is provided for reference purposes only so that Penesas customers may select the appropriate Renesas products for their use. Renesas neither makes in the reference purposes only so that Penesas customers may select the appropriate Renesas products for their use. Renesas neither makes are all to the source of the product of the source of th

### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510