LC8945

SCSI (Small Computer System Interface)

Protocol Controller

#### Overview

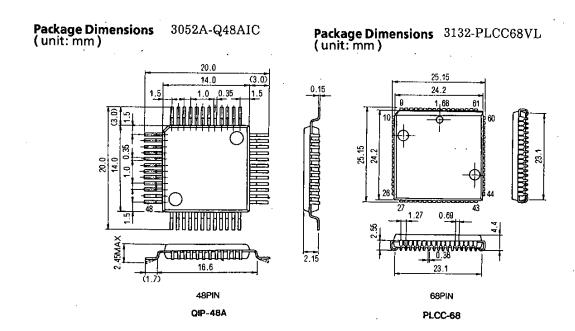

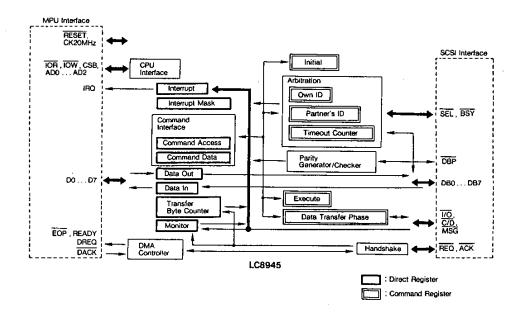

The LC8945 SCSI controller provides complete support and arbitration for asynchronous data transfer between an MPU bus and a single-ended SCSI bus. It is capable of operating as either initiator or target roles, and incorporates automatic arbitration, selection and reselection functions, parity generation and checking circuits, and 48mA open-drain line drivers. It does not support synchronous data transfer. The LC8945 uses a high-speed low-power 1.5µm CMOS process. It operates with a 20MHz clock and a single 5V power supply. The LC8945 is available in either a 48-pin QIP package or a 68-pin PLCC package.

#### **Features**

- SCSI protocol controller

- · Data transfer under program or DMA control

- · Maximum asynchronous transfer rate of more than 5MB/s

- · Capable of operating as either initiator or target

- · Automatic arbitration, selection and reselection functions

- · Parity generation and checking circuits

- · 48mA currents sink open-drain SCSI bus drivers

- · 24-bit transfer counter, 24-bit timeout counter

SANYO Electric Co., Ltd. Semiconductor Business Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

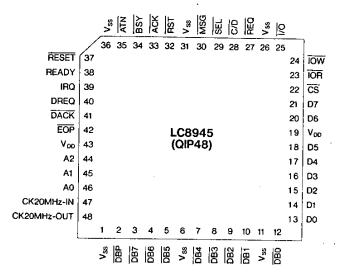

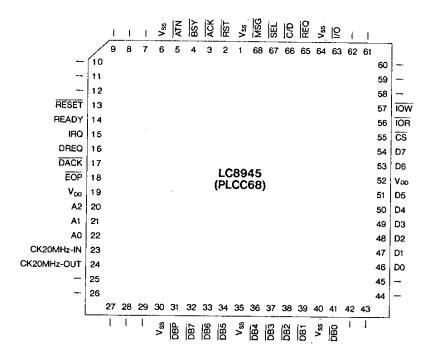

## Pin Assignment

# Equivalent Circuit Block Diagram

# Pin Description

| <mpu interface<="" th=""><th>&gt;</th><th></th></mpu> | >            |                                                                                                                   |

|-------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------|

| A0 to A2                                              | Input        | Internal register address select :                                                                                |

|                                                       |              | The addressed register is selected when $\overline{\text{CS}}$ = "0"                                              |

| $\overline{\text{CS}}$                                | Input        | Chip select:                                                                                                      |

|                                                       |              | Enables write to and read from internal registers.                                                                |

| DACK                                                  | Input        | DMA acknowledge :                                                                                                 |

|                                                       |              | DACK resets DREQ and connects the Data-In and Data-Out data                                                       |

|                                                       |              | transfer registers to D0 to D7.                                                                                   |

| DREQ                                                  | Output       | DMA request:                                                                                                      |

|                                                       |              | DREQ requests read from and write to the data transfer registers in                                               |

|                                                       |              | DMA transfer mode                                                                                                 |

| D0 to D7                                              | Input/Output | MPU data bus :                                                                                                    |

|                                                       |              | D0 to D7 are connected to the internal registers.                                                                 |

| EOP                                                   | Output       | End of process:                                                                                                   |

|                                                       |              | Command completion with byte being currently transferred or                                                       |

|                                                       |              | already transferred in DMA transfer mode                                                                          |

| READY                                                 | Output       | Accepts DMA acknowledge in DMA transfer mode                                                                      |

| ĪOR                                                   | Input        | I/O read :                                                                                                        |

|                                                       |              | Data in the register specified by A0 to A2 is placed on the MPU data                                              |

| <del>_</del>                                          |              | bus.                                                                                                              |

| IOW                                                   | Input        | I/O write:                                                                                                        |

|                                                       |              | Data on the MPU data bus is written into the register specified by A0                                             |

|                                                       |              | to A2.                                                                                                            |

| IRQ                                                   | Output       | MPU interrupt request line :                                                                                      |

|                                                       |              | Active HIGH on command completion or abortion, or on error                                                        |

|                                                       |              | condition.                                                                                                        |

| RESET                                                 | Input/Output | Initializes the LC8945                                                                                            |

| CK20MHz-IN                                            | Input        | Internal oscillator amplifier input                                                                               |

| CK20MHz-OU                                            | T Output     | Internal oscillator amplifier output                                                                              |

|                                                       |              | A 20MHz crystal may be connected between CK20MHz-IN and CK20MHz-OUT, or an external 20MHz clock may be applied to |

|                                                       |              | CK20MHz-IN.                                                                                                       |

#### <SCSI Interface>

The SCSI interface consists of the signals listed below. These signals conform fully to the SCSI specification. Refer to the SCSI standard documentation for the functions of these signals.

| $\overline{\text{ACK}}$   | $\overline{	ext{REQ}}$                     |

|---------------------------|--------------------------------------------|

| $\overline{\text{ATN}}$   | $\overline{	ext{RST}}$                     |

| $\overline{\text{BSY}}$   | $\overline{	ext{SEL}}$                     |

| $\overline{\mathrm{C/D}}$ | $\overline{ m DB0}$ to $\overline{ m DB7}$ |

| Ī/O                       | $\overline{	ext{DBP}}$                     |

| $\overline{\text{MSG}}$   |                                            |

### **Direct Registers**

|   | <b>A</b> 1 |   | R/W | Register Na   |      | D7   | D6   | `D5         | D4   | D3   | D2   | D1   | D0   |

|---|------------|---|-----|---------------|------|------|------|-------------|------|------|------|------|------|

| 0 | 0          | 0 | w   | Interrupt M   |      | MSK  | "O"  | <b>"</b> 0" | "0"  | *O"  | "0"  | "O"  | "O"  |

| 0 | 0          | 0 | R   | Interrupt     |      | END  | ERR  | ABRT        | PMM  | то   | PE   | RST  | ATN  |

| 0 | 0          | 1 |     | ········RESEF | RVED | •    |      |             |      |      |      |      |      |

| 0 | 1          | 0 | w   | Command       | No   | CN7  | CN6  | CN5         | CN4  | CN3  | CN2  | CN1  | CN0  |

| 0 | 1          | 0 | R   | Monitor       |      | PM1  | PM2  | 1/0         | C/D  | MSG  | ATN  | RST  | DATA |

| 0 | 1          | 1 | R/W | Command       | Data | CD7  | CD6  | CD5         | CD4  | CD3  | CD2  | CD1  | CDO  |

| 1 | 0          | 0 | R/W | Transfer      | 1    | BC7  | BC6  | BC5         | BC4  | всз  | BC2  | BC1  | BCO  |

| 1 | 0          | 1 | R/W | Byte          | 2    | BC15 | BC14 | BC13        | BC12 | BC11 | BC10 | BC9  | BC8  |

| 1 | 1          | 0 | R/W | Counter       | 3    | BC23 | BC22 | BC21        | BC20 | BC19 | BC18 | BC17 | BC16 |

| 1 | 1          | 1 | w   | Data-out      |      | DO7  | DO6  | DO5         | DO4  | DO3  | DO2  | DO1  | DOO  |

| 1 | 1          | 1 | R   | Data-in       |      | DI7  | DI6  | D15         | D14  | DI3  | DI2  | DI1  | DIO  |

## <Interrupt Mask> Address 0, Write Register

When all bits of the interrupt register are not 0, the interrupt mask determines whether the IRQ signal should be output or not.

All bits "1": IRQ signal is output.

All bits "0": IRQ signal is not output.

### <Interrupt > Address 0, Read Register

When the LC8945 requests interrupt service from the CPU, the appropriate bits of the interrupt register are set HIGH, and IRQ is set HIGH.

- Bit 7 : END Command execution complete.

- (1) Selection

- (2) Reselection

- (3) Data transfer

- Bit 6 : ERR Abnormal condition occurred during command execution.

- (1) ID number incorrect

- (2) A Start Reselection command is ineffective, when arbitration is disabled by the Initialize command.

- Bit 5 : ABRT Command execution aborted.

- (1) Defeated by arbitration.

- Bit 4: PMM Phase mismatch.

The set values of I/O, C/D and MSG conflicted with the SCSI bus I/O, C/D and MSG values during the data transfer phase.

- Bit 3 : TO Timeout executed during selection/reselection phase.

- Bit 2 : PE Parity error.

Only occurs if parity check has been set by the Initialize command: parity check error in selection/reselection phase or data transfer phase.

- Bit 1 : RST SCSI bus RST signal active

- Bit 0 : ATN Initiator requires attention.

## < Command Access, Command Data > Address 2,3, Write Register

The Command Access and Command Data registers are used to write commands to the LC8945, or to read the partner's ID. Refer to Commands.

## <Monitor> Address 3, Read Register

Bit 7,6: Phase Monitor

| PN          | M1 PM0          | Description                                                             |

|-------------|-----------------|-------------------------------------------------------------------------|

| 0           | 0               | Another                                                                 |

| 0           | 1               | Arbitration-Phase                                                       |

| 1           | 0               | Selection · Reselection-Phase                                           |

| 1           | 1               | Data Transfer Phase                                                     |

| Bit 5 : I/O | SCSI bus I/0    | O signal value                                                          |

| Bit 4 : C/D | SCSI bus C/     | D signal value                                                          |

| Bit 3 : MS  | G SCSI bus M    | SG signal value                                                         |

| Bit 2 : ATI | N SCSI bus A'   | l'N signal value                                                        |

| Bit 1 : RST | SCSI bus R      | ST signal value                                                         |

| Bit 0 : DA  | ΓΑ True if data | is present in the data transfer registers during a data transfer phase. |

# <Transfer Byte Counter> Address 4,5,6, Read/Write Register

The data transfer counter is 24 bits wide. Transfer Byte Counter register 1 is the least significant 8 bits, and counter 3 is the most significant 8 bits. Since data transfer starts when Transfer Byte Counter 1 is set, Transfer Byte Counter 2 and 3, and any other registers that need to be set must be written to beforehand.

# <Data Out Register> Address 7, Write Register

Data is transferred from the MPU bus to the SCSI bus during the Data Transfer Phase via the Data-Out Register.

## < Data In Register > Address 7, Read Register

Data is transferred from the SCSI bus to the MPU bus during the Data Transfer Phase via the Data-In Register.

### Commands

The command data CD0 to CD7 is first written to the Command Data Register, then the command code CA0 to CA2 is written to the Command Access Register.

The command code is first written into the Command Data Register, then the Command Access Register is read to access the specified data.

| CA2 | CA1 | CA0 | R/W | Command Name     | CD7         | CD6         | CD5  | CD4         | CD3         | CD2  | ÇD1         | CD0         |

|-----|-----|-----|-----|------------------|-------------|-------------|------|-------------|-------------|------|-------------|-------------|

| 0   | 0   | 0   | w   | Initial          | I/T         | ARB         | MONO | PC          | <b>"</b> 0" | "O"  | <b>"</b> 0" | <b>"</b> 0" |

| 0   | 0   | 1   | W   | Set Own ID       | <b>"</b> 0" | "O"         | "0"  | "0"         | <b>"</b> O" | Ol2  | Ol1         | OIO         |

| 0   | 1   | 0   | W   | Set Partner's ID | "0"         | <b>"</b> 0" | "0"  | <b>"</b> O" | <b>"</b> 0" | PI2  | Pii         | PIO         |

| 0   | 1   | 0   | R   | Get Partner's ID | PID7        | PID6        | PID5 | PID4        | PID3        | PID2 | PID1        | PIDO        |

| 0   | 1   | 1   | W   | Set Timeout      | TC24        | TC23        | TC22 | TC21        | TC20        | TC19 | TC18        | TC17        |

|     |     |     |     | Counter          |             | •           |      |             |             |      |             |             |

| 1   | 0   | 0   |     | RESERVED         |             |             |      |             |             |      |             |             |

| 1   | 0   | 1   | W   | Set Data         | I/O         | C/D         | MSG  | DMA         | BLK         | "O"  | "O"         | <b>"</b> O" |

|     |     |     |     | Transfer Phase   |             |             |      |             |             |      |             |             |

| 1   | 1   | 0   |     | RESERVED         |             |             |      |             |             |      |             |             |

| 1   | 1   | 1   | R/W | Execute          | SEL         | RSL         | ATN  | RST         | DŢP         | CLR  | "0"         | RRR         |

### <Initialize> Command 000

SCSI operational mode is set according to bits 4 to 7 written into the Command Data Register.

Bit 7 : Initiator/Target

Bit 6 : Arbitration Select/Deselect

Bit 5: Initiator Single/Multiple

Bit 4 : Parity Check Select/Deselect

Bit 3 : "0"

Bit 2 : "0"

Bit 1 : "0"

Bit 0 : "0"

### <Set Own ID> Command 001

The binary value written into the Command Data Register bits 2 to 0 is set as the Own ID.

### <Partner's ID> Command 010

The binary value written into the Command Data Register bits 2 to 0 is set as the Partner's ID.

#### <Get Partner's ID> Command 010

The value read from the Command Access Register is the partner's ID, where the position of the set bit indicates the ID, as follows:

Bit 7: Partner's ID=7

Bit 6 : Partner's ID=6

Bit 5: Partner's ID=5

Bit 4 : Partner's ID=4

Bit 3 : Partner's ID = 3

Bit 2 : Partner's ID = 2

Bit 1 : Partner's ID=1

Bit 0 : Partner's ID=0

### <Set Timeout Counter > Command 011

The value written into the Command Data Register is loaded into the timeout counter. Value between 13.1ms and 6.7s may be set.

# <Set Data Transfer Phase > Command 101

Transfer mode is set according to bits 4 to 7 written into the Command Data Register.

Bit 7 : I/O

Bit 6 : C/D

Bit 5 : MSG

Bit 4 : DMA/Program

Bit 3 : Block/Single

Bit 2 : "0"

Bit 1 : "0"

Bit 0 : "0"

### <Execute> Command 111

The phase specified by the value written into the Command Data Register is started.

Bit 7: Selection

Bit 6 : Reselection

Bit 5 : Attention

Bit 4 : SCSI reset

Bit 3 : Data Transfer Phase

Bit 2 : Clear

Bit 1 : "0"

Bit 0 : RRR (Chip Reset)

| Absolute Maximum Ratings Maximum Supply Voltage Input/Output Voltage Operating Temperature Storage Temperature Soldering Temperature | at $V_{SS} = 0V$ $V_{DD}$ max $V_{I}, V_{O}$ Topr $Tstg$ | Ta = 25°C Ta = 25°C  10s (at pin)                         | - 0.3 to +<br>- 0.3 to V <sub>DD</sub> +<br>- 30 to +<br>- 55 to + | -7.0<br>-0.3<br>+70 | unit<br>V<br>V<br>°C<br>°C<br>°C |      |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|---------------------|----------------------------------|------|

| Allowable Operating Condition                                                                                                        | tions at Ta= -                                           | $-30 \text{ to } +70^{\circ}\text{C}, V_{SS} = 0\text{V}$ | min                                                                | typ                 | max                              | unit |

| Supply Voltage                                                                                                                       | $ m v_{DD}$                                              | , 55                                                      | 4.5                                                                | -J F                | 5.5                              | V    |

| Input Voltage                                                                                                                        | $V_{IN}$                                                 |                                                           | 0                                                                  |                     | $V_{DD}$                         | v    |

| DC Characteristics at V <sub>SS</sub> =0                                                                                             | V,V <sub>DD</sub> =4.5 to                                | 5.5V,Ta = $-30$ to $+70$ °C                               |                                                                    |                     |                                  |      |

| (1) SCSI Interface                                                                                                                   |                                                          |                                                           | min                                                                | typ                 | max                              | unit |

| Input 'H'-Level Voltage                                                                                                              | $V_{IH1}$                                                |                                                           | 2.0                                                                | 71                  |                                  | V    |

| Input 'L'-Level Voltage                                                                                                              | $V_{IL1}$                                                |                                                           |                                                                    |                     | 0.8                              | v    |

| Output 'L'-Level Voltage                                                                                                             | $V_{OL1}$                                                | I <sub>OL</sub> =48mA                                     |                                                                    |                     | 0.5                              | V    |

| (2) MPU Interface (Except CK2                                                                                                        | min                                                      | typ                                                       | max                                                                | unit                |                                  |      |

| Input 'H'-Level Voltage                                                                                                              | $V_{IH2}$                                                |                                                           | 2.2                                                                |                     |                                  | V    |

| Input 'L'-Level Voltage                                                                                                              | $V_{IL2}$                                                |                                                           |                                                                    |                     | 0.8                              | V    |

| Output 'H'-Level Voltage                                                                                                             | $V_{OH2}$                                                | $I_{OL} = 3mA$                                            |                                                                    |                     | 2.4                              | v    |

| Output 'L'-Level Voltage                                                                                                             | $V_{\mathrm{OL2}}$                                       | $I_{OL} = 3mA$                                            |                                                                    |                     | 0.4                              | v    |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.