CMOS LSI

LC89610

## Preliminary

SANYO

#### Overview

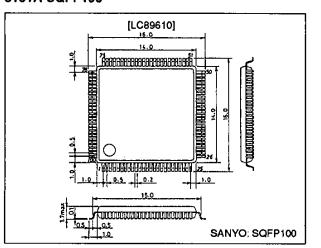

The LC89610 is a playback signal processing CMOS LSI that supports the mini-disk data format. Data that has been decoded by a CD decoder, an ACIRC decoder, or a CD-ROM decoder circuit is passed to a DRAM controller circuit and the LC89610 uses external DRAM to process shock proof. The shock proof processed data is passed to an audio data decoding LSI, the LC89602.

No. 💥 5120

#### Features

- · EFM decoder and PLL clock generator

- Detection, protection, and interpolation of the EFM frame synchronization signal

- Servo command control

- On-chip ACIRC decoder and ACIRC RAM

- ±8 frame jitter margin

- Powerful error detection and correction (C1: dual errors, C2: quadruple errors)

- · CLV control using EFM and ADIP signals

- · Subcode Q decoding and CRC error checking

- Shock proof memory using 1, 4, 16, or 64 Mbits of external DRAM

- Buffering control and management for TOC and UTOC data

- · Buffering control and management for subdata

- · ADIP decoding and CRC error checking

- Low-power design using a 0.8 μm rule CMOS process

- Support for low-voltage operation ( $V_{DD} = 3.0$  to 5.5 V)

- CCB based CPU interface

# **Package Dimensions**

unit: mm 3181A-SQFP100

### SANYO Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

## **Specifications**

### Absolute Maximum Ratings at $V_{SS}$ = 0 V

| Parameter                 | Symbol                        | Conditions             | Ratings                       | Unit |

|---------------------------|-------------------------------|------------------------|-------------------------------|------|

| Maximum supply voltage    | V <sub>DD</sub> max           | Ta = 25°C              | -0.3 to +7.0                  | V    |

| Input and output voltages | v <sub>i</sub> v <sub>o</sub> | Ta = 25°C              | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating temperature     | Topr                          |                        | -30 to +70                    | °C   |

| Storage temperature       | Tstg                          |                        | 55 to +125                    | °C   |

| Soldering conditions      |                               | 10 seconds (pins only) | 260                           | •C   |

#### Allowable Operating Ranges at Ta = -30 to $+70^{\circ}$ C, $V_{SS} = 0$ V

| Parameter      | Symbol          | Conditions | min | typ | max             | Unit |

|----------------|-----------------|------------|-----|-----|-----------------|------|

| Supply voltage | V <sub>DD</sub> |            | 3.0 |     | 5.5             | V    |

| Input voltage  | V <sub>IN</sub> |            | 0   |     | V <sub>DD</sub> | V    |

# DC Characteristics at Ta = -30 to +70 $^{\circ}C$ , $V_{SS}$ = 0 V, $V_{DD}$ = 4.5 to 5.5 V

| Parameter                 | Symbol          | Conditions                       | min                   | typ | max                                    | Unit |

|---------------------------|-----------------|----------------------------------|-----------------------|-----|----------------------------------------|------|

| Input high level voltage  | VIH             | *1                               | 0.8 V <sub>DD</sub>   | -   |                                        | v    |

| Input low level voltage   | VIL             | *1                               |                       |     | 0.2 V <sub>DD</sub>                    | v    |

| Input high level voltage  | VIH             | *2                               | 0.7 V <sub>DD</sub>   |     |                                        | v    |

| Input low level voltage   | VIL             | *2                               |                       |     | 0.3 V <sub>DD</sub>                    | v    |

| Input high level voltage  | VIH             | *3                               | 0.6 V <sub>DD</sub>   |     |                                        | v    |

| Input low level voltage   | VIL             | *3                               |                       |     | 0.4 V <sub>DD</sub>                    | v    |

| Output high level voltage | V <sub>OH</sub> | I <sub>OH</sub> = -1 mA, *4      | V <sub>DD</sub> - 0.1 |     |                                        | v    |

| Output low level voltage  | V <sub>OL</sub> | l <sub>OL</sub> ⊨ 1 mA, *4       |                       |     | 0.1                                    | v    |

| Output high level voltage | V <sub>OH</sub> | I <sub>OH</sub> = -1 mA, *5      | V <sub>DD</sub> - 1.0 |     | ······································ | v    |

| Output low level voltage  | V <sub>OL</sub> | l <sub>OL</sub> = 1 mA, *5       |                       |     | 1.0                                    | v    |

| Output high level voltage | V <sub>OH</sub> | I <sub>OH</sub> = -3 mA, *6      | V <sub>DD</sub> - 2.1 |     |                                        | v    |

| Output low level voltage  | VOL             | t <sub>OL</sub> = 3 mA, *7       |                       |     | 0.4                                    | v    |

| Input leakage current     | և               | $V_1 = V_{SS}, V_{DD}$           | -10                   |     | +10                                    | μA   |

| Output leakage current    | loz             | For high-impedance state outputs | -10                   |     | +10                                    | ۸ µ  |

| Pull-up resistance        | R <sub>UP</sub> | *8                               | 10                    | 20  | 40                                     | kΩ   |

| Quiescent current         | IDD             | *9                               |                       | 0.1 | 200                                    | μA   |

| Oulescent current         |                 | *10                              |                       | 250 | 475                                    | μA   |

Note: 1. HFL, TES, CE, CL, SUBREQ, SREQ, RESET, ADIPCRI, BIDATAI, BICLKI 2. Inputs other than \*1, 2, and 4 XIN. 3. EFMIN

4. PDO

5. EFMO

6. Outputs other than \*5 and \*6 XOUT, AO, and DO (open-drain output).

7. Outputs other than \*5 and \*6 XOUT, and AO.

8. For MD0 to MD3, TEST1 to TEST5. However, note that the pull-up resistors are not connected when the PULLSW pin is low.

9. When the PULLSW pin is low, outputs are open, and V<sub>I</sub> = V<sub>SS</sub> or V<sub>DD</sub>. 10.When the PULLSW pin is high, outputs are open, and V<sub>I</sub> = V<sub>SS</sub> or V<sub>DD</sub>.

**Block Diagram**

.

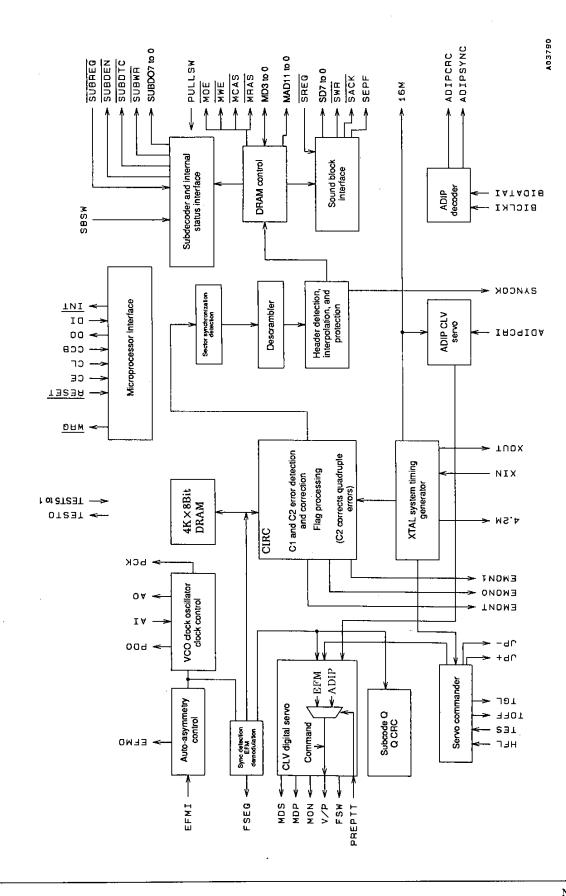

#### **Pin Functions**

| Pin No.  | Symbol          | 1/0 | Function                                       |

|----------|-----------------|-----|------------------------------------------------|

| 1        | MDP             | 0   | CLV servo signal output                        |

| 2        | MDS             | 0   | CLV servo signal output                        |

| 3        | FSW             | 0   | CLV servo signal output                        |

| 4        | V/P             | 0   | CLV servo signal output                        |

| 5        | TES             | ł   | Track jump signal input                        |

| 6        | TOFF            | 0   | Track jump signal output                       |

| 7        | TGL             | 0   | Track jump signal output                       |

| 8        | JP +            | 0   | Track jump signal output                       |

| 9        | JP –            | 0   | Track jump signal output                       |

| 10       | MAD3            | 0   | DRAM address output                            |

| 11       | MAD2            | 0   | DRAM address output                            |

| 12       | MAD1            | 0   | DRAM address output                            |

| 13       | MADO            | 0   | DRAM address output                            |

| 14       | MAD9            | - 0 | DRAM address output                            |

| 15       | MAD10           | 0   | DRAM address output                            |

| 16       | MAD11           | 0   | DRAM address output                            |

| 17       | V <sub>SS</sub> | -   | Ground                                         |

| 18       | MRAS            | 0   | DRAM RAS signal output                         |

| 19       | MILLES          | 0   | DRAM WE signal output                          |

| 20       | MD1             | 1/0 | DRAM data VO                                   |

| 20       | MD1             | 1/0 | DRAM data VO                                   |

| 21       | MD3             | 1/0 | DRAM data VO                                   |

| 22       | MD3             | 1/0 | DRAM data VO                                   |

|          | MCAS            |     | DRAM CAS signal output                         |

| 24<br>25 | MOAS            | 0   | · · · ·                                        |

|          |                 | 0   | DRAM OE signal output                          |

| 26       | MAD8            | 0   | DRAM address output                            |

| 27       | MAD7            | 0   | DRAM address output                            |

| 28       | MAD6            | 0   | DRAM address output                            |

| 29       | MAD5            | 0   | DRAM address output                            |

| 30       | MAD4            | 0   | DRAM address output                            |

| 31       | SUBDO0          | 0   | Subdata and internal status output             |

| 32       | SUBDO1          | 0   | Subdata and internal status output             |

| 33       | SUBDO2          | 0   | Subdata and internal status output             |

| 34       | SUBDO3          | 0   | Subdata and internal status output             |

| 35       | SUBDO4          | 0   | Subdata and internal status output             |

| 36       | SUBDO5          | 0   | Subdata and internal status output             |

| 37       | SUBDO6          | 0   | Subdata and internal status output             |

| 38       | SUBDO7          | 0   | Subdata and internal status output             |

| 39       | 16M             | 0   | 16.9344 MHz clock output                       |

| 40       | V <sub>SS</sub> |     | V <sub>SS</sub> ground                         |

| 41       | V <sub>DD</sub> | —   | Power supply                                   |

| 42       | XIN             | 1   | 16.9344 oscillator input                       |

| 43       | XOUT            | 0   | 16.9344 oscillator output                      |

| 44       | SUBREO          | 1   | Subdata request signal input                   |

| 45       | SUBWR           | 0   | Subdata transfer clock output                  |

| 46       | SUBDTC          | 0   | Subdata transfer complete signal output        |

| 47       | SUBDEN          | 0   | Subdata enable output                          |

| 48       | TEST5           | 1   | Test input (normally tied to V <sub>DD</sub> ) |

| 49       | TEST4           | 1   | Test input (normally tied to V <sub>DD</sub> ) |

| 50       | TEST3           | 1   | Test input (normally tied to V <sub>DD</sub> ) |

| 51       | TESTO           | 1   | Test output                                    |

| 52       | SD0             | 0   | Sound block data output                        |

| 53       | SD1             | Ó   | Sound block data output                        |

| 54       | SD2             | 0   | Sound block data output                        |

|          |                 |     |                                                |

.

Continued on next page.

Continued from preceding page.

| Ріл No, | Symbol          | l vo | Function                                         |

|---------|-----------------|------|--------------------------------------------------|

| 56      | SD4             | 0    | Sound block data output                          |

| 57      | SD5             |      | Sound block data output                          |

| 58      | SD6             | 0    | Sound block data output                          |

| 59      | SD7             | 0    | Sound block data output                          |

| 60      | SWR             | 0    | Sound block data transfer clock output           |

| 61      | SACK            | 0    | Sound block data acknowledge signal output       |

| 62      | SEPF            | 0    | Sound block data empty signal output             |

| 63      | SREQ            |      | Sound block data request signal input            |

| 64      | CL              | 1    | CPU interface data transfer clock input          |

| 65      | CE              | 1    | CPU interface chip enable signal input           |

| 66      | DI              | 1    | CPU Interface data input                         |

| 67      | DO              | 0    | CPU interface data output                        |

| 68      | WRQ             | 0    | CPU interface interrupt signal output            |

| 69      | INT             | 0    | CPU interface interrupt signal output            |

| 70      | RESET           | 1    | System reset                                     |

| 71      | ССВ             | 1    | CPU interface type switching input               |

| 72      | SYNCOK          | 0    | Sector synchronization detection signal output   |

| 73      | EMONT           | 0    | Error detection monitor signal output            |

| 74      | EMON0           | 0    | Error detection monitor signal output            |

| 75      | EMON1           | 0    | Error detection monitor signal output            |

| 76      | PCK             | 0    | 4.3218 MHz monitor signal output                 |

| 77      | FSEQ            | 0    | Frame synchronization detection signal output    |

| 78      | V <sub>SS</sub> | _    | Ground (for the on-chip DRAM only)               |

| 79      | ADIPSYN         | 0    | ADIP synchronization timing signal output        |

| 80      | ADIPCRC         | 0    | ADIP data CRC flag output                        |

| 81      | PULLSW          | 1 1  | Internal pull-up resistor switching signal input |

| 82      | SBSW            |      | Subdata/internal status switching signal input   |

| 83      | V <sub>DD</sub> | -    | Power supply (for the on-chip DRAM only)         |

| 84      | 4.2M            |      | Test input (normally tied to V <sub>DD</sub> )   |

| 85      | TEST2           | 1    | Test input (normally tied to V <sub>DD</sub> )   |

| 86      | PREPIT          | 1    | CLV servo output signal switching input          |

| 87      | EFMI            | 1    | HF signal input                                  |

| 88      | EFMO            | 0    | EFM signal output                                |

| 89      | V <sub>DD</sub> | -    | Power supply                                     |

| 90      | V <sub>SS</sub> |      | Ground                                           |

| 91      | ADIPCRI         |      | ADIP carrier signal input                        |

| 92      | BICLK           | 1    | Bi-phase data transfer clock input               |

| 93      | BIDATAI         |      | Bi-phase data input                              |

| 94      | HFL             | Ĩ    | Track detection signal input                     |

| 95      | TEST1           | 0    | 4.2336 MHz output                                |

| 96      | AO              | 0    | VCO control signal output                        |

| 97      | AI              |      | VCO control signal input                         |

| 98      | V <sub>SS</sub> | 0    | VCO control signal output                        |

| 99      | PDO             | —    | Ground                                           |

| 100     | MON             | 0    | CLV servo signal output                          |

•

No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of August, 1995. Specifications and information herein are subject to change without notice.