# LC89086M

## 8 Bit A/D Converter

# **Preliminary**

### Overview

The LC89086M is a low-power high-speed 8-bit serial-parallel A/D converter fabricated in a high-speed CMOS process.

### **Features**

• Resolution: 8 bits (with an overflow output)

• Maximum conversion rate: 20M samples per second

• Error: Less than ±1.0 LSB

• Power supply: +5-V single-voltage power supply

Power dissipation: 150 mW (typical)

Analog input voltage range: V<sub>SS</sub> to V<sub>DD</sub>

Digital output voltage: 3 state TTL level

# **Package Dimensions**

unit: mm

#### 3155-MFP24

## **Specifications**

Absolute Maximum Ratings at  $Ta = 25^{\circ}C$ ,  $DV_{SS} = AV_{SS} = 0$  V

| Parameter              | Symbol              | Conditions | Ratings                      | Unit |

|------------------------|---------------------|------------|------------------------------|------|

| Maximum supply voltage | V <sub>DD</sub> max |            | -0.3 to +7.0                 | V    |

| Input voltage          | V <sub>IN</sub> max |            | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Operating temperature  | Topr                |            | -30 to +70                   | ℃    |

| Storage temperature    | Tstg                |            | -40 to +125                  | ∞    |

### **Recommended Operating Conditions**

| Parameter                     | Symbol          | Conditions - |     | Unit |     |       |

|-------------------------------|-----------------|--------------|-----|------|-----|-------|

| raidilletei                   | Symbol          |              | min | typ  | max | Offic |

| Supply voltage                | V <sub>DD</sub> |              | 4.5 | 5.0  | 5.5 | V     |

| Operating ambient temperature | Та              |              | -30 |      | +70 | °C    |

### LC89086M

# **Electrical Characteristics**

# Electrical DC Characteristics at $Ta=-30~to~+70^{\circ}C,\,AV_{DD}=DV_{DD}=4.5~to~5.5~V,\,AV_{SS}=DV_{SS}=0~V$

| Developer                           | Currelle el       | Conditions                                                                                     |              | - Unit |                      |       |  |

|-------------------------------------|-------------------|------------------------------------------------------------------------------------------------|--------------|--------|----------------------|-------|--|

| Parameter                           | Symbol Conditions |                                                                                                | min          | typ    | max                  | Offic |  |

| Reference resistance                | Rref              | VrefH (pin 5) – VrefL (pin 8)                                                                  | 210          | 300    | 390                  | Ω     |  |

| Analog input capacitance            | C <sub>AIN</sub>  |                                                                                                |              | 30     |                      | pF    |  |

| Analog input resistance             | R <sub>AIN</sub>  |                                                                                                |              | 10     |                      | ΜΩ    |  |

| Reference high-level input voltage  | VrefH             | When VrefHO (pin 4) and VrefLO (pin 9) are unused.                                             | Vref L + 2.0 |        | V <sub>DD</sub>      | V     |  |

| Reference low-level input voltage   | VrefL             | When VrefHO (pin 4) and VrefLO (pin 9) are unuse                                               | d. 0         |        | VrefH-2.0            | V     |  |

| Reference high-level output voltage | VrefH             | When VrefHO (pin 4) and VrefLO (pin 9) are used, and AV <sub>DD</sub> = DV <sub>DD</sub> = 5 V | 1.9          | 2.0    | 2.1                  | V     |  |

| Reference low-level output voltage  | VrefL             | When VrefHO (pin 4) and VrefLO (pin 9) are used, and AV <sub>DD</sub> = DV <sub>DD</sub> = 5 V | -0.05        | 0      | +0.05                | V     |  |

| Analog input voltage                |                   |                                                                                                | VrefL        |        | VrefH                | V     |  |

| Digital high-level voltage          | V <sub>IH</sub>   |                                                                                                | 2.2          |        | V <sub>DD</sub> +0.3 | V     |  |

| Digital low-level voltage           | V <sub>IL</sub>   |                                                                                                | -0.3         |        | +0.8                 | V     |  |

| Digital high-level output current   | I <sub>OH</sub>   | $V_{OH} = V_{DD} - 0.4 \text{ V}$                                                              | -2           |        |                      | mA    |  |

| Digital low-level output current    | l <sub>OL</sub>   | V <sub>OL</sub> = 0.4 V                                                                        | 2            |        |                      | mA    |  |

# Electrical AC Characteristics 1 at $Ta=-30~to~+70^{\circ}C,~AV_{DD}=DV_{DD}=4.5~to~5.5~V,~AV_{SS}=DV_{SS}=0~V$

| Parameter                        | Course In a l   | Conditions     | Ratings |     |     |      |

|----------------------------------|-----------------|----------------|---------|-----|-----|------|

|                                  | Symbol          | Conditions     | min     | typ | max | Unit |

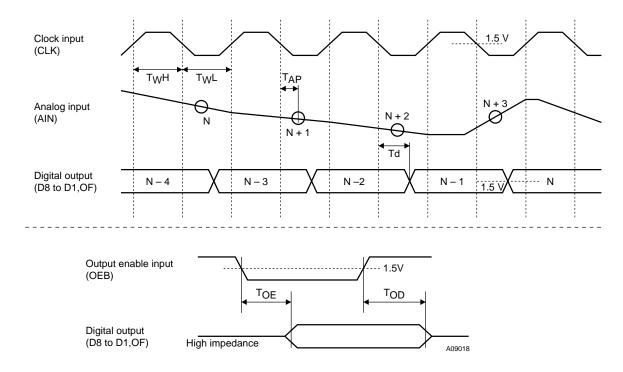

| Clock high-level period          | T <sub>WH</sub> |                | 23      |     |     | ns   |

| Clock low-level period           | T <sub>WL</sub> |                | 23      |     |     | ns   |

| Analog input acquisition time    | T <sub>AP</sub> |                | 10      | 20  | 30  | ns   |

| Digital output data delay time   | Td              | C load = 30 pF | 15      | 30  | 45  | ns   |

| Digital output data enable time  | T <sub>OE</sub> | C load = 30 pF | 2       | 5   | 10  | ns   |

| Digital output data disable time | T <sub>OD</sub> | C load = 30 pF | 2       | 5   | 10  | ns   |

## **Timing Chart**

The analog signal (AIN) is acquired on the falling edge of the clock input (CLK). The acquired analog signal is converted to a digital code and is output from the digital outputs (D8 to D1, OF) on the clock falling edge delayed three clock cycles from the clock cycle in which the analog signal was acquired.

## **Electrical AC Characteristics 2**

at Ta = 25°C,  $AV_{DD}$  =  $DV_{DD}$  = 5 V,  $AV_{SS}$  =  $DV_{SS}$  = 0 V, VrefH = 2 V, VrefL = 0 V

| Parameter                    | Symbol              | Conditions   |     | Unit |      |       |  |

|------------------------------|---------------------|--------------|-----|------|------|-------|--|

| Parameter                    | Symbol              | Conditions   | min | typ  | max  | Offic |  |

| Resolution                   | Res                 |              |     |      | 8    | bit   |  |

| Maximum conversion rate      | Fs                  |              |     |      | 20   | MSPS  |  |

| Linearity error              | LE                  | DC accuracy  |     |      | ±1.0 | LSB   |  |

| Differential linearity error | DLE                 | DC accuracy  |     |      | ±1.0 | LSB   |  |

| Offset voltage               | V <sub>offset</sub> | DC accuracy  | 10  | 50   | 90   | mV    |  |

| Power dissipation            | Pd                  | Fs = 20 MSPS |     | 150  | 220  | mW    |  |

Note: Test circuits must conform to the sample application circuit.

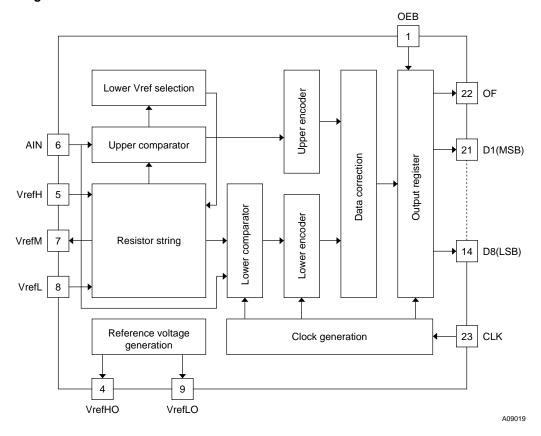

# **Block Diagram**

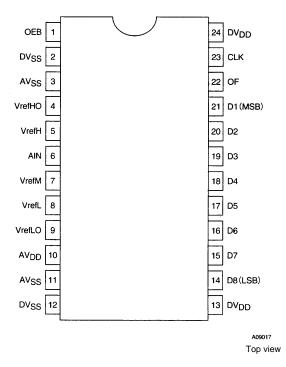

# **Pin Assignment**

### LC89086M

## **Pin Functions**

| Pin No. | Pin name         | I/O | Function                                                                                                                                                                                       |

|---------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | OEB              | I   | Digital output enable input High: high-impedance Low: Normal operation                                                                                                                         |

| 2       | DV <sub>SS</sub> |     | Digital ground                                                                                                                                                                                 |

| 3       | AV <sub>SS</sub> |     | Analog ground                                                                                                                                                                                  |

| 4       | Vref HO          | 0   | Internal reference voltage (high) generation. Shorting this pin to VrefH (pin 5) generates a voltage of 2.0 V. This pin must be left open when the internally generated potential is not used. |

| 5       | Vref H           | I   | Reference voltage input (high)                                                                                                                                                                 |

| 6       | AIN              | I   | Analog input                                                                                                                                                                                   |

| 7       | Vref M           | 0   | Reference voltage intermediate level tap.                                                                                                                                                      |

| 8       | Vref L           | I   | Reference voltage input (low)                                                                                                                                                                  |

| 9       | Vref LO          | 0   | Internal reference voltage (low) generation. Shorting this pin to VrefL (pin 8) generates a voltage of 0 V. This pin must be left open when the internally generated potential is not used.    |

| 10      | $AV_{DD}$        |     | Analog power supply                                                                                                                                                                            |

| 11      | AV <sub>SS</sub> |     | Analog ground                                                                                                                                                                                  |

| 12      | $DV_SS$          |     | Digital ground                                                                                                                                                                                 |

| 13      | $DV_DD$          |     | Digital power supply                                                                                                                                                                           |

| 14      | D8               | 0   | Digital output (LSB)                                                                                                                                                                           |

| 15      | D7               | 0   | Digital output                                                                                                                                                                                 |

| 16      | D6               | 0   | Digital output                                                                                                                                                                                 |

| 17      | D5               | 0   | Digital output                                                                                                                                                                                 |

| 18      | D4               | 0   | Digital output                                                                                                                                                                                 |

| 19      | D3               | 0   | Digital output                                                                                                                                                                                 |

| 20      | D2               | 0   | Digital output                                                                                                                                                                                 |

| 21      | D1               | 0   | Digital output (MSB)                                                                                                                                                                           |

| 22      | OF               | 0   | Digital output (Overflow)                                                                                                                                                                      |

| 23      | CLK              | ı   | Clock input                                                                                                                                                                                    |

| 24      | $DV_DD$          |     | Digital power supply                                                                                                                                                                           |

Note: There must be no potential difference between the digital system and analog system  $V_{DD}$  and  $V_{SS}$  power supply potentials.

### I/O Code Table

The table below lists the relationship between the input and output when VrefH and VrefL are set up so that the zero transient voltage is 0.000~V and the full-scale transient voltage is 2.008V.

| Analog input         | Digital output |    |    |    |    |    |    |    |    |

|----------------------|----------------|----|----|----|----|----|----|----|----|

| V <sub>AIN</sub> (V) | OF             | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 |

| Up to 0.000          | 0              | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Up to 0.008          | 0              | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Up to 0.016          | 0              | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| Up to 0.024          | 0              | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| Up to 0.032          | 0              | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| to                   |                |    |    |    |    |    |    |    |    |

| Up to 0.992          | 0              | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| Up to 1.000          | 0              | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| Up to 1.008          | 0              | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Up to 1.016          | 0              | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| to                   |                |    |    |    |    |    |    |    |    |

| Up to 1.992          | 0              | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  |

| Up to 2.000          | 0              | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| Up to 2.008          | 0              | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| Over 2.008           | 1              | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

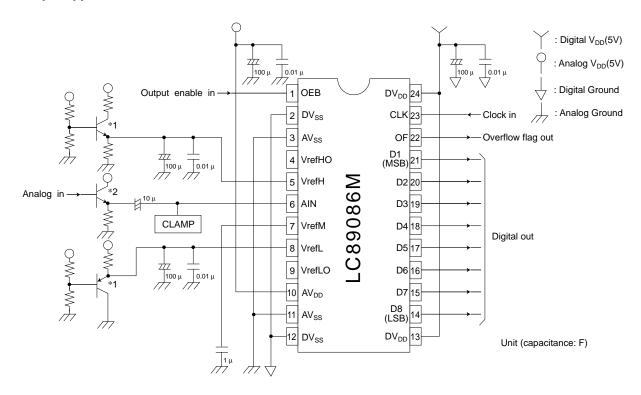

### Sample Application Circuit

Note 1. The value of the reference resistor is about 300 Ω. When this circuit is used with (VrefH – VrefL) = 2 V, a current of 6.7 mA will flow. Use an operational amplifier or emitter follower with at least this current capacity.

2. The analog input impedance is lower for AC inputs. Therefore, an operational amplifier or emitter follower with a high slew rate and a wide bandwidth must be used in the previous stage output, and the impedance must be reduced to under 100 Ω.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- 2 Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of October, 1997. Specifications and information herein are subject to change without notice.