# SANYO Semiconductors DATA SHEET

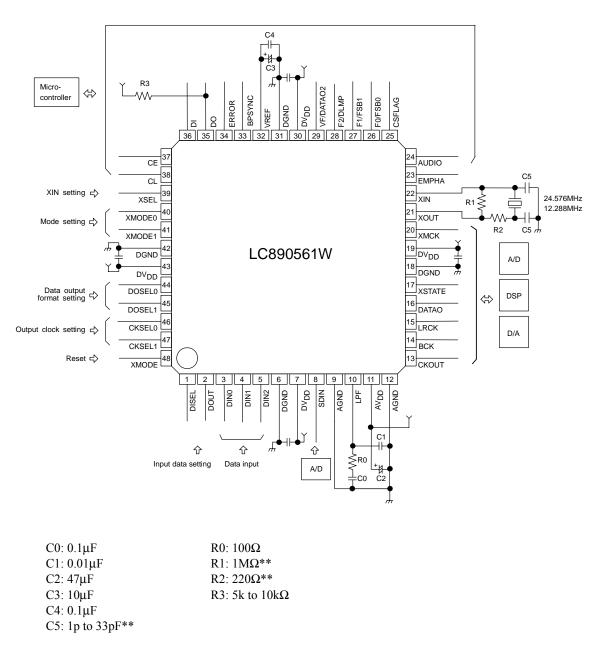

# CMOS IC LC890561W — Digital Audio Interface Receiver with Built-in Data Buffer Memory

# Overview

The LC890561W is an audio LSI that synchronizes with the input signal and demodulates the signal into the normal format signal during data transmission between digital audio devices via the IEC60958 and EIAJ CP-1201. It supports sampling frequencies of up to 192kHz. It is replaceable with the existing LC89056W by devising the mounting board. The LC890561W has a build-in data buffer memory that allows a lip synchronization function. It allows the audio data output to be delayed after demodulation.

The LC890561W is applicable to the reception of digital data transmission, such as AV amplifier, AV receiver and car audio.

#### 1. Features

- Built-in PLL circuit to synchronize with transferred input bi-phase signal.

- Built-in PLL error lock prevention circuit for accurate locking.

- Equipped with three S/PDIF data input pins that support TTL input port of 5V interface.

- Receives sampling frequencies of 32kHz to 192kHz.

- Outputs the following clocks: 512fs, 384fs, 256fs, 64fs and fs.

- Outputs the fs information of 32kHz, 44.1kHz, 48kHz, 88.2kHz, 96kHz 176.4kHz and 192kHz.

- Built-in oscillation amplifier: 24.57MHz or 12.28MHz

- Outputs transitional period signal where VCO clock and oscillation amplifier clock are switched.

- Outputs up to 24bits of data. Also supports 24bit I<sup>2</sup>S data.

- Built-in SRAM of 24576word × 24bit to allow delay of output data.

- Two types of data output pins to set delay or not delay of output data.

- Contains the pin that outputs the delay setting state of output data.

- Contains the output pin for bit 1 (Non-PCM data detection bit) of channel status.

- Outputs channel status emphasis information.

- Outputs update flag for first 48bits of channel status.

- Outputs synchronization signal for burst preambles Pa, Pb, Pc and Pd.

- Outputs validity flag.

- Switching of the serial audio input data and recovery data is possible.

- The delay setting of output data for serial audio data input is possible.

Continued on next page.

- Any and all SANYO Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO Semiconductor representative nearest you before using any SANYO Semiconductor products described or contained herein in such applications.

- SANYO Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor products described or contained herein.

#### SANYO Semiconductor Co., Ltd. TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

Continued from preceding page.

- Microcontroller interface enables various setting and outputs.

- -Clock control.

- -Digital/analog source signal switching.

- -Selection of data input pin.

- -Selection of data output format.

- -Error flag selection.

- -Lock range setting of input data.

- -PLL error flag, input fs calculation result and first 48bits of channel status output.

- -16bit Non-PCM burst preamble Pc data output.

- 3.3V single source power supply. (Built-in 1.8V output regulator, 5V TTL interface is possible.)

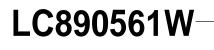

- Package: SQFP-48

# 2. Package Dimensions

unit : mm

3163B

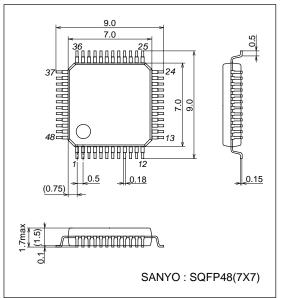

# 3. Pin Assignment

Figure 3.1 LC890561W Pin Assignment

# 4. Pin Functions

| Pin No. | Pin Name | I/O            | Function                                                                                                 |

|---------|----------|----------------|----------------------------------------------------------------------------------------------------------|

| 1       | DISEL    | I <sub>5</sub> | Selection input pin of data input pin (DIN0, DIN1)                                                       |

| 2       | DOUT     | 0              | Input bi-phase data through output pin                                                                   |

| 3       | DIN0     | I <sub>5</sub> | Input pin of TTL-compatible digital data (Pull-down resistor internal)                                   |

| 4       | DIN1     | I <sub>5</sub> | Input pin of TTL-compatible digital data (Pull-down resistor internal)                                   |

| 5       | DIN2     | I <sub>5</sub> | Input pin of TTL-compatible digital data (Pull-down resistor internal)                                   |

| 6       | DGND     | -              | Digital GND                                                                                              |

| 7       | DVDD     | -              | Digital power supply (3.3V)                                                                              |

| 8       | SDIN     | I <sub>5</sub> | Input pin of TTL-compatible serial audio data                                                            |

| 9       | AGND     | I              | Analog GND for PLL                                                                                       |

| 10      | LPF      | 0              | PLL loop filter setting pin                                                                              |

| 11      | AVDD     | -              | Analog power supply for PLL (3.3V)                                                                       |

| 12      | AGND     | -              | Analog GND for PLL                                                                                       |

| 13      | CKOUT    | 0              | Clock output pin (256fs, 384fs, 512fs, crystal oscillation, VCO free-running oscillation)                |

| 14      | BCK      | 0              | 64fs clock output pin                                                                                    |

| 15      | LRCK     | 0              | Fs clock output pin (L = R-ch, H = L-ch, inverted at $I^2S$ )                                            |

| 16      | DATAO    | 0              | Post-demodulation audio data output pin (Delay function is possible)                                     |

| 17      | XSTATE   | 0              | Source clock switch monitor output pin                                                                   |

| 18      | DGND     | -              | Digital GND                                                                                              |

| 19      | DVDD     | -              | Digital power supply (3.3V)                                                                              |

| 20      | XMCK     | 0              | Crystal oscillation clock output pin (24.576MHz or 12.288MHz)                                            |

| 21      | XOUT     | 0              | Crystal oscillation connection output pin                                                                |

| 22      | XIN      | 1              | Crystal oscillation input pin, external input supported (24.576MHz or 12.288MHz)                         |

| 23      | EMPHA    | 0              | Channel status emphasis information output pin                                                           |

| 24      | AUDIO    | 0              | Channel status bit 1 (non-PCM data detection bit) output pin                                             |

| 25      | CSFLAG   | 0              | Update flag output pin of first 48bits of channel status                                                 |

| 26      | F0/FSB0  | 0              | Input fs calculation signal output pin    Input fs calculation signal arrange frequency bands output pin |

| 27      | F1/FSB1  | 0              | Input fs calculation signal output pin    Input fs calculation signal arrange frequency bands output pin |

Table 4.1 Pin Functions

Continued on next page.

| Pin No. | Name      | I/O            | Function                                                                                   |  |

|---------|-----------|----------------|--------------------------------------------------------------------------------------------|--|

| 28      | F2/DLMP   | 0              | Input fs calculation signal output pin    Output data delay mute period monitor output pin |  |

| 29      | VF/DATAO2 | 0              | Validity flag output pin/Data output pin (Delay is impossible)                             |  |

| 30      | DVDD      | -              | Digital power supply (3.3V)                                                                |  |

| 31      | DGND      | -              | Digital GND                                                                                |  |

| 32      | VREF      | 0              | Regulator monitor output pin (1.8V)                                                        |  |

| 33      | BPSYNC    | 0              | Non-PCM burst preamble Pa, Pb, Pc, Pd sync signal output pin                               |  |

| 34      | ERROR     | 0              | PLL lock error or data error flag output pin                                               |  |

| 35      | DO        | 05             | Microcontroller I/F, read data output pin                                                  |  |

| 36      | DI        | I <sub>5</sub> | Microcontroller I/F, write data input pin                                                  |  |

| 37      | CE        | I5             | Microcontroller I/F, chip enable input pin                                                 |  |

| 38      | CL        | I <sub>5</sub> | Microcontroller I/F, clock input pin                                                       |  |

| 39      | XSEL      | I <sub>5</sub> | [XIN] crystal oscillation selection input pin (24.576MHz or 12.288MHz)                     |  |

| 40      | MODE0     | I <sub>5</sub> | Mode setting input pin                                                                     |  |

| 41      | MODE1     | I <sub>5</sub> | Mode setting input pin                                                                     |  |

| 42      | DGND      | -              | Digital GND                                                                                |  |

| 43      | DVDD      | -              | Digital power supply (3.3V)                                                                |  |

| 44      | DOSEL0    | I <sub>5</sub> | Output data format selection input pin                                                     |  |

| 45      | DOSEL1    | I <sub>5</sub> | Output data format selection input pin                                                     |  |

| 46      | CKSEL0    | I <sub>5</sub> | Output clock selection input pin                                                           |  |

| 47      | CKSEL1    | I <sub>5</sub> | Output clock selection input pin                                                           |  |

| 48      | XMODE     | 15             | System reset input pin                                                                     |  |

Note:

\* Withstand voltage input/output: I or O = -0.3 to 3.6V, I5 or  $O_5 = -0.3$  to 5.5V

\* To prevent logic circuit latch-up, digital power supply and analog power supply must be applied or removed simultaneously and with the same potential.

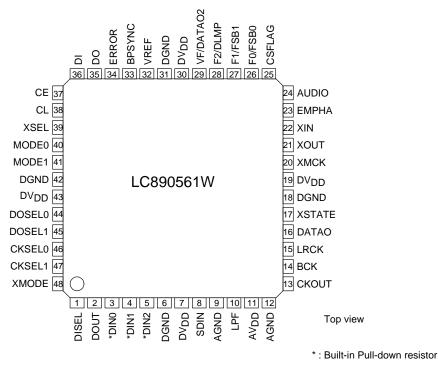

# 5. Block Diagram

Figure 5.1 LC890561W Block Diagram

# 6. Electrical Characteristics

#### 6.1 Absolute Maximum Ratings

| Parameter                     | Symbol                | Conditions | Ratings                                 | Unit |

|-------------------------------|-----------------------|------------|-----------------------------------------|------|

| Maximum Supply Voltage        | V <sub>DD</sub> 33max | 6-1-1      | -0.3 to 3.96                            | V    |

| Input Voltage 1               | V <sub>I</sub> 1      | 6-1-2      | -0.3 to V <sub>DD</sub> +0.3 (max.3.96) | V    |

| Input Voltage 2               | V <sub>l</sub> 2      | 6-1-3      | -0.3 to 5.5                             | V    |

| Output Voltage                | Vo                    |            | -0.3 to V <sub>DD</sub> +0.3 (max.3.96) | V    |

| Storage Ambient Temperature   | Tstg                  |            | -55 to 125                              | °C   |

| Operating Ambient Temperature | Topr                  |            | -30 to 70                               | °C   |

| Maximum Input/Output Current  | IN, OUT               | 6-1-4      | ±20                                     | mA   |

Table 6.1 Absolute Maximum Ratings at AGND = DGND = 0V

6-1-1: DVDD and AVDD pins

6-1-2: DISEL, XIN, XSEL, MODE0, MODE1, DOSEL0, DOSEL1, CKSEL0 and CKSEL1 input pins

6-1-3: DIN0, DIN1, DIN2, SDIN, DI, CE, CL and XMODE input pins

6-1-4: Per input/output pin

#### **6.2 Recommended Operating Conditions**

| Parameter             | Quarter            | Conditions |     | Unit |                                     |      |

|-----------------------|--------------------|------------|-----|------|-------------------------------------|------|

| Parameter             | Symbol             | Conditions | min | typ  | max                                 | Unit |

| Supply Voltage        | V <sub>DD</sub> 33 | 6-2-2      | 3.0 | 3.3  | 3.6                                 |      |

| Input Voltage Range 1 | V <sub>IN</sub> 1  | 6-2-3      | 0   |      | AV <sub>DD</sub> , DV <sub>DD</sub> | V    |

| Input Voltage Range 2 | V <sub>IN</sub> 2  | 6-2-4      | 0   |      | 5.5                                 | V    |

| Operating Temperature | Vopr               |            | -30 |      | 70                                  | °C   |

| ruche chi internation optiming containents arrierab berab | Table 6.2 Recommended Or | erating Conditi  | ions at $AGND = DGND = 0V$ |

|-----------------------------------------------------------|--------------------------|------------------|----------------------------|

|                                                           | ruble 0.2 recommended op | oracing contaits |                            |

6-2-1: DV<sub>DD</sub> and AV<sub>DD</sub> pins

6-2-2: DISEL, XIN, XSEL, MODE0, MODE1, DOSEL0, DOSEL1, CKSEL0 and CKSEL1 input pins

6-2-3: DN0, DIN1, DIN2, SDIN, DI, CE, CL and XMODE input pins

#### 6.3 DC Characteristics

| Table 6.3 DC Characteristics at Ta = -30 to 70°C, $AV_{DD} = DV_{DD} = 3.0$ to 3.6V, $AGND = DGND = 0V$ |

|---------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------|

| Deventer            | Cumhal          | Conditions | Ratings               |     |                     |      |

|---------------------|-----------------|------------|-----------------------|-----|---------------------|------|

| Parameter           | Symbol          |            | min                   | typ | max                 | Unit |

| Input, High         | ∨ <sub>IH</sub> | 6-3-1      | 2.0                   |     |                     | V    |

| Input, Low          | VIL             | 0-3-1      |                       |     | 0.3DV <sub>DD</sub> | V    |

| Input, High         | VIH             | 6-3-2      | 2.0                   |     |                     | V    |

| Input, Low          | VIL             |            |                       |     | 0.8                 | V    |

| Input, High         | ∨ <sub>IH</sub> |            | 2.0                   |     |                     | V    |

| Input, Low          | VIL             | 6-3-3      |                       |     | 0.8                 | V    |

| Output, High        | VOH             | 6-3-4      | DV <sub>DD</sub> -0.4 |     |                     | V    |

| Output, Low         | V <sub>OL</sub> | 6-3-4      |                       |     | 0.4                 | V    |

| Consumption Current | IDD             | 6-3-5      |                       | 20  | 40                  | mA   |

| Pull-Down Resistor  | DDN             | 6-3-6      | 45                    | 90  | 180                 | kΩ   |

6-3-1: CMOS level: DISEL, XIN, XSEL, MODE0, MODE1, DOSEL0, DOSEL1, CKSEL0 and CKSEL1 input pins

6-3-2: TTL level: DIN0, DIN1, DIN2 and SDIN input pins

6-3-3: TTL Schmidt level: DI, CE, CL and XMODE input pins

6-3-4:  $I_{OH} = -12mA$ ,  $I_{OL} = 12mA$ : CKOUT output pins

I<sub>OH</sub> = -8mA, I<sub>OL</sub> = 8mA: DOUT, XOUT and XMCK output pins

$I_{OH}$  = -4mA,  $I_{OL}$  = 4mA: BCK, LRCK, DATAO, VF/DATAO2 and F2/DLMP output pins

$I_{OH} = -2mA$ ,  $I_{OL} = 2mA$ : output pins other than those listed above

6-3-5: Ta =  $25^{\circ}$ C, input data fs = 96kHz

6-3-6: DIN0, DIN1 and DIN2 input pins

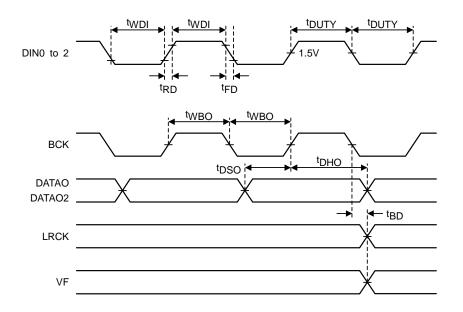

# 6.4 AC Characteristics

|                                 | Symbol                            | Conditions | Ratings |         |     | Linit |

|---------------------------------|-----------------------------------|------------|---------|---------|-----|-------|

| Parameter                       |                                   | Conditions | min     | typ     | max | Unit  |

| DIN* Rising/Falling Edge Period | <sup>t</sup> Rd <sup>, t</sup> FD |            |         |         | 15  | ns    |

| DIN* Data Pulse Width           | <sup>t</sup> WDI                  |            | 20      |         |     | ns    |

| DIN* Duty                       | <sup>t</sup> DUTY                 | 6-4-1      | 40      |         | 60  | %     |

| XIN Crystal Resonator Frequency | f <sub>XT</sub> 0                 | 6-4-2      |         | 24.576  |     | MHz   |

| XIN Crystal Resonator Frequency | f <sub>XT</sub> 1                 | 6-4-3      |         | 12.288  |     | MHz   |

| XIN Crystal Resonator Frequency | f <sub>XT</sub> 2                 | 6-4-4      | 12      |         | 25  | MHz   |

| XMCK Output Clock               | fXO                               |            | 6       |         | 25  | MHz   |

| VCO Free-Running Frequency      | fVCO                              | 6-4-5      | 1       |         | 100 | MHz   |

| CKOUT Output Clock Frequency    | <sup>f</sup> MCK                  |            | 1       |         | 100 | MHz   |

| CKOUT Duty                      | <sup>t</sup> DUTY                 |            |         | 50      |     | %     |

| BCK Output Pulse Width          | <sup>t</sup> WBO                  |            |         | 1/128fs |     | ns    |

| Output Data Setup Time          | <sup>t</sup> DSO                  | 6-4-6      |         | 1/256fs |     | ns    |

| Output Data Hold Time           | <sup>t</sup> DHO                  |            |         | 1/256fs |     | ns    |

| Output Delay                    | <sup>t</sup> BD                   |            | -10     | 0       | 10  | ns    |

6-4-1: DIN\* = 1 setting, at 1/2 DVDD

6-4-2: XSEL = 0 (Except MODE0 = 1 and MODE1 = 1 setup)

6-4-3: XSEL = 1 (Except MODE0 = 1 and MODE1 = 1 setup)

6-4-4: XSEL = 1 (MODE0 = 1 and MODE1 = 1 setup)

6-4-5: Ta = 25°C,  $DV_{DD}$  =  $AV_{DD}$  = 3.3V (At the time of recommendation circuit setup)

6-4-6: fs = input sampling frequency

Figure 6.1 AC Characteristics

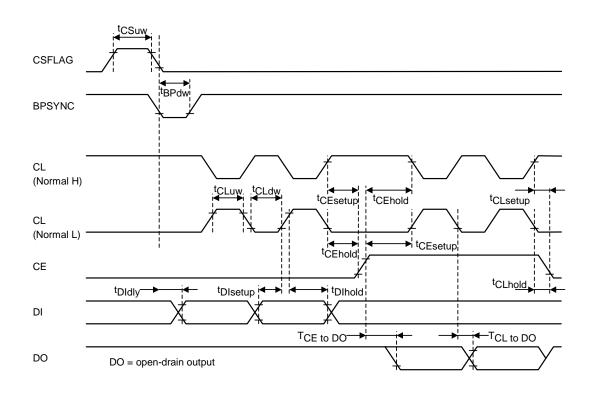

### 6.5 Microcontroller Interface AC Characteristics

| Devenuetor               | Symbol                | O an alliliana | Ratings |      |     | L la it |

|--------------------------|-----------------------|----------------|---------|------|-----|---------|

| Parameter                |                       | Conditions     | min     | typ  | max | Unit    |

| CSFLAG Pulse Width, High | t <sub>CS</sub> uw    | 6-5-1          | 1       |      |     | ms      |

| BPSYNC Pulse Width, Low  | t <sub>BP</sub> dw    | 6-5-2          |         | 41.7 |     | μs      |

| CL Pulse Width, Low      | t <sub>CL</sub> dw    |                | 100     |      |     | ns      |

| CL Pulse Width, High     | t <sub>CL</sub> uw    |                | 100     |      |     | ns      |

| CL-CE Setup Time         | t <sub>CL</sub> setup |                | 50      |      |     | ns      |

| CL-CE Hold Time          | tCEhold               |                | 50      |      |     | ns      |

| CL-DI Setup Time         | t <sub>DI</sub> setup |                | 50      |      |     | ns      |

| CL-DE Hold Time          | t <sub>DI</sub> hold  |                | 50      |      |     | ns      |

| CL-CE Setup Time         | t <sub>CL</sub> setup |                | 50      |      |     | ns      |

| CL-CE Hold Time          | tCLhold               |                | 50      |      |     | ns      |

| CL-DO Delay Time         | t <sub>CL</sub> to DO | 0.5.0          |         |      | *   | ns      |

| CE-DO Delay Time         | t <sub>CE</sub> to DO | 6-5-3          |         |      | *   | ns      |

| DI Delay Time            | <sup>t</sup> Dldly    |                |         | 0    |     | s       |

6-5-1: fs = 32kHz to 192kHz

6-5-2: fs = 48kHz

6-5-3: With a capacitance of 10pF and a  $10k\Omega$  pull-up resistor connected, the delay time is up to 150ns max. for the rising edge and up to 50ns max. for the falling edge.

Figure 6.2 Microcontroller Interface AC Characteristics

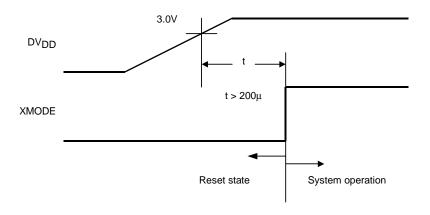

# 7. System Reset (XMODE)

- The system operates normally when XMODE pin is set to high level after 3.0V or higher supply voltage is applied.

- After power-on, the system is reset by setting XMODE to low again.

- Make sure to reset the system after turning on the power.

Figure 7.1 Reset Timing Chart

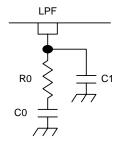

# 8. PLL (LPF)

- It has a build-in VCO (Voltage Controlled Oscillator) and synchronizes with sampling frequencies of 32kHz, 44.1kHz, 48kHz, 88.2kHz, 96kHz, 176.4kHz and 192kHz.

- The lock judgment of PLL is performed by detection of preamble B, M and W.

- The lock frequency of PLL is selected by CKSEL0 and CKSEL1. However, only 256fs is selectable on the system which input sampling frequency is over 96kHz. The proper PLL function to input over 96kHz will not be ensured when other frequency value is selected.

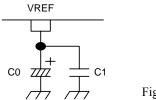

- LPF is pin for loop filter of PLL and connects resistor and capacitor as shown below.

| R0   | C0    | C1      |

|------|-------|---------|

| 220Ω | 0.1µF | 0.068µF |

Figure 8.1 Configuration of a Loop filter

# 9. Built-in Regulator (VREF)

- It has built-in regulator that can step down 3.3V to 1.8V in order to supply voltage into logic part.

- VREF is pin for voltage smoothing which can output regulator and connects the capacity as shown below.

| C0   | C1    |

|------|-------|

| 10µF | 0.1µF |

| Figure 9.1 | Composition | of the regulator | output |

|------------|-------------|------------------|--------|

# 10. Analog Source Mode

- The analog source mode is entered under the following conditions.

- -When the analog source mode is selected with the SMOD command.

- -When the input pin selected for data demodulation is no signal.

- In the analog source mode, the oscillation amplifier clock or the externally supplied clock are used.

- Each signal in the analog source mode is described below.

- -VCO holds the status of free-run oscillation when SMOD is set and also when no signal is input.

- -ERROR pin outputs high and DATAO pin outputs SDIN input data.

- -XSTATE pin outputs high after about 512\*LRCK(fs) (LRCK=48kHz or 96kHz) counts after XSTATE pin outputs low.

- -The clock set with XADC command is output from XMCK.

- -The output of BCK and LRCK are as follows.

| Tuble 10.1 Bell and Ellert outputs whit i mulog bourde |          |          |  |  |

|--------------------------------------------------------|----------|----------|--|--|

| XIN pin                                                | BCK pin  | LRCK pin |  |  |

| 12.288MHz                                              | 3.072MHz | 48kHz    |  |  |

| 24.576MHz                                              | 6.144MHz | 96kHz    |  |  |

| 12MHz to 25MHz                                         | XIN/4    | XIN/256  |  |  |

Table 10.1 BCK and LRCK Outputs with Analog Source

# 11. Setting of MODE0 and MODE1

• Selected operation mode with MODE0 and MODE1 terminals.

| Mode No.         MODE1 pin         MODE0 pin         Function |  |   |   | Ŭ              |

|---------------------------------------------------------------|--|---|---|----------------|

| 1                                                             |  | 0 | 0 | Normal mode    |

| 2                                                             |  | 0 | 1 | Fs free mode A |

| 3                                                             |  | 1 | 0 | Test mode      |

| 4                                                             |  | 1 | 1 | Fs free mode B |

T 11 11 10 W *.*.

(a) Mode1: Normal mode

-Input data fs of 32kHz to 192kHz is received only when CKOUT=256fs.

-The proper reception of data over 96kHz will not be ensured when other than 256fs is used for CKOUT output setting.

- (b) Mode2: Input fs free mode A (Terminal setting priority)

- -Restriction of input fs is canceled.

- -12.288MHz or 24.576MHz clock is supplied to XIN.

- -The receiving range of input data is based on a setup of CKOUT output.

- -Fs calculation of input data is performed in the possible range. ( $fs \pm 3$  to 4%)

- (c) Mode3: Test mode

- -Do not set this mode for the test.

- (d) Mode4: Input fs free mode B (Terminal setting priority)

- -Restriction of input fs is canceled.

- -12MHz to 25MHz arbitrary clock is supplied to XIN.

- -The reception range of input data is based on a setup of the CKOUT output.

- -Input fs is not calculated. In this case, all F0, F1 and F2 output low.

- -Output data delay after recovery processing cannot be set. However, the delay setting of the SDIN input data is possible.

- In the normal mode, when fs of input data is out of the reception setting range or the fs calculation range (*≠*target fs frequency  $\pm$  3 to 4%), ERROR is output high even if PLL is locked.

- In the input fs free mode, the reception range is set up without any restriction and fs calculation result is set so that it is not reflected in ERROR output. ERROR output will be set to low if PLL is locked.

# 12. Function

#### 12.1 Input Data (DIN0, DIN1, DIN2, DOUT, DISEL)

- DIN0, DIN1 and DIN2 are input pins that support TTL level inputs (5V tolerance).

- DIN0, DIN1 and DIN2 are grounded with the pull-down resistor when they are not selected.

- The input pin is selected with DISEL and the DIS[1:0] commands. (Command setting priority)

- With DISEL, it is selected from DIN0 or DIN1. With DIS[1:0], it is selected from DIN0, DIN1 or DIN2.

- DOUT performs through output the bi-phase data input to the selected data input pin. When, however, DOUT is not used, low fixed output setting is recommended in order to reduce the clock jitter.

| Table 12.1 Data Input Pin Selection |                             |  |

|-------------------------------------|-----------------------------|--|

| DISEL pin                           | Input pin to be demodulated |  |

| 0                                   | DIN0                        |  |

| 1                                   | DIN1                        |  |

#### 12.2 Input Data Reception Range

- The input data reception range can be extended and restricted with FSL0 and FSL1 commands, and CKSEL0 and CKSEL1 terminals. Also, the restriction can be canceled with MODE0 and MODE1.

- In the initial status at power ON, although sampling frequency of input data can be received up to 192kHz, sampling frequency of input data to be received can be restricted up to 48kHz or 96kHz. In this case, input data over this range results in an error and output data is muted.

- For information about these settings, see section "14. Microcontroller Interface".

#### 12.3 VCO and Oscillation Amplifier Clock (XIN, XOUT, XMCK, XSEL, XSTATE)

- The oscillation amplifier circuit is configured with XIN and XOUT. XIN accepts the input of the external clock.

- The clock generated with XIN and XOUT is used for the following purposes.

- -Clock for detection of data input

- -Clock for A/D converter in analog source mode

- -Clock for calculation of input sampling frequency

- -Clock for PLL error lock countermeasure

- The frequency required for XIN and XOUT is selected with XSEL. Normally the crystal resonator clock set here or external clock must be input. Moreover, make sure to connect a transducer to XIN and XOUT or supply a clock to XIN. (Normal input)

- In the case of setting the input fs free mode B, 12MHz to 25MHz arbitrary clock must be supplied to between XIN and XOUT. This case, XSEL must select the closer frequency of transducer to be connected.

| XSEL pin | Frequency |

|----------|-----------|

| 0        | 24.576MHz |

| 1        | 12.288MHz |

- Table 12.2 XIN Supply Frequency Selection

- XIN and XOUT are valid when PLL is unlocked, and oscillation amplifier clock or the divided clock of external input clock is output from the clock output pins.

- When the PLL is locked the oscillation amplifier is stopped so that it does not influence the VCO clock. The clock supplied to XIN is blocked in I/O block and the inside operates only with VCO clock. However, XIN and XOUT can also always be operated with the XCNT command. In this case, the XIN and XOUT clock is at risk of influencing the VCO clock.

- XMCK outputs the clock generated with oscillation amplifier of XIN and XOUT as a clock for A/D converter. The XMCK clock frequency is selected with the XADC command.

- When oscillation amplifier is set up for continues operation, XMCK can be stopped only during PLL is locked. It is set by the XCKS command. XCKS is for reducing clock interference to input and output buffer during the continuous operation of oscillation amplifier.

- Table 12.3 shows the status of the XIN, XOUT and XMCK pins when PLL is locked and unlocked.

| _ | Table 12.3 Status of Oscillation Amplifier Circuit when PLL Locked or Unlocked (XCNT = $0$ ) |                               |                             |  |

|---|----------------------------------------------------------------------------------------------|-------------------------------|-----------------------------|--|

|   | Pin name                                                                                     | Specified time after locked * | Unlocked status             |  |

| ſ | XIN                                                                                          | Input disabled                | Input enabled               |  |

|   | XOUT                                                                                         | н                             | XIN inverted clock output   |  |

|   | ХМСК                                                                                         | L                             | 1/1 or 1/2 XIN clock output |  |

\* Note: The specified time is the time from when PLL is locked until 8 preamble B is counted to eight. During this time, the input sampling frequency is calculated.

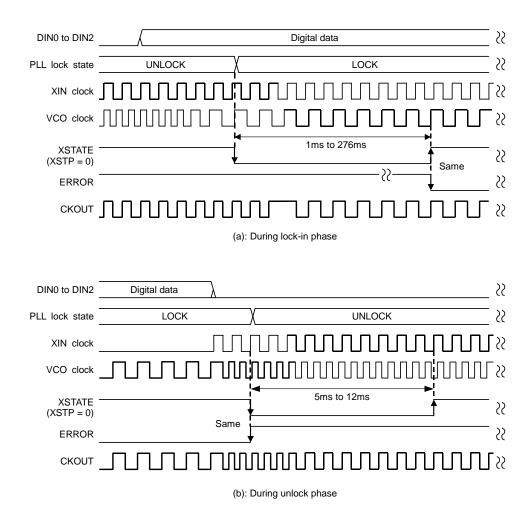

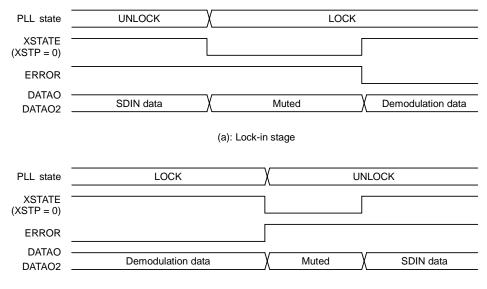

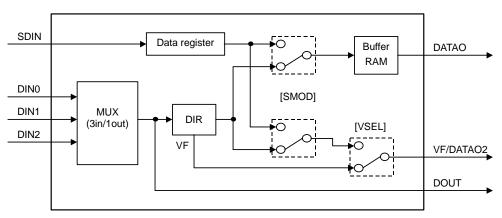

- XSTATE outputs low from the time PLL is locked until the ERROR goes low (lock-in stage), or from the time PLL is unlocked until the output clock is stabilized (unlock stage).

- L pulse width of XSTATE in lock-in process is a period from the PLL lock to the cancel of the ERROR. It is decided from the count value of Preamble B and sampling frequency of input data. For the ERROR output waiting time, see explanation of EWT[1:0] commands.

- L pulse width of XSTATE in unlock process is 512 count periods of fs clock which uses oscillation amplifier as a source clock. For example, when an oscillation amplifier clock is 12.288MHz, fs clock output from LRCK is set to 48kHz. In other words, about 10ms that counted this fs 512 times is L pulse width period. In addition, the time until the start of oscillator is required when the crystal oscillator is connected to oscillation amplifier. In this case, L pulse width is added during start-up time.

- For the XMCK output timing, see Figure 12.1.

- XSTATE outputs the low pulse, when change arises on the clocks. (when XSTP=0 setup)

- Also, the output polarity of XSATAE can be changed by the XSTP command.

- All functions of a VCO oscillation clock and an oscillation amplifier can be stopped by the STOP command. At this time, all output clock terminals serve as DC output.

## 12.4 Output Clock (CKOUT, BCK, LRCK)

• The CKOUT output clock is selected by setting CKSEL0 and CKSEL1 terminals.

| CKSEL1 pin | CKSEL0 pin | CKOUT pin      |  |  |

|------------|------------|----------------|--|--|

| 0          | 0          | 256fs output   |  |  |

| 0          | 1          | 384fs output   |  |  |

| 1          | 0          | 512fs output   |  |  |

| 1          | 1          | 512fs/2 output |  |  |

- 256fs must be chosen when receiving data over 96kHz as above table. There is no restriction of selection for data reception under 96kHz.

- 512fs/2 set PLL band as 512fs, and CKOUT clock outputs one half (256fs output).

- 64fs clock (64fs only) is outputted from BCK, and the fs clock is outputted from LRCK.

- When PLL is unlocked, the XIN and XOUT oscillation amplifier clock or the external input clock is output from CKOUT, and the divided clock of this clock is outputted from BCK and LRCK.

- Output of 1/2 CKOUT clock by CKDV command is possible.

- Reverse of the polarity of CKOUT clock by CKPO command is also possible.

- In the PLL lock and unlock phases, the CKOUT (BCK and LRCK likewise) clock switch timing is as follows.

Figure 12.1 Output Clock Switch Timing

#### 12.5 Serial Audio Data Input and Output

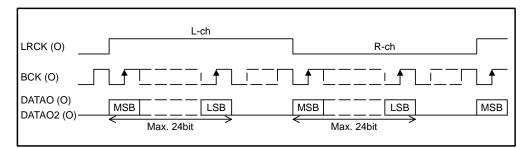

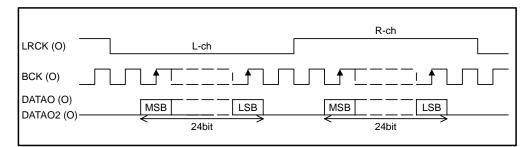

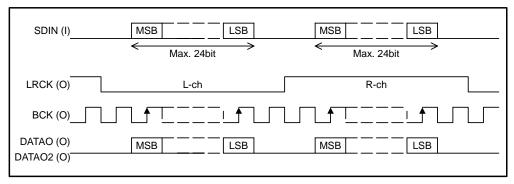

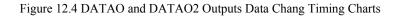

#### 12.5.1 Output Data Format (DATAO, DATAO2, DOSEL0, DOSEL1)

- DATAO and DATO2 output the digital data after demodulation. DATAO2 should be switched by the VSEL command since DATAO2 is sharing pin with validity flag output.

- The output data format is set with DOSEL0 and DOSEL1 terminals, or the DOSW command. The output data is 24bit I<sup>2</sup>S output when setup is DOSW=1. The setup of DOSW is given priority over DOSEL0 and DOSEL1.

| DOSEL1 pin | DOSEL0 pin | DATAO and DATAO2 pin                |

|------------|------------|-------------------------------------|

| 0          | 0          | (0) 24bit MSB-first left justified  |

| 0          | 1          | (1) 24bit MSB-first right justified |

| 1          | 0          | (2) 20bit MSB-first right justified |

| 1          | 1          | (3) 16bit MSB-first right justified |

Table 12.5 Data output format Selection (DOSW = 0)

• Data is output in synchronization with the falling edge of BCK from the edge of LRCK immediately after the ERROR flag goes low. However, this is the case that the delay setup is disabled (initial setting). When the delay setup is effective, DATAO is output after the delay time set. The delay setting is not applicable to DATA02. For information about these settings, see section "13. Output Data Delay Function".

(0): Setting with DOSEL0, DOSEL1

(1) (2) (3): Setting with DOSEL0, DOSEL1

(4): Setting with the DOSW command

Figure 12.2 Data Output Timing Charts

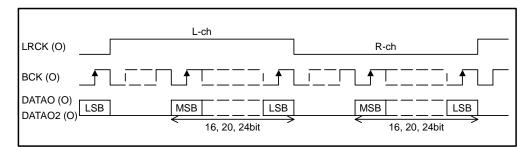

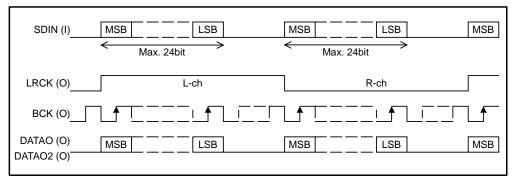

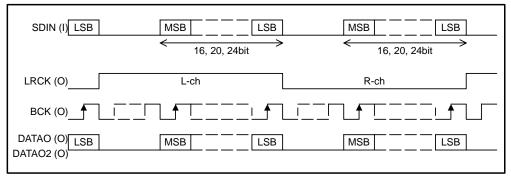

## 12.5.2 Serial Audio Data Input Format (SDIN, DOSEL0, DOSEL1)

- The LC890561W has SDIN which is serial digital audio data input pin and makes input of 24bit data possible.

- The format of the serial audio data input into SDIN should be adjusted to the same format as the demodulated data output. Therefore, the input format of SDIN is the same as the setup of DOSEL0 and DOSEL1 terminals, and the DOSW command.

- The SDIN data to be input should be in synchronization with BCK and LRCK clock.

- SDIN input data is output to DATAO and DATAO2 behind two frames since it is latched to shift register.

- When not using the SDIN terminal, it is connected to GND.

(0): Setting with DOSEL0, DOSEL1

(1) (2) (3): Setting with DOSEL0, DOSEL1

(4): Setting with the DOSW command

Figure 12.3 Data Input Timing Charts

## 12.5.3 Output Data Changing (DATAO, DATAO2, SDIN)

- DATAO and DATAO2 output demodulation data when PLL is locked, and output SDIN input data when PLL is unlocked. This switching is automatically performed according to the state of PLL lock or unlock.

- During the selection of SDIN input data, it must be switched to the clock source that is in synchronized with SDIN data.

- SDIIN input data is output to DATAO and DATAO2 with the SMOD command setting regardless of the lock / unlock state of PLL. In the case of switching PLL in the lock state, clock source is also switched to XIN. Furthermore, an ERROR flag also outputs high and a XSTATE signal also changes.

- DATAO and DATAO2 output can be muted forcibly with setting of the DOM[1:0] commands.

(b): Unlock stage

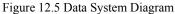

#### 12.5.4 Data System Diagram (DIN0, DIN1, DIN2, SDIN, DOUT, DATAO, DATAO2)

- Data system diagram is shown below.

- The delay setup for DATAO is possible. However, the delay setup for DATAO2 is impossible because DATAO2 does not go through a memory.

- DIN0 to DIN2 and SDIN input data are output to DATAO and DATAO2 behind two frames. Delay setup of output data is processed with the DATAO output with 2-frame delay against the input data as delay for 0ms.

- Since DATAO2 shares the pin with the validity flag output, it should be changed by the VSEL command. The initial value of VSEL is the validity flag output.

#### 12.6 Lock Error and Data Error Signal (ERROR)

- ERROR outputs an error flag, when PLL lock error arises or when a data error arises.

- The output form of an error signal is chosen by the ERF[1:0] commands.

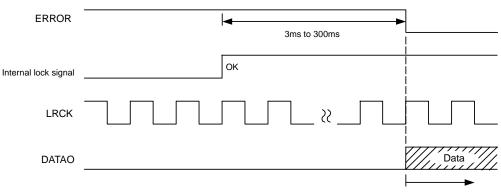

#### 12.6.1 PLL Lock Error

- PLL is unlocked to the data that has lost the pattern of input bi-phase modulation or which preamble B, M and W cannot be detected.

- ERROR outputs high upon occurrence of PLL lock error and outputs low after holding high for 3msec to 300msec after data demodulation returns to normal. See Figure 12.8.

- After PLL is locked, the holding period for high output of ERROR is decided by counting preamble B. Also, this period is changeable with EWT [1:0] commands.

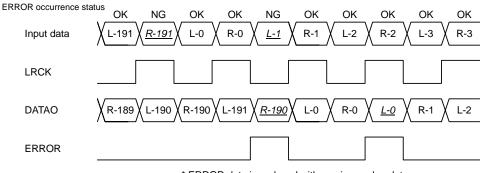

#### 12.6.2 Input Data Parity Error

- Parity bit errors (odd number) of input data and input parity errors are detected.

- If nine or more input parity errors occur in succession, ERROR outputs high, and then low after detecting the PLL lock status and holding high for 3 to 300msecs.

- If eight or fewer input parity errors occur in succession, the output format of error flag can be selected with ERF[1:0] commands.

\* ERROR data is replaced with previous value data.

Figure 12.6 Parity Error Flag Output Timing Chart (ERF[1:0] = 01, non delay setting)

#### 12.6.3 Others Error

• Even when ERROR goes low, channel status bits 24 to 27 (sampling frequency) are continuously sampled and the previous block of data and the current data are compared. If they are different, ERROR goes high immediately and the same processing as for the PLL lock error is performed. However, even if input data changes after ERROR goes low and the channel status information does not change, or if the input data changes within the PLL capture range, ERROR does not go high.

#### 12.7 Output Data Error Processing

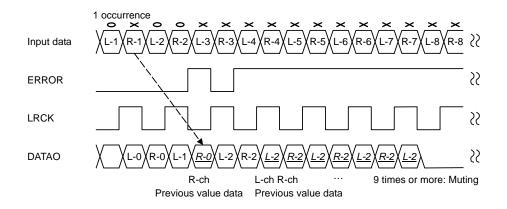

#### 12.7.1 Upon Error Occurrence (Lock Error and Parity Error)

- The data processing upon error occurrence is described below. If input parity errors occur eight times or more in succession, transfer data is replaced by the data held in L-ch and R-ch of the previous frame in the case of PCM audio data. However, if the data is Non-PCM burst data, error data is output without change as the transfer data. Non-PCM burst data is detected based on data detected prior to occurrence of an input parity error when channel status bit 1 goes high or when burst preamble Pa and Pb are detected.

- For the channel status, the data of the previous block is held in bit when a parity error occurs, regardless of the data type.

- Output data is muted upon occurrence of a PLL lock error or nine continuous parity errors.

| Data               | PLL lock error | Input parity error (a) | Input parity error (b) | Input parity error (c) |  |

|--------------------|----------------|------------------------|------------------------|------------------------|--|

| DATAO and DATAO2   | L              | L                      | Previous value data    | Output                 |  |

| F0, F1, F2 outputs | L              | Output                 | Output                 | Output                 |  |

| Channel status     | L              | Previous value data    | Previous value data    | Previous value data    |  |

| Validity flag      | L              | Output                 | Output                 | Output                 |  |

Table 12.6 Data Processing Upon Error Occurrence

\* Input parity error (a): If occurred 9 times or more in succession

\* Input parity error (b): If occurred 8 times or fewer, in the case of PCM audio data

\* Input parity error (c): If occurred 8 times or fewer, in the case of Non-PCM burst data

• Figure 12.7 shows an example of data processing upon occurrence of a parity error

Figure 12.7 Example of Data Processing Upon Parity Error Occurrence (non delay setting)

#### 12.7.2 Upon Error Recovery (Lock)

- When preamble B, M and W are detected, PLL is locked and data demodulation begins.

- DATAO and DATAO2 output data are output from the L/R clock edge after ERROR goes low.

- The start timing of the ERROR flag, and the DATAO and DATAO2 output data are shown in Figure 12.8.

- The above operation is in case the delay setup is not done. For information on operations with delay settings, see section "13. Output Data Delay Function".

Output start from LRCK edge immediately after ERROR flag is lowered

#### 12.8 Channel Status Emphasis Information Output (EMPHA)

- EMPHA outputs channel status information that indicates the presence or absence of 50/15µsec pre-emphasis.

- EMPHA is output immediately after the detection of ERROR even during high output.

| Table 12.7 EMPHA Outpu | ıt |

|------------------------|----|

|------------------------|----|

| EMPHA pin | Output condition     |

|-----------|----------------------|

| L         | No pre-emphasis      |

| Н         | 50/15μs pre-emphasis |

#### 12.9 Channel Status Bit 1 Output (AUDIO)

- AUDIO outputs bit 1 of the channel status that indicates whether transfer data has PCM audio data or data other than audio.

- AUDIO is output immediately after the detection of ERROR even during high output.

| The second | e 12.8 AUDIO Output |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| AUDIO pin | Output condition                     |

|-----------|--------------------------------------|

| L         | PCM audio data (CS bit 1 = L)        |

| Н         | Data other than audio (CS bit 1 = H) |

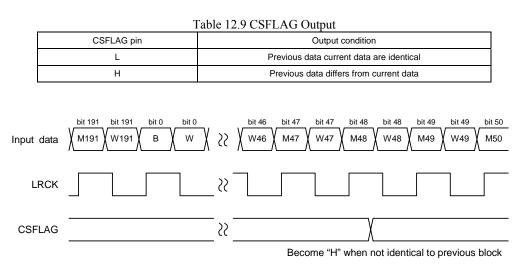

## 12.10 First 48 Channel Status Bits Update Flag Output (CSFLAG)

- CSFLAG compares the first 48 bits of channel status data of the previous block with those of the current block and outputs low in case they are the same, and high in case they are different, for 1 block of 192 frames. Therefore the channel status data output after the falling edge of the CSFLAG is the latest data.

- CSFLAG outputs high regardless of the comparison result until ERROR outputs low. After ERROR output becomes low, CSFLAG outputs low after the first 48bit data of the previous data and the current data have been confirmed to be identical.

Figure 12.9 Timing Chart for Channel Status Update Flag Output

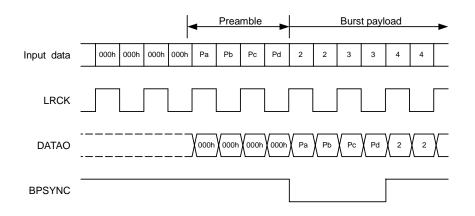

### 12.11 Non-PCM Burst Preamble Detection Signal Output (BPSYNC)

- BPSYNC outputs low while Non-PCM burst preamble Pa, Pb, Pc and Pd output, when Pa and Pb are detected following continuous all zero data of two frame. However, when output data delay is set up, low period of a BPSYNC signal and the output period of the Non-PCM burst preamble Pa, Pb, Pc, and Pd do not match. In this case, BPSYNC is output ahead of Pa, Pb, Pc, and Pd data.

- Pa, Pb, Pc and Pd are detected from the receive data even when an input parity error occurs.

Figure 12.10 Timing Chart for Pa, Pb, Pc and Pd Detection Signal Output

## 12.12 Input Sampling Frequency Calculation Signal Output (F0, F1, F2)

- By inputting 12.288MHz or 24.576MHz oscillation amplifier clock or external input clock, input sampling frequencies of 32kHz, 44.1kHz, 48kHz, 88.2kHz, 96kHz, 176.4kHz and 192kHz are calculated and the result is output from F0, F1 and F2.

- This processing is completed until preamble B is counted to eight after PLL is locked. Therefore, it is fixed by the time the ERROR flag is lowered, and it will not change until PLL is unlocked.

- If the frequency other than 12.288MHz or 24.576MHz is set, the F0, F1 and F2 outputs are not guaranteed.

- This information can also be read with the microcontroller interface.

- The fs of input data except input fs free mode is within the calculation range.

Table 12.10 Fs Calculation Results when 12.288MHz or 24.576MHz is Set ( $Ta = 25^{\circ}C$ ,  $V_{DD} = 3.3V$ )

| F2 pin | F1 pin | F0 pin | Target fs frequency | Calculation range    |

|--------|--------|--------|---------------------|----------------------|

| L      | L      | L      | Out of Range        | -                    |

| L      | L      | н      | 32kHz               | 30.8kHz to 33.3kHz   |

| L      | н      | L      | 44.1kHz             | 42.4kHz to 45.8kHz   |

| L      | н      | н      | 48kHz               | 46.2kHz to 49.9kHz   |

| н      | L      | L      | 88.2kHz             | 85.4kHz to 91.7kHz   |

| н      | L      | н      | 96kHz               | 93.1kHz to 99.0kHz   |

| н      | н      | L      | 176.4kHz            | 170.7kHz to 180.7kHz |

| н      | Н      | Н      | 192kHz              | 186.2kHz to 198.1kHz |

Note: \*Output when PLL is unlocked or when a sampling frequency cannot be calculated.

## 12.13 Validity Flag Output (VF)

- VF/DATAO2 outputs the validity flag.

- VF/DATAO2 shares the pin with the demodulated audio data output pin (delay setup is impossible). Setting as VSEL=0 (default) makes output validity flag possible.

#### Table 12.11 VF Output

| VF pin | Output condition                  |

|--------|-----------------------------------|

| L      | No (no burst data)                |

| н      | Error (possibility of burst data) |

# 13. Output Data Delay Function (DATAO, FSB0, FSB1, DLMP)

- It has built-in RAM that is utilized for the lip synchronization function that delays the sound data to the movie.

- Output data can be delayed for 256ms (fs = 48kHz) at the maximum.

- Delay processing of output data supports 24bit width data.

- The delayed data is outputted from DATAO terminal, not from DATAO2 terminal.

- Delay processing of output data is possible for demodulated data during PLL lock and serial audio data entered from the SDIN terminal.

- V, U and C bits transferred with S/PDIF input data are not delayed.

- The signal that can be used for delay setting control of output data is outputted from FSB0, FSB1 and DLMP terminals.

### 13.1 How to Set

#### 13.1.1 Output Data Delay Setup after Recovery Processing (DTMA[4:0], DTMB[3:0], DTMC[2:0])

- Output data delay after demodulation is set up by DTMA[4:0], DTMB[3:0] and DTMC[2:0] commands.

- It is possible to set different delay time for every input sampling frequency band by 10ms step unit.

- The delay time of 32kHz, 44.1kHz and 48kHz input data are set up with DTMA[4:0] commands.

- The delay time of 88.2kHz and 96kHz input data are set up with DTMB[3:0] commands.

- The delay time of 176.4kHz and 192kHz input data are set up with DTMC[2:0] commands.

# Table 13.1 Delay Time Setup of Output Data for the Data after Recovery Processing

|                     | Detay Time Setup of Outp<br>Data fs after r | ecovery processing (Hz) and setting |                             |  |  |

|---------------------|---------------------------------------------|-------------------------------------|-----------------------------|--|--|

| Delay time<br>(sec) | 32k, 44.1k, 48k<br>(DTMA[4:0])              | 88.2k, 96k<br>(DTMB[3:0])           | 176.4k, 192k<br>(DTMC[2:0]) |  |  |

| 0                   | 0                                           | 0                                   | 0                           |  |  |

| 10m                 | 0                                           | 0                                   | 0                           |  |  |

| 20m                 | 0                                           | 0                                   | 0                           |  |  |

| 30m                 | 0                                           | 0                                   | 0                           |  |  |

| 40m                 | 0                                           | 0                                   | 0                           |  |  |

| 50m                 | 0                                           | 0                                   | 0                           |  |  |

| 60m                 | 0                                           | 0                                   | 0                           |  |  |

| 70m                 | 0                                           | 0                                   | <b>♦</b>                    |  |  |

| 80m                 | 0                                           | 0                                   |                             |  |  |

| 90m                 | 0                                           | 0                                   |                             |  |  |

| 100m                | 0                                           | 0                                   |                             |  |  |

| 110m                | 0                                           | 0                                   |                             |  |  |

| 120m                | 0                                           | 0                                   |                             |  |  |

| 130m                | 0                                           | ◆                                   |                             |  |  |

| 140m                | 0                                           |                                     |                             |  |  |

| 150m                | 0                                           |                                     |                             |  |  |

| 160m                | 0                                           |                                     |                             |  |  |

| 170m                | 0                                           |                                     |                             |  |  |

| 180m                | 0                                           |                                     |                             |  |  |

| 190m                | 0                                           | See section "14.5.2 De              | tails of Write Commands"    |  |  |

| 200m                | 0                                           | See Section 14.5.2 De               | ans of write commands       |  |  |

| 210m                | 0                                           |                                     |                             |  |  |

| 220m                | 0                                           |                                     |                             |  |  |

| 230m                | 0                                           |                                     |                             |  |  |

| 240m                | 0                                           |                                     |                             |  |  |

| 250m                | 0                                           |                                     |                             |  |  |

| Max.                | •                                           |                                     |                             |  |  |

("○" can be set, "◆" maximum delay time is set)

- DTMA[4:0], DTMB[3:0] and DTMC[2:0] commands have the same address. Therefore, they can be set up together.

- Each command setting value is assigned to output data according to the sampling frequency of input data.

- Delay time is set up with the number of frames which is obtained by multiplying the sampling frequency calculation value of input data by the setting value of DTMA[4:0], DTMB[3:0] and DTMC[2:0] commands.

- Delay time can be freely switched within the range where the setup is possible.

- This setup is continued until it is canceled (delayed 0ms, non delay).

- This function is not performed when mode 4, "Input fs free mode B", by MODE0 and MODE1 is set. Even the above setting is set, it will be invalid.

## 13.1.2 Output Data Delay Setup of SDIN Input Data (DTMX[4:0], DTMY[3:0])

- Output data delay of SDIN input data is set up by DTMX[4:0] and DTMY[3:0] commands.

- SDIN input data needs to synchronize with BCK and LRCK output clocks. Therefore, the sampling frequency of SDIN data is decided by setup of XSEL (XIN input clock frequency). In other word, input data is either 48kHz or 96kHz, and uses a setup of either DTMX[4:0] or DTMY[3:0] commands.

- Delay time can be freely switched within the range where the setup is possible.

- This setup is continued until it is canceled (delayed 0ms, non delay).

- The following delay time is performed when mode 4, "Input fs free mode B", by MODE0 and MODE1 is set. Delay time = {(256fs × delay time of DTMX [4:0] or DTMY [3:0]) / XIN input clock}

|            |             | (Hz) and setting commands                         |

|------------|-------------|---------------------------------------------------|

| Delay time | 48k         | 96k                                               |

| (sec)      | (DTMX[4:0]) | (DTMY[3:0])                                       |

| 0          | 0           | 0                                                 |

| 10m        | 0           | 0                                                 |

| 20m        | 0           | 0                                                 |

| 30m        | 0           | 0                                                 |

| 40m        | 0           | 0                                                 |

| 50m        | 0           | 0                                                 |

| 60m        | 0           | 0                                                 |

| 70m        | 0           | 0                                                 |

| 80m        | 0           | 0                                                 |

| 90m        | 0           | 0                                                 |

| 100m       | 0           | 0                                                 |

| 110m       | 0           | 0                                                 |

| 120m       | 0           | 0                                                 |

| 130m       | 0           | •                                                 |

| 140m       | 0           |                                                   |

| 150m       | 0           |                                                   |

| 160m       | 0           |                                                   |

| 170m       | 0           |                                                   |

| 180m       | 0           |                                                   |

| 190m       | 0           |                                                   |

| 200m       | 0           | See section "14.5.2 Details of Write<br>Commands" |

| 210m       | 0           | Commands                                          |

| 220m       | 0           |                                                   |

| 230m       | 0           |                                                   |

| 240m       | 0           |                                                   |

| 250m       | 0           |                                                   |

| Max.       | <b>♦</b>    |                                                   |

| Table 13.2 Delay | Time Setup    | of Output Data  | for the SDIN Input Data |

|------------------|---------------|-----------------|-------------------------|

| 10010 10.2 2010  | 1 mile Severp | or o aipai Daia | iei me sen input suu    |

("○" can be set, "◆" maximum delay time is set)

#### 13.2 DATAO Output Data Processing

- When any of the DTMA [4:0], DTMB [3:0], DTMC [2:0], DTMX [4:0], DTMY [3:0] is set up (setup of those other than an initial state), delay processing of output data is performed.

- Delay processing of the target data and mute processing of output data are explained below.

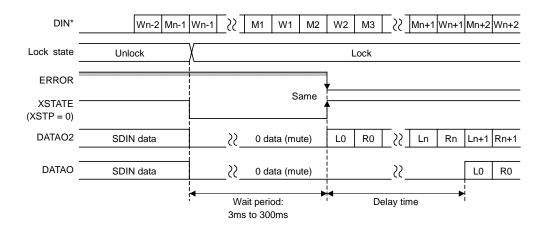

#### 13.2.1 Output Data Delay Setup after Recovery Processing (Setting at the state of ERROR = H)

- When the DTMA[4:0], DTMB[3:0] and DTMC[2:0] commands are set up or changed during high output of ERROR flag, data is written into memory in synchronization with the rising edge of XSTATE after PLL is locked.

- Readout of the data written in the memory is started after the set delay time (frame).

- The data read out is constantly output form DATAO with the delay of the setup time.

- DATAO will be muted until the set delay time is over, because sufficient data is not written into memory immediately after the low output of ERROR flag.

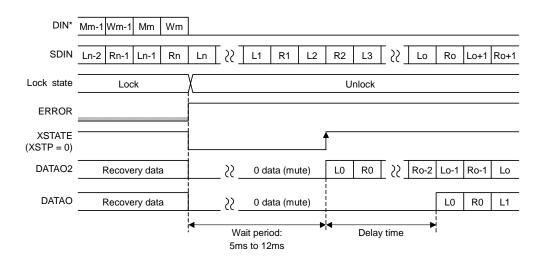

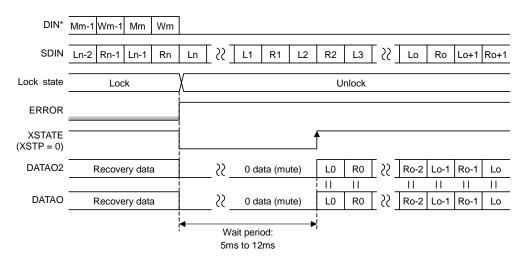

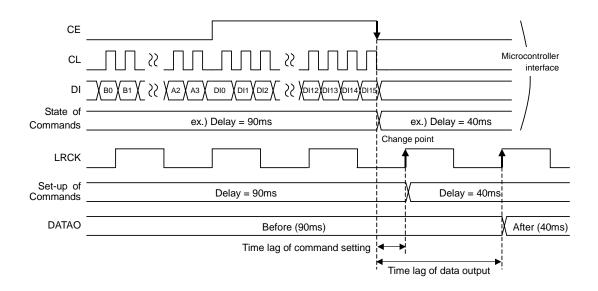

Figure 13.1 Timing Chart for Output Data after Setup or Change of the Delay Time During PLL Lock-in

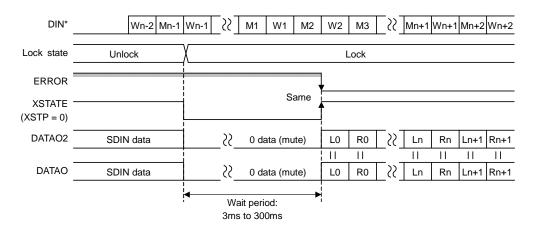

• When the DTMA[4:0], DTMB[3:0] and DTMC[2:0] commands are canceled during high output of ERROR flag, data is output from DATAO synchronizing with the rising edge of XSTATE after PLL is locked. This is normal operation which does not perform a delay processing setup.

Figure 13.2 Timing Chart for Output Data after Cancel of the Delay Time Setting During PLL Lock-in

#### 13.2.2 Output Data Delay Setup after Recovery Processing (Setting at the state of ERROR = L)

- When the DTMA[4:0], DTMB[3:0] and DTMC[2:0] commands are set up or changed during L output of ERROR flag, delay processing is performed according to the setup of those commands.

- After power up, when the command is set up for the first time, a memory domain is assigned according to the set delay, and data is written in a memory.

- A memory domain is reset when the delay time is changed in the state where the command is already set up. And a memory domain is assigned according to the newly set-up delay time, and the data writing to a memory is started.

- Readout of the data written in the memory is started after the set delay time (frame).

- DATAO output is muted immediately after the command setup until the end of the set delay time.

| ERROR                    |      | L       |        |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      |                   |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |        |          |      |      |      |      |      |

|--------------------------|------|---------|--------|------|-----------------------------------------|------|-------------------|------|-----------------------------------------|--------|----------|------|------|------|------|------|

| XSTATE<br>(XSTP = 0)     |      | н —     |        |      |                                         |      |                   |      |                                         |        |          |      |      |      |      |      |

| LRCK                     |      |         |        |      | •                                       |      | ţ l               |      |                                         |        | <u>}</u> |      |      |      |      |      |

| Setting of<br>Delay time | ex.  | .) Dela | y = 50 | ms   | X                                       |      | ex.) Delay = 70ms |      |                                         |        |          |      |      |      |      |      |

| -                        |      |         |        |      |                                         | -    | <br>              |      |                                         |        |          |      |      |      |      |      |

| DATAO2                   | Ln-1 | Rn-1    | Ln     | Rn   | Ln+1                                    | Rn+1 | Ln+2              | Rn+2 | Ln+3                                    |        | <u> </u> | Rn+a | Ln+b | Rn+b | Ln+c | Rn+c |

|                          |      |         |        |      |                                         |      |                   |      |                                         |        |          |      |      |      |      |      |

| DATAO                    | Lm-2 | Rm-2    | Lm-1   | Rm-1 | Lm                                      | Rm   |                   |      |                                         | 0 dat  | a (mute) | )    |      |      | Ln-a | Rn-a |

|                          |      |         |        |      |                                         |      | <b>.</b>          |      | De                                      | lay ti | me (70n  | ns)  |      |      |      |      |

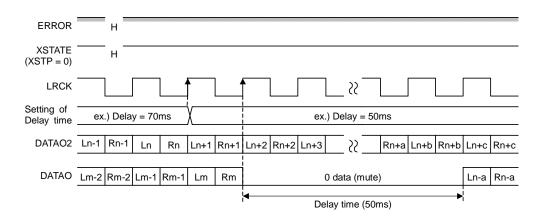

Figure 13.3 Timing Chart for Output Data after Setup or Change of the Delay Time During PLL Lock

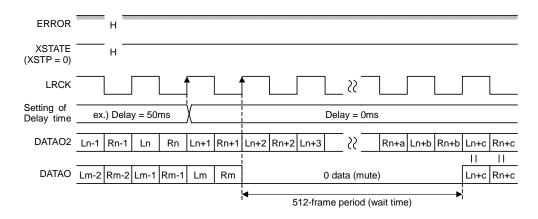

• When delay time is canceled in the state where the command is already set up, the writing to the memory is stopped. However, DATAO is output after muting the input data for 512-frame period. DATAO is not output immediately after cancel of command setting. The 512-frame period is dependent on the sampling frequency of input data.

| ERROR                    |      | L       |        |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |        |      |           |          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|--------------------------|------|---------|--------|------|-----------------------------------------|-----------------------------------------|------|-----------------------------------------|--------|------|-----------|----------|-----------------------------------------|-----------------------------------------|------|-----------------------------------------|

| XSTATE<br>(XSTP = 0)     |      | H       |        |      |                                         |                                         |      |                                         |        |      |           |          |                                         |                                         |      |                                         |

| LRCK                     |      |         |        |      | •                                       |                                         |      |                                         |        |      |           |          |                                         |                                         |      |                                         |

| Setting of<br>Delay time | ex   | .) Dela | y = 50 | ms   | X                                       |                                         |      |                                         |        | Dela | ay = 0ms  |          |                                         |                                         |      |                                         |

| DATAO2                   | Ln-1 | Rn-1    | Ln     | Rn   | Ln+1                                    | Rn+1                                    | Ln+2 | Rn+2                                    | Ln+3   |      | 25        | Rn+a     | Ln+b                                    | Rn+b                                    | Ln+c | Rn+c                                    |

|                          |      |         |        |      |                                         |                                         |      |                                         |        |      | ·         |          |                                         |                                         |      | 11                                      |

| DATAO                    | Lm-2 | Rm-2    | Lm-1   | Rm-1 | Lm                                      | Rm                                      |      |                                         |        | 0 da | ta (mute) |          |                                         |                                         | Ln+c | Rn+c                                    |

|                          |      |         |        |      |                                         |                                         | •    | 5                                       | 12-fra | me p | eriod (wa | ait time | e)                                      |                                         |      |                                         |

Figure 13.4 Timing Chart for Output Data after Cancel of the Delay Time Setting During PLL Locked

• When the command is changed before the completion of command setting, the delay process is initialized every command setting. For DATAO output, mute output is continued until the setting is fixed.

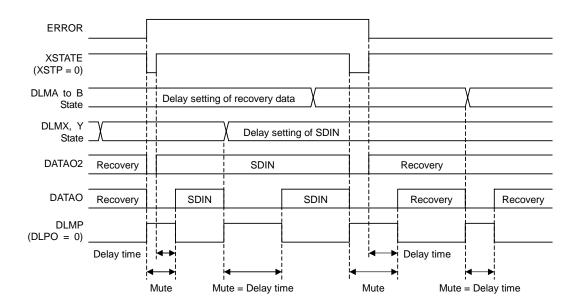

#### 13.2.3 Output Data Delay Setup of SDIN Input Data (Setting at the state of ERROR = L)

- When the DTMX[4:0] or DTMY[3:0] commands are set up during low output of ERROR flag, data is written to a memory in synchronization with the rising edge of XSTATE after PLL unlock.

- Readout of the data written in the memory is started after the set delay time (frame).

- The data read out is constantly output form DATAO with the delay of the setup time.

- DATAO will be muted until the set delay time is over, because sufficient data is not written into memory immediately after the low output of ERROR flag.

Figure 13.5 Timing Chart for Output Data after Setup or Change of the Delay Time During PLL Unlock

• When the DTMX[4:0] or DTMY[3:0] commands are canceled during low output of ERROR flag, data is output from DATAO synchronizing with the rising edge of XSTATE after PLL unlock. This is normal operation which does not perform a delay processing setup.

Figure 13.6 Timing Chart for Output Data after Cancel of the Delay Time Setting During PLL Unlock

#### 13.2.4 Output Data Delay Setup of SDIN Input Data (Setting at the state of ERROR = H)

- When the DTMX[4:0] or DTMY[3:0] commands are set up or changed during high output of ERROR flag, delay processing is performed according to the setup of those commands.

- After power up, when the command is set up for the first time, a memory domain is assigned according to the set delay, and data is written in a memory.

- A memory domain is reset when the delay time is changed in the state where the command is already set up. And a memory domain is assigned according to the newly set delay time, and the data writing to a memory is started.

- Readout of the data written in the memory is started after the set delay time (frame).

- DATAO output is muted immediately after the command setup until the end of the set delay time.

Figure 13.7 Timing Chart for Output Data after Setup or Change of the Delay Time During PLL Unlock

• When delay time is canceled in the state where the command is already set up, the writing to the memory is stopped. However, DATAO is output after muting the input data for 512-frame period. DATAO is not output immediately after cancel of command setting. The 512-frame period is dependent on the sampling frequency of input data.

Figure 13.8 Timing Chart for Output Data after Cancel of the Delay Time Setting During PLL Unlock

• When the command is changed before the completion of command setting, the delay process is initialized every command setting. For DATAO output, mute output is continued until the setting is fixed.

### 13.3 Time Lag of the Command Setup (DTMA[4:0], DTMB[3:0], DTMC[2:0], DTMX[4:0], DTMY[3:0])

- DTMA [4:0], DTMB [3:0], DTMC [2:0], DTMX [4:0] and DTMY [3:0] commands are performed synchronizing with the rising edge (the falling edge is used for the I<sup>2</sup>S data format setup) of LRCK clock. Therefore, the time lag of 1 LRCK cycle at the maximum arises after setting up the command until it is executed.

- Moreover, the minimum interval of a command setup becomes 1 LRCK period.

- Furthermore, data processing by command setup is performed after 1 LRCK period progress.

- Setup, change and cancel of the delay time are processed per command.

- Setup, change and cancel of the command in the same address are performed for the data of the target input sampling frequency.

- Cancel of the command is the case where the delay time is set as 0.

Figure 13.9 Timing Chart from a Command Setup to Execution

### 13.4 Monitor Setup for Output Data Delay Setting (FSEL)

- Information available for delay setting of output data can be monitored by FSB0, FSB1 and DLMP pins by switching the FSEL command. This setup is switched by FSEL command.

- FSB0 and FSB1 terminal classifies the calculation result of the sampling frequency of input data into standard frequency, standard ×2, and standard ×4 and outputs.

- However, when S/PDIF data is not received, PLL is not locked, or when the mode 4 is set up with MODE0 and MODE1 terminal, FSB0 and FSB1 terminals output low.

- DLMP terminal outputs a pulse signal during the waiting time period at the time of ERROR flag switching, or during the mute period at the time of a delay setup. This pulse can change polarity by DLPO command.

Table 13.3. FSB0 and FSB1 output state (FSEL = 1)

| FSB1 pin | FSB0 pin | Output state                                                                                              |

|----------|----------|-----------------------------------------------------------------------------------------------------------|

| L        | L        | S/PDIF data is not received, or PLL is unlocked, when the mode 4 is set up with MODE0 and MODE1 terminal. |

| L        | н        | S/PDIF data is either of the 32kHz or 44.1kHz or 48kHz.<br>(Standard frequency)                           |

| Н        | L        | S/PDIF data is either of the 88.2kHz or 96kHz.<br>(Standard ×2 frequency)                                 |

| Н        | Н        | S/PDIF data is either of the 176.4kHz or 192kHz.<br>(Standard ×4 frequency)                               |

Figure 13.10 Timing Chart for DLMP Output Mute Period (command cancel is not included)

# 14. Microcontroller Interface (CL, CE, DI, DO)

# 14.1 Chip Address Settings

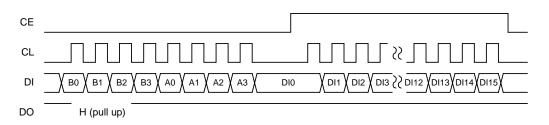

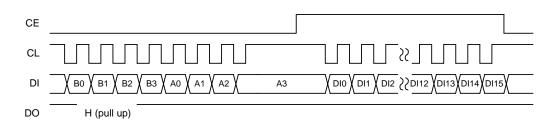

• The microcontroller interface uses Sanyo's original serial bus format (CCB). Data input/output is performed after data input/output address has been assigned. DO pin is an open drain output system.

|          |           | Table 14    | I.I Add | iresses | Setting | <u>ş</u> s |    |    |    |    |

|----------|-----------|-------------|---------|---------|---------|------------|----|----|----|----|

| Data inp | ut/output | CCB address | B0      | B1      | B2      | B3         | A0 | A1 | A2 | A3 |

| Data i   | nput 1    | 0xE8        | 0       | 0       | 0       | 1          | 0  | 1  | 1  | 1  |

| C bit o  | output    | 0xE9        | 1       | 0       | 0       | 1          | 0  | 1  | 1  | 1  |

| Pc data  | output    | 0xEA        | 0       | 1       | 0       | 1          | 0  | 1  | 1  | 1  |

| Data i   | nput 2    | 0xEB        | 1       | 1       | 0       | 1          | 0  | 1  | 1  | 1  |

| Data i   | nput 3    | 0xEC        | 0       | 0       | 1       | 1          | 0  | 1  | 1  | 1  |

| Data i   | nput 4    | 0xED        | 1       | 0       | 1       | 1          | 0  | 1  | 1  | 1  |

| <b>T</b> 1 1 1 |     |           | a        |

|----------------|-----|-----------|----------|

| Table          | 4.1 | Addresses | Settings |

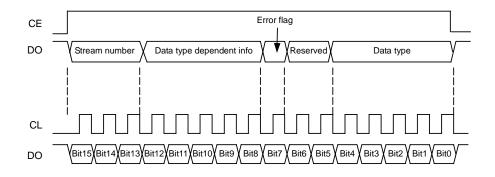

# 14.2 Input/Output Timing

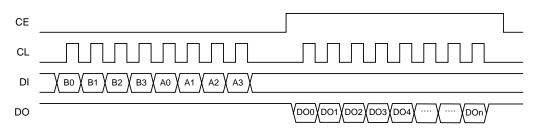

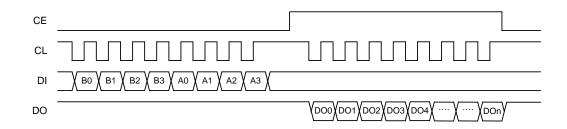

Figure 14.1 Input Timing Chart (Normal L Clock)

Figure 14.2 Input Timing Chart (Normal H Clock)

Figure 14.3 Output Timing Chart (Normal L Clock, DO includes a pull-up resister)

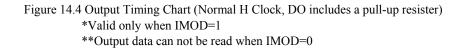

#### 14.3 0xE9 Data Output Timing

Figure 14.5 Output Timing of Flag + Channel Status Data

## 14.4 0xEA Data Output Timing

Figure 14.6 Output Timing of Preamble Pc Data

# 14.5 Write Data

## 14.5.1 List of Write Commands

• A list of the write commands is shown below.

| Tab           | le 14.2 Input Register                                                                                                       | Map                                                                                                           |                                                                                                                                                       |