# CMOS LSI

LC89052T

# **Digital Audio Interface Receiver**

## 1. Overview

The LC89052T is an audio LSI that demodulates according to the data format for the data transferred between digital audio devices via the IEC 60958/61937 and EIAJ CP-1201. It supports sampling frequencies of up to 192kHz and output data lengths up to 28 bits. Despite it is compact and made in a low cost, the LC89052T includes a built-in oscillator and serial data input circuits and allows the system microcontroller to read the sub-code Q data and channel status. It supports low-power modes that allow low-voltage operation. It also supports a lower power mode, which is suitable for application that requires long battery life, such as cell phones, PDAs, and portable audio devices.

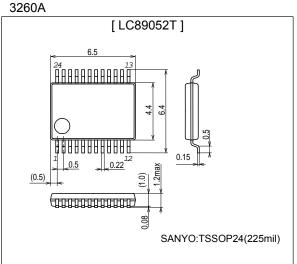

## 3. Package Dimensions

unit: mm

## 2. Features

- Incorporates a built-in PLL circuit to synchronize with transferred bi-phase mark signal.

- Can receive input with sampling frequencies of 32kHz to 192kHz.

- Can set the upper limit of sampling frequency of received data.

- Can receive input data of specific sampling frequencies.

- Outputs the following clocks: fs, 64fs, 128fs, 256fs, 384fs, and 512fs.

- Contains a built-in oscillation amplifier that can construct a oscillation circuit. An external clock can be also provided.

- Outputs an externally input clock signal that can be used as the A/D converter clock when the PLL is unlocked.

- Maintains the continuity of the output clock when the clock is switched.

- Equipped with a serial digital audio data input pin that can be configured for a demodulated signal output.

- Can output up to 28 bits of data, and also supports output of I<sup>2</sup>S and input NRZ data.

- Can output bi-phase mark signal synchronized with the 128fs bit clock.

- Provides an output pin for the channel status bit 1 non-PCM data detection bit.

- Provides an output pin for the channel status emphasis detection bit.

- Supports a lower-power mode.

Continued on next page.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN Continued from preceding page.

- Calculates the input signal sampling frequency and outputs it from the microcontroller interface.

- Can output the first 48 bits of the channel status with the microcontroller interface.

- Can output the 80-bit sub-code Q data with CRC flags via microcontroller interface.

- Outputs various state changes as interrupt signals to the microcontroller interface.

- Equipped with a user definable output port that can be selected from the following functions.

—Microcontroller interface register output (for power saving mode optical module control signals, etc.)

—Signal output of transitional period where VCO clock and external input clock are switched.

- -Signal output of transitional period where vCO clock and external input

- Can dispense with un-used microcontroller control.

- 3.3V single source power supply (Can operate at a minimum voltage of 2.7V.)

- The TTL input ports can support 5V interface operation.

- Package: TSSOP-24

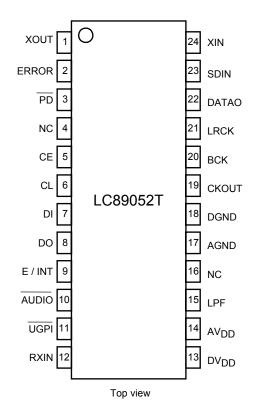

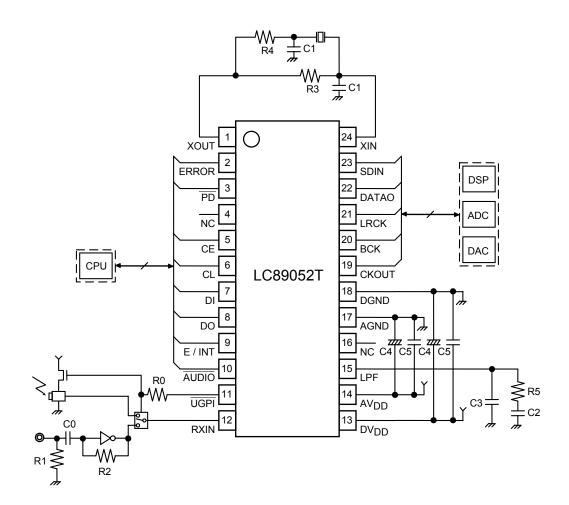

## 4. Pin Assignments

## 5. Pin Description

| Pin No. | Name             | I/O            | Function                                                                 |  |  |  |  |  |

|---------|------------------|----------------|--------------------------------------------------------------------------|--|--|--|--|--|

| 1       | XOUT             | 0              | Oscillation amplifier circuit output pin                                 |  |  |  |  |  |

| 2       | ERROR            | 0              | PLL lock error and data error output pin                                 |  |  |  |  |  |

| 3       | PD               | I <sub>5</sub> | System reset and low-power mode control input pin                        |  |  |  |  |  |

| 4       | NC               |                | Non connection                                                           |  |  |  |  |  |

| 5       | CE               | I <sub>5</sub> | Microcontroller interface: chip enable input pin                         |  |  |  |  |  |

| 6       | CL               | I <sub>5</sub> | Microcontroller interface: serial clock input pin                        |  |  |  |  |  |

| 7       | DI               | I <sub>5</sub> | Microcontroller interface: write data input pin                          |  |  |  |  |  |

| 8       | DO               | 0              | Microcontroller interface: read data output pin                          |  |  |  |  |  |

| 9       | E / INT          | 0              | Pre-emphasis detection or microcontroller interface interrupt output pin |  |  |  |  |  |

| 10      | AUDIO            | 0              | Channel status bit 1 non-PCM data detection output pin                   |  |  |  |  |  |

| 11      | UGPI             | 0              | User settable output pin *                                               |  |  |  |  |  |

| 12      | RXIN             | I <sub>5</sub> | Digital data input pin                                                   |  |  |  |  |  |

| 13      | DVDD             |                | Digital power supply pin                                                 |  |  |  |  |  |

| 14      | AV <sub>DD</sub> |                | Analog power supply pin                                                  |  |  |  |  |  |

| 15      | LPF              | 0              | PLL loop filter pin                                                      |  |  |  |  |  |

| 16      | NC               |                | Non connection                                                           |  |  |  |  |  |

| 17      | AGND             |                | Analog GND pin                                                           |  |  |  |  |  |

| 18      | DGND             |                | Digital GND pin                                                          |  |  |  |  |  |

| 19      | CKOUT            | 0              | System clock output pin **                                               |  |  |  |  |  |

| 20      | BCK              | 0              | 64fs clock output pin                                                    |  |  |  |  |  |

Table 5.1 Pin Functions

\* : Microcontroller register output or clock switching transition period signal.

Fs clock output pin

Demodulated data output pin

Oscillator or external clock input pin

Serial digital data input pin

\*\* : 128fs, 256fs, 384fs, 512fs, or oscillator amplifier outputs.

0

0

l5

Т

\*\*\* : Other than I<sup>2</sup>S mode ; Low: right channel, High: left channel. I<sup>2</sup>S mode ; Low: left channel, High: right channel.

1) I/O voltage handling :

21

22

23

24

I or O pins : -0.3 to +3.6V,

I5 pins : -0.3 to +5.5V

LRCK

DATAO

SDIN

XIN

2) To prevent logic circuit latch-up, all power supply must be applied or removed simultaneously.

\*\*\*

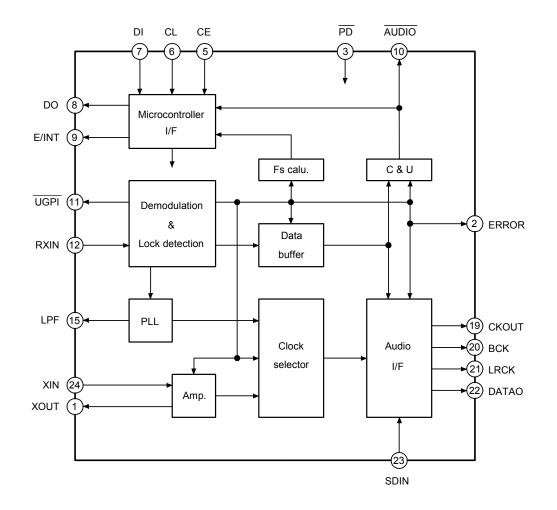

## 6. Block Diagram

## 7. Electrical Characteristics

7.1 Absolute Maximum Ratings

Table 7.1 Absolute Maximum Ratings at AGND = DGND = 0V

| Parameter              | Symbol               | Conditions | Ratings     | unit |

|------------------------|----------------------|------------|-------------|------|

| Maximum supply voltage | AV <sub>DD</sub> max | 7-1-1      | -0.3 to 4.6 | V    |

| Maximum supply voltage | DV <sub>DD</sub> max | 7-1-2      | –0.3 to 4.6 | V    |

| Input voltage 1        | V <sub>IN</sub> 1    | 7-1-3      | –0.3 to 3.9 | V    |

| Input voltage 2        | V <sub>IN</sub> 2    | 7-1-4      | –0.3 to 5.8 | V    |

| Output voltage         | VOUT                 | 7-1-5      | –0.3 to 3.9 | V    |

| Storage temperature    | Tstg                 |            | –55 to 125  | °C   |

| Operating temperature  | Торд                 |            | -30 to 70   | °C   |

| Maximum output current | li, I <sub>OUT</sub> | 7-1-6      | ±20         | mA   |

7-1-1: AV<sub>DD</sub> pin.

7-1-2: DV<sub>DD</sub> pin.

7-1-3 : XIN pin.

7-1-4: RXIN, SDIN, PD, CE, CL, and DI pins.

7-1-5: XOUT, ERROR, DO, E/INT, AUDIO, UGPI, CKOUT, BCK, LRCK, and DATAO pins.

7-1-6 : Per single input or output pin.

### 7.2 Recommended Operating Conditions

Table 7.2 Recommended Operating Conditions

| Parameter             | Symbol                              | Conditions | min | typ | max | unit |

|-----------------------|-------------------------------------|------------|-----|-----|-----|------|

| Supply voltage 1      | av <sub>dd</sub> , dv <sub>dd</sub> | 7-2-1      | 2.7 | 3.3 | 3.6 | V    |

| Supply voltage 2      | AV <sub>DD</sub> , DV <sub>DD</sub> | 7-2-2      | 3.0 | 3.3 | 3.6 | V    |

| Input voltage range 1 | V <sub>IN</sub> 1                   | 7-2-3      | 0   | 3.3 | 3.6 | V    |

| Input voltage range 2 | V <sub>IN</sub> 2                   | 7-2-4      | 0   | 3.3 | 5.5 | V    |

| Operating temperature | Vopg                                |            | -30 |     | 70  | °C   |

7-2-1 : PLLCK [1:0] = "00" or PLLCK [1:0] = "01"

7-2-2: PLLCK [1:0] = "10" or PLLCK [1:0] = "11"

7-2-3: XIN pin

7-2-4: RXIN, SDIN, PD, CE, CL, and DI pins

#### 7.3 Input and Output Pin Capacitances

Table 7.3 Input and Output Pin Capacitances

| Parameter   | Symbol           | Conditions | min | typ | max | unit |

|-------------|------------------|------------|-----|-----|-----|------|

| Input pins  | C <sub>IN</sub>  | 7-3-1      |     |     | 10  | pF   |

| Output pins | C <sub>OUT</sub> | 7-3-1      |     |     | 10  | pF   |

7-3-1:  $AV_{DD} = DV_{DD} = V_{IN}1 = V_{IN}2 = 0$  V,  $Ta = 25^{\circ}C$ , f = 1MHz

## 7.4 DC Characteristics

| Table 7.4 DC Characteristics at $Ta = -30$ to | $\sqrt{70^{\circ}C}$ $\Lambda V_{DD} = DV_{DD}$ | $-20 t_0 26V ACND - DCND - 0V$     |

|-----------------------------------------------|-------------------------------------------------|------------------------------------|

| - Table 7.4 DC Characteristics at Ta = -50 to | $\mathcal{F}$                                   | = 5.010.5.0 V. AUND $= DUND = 0$ V |

|                                               |                                                 |                                    |

|                           |                   | 22         |                        |     |                     |      |

|---------------------------|-------------------|------------|------------------------|-----|---------------------|------|

| Parameter                 | Symbol            | Conditions | min                    | typ | max                 | unit |

| High-level input voltage  | VIH               | 7-4-1      | 0.7DV <sub>DD</sub>    |     |                     | V    |

| Low-level input voltage   | VIL               |            |                        |     | 0.2DV <sub>DD</sub> | V    |

| High-level input voltage  | VIH               | 7-4-2      | 2.0                    |     | 5.8                 | V    |

| Low-level input voltage   | VIL               |            | -0.3                   |     | 0.8                 | V    |

| High-level output voltage | V <sub>OH</sub>   | 7-4-3      | DV <sub>DD</sub> – 0.8 |     |                     | V    |

| Low-level output voltage  | V <sub>OL</sub>   |            |                        |     | 0.4                 | V    |

| High-level output voltage | V <sub>OH</sub>   | 7-4-4      | DV <sub>DD</sub> – 0.8 |     |                     | V    |

| Low-level output voltage  | V <sub>OL</sub>   |            |                        |     | 0.4                 | V    |

| High-level output voltage | V <sub>OH</sub>   | 7-4-5      | DV <sub>DD</sub> – 0.8 |     |                     | V    |

| Low-level output voltage  | V <sub>OL</sub>   |            |                        |     | 0.4                 | V    |

| Power consumption         | I <sub>DD</sub> 1 | 7-4-6      |                        | 6.5 | 13                  | mA   |

| Power consumption         | I <sub>DD</sub> 2 | 7-4-7      |                        |     | 0.1                 | μA   |

| Power consumption         | I <sub>DD</sub> 3 | 7-4-8      |                        | 4.5 | 9                   | mA   |

| Power consumption         | I <sub>DD</sub> 4 | 7-4-9      |                        | 5   | 10                  | mA   |

7-4-1: CMOS level pins: XIN pin.

7-4-2: TTL level pins: Input pins other than those listed above.

7-4-3 :  $I_{OH} = -8mA$ ,  $I_{OL} = 6mA$ : CKOUT pin.

7-4-4 :  $I_{OH} = -2mA$ ,  $I_{OL} = 2mA$ : BCK, LRCK, DATAO, and DO pins.

7-4-5 :  $I_{OH} = -1mA$ ,  $I_{OL} = 1mA$ : Output pins other than those listed above.

7-4-6 : Operating mode: PLLSEL = "0", AMPOPR = "0", fs = 44.1 kHz,  $C_L = 30 \text{ pF}$

7-4-7 : Low power mode condition 1) :  $\overline{PD} = low$

7-4-8 : Low power mode condition 2) : PDOWN [1:0] = "01", XIN = 11.2896MHz, CL = 30pF

7-4-9: Low power mode condition 3): PDOWN [1:0] = "10", XIN = 11.2896MHz, CL = 30pF

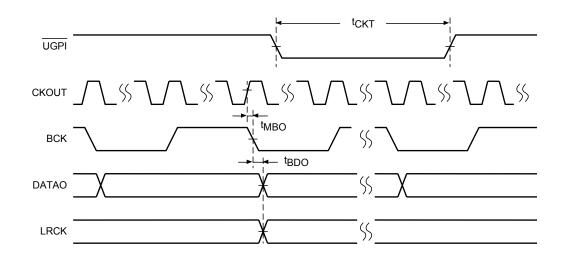

## 7.5 AC Characteristics

| Parameter                  | Symbol                       | Conditions | min | typ     | max | unit |

|----------------------------|------------------------------|------------|-----|---------|-----|------|

| RXIN sampling frequency    | f <sub>FS</sub> 1            | 7-5-1      | 30  |         | 195 | kHz  |

| RXIN sampling frequency    | f <sub>FS</sub> 2            | 7-5-2      | 30  |         | 108 | kHz  |

| XIN clock frequency        | fXF1                         | 7-5-3      |     | 11.2896 |     | MHz  |

| XIN clock frequency        | f <sub>XF</sub> 2            | 7-5-4      |     | 12.2880 |     | MHz  |

| XIN clock frequency        | f <sub>XF</sub> 3            | 7-5-5      |     | 16.9344 |     | MHz  |

| XIN clock frequency        | <sup>f</sup> XF <sup>4</sup> | 7-5-6      |     | 22.5792 |     | MHz  |

| XIN clock frequency        | f <sub>XF</sub> 5            | 7-5-7      |     | 24.5760 |     | MHz  |

| XIN clock frequency        | f <sub>XF</sub> 6            | 7-5-8      |     | 33.8688 |     | MHz  |

| CKOUT clock frequency      | <sup>f</sup> MCK             |            | 2   |         | 100 | MHz  |

| CKOUT clock jitter         | tj                           |            |     | 200     |     | ps   |

| CKOUT to BCK delay         | <sup>t</sup> MBO             |            |     |         | 10  | ns   |

| BCK to DATAO delay         | <sup>t</sup> BDO             |            |     |         | 5   | ns   |

| UGPI low-level pulse width | tскт                         | 7-5-9      |     |         | 100 | ms   |

7-5-1 : PLLCK [1:0] = "00"

7-5-2: Settings other than PLLCK [1:0] = "00".

7-5-3 : XISEL [3:0] = "0000"

7-5-4 : XISEL [3:0] = "0001"

7-5-5 : XISEL [3:0] = "0010"

7-5-6 : XISEL [3:0] = "0100"

7-5-7: XISEL [3:0] = "0101"

7-5-8 : XISEL [3:0] = "0110"

7-5-9: When signal output is set during a transitional period of clock switching.

Figure 7.1 AC Characteristics

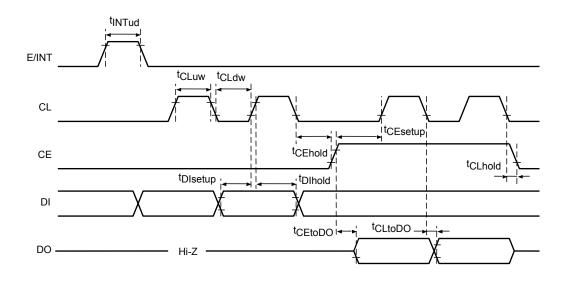

### 7.6 Microcontroller Interface AC Characteristics

Table 7.6 Microcontroller Interface AC Characteristics

| at Ta = -30 to 70°C, $AV_{DD} = DV_{DD} = 3.0$ to 3.6V, $AGND = DGND = 0V$ |                      |            |     |      |     |      |

|----------------------------------------------------------------------------|----------------------|------------|-----|------|-----|------|

| Parameter                                                                  | Symbol               | Conditions | min | typ  | max | unit |

| PD low-level pulse width                                                   | <sup>t</sup> PDdw    |            | 200 |      |     | μs   |

| E/INT high-level pulse width                                               | <sup>t</sup> INTuw   | 7-6-1      | 5   | 1/fs | 63  | μs   |

| CL low-level pulse width                                                   | <sup>t</sup> CLdw    |            | 100 |      |     | ns   |

| CL high-level pulse width                                                  | <sup>t</sup> CLuw    |            | 100 |      |     | ns   |

| CL to CE setup time                                                        | <sup>t</sup> CEsetup |            | 50  |      |     | ns   |

| CL to CE hold time                                                         | <sup>t</sup> CEhold  |            | 50  |      |     | ns   |

| CL to DI setup time                                                        | <sup>t</sup> DIsetup |            | 50  |      |     | ns   |

| CL to DI hold time                                                         | <sup>t</sup> Dlhold  |            | 50  |      |     | ns   |

| CL to CE hold time                                                         | <sup>t</sup> CLhold  |            | 50  |      |     | ns   |

| CL to DO delay time                                                        | <sup>t</sup> CLtoDO  |            |     |      | 20  | ns   |

| CE to DO delay time                                                        | <sup>t</sup> CEtoDO  |            |     |      | 20  | ns   |

7-6-1: INTOPF = "1", INTSEL = "1", and fs is the input sampling frequency.

Figure 7.2 Microcontroller AC Characteristics

## 8. Function Description

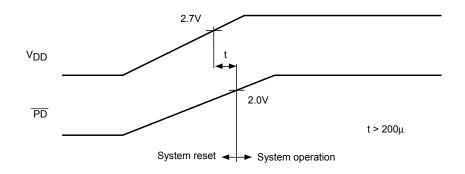

## 8.1 System Reset (PD)

- The system operates normally when  $\overline{PD}$  pin is set to high level after a supply voltage is rises to 2.7V or higher. When you set the  $\overline{PD}$  pin to low again after power is applied, the system is reset.

- When power is on, resetting must be done with the  $\overline{PD}$  pin set to low.

- If a crystal oscillator is used, you must wait to start normal operation for at least 10ms until the oscillation gets stable after the  $\overline{PD}$  pin goes from low to high.

Figure 8.1 PD Pin Levels at Power On

## 8.2 Low-Power Modes

- The LC89052T supports two low-power modes: the mode in which whole circuit is controlled with the PD pin and the mode in which only special functions are controlled by the PDOWN[1:0].

- The low-power mode controlled by the PD applies to the entire circuit of the LC89052T. All clocks are stopped and the registers are initialized.

- The pins that are available with the low-power settings except for the oscillation amplifier are only the XIN pin and XOUT pin. These can be used to provide the master clock for the DSP and other circuits.

- The pins that are available with the PDOWN[1:0] low-power mode settings except those for the oscillator amplifier and its divider circuit are only the CKOUT, BCK, LRCK, DATAO, SDIN, XIN and XOUT pins. This mode can be used to minimize power consumption during analog data processing.

- When the oscillator amplifier is stopped by the AMPOPR in a low-power mode setup with PDOWN[1:0] or when this circuit is already stopped, it is impossible for the LC89052T to provide a clock output. Thus the AMPOPR takes precedence. Note that the PLLOPR setting is invalid and the PLL circuit is stopped.

- When the low-power mode is set with PDOWN[1:0], it is possible to write to the microcontroller registers. However, all the sub-code Q and channel status that are read are fixed at a low level.

• The table below summaries the low-power modes.

| Tables.1 Low-power Modes |       |        |        |        |        |                                                                           |  |

|--------------------------|-------|--------|--------|--------|--------|---------------------------------------------------------------------------|--|

| Mode                     | PD    | AMPOPR | PLLOPR | PDOWN1 | PDOWN0 | Function                                                                  |  |

| (1)                      | Low   | ×      | ×      | ×      | ×      | Reset (stand-by)                                                          |  |

| (2)                      |       | 0      | 0      | 0      | 0      | Normal operation                                                          |  |

| (3)                      |       | 0      | 1      | 0      | 0      | VCO stopped.                                                              |  |

| (4)                      | Llink | 0      | ×      | 0      | 1      | All circuits except the oscillator amplifier<br>stopped.                  |  |

| (5)                      | High  | 0      | ×      | 1      | 0      | All circuits except the oscillator amplifier and divider circuit stopped. |  |

| (6)                      |       | 1      | 0      | 0      | 0      | Oscillator amplifier stopped.                                             |  |

| (7)                      |       | 1      | 1      | ×      | ×      | All circuits stopped.                                                     |  |

Table8.1 Low-power Modes

• The table below lists the output pin states in the above modes.

| Table 8.2 | Output Pin Sta | tes in Modes ( | 1) to (7) |

|-----------|----------------|----------------|-----------|

|           |                |                |           |

| Output pin | Mode (1) | Mode (2) | Mode (3) | Mode (4) | Mode (5) | Mode (6) | Mode (7) |

|------------|----------|----------|----------|----------|----------|----------|----------|

| AUDIO      | Low      | Output   | Low      | Low      | Low      | Output   | Low      |

| UGPI       | High     | Output   | Output   | Output   | Output   | Output   | Output   |

| CKOUT      | Low      | Output   | Output   | Output   | Output   | Output   | Low      |

| BCK        | Low      | Output   | Output   | Low      | Output   | Output   | L or H   |

| LRCK       | Low      | Output   | Output   | Low      | Output   | Output   | L or H   |

| DATAO      | Low      | Output   | Output   | Low      | Output   | Output   | Low      |

| XOUT       | High     | Output   | Output   | Output   | Output   | High     | High     |

| ERROR      | High     | Output   | High     | High     | High     | Output   | High     |

| E/INT      | Low      | Output   | Low      | Low      | Low      | Output   | Low      |

1) In modes (3), (4), and (5), the clock supplied from the XIN pin is used as the source.

2) Mode (3) applies to the state where an external clock other than CKOUT is supplied to XIN. If XIN pin and CKOUT pin are connected, no clock signals are output in this mode.

3) Mode (6) applies when the PLL circuit is locked.

When the PLL circuit is unlocked, all circuits are stopped since no clock signal is supplied from XIN pin.

4) In mode (7), the states immediatly before the setup is retained.

## 8.3 Clocks

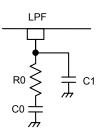

## 8.3.1 PLL (LPF)

- The LC89052T incorporates a VCO (Voltage Controlled Oscillator) that can synchronize with sampling frequencies of 30kHz to 195kHz.

- The locking frequency is selected with PLLCK[1:0]. The VCO circuit can be stopped with PLLOPR.

- The range of input data that can be received differs depending on the settings of PLLCK[1:0].

- The (512/2)fs for the PLLCK[1:0] = "11" in the table below is the state where the PLL itself is synchronized with the 512fs clock, but the clock signal output from the CKOUT pin is 1/2 of the PLL locked frequency, which is 256fs. See the chapter on the of output clock for further information.

- We recommend the 256fs setting with PLLCK[1:0] = "00" for the systems such as portable equipment that need to restrain the consumption electric power. We also recommend the 512fs setting with PLLCK[1:0] = "10" or the (512/2)fs with PLLCK[1:0] = "11" for the systems such as AV amplifiers that require improved performance.

| PLLCK1 | PLLCK0 | PLL lock frequency | Input data reception range |

|--------|--------|--------------------|----------------------------|

| TELORI | TLLONO |                    |                            |

| 0      | 0      | 256fs              | 30k to 195kHz              |

| 0      | 1      | 384fs              | 30k to 108kHz              |

| 1      | 0      | 512fs              | 30k to 108kHz              |

| 1      | 1      | (512/2)fs          | 30k to 108kHz              |

Table 8.3 Input Data Reception Ranges and PLL Lock Frequency Settings

• LPF is the PLL loop filter connection pin. Use the correct recommended resistance and capacitance as values listed in the table below according to the PLLCK[1:0] settings.

| PLLCK1 | PLLCK0 | R0   | C0      | C1       |

|--------|--------|------|---------|----------|

| 0      | 0      | 1500 | 0.047.5 | 0.0000   |

| 0      | 1      | 150Ω | 0.047µF | 0.0068µF |

| 1      | 0      | 1500 | 0.000   | 0.0047.5 |

| 1      | 1      | 150Ω | 0.068µF | 0.0047µF |

Figure 8.2 PLL Loop Filter Configuration

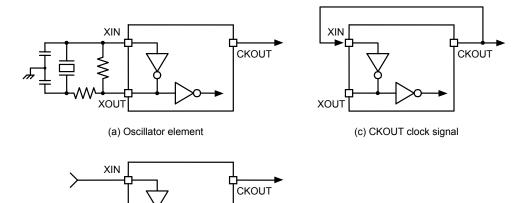

### 8.3.2 Oscillator amplifier (XIN and XOUT)

• The following methods can be used to supply the clock signal to the internal oscillator amplifier.

(b) External clock signal

XOU

Figure 8.3 XIN and XOUT Pin Circuit Configurations

- When you connect an oscillator, use the one with the fundamental frequency. Since the load capacitance depends on the oscillator characteristics, give careful consideration.

- Since the clock supplied to the XIN pin is normally used for the following purposes, the clock signal should be present all the time.

-Externally supplied clock used when the PLL circuit is unlocked and when XIN is the clock source -For calculation of sampling frequencies of the input data

- Input a clock with a frequency of 11.2896M, 12.288M, 16.9344M, 22.5792M, 24.576M, or 33.8688MHz according to the setting of the XISEL[2:0]. Input digital data only after the XISEL[2:0] has been set to match the set frequency and the oscillator or external clock input frequency. The LC89052T may malfunction if data is input when the input frequency and the set frequency are not consistent.

- The LC89052T operates even when the frequency set with the XISEL[2:0] and the frequency supplied to the XIN pin are different. However, continuity at clock switching time and correct input fs calculation are not guaranteed.

- The LC89052T supports a structure in which CKOUT pin is connected to the XIN pin to set XISEL3, requiring no oscillator. However, since only VCO can be used as the source clock, the VCO free-running frequency (10M to 16MHz) is output from the CKOUT pin when the PLL is not locked. Furthermore, input fs calculation and limitation are impossible with this approach. Also, since no clock is supplied to the oscillator amplifier circuit when the VCO is set to stop, the whole system stops. This function is available only for the PLLCK[1:0] = "00" setting, which is 256fs. Other system clock settings might cause malfunction.

- Normally the oscillator amplifier stops automatically when the PLL is locked. It is possible to change to a continuous operation mode with AMPCNT. Setting the LC89052T to the continuous operation mode makes it possible to calculate the input sampling frequency even when the PLL is locked. However, since both the oscillator amplifier clock and the PLL clock signals coexist in that case the user must pay attention and make sure audio quality is not adversely affected.

- The oscillator amplifier can be stopped when not required by setting the AMPOPR. However, the application must maintain its state for at least 10ms until the oscillator stabilizes, when returning from stop to operation mode. After that the LC89052T must be returned to the normal operation mode.

#### 8.3.3 Output clocks (CKOUT, BCK, LRCK)

- The clock source for the clocks output from CKOUT, BCK, and LRCK can be selected from two master clocks, the PLL circuit and the XIN pin.

- Normally, when the PLL circuit is locked, the master clock is switched to the PLL source, and when the PLL circuit is unlocked, the master clock automatically switches to the XIN source. To switch the clock source forcibly, set with OCKSEL. Clock continuity is maintained when the clock source is selected by the locked/unlocked state of the PLL circuit or OCKSEL.

- Clock switching depends on the PLL circuit locked/unlocked state at the time of the register setup. If the PLL source is selected with OCKSEL when the PLL circuit is unlocked, the clock is automatically switched after the PLL circuit is locked.

- When VCO operation is stopped with PLLOPR, XIN becomes the clock source. However, clock continuity cannot be maintained if the operation is stopped with PLLOPR while the PLL circuit is locked. When a low-power mode is set, continuity cannot be maintained if the mode is switched from the locked PLL.

| Table 6.4 Register Settings, TEE States, and the Clock Source |        |          |        |          |  |

|---------------------------------------------------------------|--------|----------|--------|----------|--|

| OCKSEL                                                        | (      | )        |        | 1        |  |

| PLL state                                                     | Locked | Unlocked | Locked | Unlocked |  |

| Clock source                                                  | PLL    | XIN      | XIN    | XIN      |  |

Table 8.4 Register Settings, PLL States, and the Clock Source

- Either the PLL clock or the XIN clock is output from the CKOUT pin. The divided clock of CKOUT is output from the BCK pin and LRCK pin.

- The PLL lock time frequency is set with PLLCK[1:0]. However, it is possible to maintain clock continuity without losing the PLL locked state when switching, in the PLL locked state, from the 512fs setting mode with PLLCK[1:0] = "10" to the (512/2)fs setting with the PLLCK[1:0] = "11", as well as when switching in the reverse direction.

- If you use the following procedure to switch between 512fs and (512/2)fs, the BCK and LRCK output clock continuity can be maintained, and the CKOUT output clock frequency can be held within a narrow band. Other PLLCK[1:0] switching would result in a lock error.

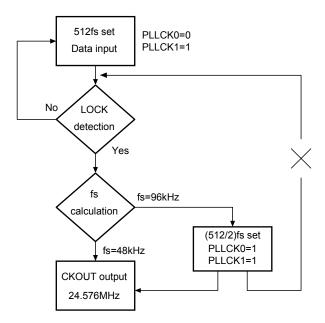

Figure 8.4 Flowchart for CKOUT Output Clock Narrow Band Operation

| • The tables below show the output clocks generated in the XIN and PLL clock source modes. |

|--------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------|

| PLLCK1 | PLLCK0 | XISEL1 | XISEL0 | CKOUT pin  | BCK pin   | LRCK pin |

|--------|--------|--------|--------|------------|-----------|----------|

| 0      | 0      | 0      | 0      | 11.2896MHz | 2.8224MHz | 44.1kHz  |

| 0      | 0      | 0      | 1      | 12.2880MHz | 3.0720MHz | 48kHz    |

| 0      | 0      | 1      | 0      | 16.9344MHz | 4.2336MHz | 66.15kHz |

| 0      | 1      | 0      | 0      | 11.2896MHz | 1.8816MHz | 29.4kHz  |

| 0      | 1      | 0      | 1      | 12.2880MHz | 2.0480MHz | 32kHz    |

| 0      | 1      | 1      | 0      | 16.9344MHz | 2.8224MHz | 44.1kHz  |

| 1      | 0      | 0      | 0      | 11.2896MHz | 2.8224MHz | 44.1kHz  |

| 1      | 0      | 0      | 1      | 12.2880MHz | 3.0720MHz | 48kHz    |

| 1      | 0      | 1      | 0      | 16.9344MHz | 4.2336MHz | 66.15kHz |

| 1      | 1      | 0      | 0      | 11.2896MHz | 2.8224MHz | 44.1kHz  |

| 1      | 1      | 0      | 1      | 12.2880MHz | 3.0720MHz | 48kHz    |

| 1      | 1      | 1      | 0      | 16.9344MHz | 4.2336MHz | 66.15kHz |

AVIOLI O

Table 8.6 XIN Output Clocks in Clock Source Mode (XISEL2 = "1", PLL unlocked state or forced setting)

|        | *      |        |        | ,          |           | 8/       |

|--------|--------|--------|--------|------------|-----------|----------|

| PLLCK1 | PLLCK0 | XISEL1 | XISEL0 | CKOUT pin  | BCK pin   | LRCK pin |

| 0      | 0      | 0      | 0      | 22.5792MHz | 5.6448MHz | 88.2kHz  |

| 0      | 0      | 0      | 1      | 24.5760MHz | 6.1440MHz | 96kHz    |

| 0      | 0      | 1      | 0      | 33.8688MHz | 8.4672MHz | 132.3kHz |

| 0      | 1      | 0      | 0      | 22.5792MHz | 3.7632MHz | 58.8kHz  |

| 0      | 1      | 0      | 1      | 24.5760MHz | 4.0960MHz | 64kHz    |

| 0      | 1      | 1      | 0      | 33.8688MHz | 5.6448MHz | 88.2kHz  |

| 1      | 0      | 0      | 0      | 22.5792MHz | 5.6448MHz | 88.2kHz  |

| 1      | 0      | 0      | 1      | 24.5760MHz | 6.1440MHz | 96kHz    |

| 1      | 0      | 1      | 0      | 33.8688MHz | 8.4672MHz | 132.3kHz |

| 1      | 1      | 0      | 0      | 22.5792MHz | 5.6448MHz | 88.2kHz  |

| 1      | 1      | 0      | 1      | 24.5760MHz | 6.1440MHz | 96kHz    |

| 1      | 1      | 1      | 0      | 33.8688MHz | 8.4672MHz | 132.3kHz |

| Table 8.7 PLL Output C | Clocks in Clock Source M | lode (PLL locked state) |

|------------------------|--------------------------|-------------------------|

|------------------------|--------------------------|-------------------------|

| PLLCK1 | PLLCK0 | CKOUT pin | BCK pin | LRCK pin |

|--------|--------|-----------|---------|----------|

| 0      | 0      | 256fs     | 64fs    | fs       |

| 0      | 1      | 384fs     | 64fs    | fs       |

| 1      | 0      | 512fs     | 64fs    | fs       |

| 1      | 1      | 256fs     | 64fs    | fs       |

• The CKOUT output clock frequency can be set to 1/2 of its normal value with MCKHFO, regardless of the PLL locked/unlocked state. Clock switching with this setting can be done without unlocking the PLL but clock continuity is not maintained.

• If the audio output format is set to bi-phase data output, the BCK output clock frequency is doubled to 128fs when the PLL circuit is locked. However, when unlocked, a BCK signal shown in the above tables is output. Note that the clock continuity is not maintained when this output format is set.

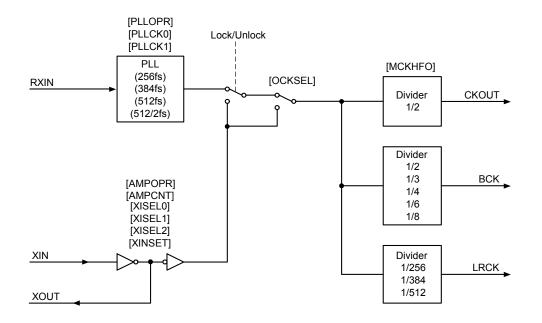

#### 8.3.4 Clock system diagram

- This section shows the relationship between the two types of master clock and clock switching and dividing functions.

- The items in square brackets near the switch and function blocks are the names of write commands.

- Lock/Unlock is switched automatically according to the PLL lock/unlock state.

Figure 8.5 Master Clock System Diagram

8.3.5 Point to notice when switching the clock source

- If an attempt is made to switch the clock source from PLL lock state (oscillator amplifier stopped) to XIN using OCKSEL when a mode in which the results of input fs calculation are reflected in the error flags is specified through FLIMIT, an error signal (H) is temporarily placed at the ERROR pin though the continuity of the clock is preserved. The reason for this follows. When the clock switching is carried out, the oscillator amplifier is activated and the input fs calculation is restarted. At the same time, the old results of fs calculation are reset and consequently, a change in the fs value is recognized when the old fs value is compared with the newly calculated fs value.

- To switch the clock source using OCKSEL while maintaining the state of the ERROR pin when the PLL is locked in this mode setting, it is necessary to put the oscillator amplifier into the continuous mode using AMPCNT.

- Note that when the clock source is switched to XIN from the state where the oscillator amplifier is stopped with the PLL circuit locked, output clocks whose source is XIN start outputting after the oscillator amplifier has started operation. While the PLL is locked, clock source switching from XIN to PLL is carried out immediately. In both cases, clock continuity is maintained.

- When the CKOUT clock is supplied to XIN without using an oscillator or an external clock, the VCO free-running frequency output from the CKOUT pin with the PLL unlocked is somewhere between 10M and 16MHz. Clock signals created by dividing CKOUT are output from BCK and LRCK pins. However, these clock frequencies vary depending on the LC89052T sample and fluctuate depending on supply voltage and operating environments. Therefore, the frequency is not fixed. You need to take care when using the CKOUT, BCK, and LRCK clocks while the PLL circuit is unlocked.

## 8.4 Data Input and Output

8.4.1 Bi-phase mark modulated digital data input (RXIN)

- RXIN is an input pin for bi-phase mark modulated digital data.

- The RXIN pin supports TTL levels. This allows a 5V-optical reception module to be connected directly.

#### 8.4.2 Setting the bi-phase mark modulated input data reception range

- The LC89052T allows the user to set the upper limit sampling frequency of the receivable input data and can receive input data of specific sampling frequencies.

- These are set with FLIMIT and FSSEL[3:0].

- However, this function does not work in modes where the reception range is not limited with the FLIMIT.

| FSSEL3 | FSSEL2 | FSSEL1 | FSSEL0 | Input data reception range |

|--------|--------|--------|--------|----------------------------|

| 0      | 0      | 0      | 0      | 32kHz to 96kHz             |

| 0      | 0      | 0      | 1      | 32kHz only                 |

| 0      | 0      | 1      | 0      | 44.1kHz only               |

| 0      | 0      | 1      | 1      | 48kHz only                 |

| 0      | 1      | 0      | 0      | 88.2kHz only               |

| 0      | 1      | 0      | 1      | 96kHz only                 |

| 0      | 1      | 1      | 0      | 44.1kHz or 88.2kHz only    |

| 0      | 1      | 1      | 1      | 48kHz or 96kHz only        |

| 1      | 0      | 0      | 0      | 32kHz or 44.1kHz or 48kHz  |

| 1      | 0      | 0      | 1      |                            |

|        |        |        |        | Reserved                   |

| 1      | 1      | 1      | 1      |                            |

#### Table 8.8 Input Data Reception Range (FS4XIN = "0")

- The notation 32kHz to 96kHz means 32k, 44.1k, 48k, 64k, 88.2k, or 96kHz.

- The table above only applies when the input fs calculation mode (FS4XIN) is set to "0". When FS4XIN is set to "1", input data reception range is doubled.

- Input data out of the set range is treated as an error, in which case the XIN source clock is output. At this time, the DATAO output data is subject to the RDTSEL setting.

- When the PLL follows a source with a variable fs, such as a CD player with variable pitch control, from the state where the oscillator amplifier is stopped while PLL is locked, the fs is not calculated. As a result, an input frequency not within the set range is not regarded as an error. The oscillator amplifier must be set to a continuous operation mode to support such sources.

- The reception range of input data can not be limited when setting up a system where no oscillator is required as XIN and CKOUT are connected, because fs calculation is impossible in that case.

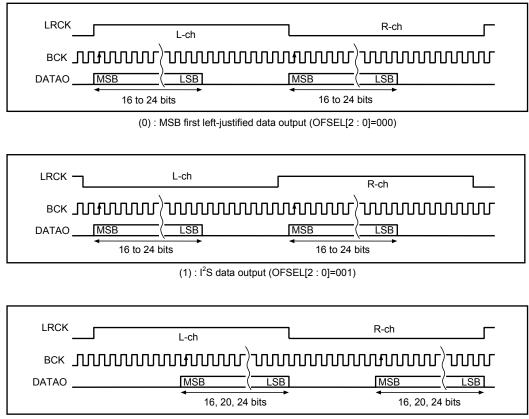

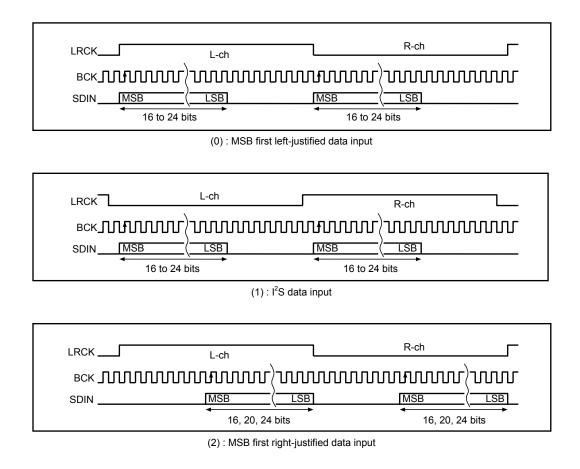

8.4.3 Output data formats: normal mode (DATAO)

- The output format of after-demodulation audio data must be set with OFSEL[2:0].

- In the format shown below, the input data only within the audio data range is output.

- BCK, LRCK, and DATAO are output in synchronization with the rising edge of CKOUT. DATAO is output in synchronization with the falling edge of BCK.

- Generation of output data starts at the LRCK edge immediately after the ERROR output turns low.

- The low level is output all the time except for the effective bit length of output data.

(2) : MSB first right-justified data output (OFSEL[2 : 0]=010, 011 or 100)

Figure 8.6 Data Output Timing (Normal Mode)

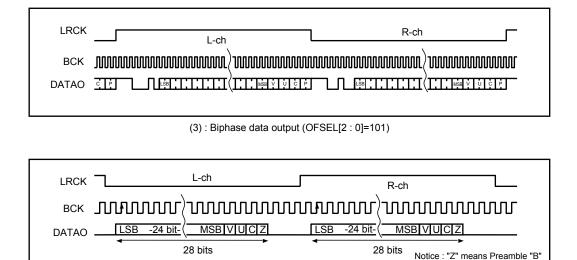

#### 8.4.4 Output data formats: special mode (DATAO)

- The output format of after-demodulation audio data must be set with OFSEL[2:0].

- In the format shown below, input data information except the audio data is output as well.

- BCK, LRCK, and DATAO are output in synchronization with the rising edge of CKOUT. DATAO is output in synchronization with the falling edge of BCK.

- Generation of output data starts at the LRCK edge immediately after the ERROR output turns low.

- (3) as bi-phase data output, the input bi-phase data is output in synchronization with 128fs clock BCK and fs clock LRCK. However, BCK in PLL unlocked state is set to the 64fs clock.

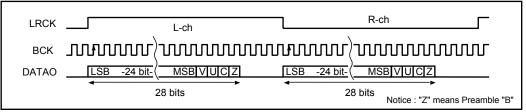

- As for NRZ data output in (4), (5), 28bits are output. 4 bits of validity (V), user data (U), channel status (C) and also preamble B (Z) plus 24 bits of LSB first audio data. H is output as Z bit in the frames (L-ch and R-ch) whose preamble B is confirmed.

- The low level is output all the time except for the effective bit length of the NRZ data output.

(4) : NRZ data I<sup>2</sup>S output (OFSEL[2 : 0]=110)

(5) : NRZ data LSB first left-justified output (OFSEL[2:0]=111)

Figure 8.7 Data Output Timing (Special Mode)

8.4.5 Serial audio data input format (SDIN)

- SDIN is the pin that inputs serial digital audio data such as A/D converter output.

- Data input to the SDIN can be output from the DATAO pin. The data to be input to SDIN must synchronize with BCK and LRCK.

- Given below shows an example of a serial audio data input timing.

- Except for a special setting, we suggest the SDIN input format be consistent with the format of output data after demodulation.

Figure 8.8 Example of Serial Audio Data Input Timing

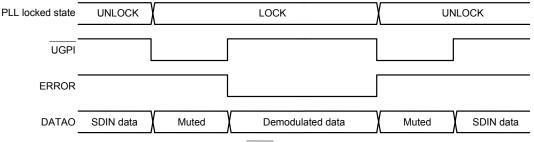

### 8.4.6 Output data switching (SDIN, DATAO)

- The DATAO pin outputs the demodulated data when the PLL circuit is locked and the SDIN input data when the PLL circuit is unlocked. This switching is performed automatically according to the locked/unlocked state of the PLL circuit.

- The data input to SDIN must be synchronized with CKOUT, BCK, and LRCK clocks when XIN is the clock source.

- The SDIN input data is output to DATAO by setting RDTSTA, regardless of the PLL circuit locked/unlocked state. In this case, the CKOUT, BCK, and LRCK clocks are also switched to the XIN clock source. The switch occurs in synchronization with the LRCK edge after RDTSTA setup.

- The DATAO output data can also be forcibly muted by setting RDTMUT. The muting processing is output in synchronization with the LRCK edge after RDTMUT setup.

- The DATAO output can also be muted in the PLL unlocked state by RDTSEL setup.

- These setups take priority in the following order: RDTSEL < RDTSTA < RDTMUT.

- When XIN is set to be the clock source with OCKSEL, the PLL circuit operates as long as PLL operation is not stopped with PDOWN[1:0] or PLLOPR. In this mode the state of the PLL circuit is always output from the ERROR pin. Information processed regardless of the PLL state can be read out over the microcontroller interface.

UGPI : When the clock switching transition period signal is selected

Figure 8.9 Timing Chart for DATAO Output Data Switching (When RDTSEL is set to "0")

8.4.7 Calculation of input data sampling frequency

- The input data sampling frequency is calculated using the XIN clock.

- Normally, in modes where the oscillator amplifier is automatically stopped when the PLL circuit is locked, the calculation is done during the error period associated with ERROR and completed, and the value is retained when the oscillator amplifier is stopped. Therefore, after the calculation is confirmed, the value does not change until the PLL circuit is unlocked.

- In continuous operation mode, the oscillator amplifier continuously repeats calculations.

- The calculation result can be read out from CCB address 0xEC or output registers DO4 to DO6. However, note that while the PLL can synchronize with data of 32k to 192kHz, fs calculation mode can be selected from two modes: 32k to 96kHz calculation mode and 64k to 192kHz calculation mode. These modes are switched by FS4XIN. It is not possible to monitor the fs calculation result of 32k to 192kHz in the same mode.

- If a system where the XIN and CKOUT pins are connected and no oscillator is required is being setup, the fs calculation result will always be "out of range".

## 8.5 Error Output Processing (ERROR)

8.5.1 Lock error and data error output

• The ERROR pin outputs high level when a PLL lock error happens or an error occurs in the transmitted data.

#### 8.5.2 PLL lock error

- The PLL circuit will unlock the input data which does not conform to the bi-phase modulation rules or can not detect the preamble B, M, or W.

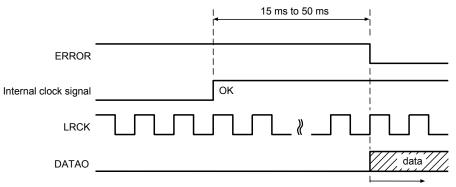

- ERROR turns to H when a PLL lock error occurs. When data modulation returns to the normal state, it remains high for 15m to 50ms, before going to the to low level.

- The output of ERROR is synchronized with LRCK.

#### 8.5.3 Input data transmission error

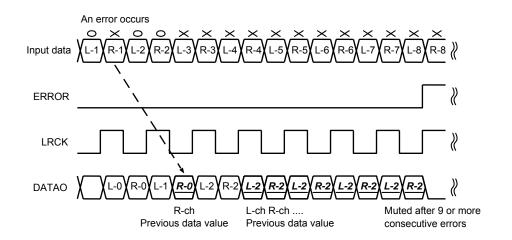

- An odd number of input parity errors are detected from the parity bits in the input data.

- When input parity errors occur 9 times or more in a row, ERROR turns to high level. After the high level is held for 15m to 50ms following the detection of the PLL lock state, the ERROR returns to low level.

- When 8 or fewer input parity errors occur consecutively, an error is output only for intervals between sub-frames where the errors occurred when non-PCM data is recognized by data delimiter bit 1 in the channel status. In this case, the parity error flag is not output when PCM data is recognized.

#### 8.5.4 Other errors

- Even when ERROR has turned to low, the LC89052T always acquires bits 24 to 27 (sampling frequency) of the channel status and compares the current data with the data of the previous block. If any differences are found, ERROR is immediately set to high and processes similar to those for the PLL lock error are carried out.

- Similarly, even when the mode that reflects fs calculation results in an error flag is set with FLIMIT, the fs calculation results are always compared. Here as well, if a disparity occurs in the data, ERROR is immediately turned to high, and the processing similar to that for the PLL lock error is carried out.

#### 8.5.5 Data processing upon occurrence of errors

- This section describes the data processing performed when an error occurs. When up to 8 consecutive input parity errors occur, if the transmitted data is PCM audio data, the data is replaced with the corresponding left and right channel data from the immediately preceding frame. However, if the transmitted data is non-PCM data, the error data is output as it is. Non-PCM data is based on the data that is detected before the input parity error has occurred, and is the data for which the channel status bit 1 non-PCM data detection bit is "1". Non-PCM data refers to the data established when bit 1 non-PCM data detection bit of the channel status turns to high based on the data detected prior to the occurrence of the input parity error.

- The output data when a PLL lock error or 9 or more parity errors occur consecutively are muted.

- For the channel status data, the data for the previous block held in 1 bit units is output when an 8 or less parity error occurs successively.

| Table 6.9 Data Trocessing when Errors occur |                |                        |                        |                        |  |

|---------------------------------------------|----------------|------------------------|------------------------|------------------------|--|

| Data and detection flags                    | PLL lock error | Input parity error (a) | Input parity error (b) | Input parity error (c) |  |

| DATAO output pin                            | Low            | Low                    | Previous data          | Output                 |  |

| Input fs calculation                        | Low            | Low                    | Output                 | Output                 |  |

| Channel status data                         | Low            | Low                    | Previous data          | Previous data          |  |

| Sub-code Q data                             | Low            | Low                    | Output                 | _                      |  |

| Table 8.9 Data Processing when Errors Occur | Table 8.9 | Data | Processing | when | Errors | Occur |

|---------------------------------------------|-----------|------|------------|------|--------|-------|

|---------------------------------------------|-----------|------|------------|------|--------|-------|

1) Input parity error (a): When 9 or more consecutive parity errors occur

2) Input parity error (b): When up to 8 consecutive parity errors occur in audio data

3) Input parity error (c): When up to 8 consecutive parity errors occur in non-PCM burst data

• The figure below presents an example of the data processing performed when a parity error occurs.

Figure 8.10 Data Processing Example for a Parity Error (When PCM data is received)

### 8.5.6 Processing during error recovery

- When the preambles B, M, and W are detected, the PLL circuit goes to the locked state and data demodulation starts.

- The DATAO output data is output on the first LRCK edge after ERROR goes low.

Output starts at the LRCK edge immediately following the fall of the ERROR flag.

#### Figure 8.11 Data Processing when Data Demodulation Starts

#### 8.6 Channel Status Data Output

8.6.1 Data delimiter bit 1 output (AUDIO)

• AUDIO outputs channel status bit 1, which indicates whether or not the input bi-phase data is PCM audio data.

| AUDIO pin | Output conditions               |

|-----------|---------------------------------|

| Low       | PCM audio data (CS bit 1 = low) |

| High      | Non-PCM data (CS bit 1 = high)  |

## 8.6.2 Emphasis information output (E/INT)

• E/INT is shared by the microcontroller interface interrupt function. However, in the initial state, it outputs the presence or absence of emphasis with a time constant of 50/15µs for use in consumer products or broadcast studios.

#### Table 8.11 E/INT Output

| E/INT pin | Output conditions    |  |  |  |  |  |

|-----------|----------------------|--|--|--|--|--|

| Low       | Low No pre-emphasis  |  |  |  |  |  |

| High      | 50/15µs pre-emphasis |  |  |  |  |  |

## 8.7 User General Definable Output Port (UGPI)

- UGPI pin is a user-definable output port that can be selected for the following functions. —Microcontroller interface register output

- -Signal output during clock switching transitional period

- Selection is done by GPISEL. The initial setting is set to the microcontroller interface register GPIDAT. However, the initial setting of this GPIDAT register is "1", so high level is output from the  $\overline{UGPI}$  pin.

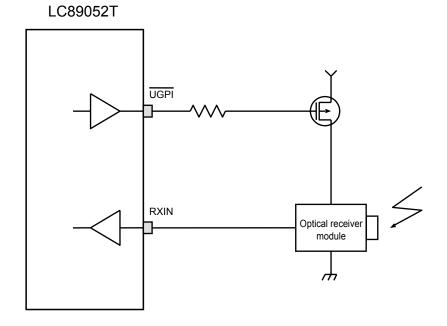

- 8.7.1 Microcontroller interface register output (Example of signals that control low power of optical module)

- This section describes an example in which UGPI is used as a power supply control signal for an optical module as a microcontroller interface register output.

- (a) Connect the  $\overline{\text{UGPI}}$  output to the power supply control switch of the optical module.

- (b) After a reset due to PD, microcontroller interface register output is selected as the initial state of UGPI. As a result, the default GPIDAT value is output.

- (c) After a reset, the initial value of GPIDAT is set to "1", so H is output from  $\overline{\text{UGPI}}$ . Therefore, after a reset, the control switch is turned off, and data is not supplied from the optical module.

- (d) The application must set GPIDAT to "0" to have the optical module supply data. That is, the UGPI output can be controlled with GPIDAT, and the current drain can be minimized when the optical module is not used.

Figure 8.12 UGPI Output Example (Power supply control signal for an optical module)

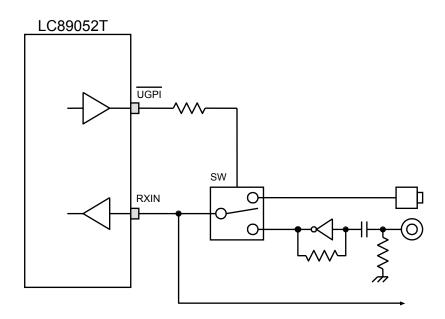

- 8.7.2 Microcontroller interface register output (Example of signals that control switching of Digital data input)

- UGPI, when used as a microcontroller interface register output, can be used as a control signal that switches the digital data input.

- When increasing the number of digital data input systems, an peripheral circuit such as an input selector and a control signal for that selector is required. The number of digital data input ports can be increased to two systems without having to provide a control signal from the microcontroller by using the UGPI output.

- Note that after a reset, the initial value of GPIDAT is set to "1", so high level is output from  $\overrightarrow{\text{UGPI}}$ . Be aware that the initial value of the switching signal is high level.

Figure 8.13 UGPI Output Example (Signal that controls the switching of data input)

8.7.3 Output of clock switch transition signal

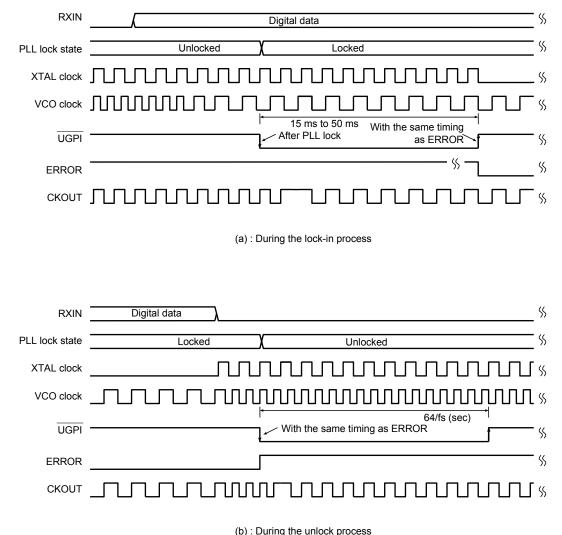

- This section describes the operation when UGPI is selected as an output pin during the clock switching transitional period.

- A clock switching transitional period signal is a signal that reports a clock switching condition to external circuits due to a change in the PLL locked/unlocked state. This signal allows the application to grasp the PLL lock state transitions and the timing of change in the clock signals. This setup is selected with GPISEL.

- After setting GPISEL, high level is output from UGPI. Low pulse is output when the output clock changes due to the change in the PLL circuit locked/unlocked state.

- In the lock in process, the UGPI low pulse rises with the word clock generated by the XIN clock after input data is detected and PLL is locked. After a certain period, it rises with the same timing as ERROR.

- In the unlock process, the UGPI low pulse falls at the same timing as ERROR, which is the PLL lock detecting signal and it rises after the word clocks generated from the XIN clock are counted for a certain period.

Figure 8.14 Clock Switching Timing

## 9 Microcontroller Interface (E/INT, CE, CL, DI, DO)

## 9.1 Interrupt Output (E/INT)

- The E/INT pin can be set to function as the microcontroller interface interrupt output by setting INTSEL.

- An interrupt output is issued when a change occurs in the PLL lock state or output data information.

- The interrupt output consists of registers for selecting interrupts, the E/INT pin, which outputs those state transitions, and registers that store interrupt related data.

- The E/INT pin normally is at the low level, and goes to the high level when an interrupt occurs. After going to high level, it returns to low level according to the INTOPF setting.

- INTOPF determines whether the E/INT pin holds the high pulse for a certain period and is then cleared (returning to low), or the E/INT pin is cleared at the same time as the output register is read.

- The interrupts can be selected from the sources listed below. More than one items can be set as interrupt sources at the same time by setting the contents of CCB address 0xEA. The interrupt signal is issued whenever any one of the interrupt sources arises.

E/INT output = (selected interrupt 1) + (selected interrupt 2) + ... + (selected interrupt n)

| No. | Command | Description                                                           |  |  |  |

|-----|---------|-----------------------------------------------------------------------|--|--|--|

| 1   | INTERR  | Output when the state of the ERROR pin changes.                       |  |  |  |

| 2   | INTPCM  | Output when the state of the AUDIO pin changes.                       |  |  |  |

| 3   | INTEMP  | put when the state of the pre-emphasis information changes.           |  |  |  |

| 4   | INTVFL  | tput when the state of the validity flag changes.                     |  |  |  |

| 5   | INTFSC  | Output when the input fs calculation result changes.                  |  |  |  |

| 6   | INTCSF  | Output when the first 48 bits of the channel status data are updated. |  |  |  |

| 7   | INTSQY  | Output when the sub-code Q data can be read out.                      |  |  |  |

#### Table 9.1 Interrupt Source Settings

- The contents of the set interrupt source are stored in output registers DO1 to DO7 at CCB address 0xEB when an interrupt source arises. However, the registers read for source items 1 through 4 output the current state of those sources regardless of the E/INT output. For source items 5 through 7, the states are stored when an interrupt source arises.

- To monitor interrupt source item 5 in the PLL locked state, the oscillator amplifier must be set to continuous operation mode, since the oscillator amplifier clock is used.

- When the LC89052T is set to the mode in which a H pulse is output from E/INT when an interrupt source occurs, the pulse width of each interrupt source is somewhere between 1/2 fs and 3/2 fs.

- The action to clear the E/INT pin output simultaneously with the reading of the output registers following the occurrence of an interrupt is carried out immediately after the output registers at 0xEB are set up. Since, however, the data associated with interrupt sources 6 and 7 is updated at the intervals listed below, it must be read promptly whenever the corresponding interrupt sources are detected.

| Tuble 9.2 Dua Opuate Inter tais (Input is - 52k to 90kHz) |                                          |  |  |  |  |  |

|-----------------------------------------------------------|------------------------------------------|--|--|--|--|--|

| Data                                                      | Update interval                          |  |  |  |  |  |

| Channel status and preamble B                             | 2ms to 6ms                               |  |  |  |  |  |

| Sub-code Q data                                           | 13.3ms (fs = 44.1kHz), 6.65ms (2x speed) |  |  |  |  |  |

#### Table 9.2 Data Update Intervals (Input fs = 32k to 96kHz)

#### 9.2 CCB Addresses

- Setting various functions, and reading and writing data must be carried out though the microcontroller interface.

- The data through the microcontroller interface conforms to the Sanyo's original serial bus format (CCB). However, the three-state is employed instead of open-drain as the data output type.

- Data must be input or output after the CCB address is input. See the I/O timing chart for details of the data input and output timing.

| Tuble 9.5 Register 1/0 Content and CCD Addresses |       |             |    |    |    |    |    |    |    |    |

|--------------------------------------------------|-------|-------------|----|----|----|----|----|----|----|----|

| Register content                                 | R/W   | CCB address | B0 | B1 | B2 | B3 | A0 | A1 | A2 | A3 |

| Function settings data 1                         | Write | 0xE8        | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 1  |

| Function settings data 2                         | Write | 0xE9        | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 1  |

| Function settings data 3                         | Write | 0xEA        | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  |

| Interrupt data output                            | Read  | 0xEB        | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 1  |

| Fs value, CS data output                         | Read  | 0xEC        | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 1  |

| Sub-code Q data output                           | Read  | 0xED        | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1  |

#### 9.3 Data Write Procedure

- The bit length of data input is 16 bits.

- After inputting one of the CCB addresses data 0xE8 to 0xEA, set CE to the high level.

- Input data is taken in on the rising edge of CL.

- The bits marked "0" in the table are reserved bits. 0 (zero) must be input to these bits.

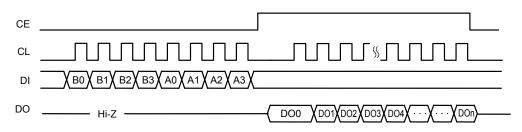

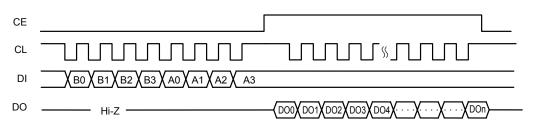

#### 9.4 Data Read Procedure

- Read data is output from DO. DO goes to the high-impedance state when CE is low, and output starts on the CE rising edge that follows the output setup with the CCB address. After that, the DO pin is returned to the high-impedance state when CE is set low.

- The number of data bits read differs with the data to be read. Interrupt data (0xEB) is 8 bits long, the channel status related data (0xEC) is 56 bits long, and the sub-code Q data (0xED) is 88 bits long. However, it is not necessary to read out all data bits. During readout, an application can stop providing CL input and set CE low and still have acquired the data read up to that point. For example, when reading the sub-code Q data, if the CRC flags are read and the data is found no good, there is no need to read the subsequent data.

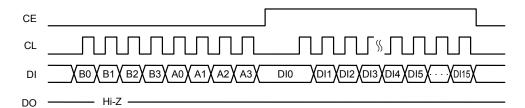

Figure 9.1 Input Timing Chart (Normal low clock)

Figure 9.2 Input Timing Chart (Normal high clock)

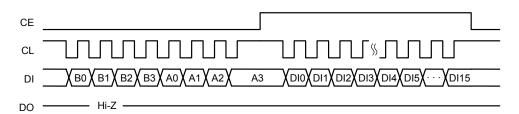

Figure 9.3 Output Timing Chart (Normal low clock)

Figure 9.4 Output Timing Chart (Normal high clock. It is necessary to read DO0 with a port.)

• In the output timing shown in figure 9.4, data is allocated so that there are no problems even if the output register DO0 is not read. See the read register table for details.

## 9.6 Write Registers

9.6.1 List of write registers

• The table shows the write registers.

| Table 9.4 Write Register Map |        |        |        |  |  |  |  |

|------------------------------|--------|--------|--------|--|--|--|--|

| Input register               | 0xE8   | 0xE9   | 0xEA   |  |  |  |  |

| DIO                          | SYSRST | GPISEL | INTOPF |  |  |  |  |

| DI1                          | 0      | GPIDAT | 0      |  |  |  |  |

| DI2                          | PDOWN0 | FLIMIT | 0      |  |  |  |  |

| DI3                          | PDOWN1 | FS4XIN | 0      |  |  |  |  |

| DI4                          | PLLOPR | FSSEL0 | 0      |  |  |  |  |

| DI5                          | PLLCK0 | FSSEL1 | 0      |  |  |  |  |

| DI6                          | PLLCK1 | FSSEL2 | 0      |  |  |  |  |

| DI7                          | MCKHFO | FSSEL3 | 0      |  |  |  |  |

| DI8                          | 0      | OFSEL0 | INTSEL |  |  |  |  |

| DI9                          | AMPOPR | OFSEL1 | INTERR |  |  |  |  |

| DI10                         | AMPCNT | OFSEL2 | INTPCM |  |  |  |  |

| DI11                         | OCKSEL | 0      | INTEMP |  |  |  |  |

| DI12                         | XISEL0 | RDTSEL | INTVFL |  |  |  |  |

| DI13                         | XISEL1 | RDTSTA | INTFSC |  |  |  |  |

| DI14                         | XISEL2 | RDTMUT | INTCSF |  |  |  |  |

| DI15                         | XISEL3 | 0      | INTSQY |  |  |  |  |

• The shaded columns indicate reserved bits. Input 0 (zero) to these bits.

## 9.6.2 Details of write data

| Table 9.5 Input Register Function Settings 1: System Settings (0xE8) |        |        |        |        |        |        |        |

|----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| DI7                                                                  | DI6    | DI5    | DI4    | DI3    | DI2    | DI1    | DI0    |

| MCKHFO                                                               | PLLCK1 | PLLCK0 | PLLOPR | PDOWN1 | PDOWN0 | 0      | SYSRST |

| DI15                                                                 | DI14   | DI13   | DI12   | DI11   | DI10   | DI9    | DI8    |

| XISEL3                                                               | XISEL2 | XISEL1 | XISEL0 | OCKSEL | AMPCNT | AMPOPR | 0      |

|                                                                      |        |        |        |        |        |        |        |

Table 9.5 Input Register Function Settings 1: System Settings (0xE8)

| SYSRST:     | System reset                                                                                |

|-------------|---------------------------------------------------------------------------------------------|

|             | 0: No reset performed (initial value)                                                       |

|             | 1: Reset all circuits other than the command registers.                                     |

| PDOWN[1:0]: | Low power mode settings (Only specific functions are enabled.)                              |

|             | 00: Normal operation (initial value)                                                        |

|             | 01: Only the oscillator amplifier is enabled.                                               |

|             | 10: Only the oscillator amplifier and the output clock divider are enabled.<br>11: Reserved |

|             |                                                                                             |

| PLLOPR:     | PLL (VCO) operate/stop setting                                                              |

|             | 0: Operate (initial value)                                                                  |

|             | 1: Stop                                                                                     |

| PLLCK[1:0]: | Clock frequency setting in the PLL locked state                                             |

|             | 00: 256fs (initial value)                                                                   |

|             | 01: 384fs                                                                                   |

|             | 10: 512fs                                                                                   |

|             | 11: $(512/2)$ fs = 256fs                                                                    |

| MCKHFO:     | Frequency setting of CKOUT output clock                                                     |

|             | 0: 1/1 output (initial value)                                                               |

|             | 1: 1/2 output                                                                               |

|             | *                                                                                           |

- It is possible to maintain clock continuity when switching from the 512fs setting with PLLCK[1:0] = "10" to the (512/2) fs setting with PLLCK[1:0] = "11", and switching vice versa without entering the PLL lock error state.

- For systems that must minimize power consumption such as portable equipment, we recommend the PLLCK[1:0] = "00" (256fs) setting. For systems that require improved performance such as AV amplifiers, we recommend the PLLCK[1:0] = "10" (512fs) or PLLCK[1:0] = "11" (512/2fs) setting.

| AMPOPR:     | Oscillator amplifier operate / stop setting<br>0: Operate (initial value)<br>1: Stop                                                                                                                                                                                         |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMPCNT:     | Oscillator amplifier state setting<br>0: Automatically stop in the PLL locked state (initial value)<br>1: Always operate continuously                                                                                                                                        |

| OCKSEL:     | Clock source setting<br>0: Use the XIN clock as the source when the PLL is unlocked. (initial value)<br>1: Use the XIN clock as the source regardless of the PLL state.                                                                                                      |

| XISEL[3:0]: | XIN input frequency setting<br>0000: 11.2896MHz (initial value)<br>0001: 12.288MHz<br>0010: 16.9344MHz<br>0011: Reserved<br>0001: 22.5792MHz<br>0010: 24.576MHz<br>0010: 33.8688MHz<br>0011: Reserved<br>1xxx: Must be set when the CKOUT pin and the XIN pin are connected. |

| DI7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DI6                                                                                                                                                                                                                                                                                                                                                                | e 9.6 Input Reg                                                                                                                                                                                                                             | DI4    | DI3    | Data Settings (0 | DI1    | DI0    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------------|--------|--------|--|

| FSSEL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FSSEL2                                                                                                                                                                                                                                                                                                                                                             | FSSEL1                                                                                                                                                                                                                                      | FSSEL0 | FS4XIN | FLIMIT           | GPIDAT | GPISEL |  |

| DI15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DI14                                                                                                                                                                                                                                                                                                                                                               | DI13                                                                                                                                                                                                                                        | DI12   | DI11   | DI10             | DI9    | DI8    |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RDTMUT                                                                                                                                                                                                                                                                                                                                                             | RDTSTA                                                                                                                                                                                                                                      | RDTSEL | 0      | OFSEL2           | OFSEL1 | OFSEL1 |  |

| GPIS<br>GPID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0:<br>1:<br>AT: <u>U</u>                                                                                                                                                                                                                                                                                                                                           | UGPI pin setting         0: Outputs the microcontroller interface register state. (initial value)         1: Outputs clock switching transitional period signal.         UGPI output setting (valid only when register output mode is set.) |        |        |                  |        |        |  |

| FLIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>0: Outputs the low level.</li> <li>1: Outputs the high level. (initial value)</li> <li>FLIMIT: Input data reception limit setting</li> <li>0: Reception is not limited. All data within the PLL locked range can be received. (initial value)</li> <li>1: Reception is limited. The input fs calculation result is reflected in the error flag</li> </ul> |                                                                                                                                                                                                                                             |        |        |                  |        |        |  |