LC8991

### NTSC CCD 1H Delay Line

### Overview

The Sanyo LC8991 is a 1H delay line for NTSC television systems.

### **Features**

- Single 9 V power supply

- · Low clock input voltage

- 1H delay signal can be obtained with low-pass filter and 7.16 MHz clock input

- Minimum number of external components required because timing generator, driver, bias generator and output amplifier are built in

- 8-pin DIP (Small package)

### **Functions**

- 453 stages CCD shift register

- CCD drive circuit

- · Auto-bias circuit

- Sync tip clamp circuit

Sample-and-hold circuit

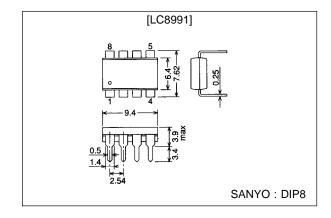

# **Package Dimensions**

unit: mm

#### 3001B-DIP8

# **Specifications**

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions | Ratings     | Unit |

|-----------------------------|---------------------|------------|-------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |            | 11          | V    |

| Allowable power dissipation | Pd max              |            | 500         | mW   |

| Operating temperature       | Topr                |            | -10 to +60  | ∞    |

| Storage temperature         | Tstg                |            | -55 to +125 | ∞    |

# LC8991

### **Electrical Characteristics**

| Parameter                                                                             | Symbol              | Conditions              | min  | typ   | max  | Unit  |  |

|---------------------------------------------------------------------------------------|---------------------|-------------------------|------|-------|------|-------|--|

| DC Characteristics at Ta = 25°C, V <sub>DD</sub> = 9 V, CLOCK = 7.15909 MHz; 0.3 Vp-p |                     |                         |      |       |      |       |  |

| Supply voltage                                                                        | V <sub>DD</sub>     |                         | 8.5  | 9.0   | 9.5  | V     |  |

| Supply current                                                                        | I <sub>DD</sub>     |                         |      | 16.5  | 20.0 | mA    |  |

| DC output voltage                                                                     | $V_{GG}$            |                         |      | 13.5  |      | ٧     |  |

|                                                                                       | OUT                 |                         |      | 3.1   |      | V     |  |

|                                                                                       | VOB                 |                         |      | 4.5   |      | V     |  |

|                                                                                       | VID IN              |                         |      | 2.8   |      | V     |  |

|                                                                                       | CLK                 |                         |      | 2.0   |      | V     |  |

|                                                                                       | COMP                |                         |      | 2.7   |      | V     |  |

| AC Characteristics at Ta = 25°C, V <sub>DD</sub> = 9 V, CLOCK = 7.15909 MHz; 0.3 Vp-p |                     |                         |      |       |      |       |  |

| Maximum input voltage                                                                 | V <sub>IN</sub> max |                         |      | 0.5   | 0.7  | Vp-p  |  |

| Voltage gain                                                                          | VG                  | Input: 15 kHz, 0.5 Vp-p | 6    | 9     | 11   | dB    |  |

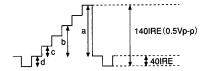

| Linearity                                                                             | L6                  | b/a, Note 1             | 56   | 60    | 64   | %     |  |

|                                                                                       | L2                  | c/a, Note 1             | 18   | 20    | 22   | %     |  |

|                                                                                       | LS                  | d/a, Note 1             | 37   | 40    | 43   | %     |  |

| Frequency response                                                                    | Gf                  | Note 2                  | -3.0 | -2.3  |      | dB    |  |

| Noise                                                                                 | V <sub>NO</sub>     | 3.4 MHz bandwidth       |      | 1.1   |      | mVrms |  |

| Clock input voltage                                                                   | Eck                 |                         | 0.1  | 0.3   | 1.0  | Vp-p  |  |

| Output impedance                                                                      | Z <sub>O</sub>      |                         |      | 520   |      | Ω     |  |

| Delay time                                                                            | to                  |                         |      | 63.42 |      | μs    |  |

Note 1) Linearity test

Input: 5 step staircase signal

Note 2) Frequency response test

Input = 0.5 Vp-p sine wave (2.4 MHz)/(20 kHz)

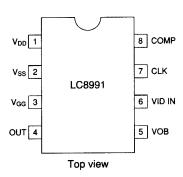

# **Pin Assignment**

# **Pin Description**

|         | 1               | T                              |  |

|---------|-----------------|--------------------------------|--|

| Pin No. | Symbol          | Function                       |  |

| 1       | $V_{DD}$        | Power supply                   |  |

| 2       | V <sub>SS</sub> | GND                            |  |

| 3       | V <sub>GG</sub> | V <sub>GG</sub> voltage output |  |

| 4       | OUT             | Delay signal output            |  |

| 5       | VOB             | Feedback output                |  |

| 6       | VID IN          | Signal input                   |  |

| 7       | CLK             | Clock input                    |  |

| 8       | COMP            | Duty cycle compensation output |  |

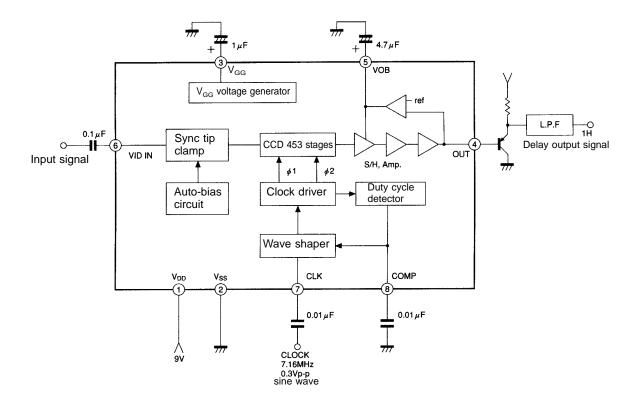

### **Block Diagram**

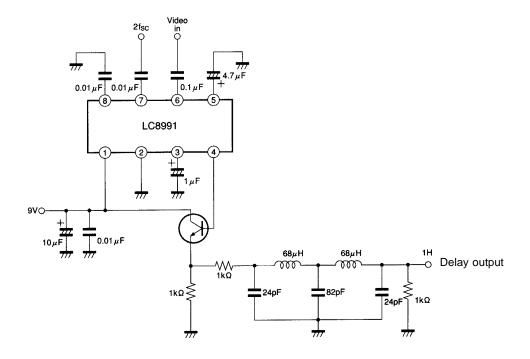

# **Sample Application Circuit**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of January, 1997. Specifications and information herein are subject to change without notice.