No.3215B

LC8955

## CD-I Format ADPCM Data Replay LSI

### Overview

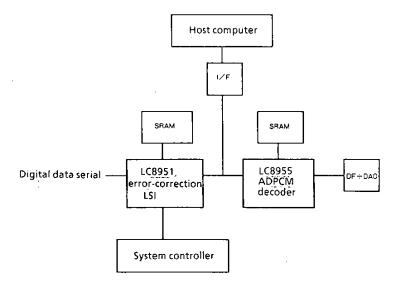

The Sanyo LC8955 is a stereo/mono replay LSI for CD-I format ADPCM data. In addition to an ADPCM decoding circuit, the LC8955 also incorporates a DMA interface, buffer RAM interface and a D/A converter serial interface.

The LC8955 interfaces directly with the Sanyo LC8951 Real-time Error-correction and Host Interface Processor, allowing a CD-I replay system to be configured easily.

The LC8955 is designed to operate with a host microprocessor which sets the operating mode. It operates from a single 5V supply, and is available in 80-pin plastic QIPs.

#### **Features**

- · Real-time ADPCM decoder LSI

- · Direct interface to Sanyo's LC8951 error-correction LSI for high-speed data transfer

- · Data transfer under program or DMA control

- · Independent data and control busses in auto-request transfer

- · 8K byte external static RAM interface

- · Buffers up to 64 ADPCM sound groups in external RAM

- · DAC interface circuit

- · 80-pin plastic QIP

### **Functional Description**

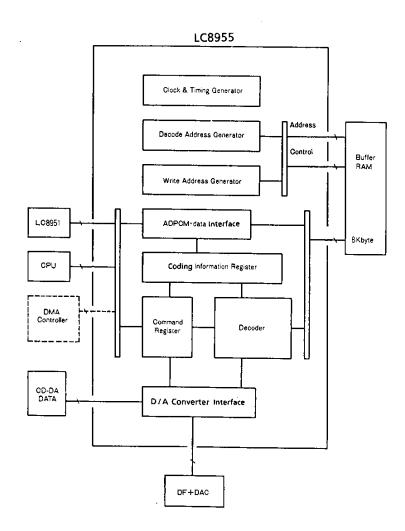

The LC8955 is divided into three major functional blocks.

### ADPCM Input Block

The ADPCM input block has three data input modes, selected by setting internal registers.

① Auto-request transfer

Data is transferred automatically into the LC8955's data port without CPU intervention. A number of handshaking signals control data transfer. The input device can be an LC8951 Real-time Error-correction and Host Interface Processor or another CD-ROM output device.

Program transfer

The CPU writes each byte of data directly into the LC8955 under program control. Data is transferred using the CPU data bus.

3 DMA transfer

Data is written into the LC8955 by an external DMA controller using the CPU data bus. Up to 64 ADPCM sound groups can be written to an external 8K byte buffer RAM. One sound group consists of 128 bytes of CD-I data.

The LC8955 then decodes data in the buffer without intervention from the CPU or DMA controller, leaving these devices free for other tasks.

### Decoder Block

The decoder block converts the ADPCM data into 16-bit linear PCM data. Decoding parameters can either be set by the CPU, or read from subheader information in the ADPCM data stream.

SANYO Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

### **DAC Interface Block**

Two output formats are available. The first is suitable for input to Sanyo's LC7883, 7883M DA converters, and the second is the standard CD-I format. The output circuit will also accept CD-DA format input data and, by setting an LC8955 internal register, switch it through to the output pins without processing.

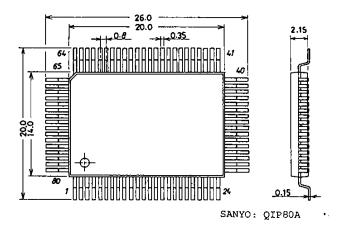

# Package Dimensions (unit: mm)

3044B-Q80AIC

## Pin Assignment

Туре

I : Input pin

O : Output pin

B : Bidirectional pin

P : Power supply pin

NC : No connection

Note) All  $V_{DD}$  and  $V_{SS}$  pins should be connected to the positive supply or ground.

| No.  | Pin Name | Туре     | ΙГ         |

|------|----------|----------|------------|

| 1    | T2       |          |            |

| 2    | Τ1       | 1        |            |

| 3    | OUTSET   | 1        |            |

| 4    | Vss      | Р        |            |

| 5    | A12      | 0        |            |

| 6    | A11      | 0        |            |

| 7    | A10      | 0        |            |

| 8    | A9       | 0        |            |

| 9    | A8       | 0        |            |

| 10   | A7       | 0        |            |

| 11   | A6       | 0        |            |

| 12   | A5       | 0        |            |

| _ 13 | Vss      | Р        |            |

| 14   | A4       | 0        |            |

| 15   | A3       | 0        |            |

| 16   | A2       | 0        |            |

| 17   | A1       | 0        |            |

| 18   | A0       | 0        |            |

| 19   | MWEB     | 0        |            |

| 20   | MCSB     | 0        |            |

| 21   | Vss      | Р        |            |

| 22   | 107      | В        |            |

| 23   | 106      | . В      | L          |

| 24   | 105      | . 8      | L          |

| 25   | 104      | В        | L          |

| 26   | 103      | В        | L          |

| 27   | 102      | В        | L          |

| 28   | 101      | В        |            |

| 29   | 100      | В        | <u> </u>   |

| 30   | DD7      | I        |            |

| 31   | Voo      | P        | L          |

| 32   | DD6      | . '      | L          |

| 33   | DD5      | 1        | L          |

| 34   | DD4      | I        | L          |

| 35   | DD3      | 1        | <u> </u> _ |

| 36   | DD2      | <u> </u> | L          |

| 37   | DD1      | 1        | L          |

| 38   | DD0      | 1        | L          |

| 39   | EFLAG    | - I      | <u> </u> _ |

| 40   | READB    | 0        | L          |

|     | 41         | WAITB    | ; | ı   |

|-----|------------|----------|---|-----|

|     | 42         | MCK      | : | 1   |

|     | 43         | DTENB    |   | 1   |

| ]   | 44         | EOPB     |   | 1   |

|     | 45         | SD7      |   | В   |

| 1   | 46         | SD6      | - | В   |

| 1   | 47         | SD5      |   | В   |

| 1   | 48         | SD4      |   | В   |

|     | 49         | SD3      | _ | В   |

| ]   | 50         | SD2      | _ | В   |

| ] . | 51         | SD1      |   | В   |

|     | 52         | Vss      |   | Р   |

|     | 53         | SD0      | 1 | В   |

| ]   | 54         | SA1      | : | ı   |

| 1 1 | 55         | SA0      | i | - ( |

| 1   | 56         | CSB      | i | Ī   |

| 1   | 57         | RDB      | : | 1   |

| 1   | 58         | WRB      | 1 | ļ   |

| 1   | 59         | BUSY     | į | 0   |

|     | 60         | BUFFULL. | Ì | 0   |

|     | 61         | UNDFLOW  | Ţ | 0   |

| 1   | 62         | DATAEMP  | Ť | 0   |

|     | 63         | MEMPHAS  | i | 0   |

| 1   | 64         | MBITSPL  | i | 0   |

| 1   | 65         | MSPLFRQ  | T | 0   |

| 1   | 66         | MSTEMON  | Т | 0   |

|     | 67         | RESETB   | 1 | Ī   |

| ]   | 68         | LRCLK    | - | 0   |

|     | 69         | WCLK     | T | 0   |

|     | 70         | DATA     | ļ | 0   |

|     | 71         | BCLK     | 1 | 0   |

|     | 72         | CLRCLK   | Ī | ı   |

| 1   | 73         | Voo      | Ţ | Ρ,  |

|     | 74         | CWCLK    | Ţ | ı   |

| ]   | 75         | CDATA    | i | 1   |

| 1   | 76         | CBCLK    |   | 1   |

| 1   | <b>7</b> 7 | REQB     | T | 0   |

| 1   | 78         | DACKB    | Ť | 1   |

| 1   | 79         | READYB   | Ţ | 0   |

|     | <b>B</b> 0 | DONEB    | Ì | 1   |

| •   |            | •        |   |     |

## System Diagram

## **Block Diagram**

## Absolute Maximum Ratings at V<sub>SS</sub>=0V

| Parameter                   | Symbol              | Condition Ratings           |                                | Unit |  |

|-----------------------------|---------------------|-----------------------------|--------------------------------|------|--|

| Maximum Supply Voltage      | V <sub>DD</sub> max | Ta=25°C                     | -0.3  to  +7.0                 | V    |  |

| Input/Output Voltage        | $V_{I}, V_{O}$      | Ta = 25°C                   | $-0.3 \text{ to V}_{DD} + 0.3$ | V    |  |

| Allowable Power Dissipation | Pd max              | Ta≦70°C                     | 350                            | mW   |  |

| Operating Temperature       | Topr                |                             | -30  to  +70                   | °C   |  |

| Storage Temperature         | Tstg                |                             | - 55 to + 125                  | °C   |  |

| Solder Temperature          |                     | 10sec.,dipping of pins only | 260                            | °C   |  |

## Allowable Operating Conditions at $Ta = -30 \text{ to } +70^{\circ}\text{C}, V_{SS} = 0\text{V}$

| Parameter           | Symbol          |     | Ratings | Unit     |          |  |

|---------------------|-----------------|-----|---------|----------|----------|--|

| Tarameter           | Dymoor          | min | typ     | max      | 7 0 1111 |  |

| Supply Voltage      | $V_{DD}$        | 4.5 | 5.0     | 5.5      | v        |  |

| Input Voltage Range | V <sub>IN</sub> | 0   |         | $V_{DD}$ | V        |  |

## DC Characteristics at $V_{SS} = 0V$ , $V_{DD} = 4.5$ to 5.5V, $T_a = -30$ to $+70^{\circ}C$

| Parameter                | Symbol           | Applicable                          | Condition                            | Ratings |     |     | 17:4 |

|--------------------------|------------------|-------------------------------------|--------------------------------------|---------|-----|-----|------|

|                          | Dy moor          | Pins                                | Condition                            | min     | typ | max | Unit |

| Input 'H'-Level Voltage  | VIIII            | All input pins<br>except RESETB,    |                                      | 2.2     | -   |     | V    |

| Input 'L'-Level Voltage  | V <sub>IL1</sub> | EOPB, 107 to 0,<br>SD7 to 0         |                                      |         |     | 0.8 | V    |

| Input 'H'-Level Voltage  | V <sub>IH2</sub> | RESETB, EOPB,<br>IO7 to 0, SD7 to 0 |                                      | 2.5     |     |     | V    |

| Input 'L'-Level Voltage  | V <sub>IL2</sub> |                                     |                                      |         |     | 0.6 | V    |

| Output 'H'-Level Voltage | V <sub>OH</sub>  | All output pins                     | $l_{OH} = -3mA$                      | 2.4     |     |     | V    |

| Output 'L'-Level Voltage | V <sub>OL</sub>  |                                     | I <sub>OL</sub> =3mA                 |         |     | 0.4 | v    |

| Input Leakage Current    | IL               | All input pins                      | $V_{\rm I} = V_{\rm SS}, V_{\rm DD}$ | -25     | _   | 25  | μΛ   |

| Pull-up Resistor         | R <sub>UP</sub>  | 100 to 7, SD0 to 7                  |                                      | 10      | 20  | 40  | kΩ   |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.