# General-Purpose 68000 MPU Peripheral Interface IC

## PUPPET (Programmable Universal Peripheral/Port Expansion uniT)

### **Overview**

There are many application systems using the 68000 chip as their MPU (Main Processing Unit). It is common to them that designing the peripheral circuits such as address decoders, interrupt controllers, serial interface and DMA (Direct Memory Access) has become a time-consuming task. As a result, each of the application systems requires a larger board size, which makes it very expensive.

In addition, 68000 family peripherals are highly advanced functional ICs. The application system designer finds it difficult to use them in small- and medium-sized application products in terms of cost as well as functional complexity. The LC8953 (Programmable Universal Peripheral/Port Expansion uniT) has optimized on-chip control circuits enabling the 68000 MPU to control the LC8951 (RCHIP) and LC8955. Use of the optimized control circuits allows the user to easily build up CD-ROM and CD-I systems which offer excellent performance in terms of space and cost.

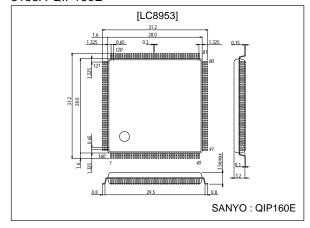

### **Package Dimensions**

unit:mm

3153A-QIP160E

#### **Features**

- Programmable address decoder.

- Programmable DTACK generator.

- Programmable interrupt handler.

- · Clock divider.

- Bus error generator.

- TICK generator (programmable timer interrupt generator)

- Serial mouse interface (1 port)

- LC8951 (RCHIP–Real-time error Correction & Host-interface Integrated Processor) interface.

- LC8955 interface.

- Micro-programmable 1-channel DMA controller.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges,or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

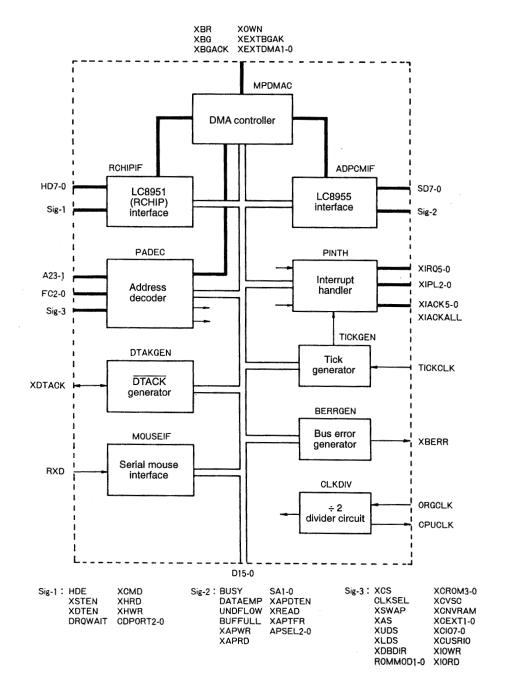

### **Block Diagram**

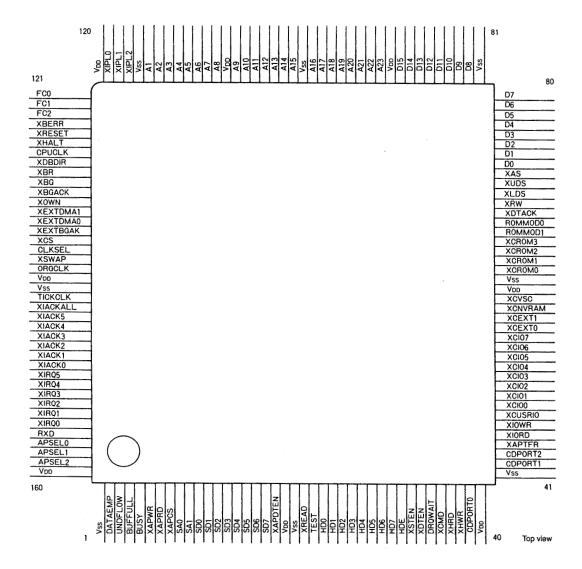

### **Pin Assignment**

## **Pin Functions**

| Number | Name <sup>1</sup>     | I/O      | Function                                                                           |

|--------|-----------------------|----------|------------------------------------------------------------------------------------|

| 1      | V <sub>SS</sub>       | _        | Ground pin                                                                         |

| 2      | DATAEMP               | I        | Data empty signal input pin for the LC8955                                         |

| 3      | UNDFLOW               | I        | Underflow signal input pin for the LC8955                                          |

| 4      | BUFFULL               | 1        | Buffer full signal input pin for the LC8955                                        |

| 5      | BUSY                  | I        | Busy signal input pin for the LC8955                                               |

| 6      | XAPWR                 | I        | Data write signal input pin for the LC8955                                         |

| 7      | XAPRD                 | 1        | Data read signal input pin for the LC8955                                          |

| 8      | XAPCS                 | 1        | Chip select input pin for the LC8955                                               |

| 9      | SA0                   | 0        | Posister coloct signal output ping for the LC0055                                  |

| 10     | SA1                   | 0        | Resister select signal output pins for the LC8955                                  |

| 11     | SD0                   | I/O      |                                                                                    |

| 12     | SD1                   | I/O      |                                                                                    |

| 13     | SD2                   | I/O      |                                                                                    |

| 14     | SD3                   | I/O      |                                                                                    |

| 15     | SD4                   | I/O      | Data signal I/O pins for the LC8955                                                |

| 16     | SD5                   | I/O      |                                                                                    |

| 17     | SD6                   | I/O      |                                                                                    |

| 18     | SD7                   | I/O      |                                                                                    |

| 19     | XAPDTEN               | 0        | Data enable signal output pin for the LC8955 for automatic request transfer        |

| 20     | V <sub>DD</sub>       |          | +5V supply pin                                                                     |

| 21     | V <sub>SS</sub>       |          | Ground pin                                                                         |

| 22     | XREAD                 |          | Read signal input pin for the LC8955 for automatic request transfer                |

| 23     | TEST                  | <u> </u> | Test input pin (Tied low)                                                          |

| 24     | HD0                   | I/O      | rest input pin (ned low)                                                           |

| 25     | HD1                   | I/O      |                                                                                    |

|        | HD2                   | I/O      |                                                                                    |

| 26     |                       |          |                                                                                    |

| 27     | HD3                   | 1/0      | Data signal I/O pins for the LC8951 (RCHIP)                                        |

| 28     | HD4                   | 1/0      |                                                                                    |

| 29     | HD5                   | I/O      |                                                                                    |

| 30     | HD6                   | I/O      |                                                                                    |

| 31     | HD7                   | I/O      |                                                                                    |

| 32     | HDE                   | ı        | Erasure flag signal input pin for the LC8951 (RCHIP)                               |

| 33     | XSTEN                 | I        | Status enable signal input pin for the LC8951 (RCHIP)                              |

| 34     | XDTEN                 | I        | Data enable signal input pin for the LC8951 (RCHIP)                                |

| 35     | DRQWAIT               | I        | Data request/Wait select signal input pin for the LC8951 (RCHIP)                   |

| 36     | XCMD                  | 0        | Command/Data select signal output pin for the LC8951 (RCHIP)                       |

| 37     | XHRD                  | 0        | Data read signal output pin for the LC8951 (RCHIP)                                 |

| 38     | XHWR                  | 0        | Data write signal output pin for the LC8951 (RCHIP)                                |

| 39     | CDPORT0               | I/O      | General-purpose input/output signal pin                                            |

| 40     | V <sub>DD</sub>       | -        | +5V supply pin                                                                     |

| 41     | V <sub>SS</sub>       | -        | Ground pin                                                                         |

| 42     | CDPORT1               | I/O      | General-purpose input/output signal pins                                           |

| 43     | CDPORT2               | I/O      |                                                                                    |

| 44     | XAPTFR                | I        | Mask operation select signal input pin for the LC8955 automatic request transfer   |

| 45     | XIORD                 | 0        | IC read signal output pin for Intel peripheral ICs                                 |

| 46     | XIOWR                 | 0        | Write signal output pin for Intel peripheral ICs                                   |

| 47     | XCUSRIO               | 0        | User I/O address select signal output pin                                          |

| 48     | XCIO0                 | 0        |                                                                                    |

| 49     | XCIO1                 | 0        |                                                                                    |

| 50     | XCIO2                 | 0        |                                                                                    |

| 51     | XCIO3                 | 0        | <del>- </del>                                                                      |

| 52     | XCIO4                 | 0        | Programmable I/O address select signal output pins                                 |

| 53     | XCIO4<br>XCIO5        | 0        | $\dashv$                                                                           |

|        |                       | 0        | _                                                                                  |

| 54     | XCIO6                 |          | _                                                                                  |

| EE     | XCIO7                 | 0        |                                                                                    |

| 55     | VOEVTO                |          |                                                                                    |

| 56     | XCEXT0                | 0        | External address select signal output pins                                         |

|        | XCEXT0 XCEXT1 XCNVRAM | 0        | External address select signal output pins  NVRAM address select signal output pin |

Continued on next page.

### Continued from preceding page.

| Number | Name <sup>1</sup> | I/O | Function                                       |  |  |  |  |  |

|--------|-------------------|-----|------------------------------------------------|--|--|--|--|--|

|        |                   |     |                                                |  |  |  |  |  |

| 60     | V <sub>DD</sub>   | _   | +5V supply pin                                 |  |  |  |  |  |

| 61     | V <sub>SS</sub>   | _   | Ground pin                                     |  |  |  |  |  |

| 62     | XCROM0            | 0   |                                                |  |  |  |  |  |

| 63     | XCROM1            | 0   | ROM address select signal output pins          |  |  |  |  |  |

| 64     | XCROM2            | 0   | Trom dadross solisti signar sarpar pins        |  |  |  |  |  |

| 65     | XCROM3            | 0   |                                                |  |  |  |  |  |

| 66     | ROMMOD1           | 1   | ROM mode select signal input pins              |  |  |  |  |  |

| 67     | ROMMOD0           | I   | ROW mode select signal input pins              |  |  |  |  |  |

| 68     | XDTACK            | I/O | Data acknowledge signal input/output pin       |  |  |  |  |  |

| 69     | XRW               | I/O | Read/Write signal input/output pin             |  |  |  |  |  |

| 70     | XLDS              | I/O | Low-order data strobe signal input/output pin  |  |  |  |  |  |

| 71     | XUDS              | I/O | High-order data strobe signal input/output pin |  |  |  |  |  |

| 72     | XAS               | I/O | Address strobe signal input/output pin         |  |  |  |  |  |

| 73     | D0                | 1/0 | / Addition of the original impurodipat pin     |  |  |  |  |  |

| 74     | D1                | 1/0 | _                                              |  |  |  |  |  |

|        |                   |     |                                                |  |  |  |  |  |

| 75     | D2                | 1/0 | _                                              |  |  |  |  |  |

| 76     | D3                | 1/0 | Data bus signal input/output pins              |  |  |  |  |  |

| 77     | D4                | I/O |                                                |  |  |  |  |  |

| 78     | D5                | 1/0 |                                                |  |  |  |  |  |

| 79     | D6                | I/O |                                                |  |  |  |  |  |

| 80     | D7                | I/O |                                                |  |  |  |  |  |

| 81     | V <sub>SS</sub>   | -   | Ground pin                                     |  |  |  |  |  |

| 82     | D8                | I/O |                                                |  |  |  |  |  |

| 83     | D9                | I/O |                                                |  |  |  |  |  |

| 84     | D10               | I/O |                                                |  |  |  |  |  |

| 85     | D11               | I/O |                                                |  |  |  |  |  |

| 86     | D12               | I/O | Data bus signal input/output pins              |  |  |  |  |  |

| 87     | D13               | I/O |                                                |  |  |  |  |  |

| 88     | D14               | I/O |                                                |  |  |  |  |  |

| 89     | D15               | 1/0 | $\dashv$                                       |  |  |  |  |  |

|        |                   | -   | LEM avandu nin                                 |  |  |  |  |  |

| 90     | V <sub>DD</sub>   |     | +5V supply pin                                 |  |  |  |  |  |

| 91     | A23               | 1/0 |                                                |  |  |  |  |  |

| 92     | A22               | I/O |                                                |  |  |  |  |  |

| 93     | A21               | I/O |                                                |  |  |  |  |  |

| 94     | A20               | I/O | Address bus signal input/output pins           |  |  |  |  |  |

| 95     | A19               | I/O |                                                |  |  |  |  |  |

| 96     | A18               | I/O |                                                |  |  |  |  |  |

| 97     | A17               | I/O |                                                |  |  |  |  |  |

| 98     | A16               | I/O |                                                |  |  |  |  |  |

| 99     | V <sub>SS</sub>   | _   | Ground pin                                     |  |  |  |  |  |

| 100    | A15               | I/O |                                                |  |  |  |  |  |

| 101    | A14               | I/O |                                                |  |  |  |  |  |

| 102    | A13               | I/O |                                                |  |  |  |  |  |

| 103    | A12               | I/O | Address bus signal input/output pins           |  |  |  |  |  |

| 104    | A11               | I/O |                                                |  |  |  |  |  |

| 105    | A10               | 1/0 |                                                |  |  |  |  |  |

| 106    | A9                | I/O |                                                |  |  |  |  |  |

| 107    | _                 | -   | +5V supply pin                                 |  |  |  |  |  |

|        | V <sub>DD</sub>   | I/O | тоу зарруу ріп                                 |  |  |  |  |  |

| 108    | A8                |     | $\dashv$                                       |  |  |  |  |  |

| 109    | A7                | 1/0 | $\dashv$                                       |  |  |  |  |  |

| 110    | A6                | 1/0 | _                                              |  |  |  |  |  |

| 111    | A5                | I/O | Address bus signal input/output pins           |  |  |  |  |  |

| 112    | A4                | I/O |                                                |  |  |  |  |  |

| 113    | A3                | I/O |                                                |  |  |  |  |  |

| 114    | A2                | I/O |                                                |  |  |  |  |  |

| 115    | A1                | I/O |                                                |  |  |  |  |  |

| 116    | V <sub>SS</sub>   | _   | Ground pin                                     |  |  |  |  |  |

| 117    | XIPL2             | 0   |                                                |  |  |  |  |  |

| 118    | XIPL1             | 0   | Interrupt level signal output pins for the MPU |  |  |  |  |  |

| 119    | XIPL0             | 0   |                                                |  |  |  |  |  |

|        | 1 =0              |     | L                                              |  |  |  |  |  |

Continued on next page.

### Continued from preceding page.

| -      |                   |     |                                                               |

|--------|-------------------|-----|---------------------------------------------------------------|

| Number | Name <sup>1</sup> | I/O | Function                                                      |

| 120    | V <sub>DD</sub>   | -   | +5V supply pin                                                |

| 121    | FC0               | I/O |                                                               |

| 122    | FC1               | I/O | MPU function code signal input/output pins                    |

| 123    | FC2               | I/O |                                                               |

| 124    | XBERR             | 0   | Bus error signal output pin                                   |

| 125    | XRESET            | I   | Reset signal input pin                                        |

| 126    | XHALT             | ļ   | Halt signal input pin                                         |

| 127    | CPUCLK            | 0   | MPU clock signal output pin                                   |

| 128    | XDBDIR            | 0   | Data bus direction signal output pin                          |

| 129    | XBR               | 0   | DMA bus request signal output pin                             |

| 130    | XBG               | I   | DMA bus request-granted signal input pin                      |

| 131    | XBGACK            | 0   | DMA bus request-granted acknowledge signal output pin         |

| 132    | XOWN              | 0   | DMA cycle active signal output pin                            |

| 133    | XEXTDMA1          | I/O | DMA signal installation                                       |

| 134    | XEXTDMA0          | I/O | DMA signal input/output pins                                  |

| 135    | XEXTBGAK          | I   | External DMA bus request-granted acknowledge signal input pin |

| 136    | XCS               | I   | Address decoder mode select signal input pin                  |

| 137    | CLKSEL            | I   | Master clock (CPUCLK) divider select signal input pin         |

| 138    | XSWAP             | I   | Memory swap function select signal input pin                  |

| 139    | ORGCLK            | I   | Clock input pin                                               |

| 140    | V <sub>DD</sub>   | -   | +5V supply pin                                                |

| 141    | V <sub>SS</sub>   | -   | Ground pin                                                    |

| 142    | TICKCLK           | I   | External clock input pin for the tick generator               |

| 143    | XIACKALL          | 0   | Interrupt acknowledge common signal output pin                |

| 144    | XIACK5            | 0   |                                                               |

| 145    | XIACK4            | 0   |                                                               |

| 146    | XIACK3            | 0   | Interrupt colynousledge cignel cutout piec                    |

| 147    | XIACK2            | 0   | Interrupt acknowledge signal output pins                      |

| 148    | XIACK1            | 0   |                                                               |

| 149    | XIACK0            | 0   |                                                               |

| 150    | XIRQ5             | I   |                                                               |

| 151    | XIRQ4             | I   |                                                               |

| 152    | XIRQ3             | I   | Interrupt request signal input pins                           |

| 153    | XIRQ2             | I   | interrupt request signal input pins                           |

| 154    | XIRQ1             | I   |                                                               |

| 155    | XIRQ0             | I   |                                                               |

| 156    | RXD               | I   | Mouse data signal input pin                                   |

| 157    | APSEL0            | 0   |                                                               |

| 158    | APSEL1            | 0   | General-purpose output port pins                              |

| 159    | APSEL2            | 0   |                                                               |

| 160    | V <sub>DD</sub>   | -   | +5V supply pin                                                |

|        |                   |     |                                                               |

1. An "X" at the beginning of a pin name indicates negative logic.

## **Specifications**

### Absolute Maximum Ratings at $V_{SS} = 0\,V$

| Parameter                   | Symbol                          | Conditions            | Ratings                      | Unit |

|-----------------------------|---------------------------------|-----------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max             | Ta=25°C               | -0.3 to +7.0                 | V    |

| Input and output voltage    | V <sub>I</sub> , V <sub>O</sub> | Ta=25°C               | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation | Pd max                          | Ta≤70°C               | 400                          | mW   |

| Operating temperature range | Topr                            |                       | -30 to +70                   | °C   |

| Storage temperature range   | Tstg                            |                       | -55 to +125                  | °C   |

| Soldering temperature       | Tsol                            | Manual soldering, 3s  | 350                          | °C   |

| Soldering temperature       | 1501                            | Reflow soldering, 10s | 235                          | °C   |

### Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}, V_{SS} = 0\text{V}$

| Parameter           | Symbol          | Conditions | Ratings |     |          | Unit  |

|---------------------|-----------------|------------|---------|-----|----------|-------|

| Falanietei          |                 |            | min     | typ | max      | Offic |

| Supply voltage      | V <sub>DD</sub> |            | 4.5     | 5.0 | 5.5      | V     |

| Input voltage range | V <sub>IN</sub> |            | 0       |     | $V_{DD}$ | V     |

## DC Electrical Characteristics at Ta = -30 to +70 °C, $V_{SS} = 0V$ , $V_{DD} = 4.5$ to 5.5V

| Parameter                 | Symbol                       | Conditions                                                                                          |                        | Ratings            |     |                    | Unit  |

|---------------------------|------------------------------|-----------------------------------------------------------------------------------------------------|------------------------|--------------------|-----|--------------------|-------|

| Farameter                 | Symbol                       |                                                                                                     |                        | min                | typ | max                | Offic |

| Input high-level voltage  | V <sub>IH</sub> 1            | TTL compatible: All input pins (including bidirectional pins) except those listed in notes 1 and 2. |                        | 2.2                |     |                    | V     |

| Input low-evel voltage    | V <sub>IL</sub> 1            |                                                                                                     |                        |                    |     | 0.8                | V     |

| Input high-level voltage  | V <sub>IH</sub> 2            | TTL-compatible Schmitt: See note 1.                                                                 |                        | 2.5                |     |                    | V     |

| Input low-level voltage   | V <sub>IL</sub> 2            |                                                                                                     |                        |                    |     | 0.6                | V     |

| Output high-level voltage | V <sub>OH</sub> 1            | I <sub>OH</sub> =-3mA                                                                               |                        | 2.4                |     |                    | V     |

| Outpu low-level voltage   | V <sub>OL</sub> 1            | I <sub>OL</sub> =3mA                                                                                |                        |                    |     | 0.4                | V     |

| Input leakage current     | ΙL                           | V <sub>I</sub> =V <sub>SS</sub> , V <sub>DD</sub>                                                   |                        | -25                |     | +25                | μΑ    |

| Output leakage current    | loz                          | High-impedan-<br>ce output                                                                          | All bidirectional pins | -100               |     | +100               | μΑ    |

| Input high-level voltage  | V <sub>IH</sub> 3            | CMOS compatible: ORGCLK (pin 139)                                                                   |                        | 0.7V <sub>DD</sub> |     |                    | V     |

| Input low-level voltage   | V <sub>IL</sub> 3            |                                                                                                     |                        |                    |     | 0.3V <sub>DD</sub> | V     |

| Output high-level voltage | V <sub>OH</sub> <sup>2</sup> | I <sub>OH</sub> =-6mA XDTACK (pin 68), D0 to D15 (pins 73 to 89)                                    |                        | 2.4                |     |                    | V     |

| Outpu low-level voltage   | V <sub>OL</sub> 2            |                                                                                                     |                        |                    |     | 0.4                | V     |

### Notes

- 1. DATAEMP (pin 2), UNDFLOW (pin 3), BUFFULL (pin 4), BUSY (pin 5), XSTEN (pin 33), XDTEN (pin 34), DRQWAIT (pin 35), XAPTFR (pin 44), XRESET (pin 125), XHALT (pin 126), XEXTBGAK (pin 135), XIRQ0 to 5 (pins 150 to 155), RXD (pin 156)

- 2. ORGCLK (pin 139)

- 3. XDTACK (pin 68), D0 to D15 (pins 73 to 89)

#### Internal Functional Blocks

The PUPPET consists of about 10 functional blocks. See the "Block Diagram".

### PADEC (Programmable Address Decoder)

The PADEC functional block is used to generate the chip select (CS) signals for ROM, RAM, I/O devices and so on. The CS signal addresses are programmable, which enables address allocation specific to your system configuration.

### **DTAKGEN (Programmable DTACK Generator)**

The DTAKGEN functional block is used to generate the data acknowledge signals for the chip select address space selected by the PADEC. The access speed of peripheral IC devices is generally slower than that of the main processing unit (MPU). To adjust this speed gap between them, the user is allowed to insert from 0 to 4 wait cycles into each address cycle. The number of wait cycles to be inserted is programmable. In addition, the user is permitted to disable the DTACK (active low) generator so that it can be generated by an external device.

### **PINTH (Programmable Interrupt Handler)**

The PINTH functional block is used as an interrupt handler to output the vectored numbers corresponding to the 68000 MPU vectored interrupts. Each of the IPL levels and vectored numbers for internal block/external interrupt requests is programmable.

### RCHIPIF (LC8951 RCHIP Interface)

The RCHIPIF functional block is used to provide the interface between the 68000 MPU and the LC8951 RCHIP. This interface enables direct communication between them. As a result, status data, data signal and error bit information can be directly communicated between them.

### ADPCMIF (LC8955 Interface)

The ADPCMIF functional block is used to provide the interface between the 68000 MPU and the LC8955. This interface enables direct communication between them. As a result, data can be directly read from or written to internal registers of the LC8955 from the MPU.

### **TICKGEN (Tick Generator)**

The TICKGEN functional block is used to generate timer interrupt clocks for a real-time operating system. The timer interrupt clocks can be generated by dividing the system clock or selecting an external input clock. As a result, the tick can be set independent of the system clock frequency.

### **MOUSEIF (Serial Mouse Interface)**

The MOUSEIF functional block is used as the data receive port for a standard serial mouse. The communication parameters such as parity bit, stop bit, data bits and baud rate can be changed by software. In addition, the interrupt signal generation timing can be set to either 3-byte or 1-byte intervals. Therefore, this functional block can be used as a general-purpose receive serial port as well as the mouse serial port. Note that the mouse transmits an XY coordinate value to the serial port in 3-byte packets.

### MPDMAC (Micro-Programmable DMA Controller)

The MPDMAC functional block is used as the DMA controller. With this controller, the operation can be programmed by a 16-instruction micro code. These instructions can be programmed to support data read operations from the LC8951 (RCHIP), data write operations to the LC8955 as well as the basic transfer operations with memory. In addition, they include rather complicated instructions to enable data comparison, logical operation and conditional jump operations. Therefore, this controller block can be used as a sub-CPU to enable intelligent processing, and to reduce the load on the MPU.

### **BERRGEN (Bus Error Generator)**

The BERRGEN functional block is used to generate the bus error signal for the 68000 MPU when no AS (active low) signal is detected. There are four AS signal inactive periods. The user is allowed to select one from the four to best suit the application system in mind.

### **CLKDIV** (Clock Divider Circuit)

The CLKDIV function block is used to generate the MPU clock with 1: 1 duty cycle by dividing the master clock by 2.

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data,services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of August, 2001. Specifications and information herein are subject to change without notice.