## **CN8236**

## ATM ServiceSAR Plus with xBR Traffic Management

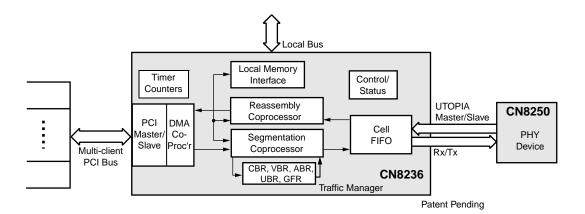

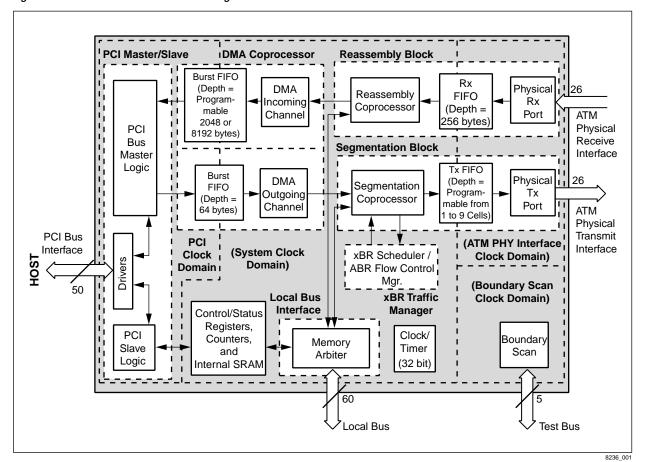

The CN8236 Service Segmentation and Reassembly Controller integrates ATM terminal functions, PCI Bus Master and Slave controllers, and a UTOPIA level 1 or 2 interface with service-specific functions in a single package for AALO, 3/4, and 5 operations. The *Service*SAR Controller generates and terminates ATM traffic and automatically schedules cells for transmission. The CN8236 is targeted at 155 Mbps throughput systems where the number of VCCs is relatively large, or the performance of the overall system is critical. Examples of such networking equipment include Routers, Ethernet switches, ATM Edge switches, or Frame Relay switches.

### Service-Specific Performance Accelerators

The CN8236 incorporates numerous service-specific features designed to accelerate and enhance system performance. As examples, the CN8236 implements Echo Suppression of LAN traffic via LECID filtering, and supports Frame Relay DE to CLP interworking.

### Advanced xBR Traffic Management

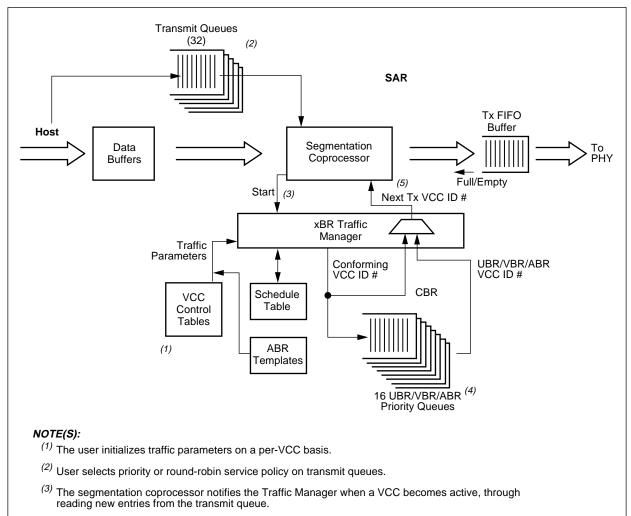

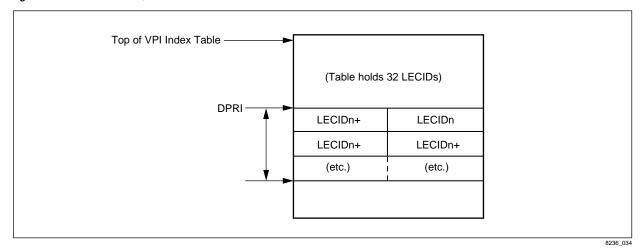

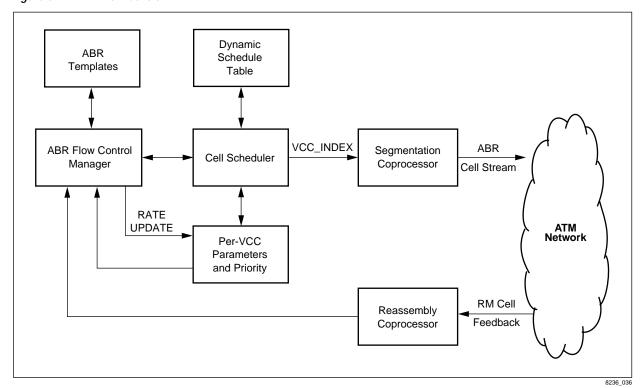

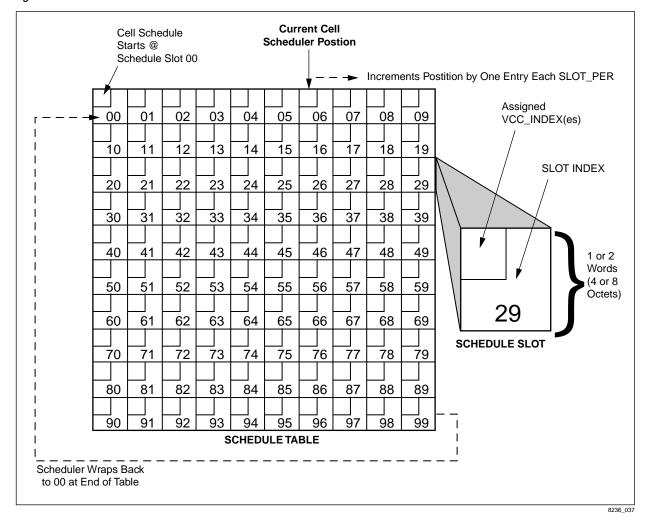

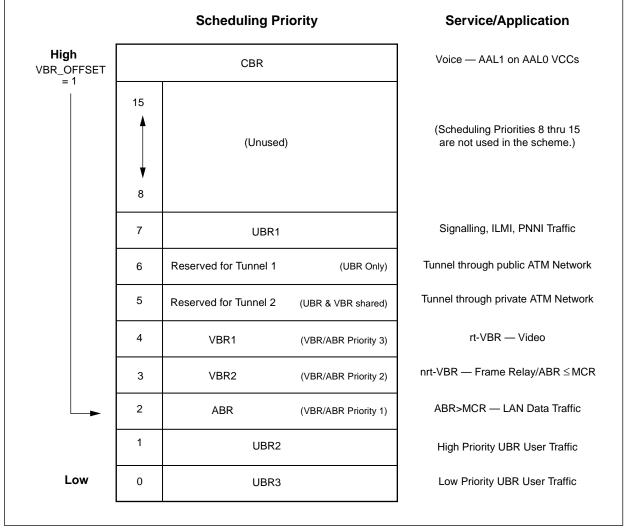

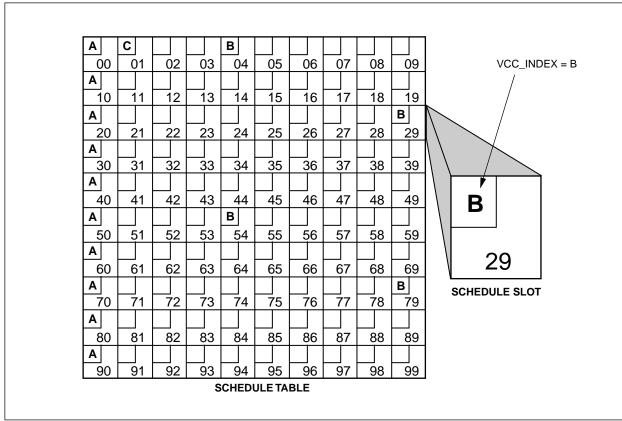

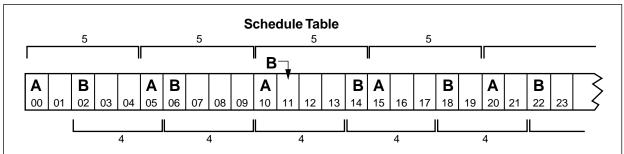

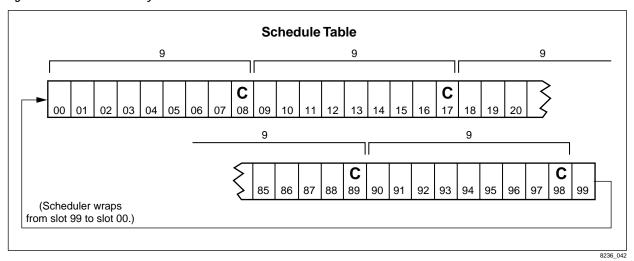

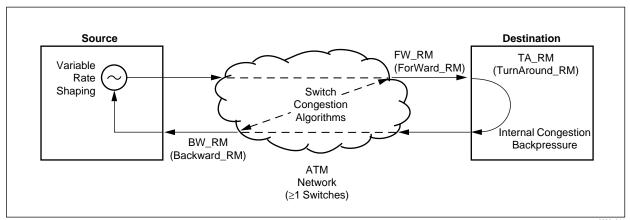

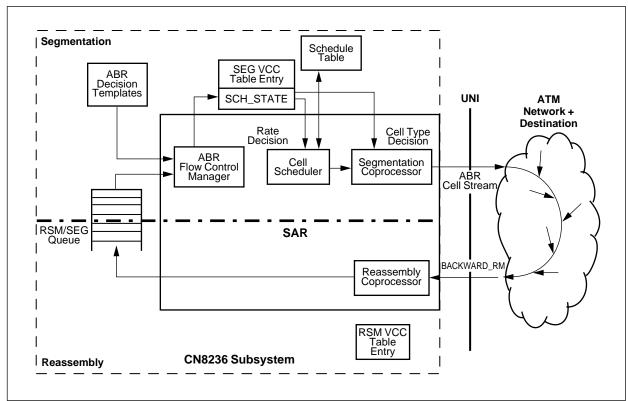

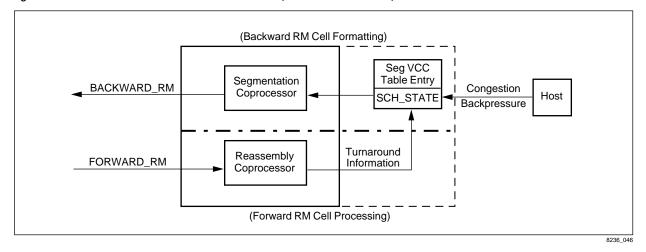

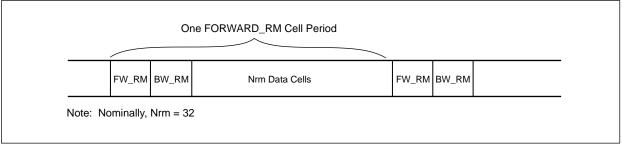

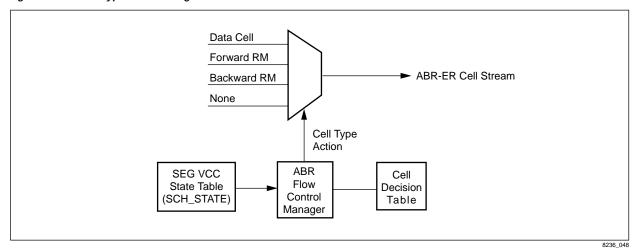

The xBR Traffic Manager in the CN8236 supports multiple ATM service categories. This includes CBR, VBR (both single and dual leaky bucket), UBR, GFR (Guaranteed Frame Rate), and ABR. The CN8236 manages each VCC independently. It dynamically schedules segmentation traffic to comply with up to 16+CBR user-configured scheduling priorities for the various traffic classes. Scheduling is controlled by a Schedule table configured by the user and based on a user-specified time reference. ABR channels are managed in hardware according to user-programmable ABR templates. These templates tune the performance of the CN8236's ABR algorithms to a specific system's or network's requirements.

—Continued—

### **Distinguishing Features**

#### Service-Specific Performance Accelerators

- · LECID filtering and echo suppression

- Dual leaky bucket based on CLP (frame relay)

- · Frame relay DE interworking

- · Internal SNMP MIB counters

- IP over ATM; supports both CLP0+1 and ABR shaping

#### Flexible Architectures

- Multi-peer host

- Direct switch attachment via reverse UTOPIA

- ATM terminal

- Host control

- Local bus control

- Optional local processor

-Continued-

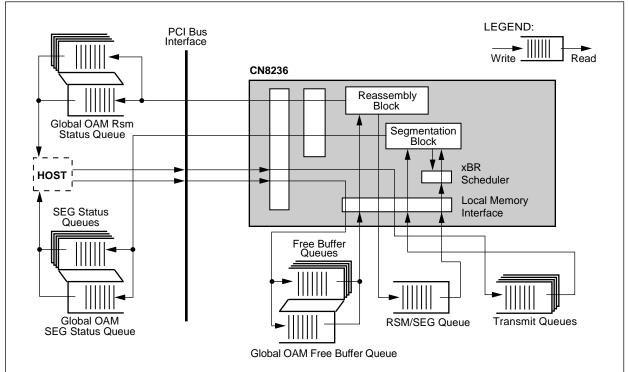

### **Functional Block Diagram**

Data Sheet 28236-DSH-001-B May 2003

### Ordering Information

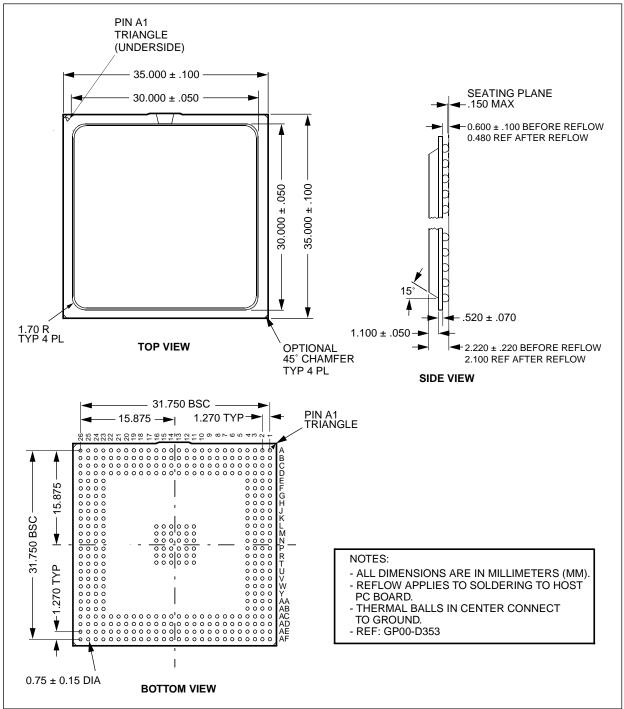

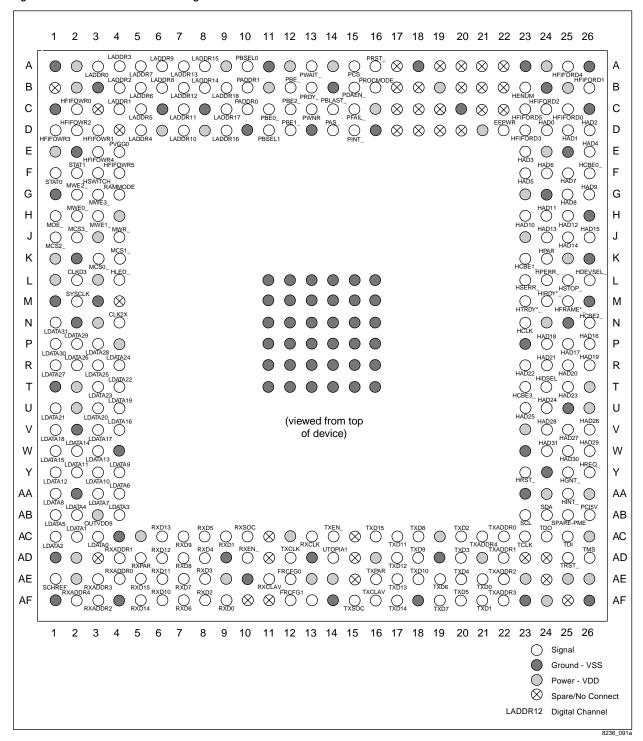

| Model Number                                  | Manufacturing<br>Part Number | Product Revision | Package     | Operating<br>Temperature |

|-----------------------------------------------|------------------------------|------------------|-------------|--------------------------|

| CN8236                                        | 28236-12                     | В                | 388-pin BGA | –40 °C to 85 °C          |

| CN8236/<br>CX28250EVM<br>Evaluation<br>Module | BT00-D700-601                |                  | _           |                          |

## **Document Revision History**

| Document Number | Device Revision | Comments                                                   |

|-----------------|-----------------|------------------------------------------------------------|

| N8236DSA        | CN8236 Rev. A   | This is the advanced issue of the data sheet.              |

| 100453B         | CN8236 Rev. B   | Put into new Conexant format.                              |

| 500372A         | CN8236 Rev. B   | Revisions made. Changed format from Conexant to Mindspeed. |

| 500372B         | CN8236 Rev. B   | Corrections as noted by change bars.                       |

| 28236-DSH-001-A | CN8236 Rev. B   | Corrections as noted by change bars.                       |

| 28236-DSH-001-B | CN8236 Rev. B   | Corrections as noted by change bars.                       |

© 1999-2003, Mindspeed Technologies™, a Conexant business All Rights Reserved.

Information in this document is provided in connection with Mindspeed Technologies ("Mindspeed") products. These materials are provided by Mindspeed as a service to its customers and may be used for informational purposes only. Mindspeed assumes no responsibility for errors or omissions in these materials. Mindspeed may make changes to specifications and product descriptions at any time, without notice. Mindspeed makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Mindspeed's Terms and Conditions of Sale for such products, Mindspeed assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MINDSPEED PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MINDSPEED FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MINDSPEED SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Mindspeed products are not intended for use in medical, lifesaving or life sustaining applications. Mindspeed customers using or selling Mindspeed products for use in such applications do so at their own risk and agree to fully indemnify Mindspeed for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Mindspeed Technologies™, the Mindspeed™ logo, and "Build It First"™. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Mindspeed Technologies Legal Information posted at <a href="https://www.mindspeed.com">www.mindspeed.com</a> which is incorporated by reference.

Mindspeed Technologies™

### **Multi-Queue Segmentation Processing**

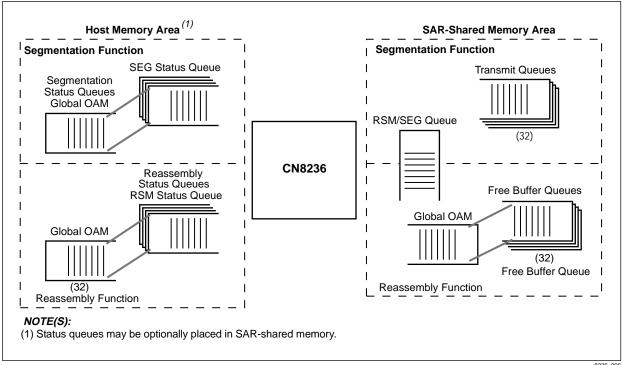

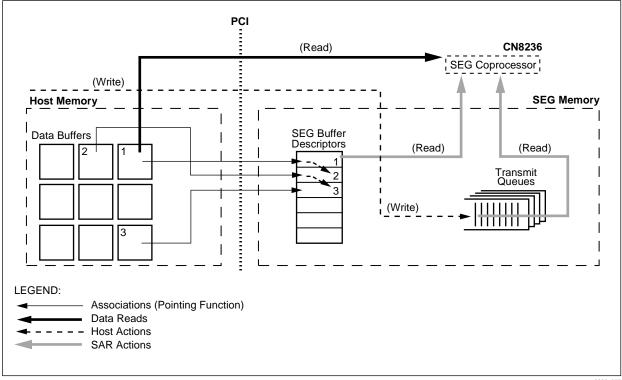

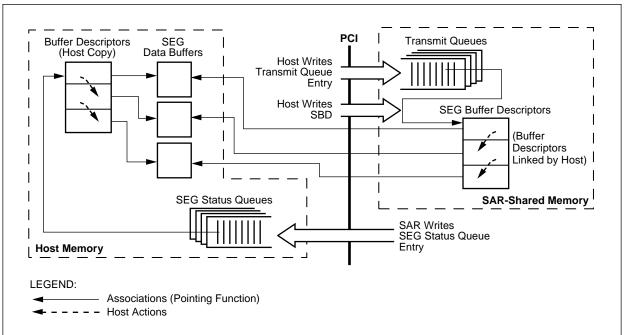

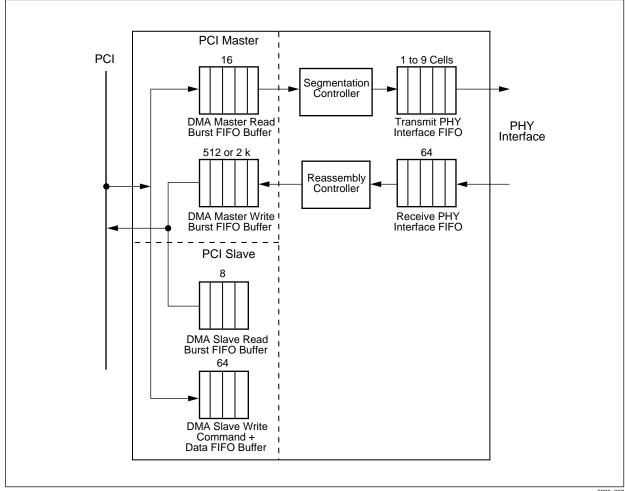

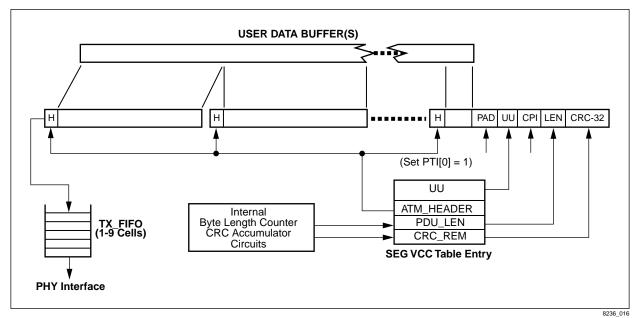

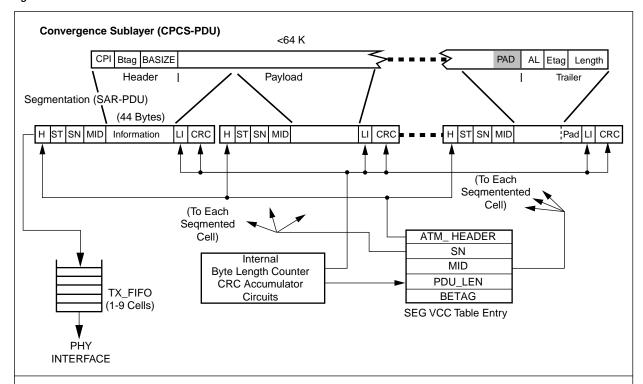

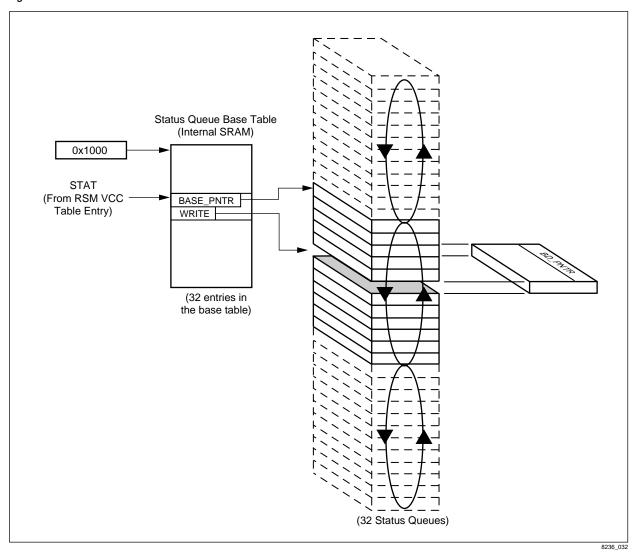

The CN8236's segmentation coprocessor generates ATM cells for up to 64 K VCCs. The segmentation coprocessor formats cells on each channel according to segmentation VCC tables, utilizing up to 32 independent transmit queues and reporting segmentation status on a parallel set of up to 32 segmentation status queues. The segmentation coprocessor fetches client data from the host, formats ATM cells while generating and appending protocol overhead, and forwards these to the UTOPIA port. The segmentation coprocessor operates as a slave to the xBR Traffic Manager which schedules VCCs for transmission.

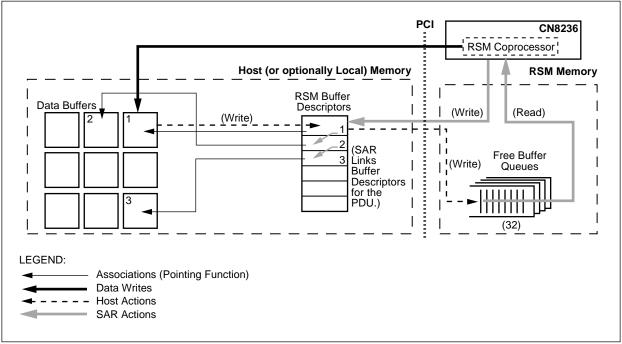

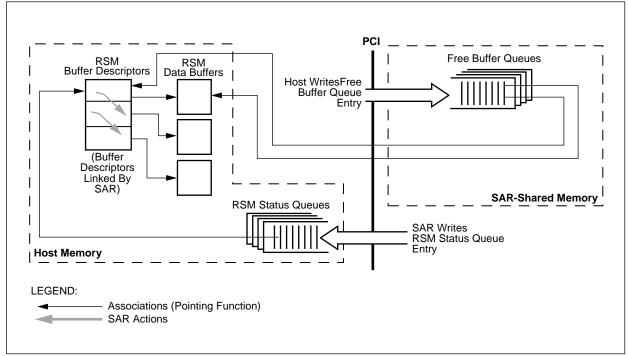

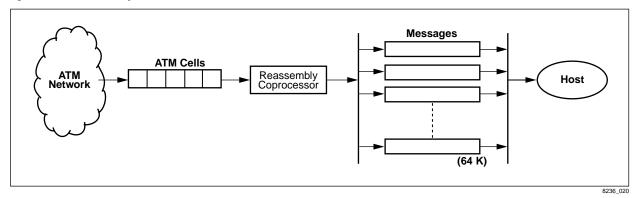

### Multi-Queue Reassembly Processing

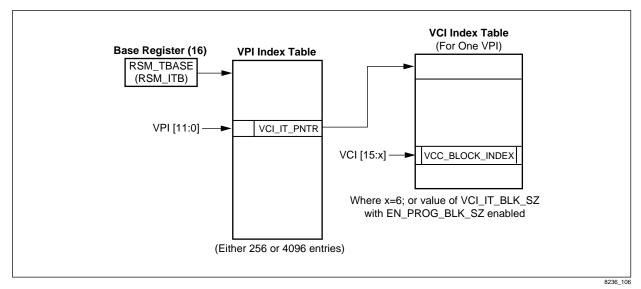

The CN8236's reassembly coprocessor stores the payload data from the cell stream received by the UTOPIA port into host data buffers. Using a dynamic lookup method which supports NNI or UNI addressing, the reassembly coprocessor processes up to 64 K VCCs simultaneously. The host supplies free buffers on up to 32 independent free buffer queues, and the reassembly coprocessor performs all CPCS protocol checks and reports the results of these checks as well as other status data on one of 32 independent reassembly status queues.

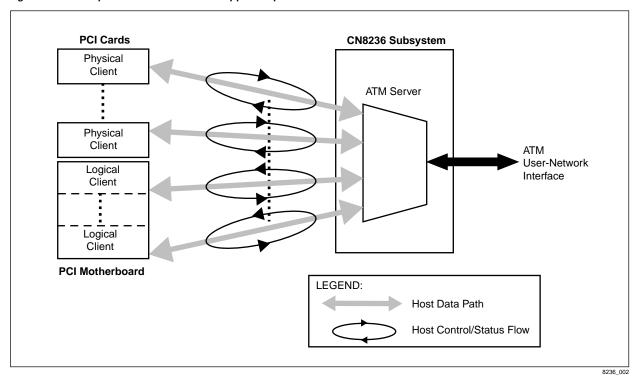

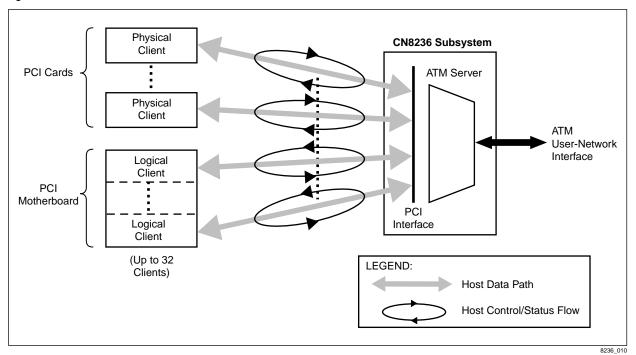

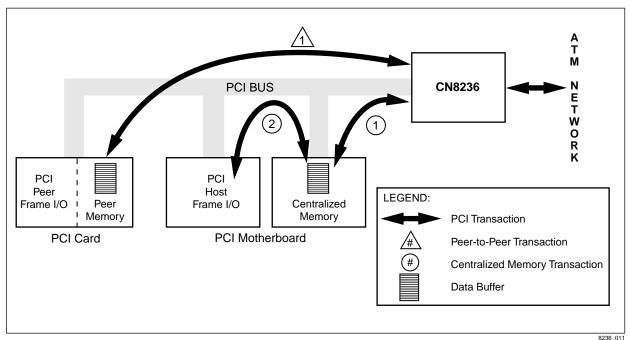

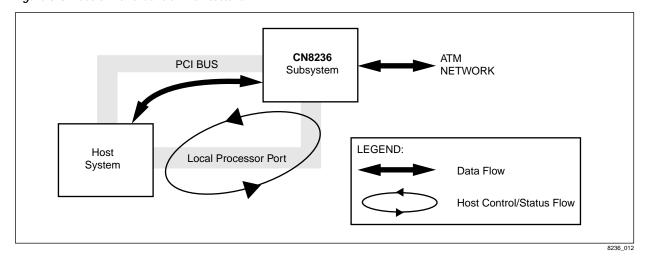

### High Performance Host Architecture with Buffer Isolation

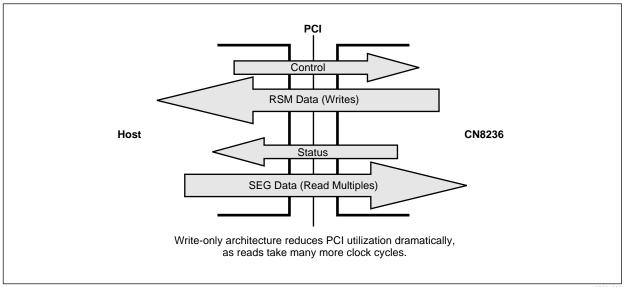

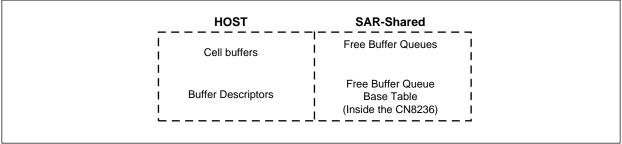

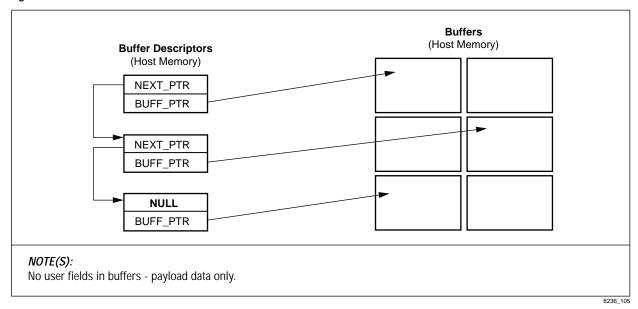

The CN8236 host interface architecture maximizes performance and system flexibility. The device's control and status queues enable host/SAR communication via write operations alone. This write-only architecture lowers latency and PCI bus occupancy. Flexibility is achieved by supporting a scalable peer-to-peer architecture. Multiple host clients can be addressed by the segmentation and reassembly (SAR) as separate physical or logical PCI peers. Segmentation and reassembly data buffers on the host system are identified by buffer descriptors in SAR-shared (or host) memory which contain pointers to buffers. The use of buffer descriptors in this way allows for isolation of data buffers from the mechanisms that handle buffer allocation and linking. This provides a layer of indirection in buffer assignment and management that maximizes system architecture flexibility.

### **Designer Toolkit**

Mindspeed provides an evaluation environment for the CN8236/RS8254EVM which provides a working reference design, an example of a software driver, and facilities for generating and terminating all service categories of ATM traffic. This system accelerates ATM system development by providing a rapid prototyping environment.

#### -Continued Distinguishing Features-

#### **New Features**

- 3.3 V, 388 BGA lowers power and eases PCB assembly

- AAL3/4 CPCS generation and checking

- PCI 2.1, including support for serial EEPROM

- Enhancements to xBR Traffic Manager

- fewer ABR templates

- improved CBR tunneling

- Reduced memory size for VCC lookup tables

- · Increased addressing flexibility

- Additional byte lane swappers for increased system flexibility

- UTOPIA level 2, 8/16 bit 50 MHz

- Programmable size routing tags up to 64 byte cells

- Selectable single/separate UTOPIA clocks

- Interworking function for AAL1 and 2 scheduling

- Cell on demand scheduling

- Updated PM-OAM processing per i.610

- SECBC calculated per GR-1248

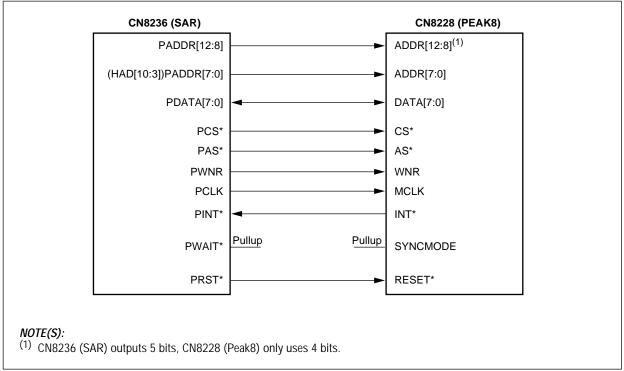

- Paging function in order to gluelessly control RS8228 cell delineator (SAR provides power)

- Robust EEPROM operation

- Compact PCI Hot Swap capabilities

- Master PCI write over read arbitration control

- Increase incoming DMA FIFO buffer from 2 kB to 8 kB

- Prepended VCC index on RSM BOM cells

- Optional reference clock drive scheduler

- Head of Line Flushing (HoLF) mechanism

- · Internal loopback in multiPHY mode

- Programmable number of slots that the scheduler can fall behind

### xBR Traffic Management

- TM4.1 Service Classes

- CBR

- VBR (single, dual and CLP-based leaky buckets)

- Real time VBR

- ABR

- UBR

- GFC (controlled & uncontrolled flows)

- Guaranteed Frame Rate (GFR) (guaranteed MCR on UBR VCCs)

- 16 levels of priorities (16 + CBR)

- Dynamic per-VCC scheduling

- Multiple programmable ABR templates (supplied by Mindspeed or user)

### 28236-DSH-001-B

- Scheduler driven by selectable clock

- Local system clock

- External reference clock

- Internal RM OAM cell feedback path

- Virtual FIFO buffer rate matching (Source Rate Matching)

- Per-VCC MCR and ICR

- Tunneling

- VP tunnels (VCI interleaving on PDU boundaries)

- CBR tunnels (cells interleaved as UBR, VBR or ABR with an aggregate CBR limit)

- 155 Mbps full duplex (two cell PDUs)

### **Multi-Queue Segmentation Processing**

- 32 transmit queues with optional priority levels

- 64 K VCCs maximum

- AAL5 and AAL3/4 CPCS generation

- AALO Null CPCS (optional use of PTI for PDU demarcation)

- · ATM cell header generation

- Raw cell mode (52 octet)

- 200 Mbps half duplex

- 155 Mbps full duplex (w/ 2-cell PDUs)

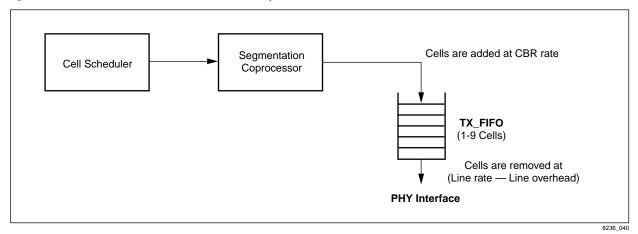

- Variable length transmit FIFO buffer -CDV - host latency matching (one to nine cells)

- Symmetric Tx and Rx architecture

- buffer descriptors

- queues

- User defined field circulates back to the host (32 bits)

- Distributed host or SAR-shared memory segmentation

- Simultaneous segmentation and reassembly

- Per-PDU control of CLP/PTI (UBR)

- Per-PDU control of AAL5 UU field

- Message and streaming status modes

- Virtual Tx FIFO buffer (PCI host)

### Multi-Queue Reassembly Processing

- 32 reassembly queues

- 64 K VCCs maximum \*

- AAL5 and AAL3/4 CPCS checking

- AAI 0

- PTI termination

- Cell count termination

- Early Packet Discard, based on:

- Receive buffer underflow

- Receive status overflow

- CLP with priority threshold

- AAL5 max PDU length

- Rx FIFO buffer full

- Frame relay DE with priority threshold

- LECID filtering and echo suppression

- Per-VCC firewalls

- Dynamic channel lookup (NNI or UNI addressing)

- Supports full address space

- Deterministic

- Flexible VCI count per VPI

- Optimized for signalling address assignment

- Message and streaming status modes

- Raw cell mode (52 octet)

- 200 Mbps half duplex

- 155 Mbps full duplex (w/ 2-cell PDUs)

- Distributed host or SAR-shared memory reassembly

- Eight programmable reassembly hardware time-outs (per-VCC assignable)

- Global max PDU length for AAL5

- Per-VCC buffer firewall (memory usage limit)

- Simultaneous reassembly and segmentation

- Idle cell filtering

## High Performance Host Architecture with Buffer Isolation

- · Write-only control and status

- Read multiple command for data transfer

- Up to 32 host clients control and status queues

- · Physical or logical clients

- Enables peer-to-peer architecture

- Descriptor-based buffer chaining

- Scatter/gather DMA

- Endian neutral (allows data word and control word byte swapping, for both big and little endian systems)

- Non-word (byte) aligned host buffer addresses

- Automatically detects presence of Tx data or Rx free buffers

- Virtual FIFO buffers (PCI bursts treated as a single address)

- · Hardware indication of BOM

- Allows isolation of system resources

- Status queue interrupt delay

### Designer Toolkit

- Evaluation hardware and software

- Reference schematics

- Hardware Programming Interface-RS823xHPI reference source code (C)

-Continued-

## Generous Implementation of OAM-PM Protocols

- Detection of all F4/F5 OAM flows

- Internal PM monitoring and generation for up to 128 VCCs

- · Optional global OAM Rx/Tx queues

- In-line OAM insertion and generation

### Standards-Based I/O

- 33 MHz PCI 2.1 (to 40 MHz)

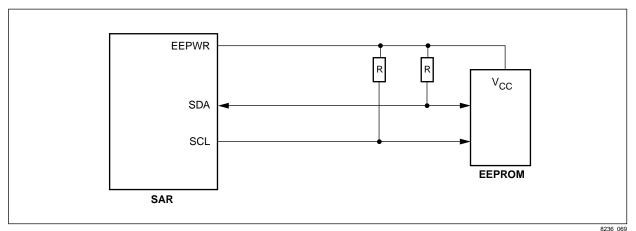

- Serial EEPROM to store PCI configuration information

- · PHY interfaces

- UTOPIA master (Level 1)

- UTOPIA slave (Level 1)

- UTOPIA master (Level 2)

- UTOPIA slave (Level 2)

- Flexible SAR-shared memory architecture

- · Optional local control interface

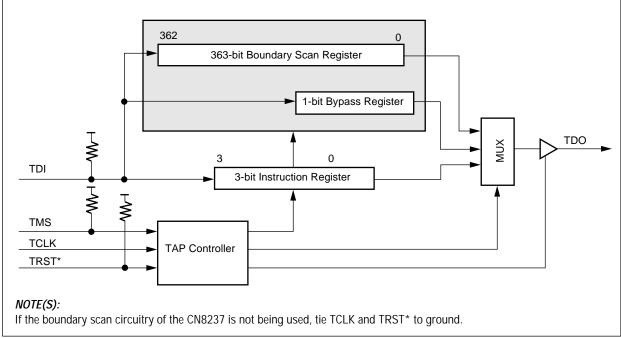

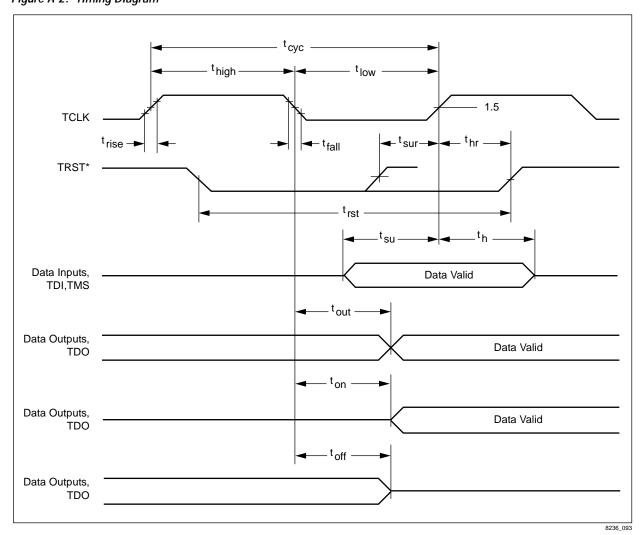

- · Boundary scan for board-level testing

- · Source loopback, for diagnostics

- Glueless connection to Mindspeed's ATM physical layer device, the RS825x and Bt8223

### **Standards Compliance**

- UNI/NNI 3.1

- TM 4.0/TM4.1

- · Bellcore GR-1248

- · ATM Forum B-ICI V2.0

## **Table of Contents**

| Tabl | e of Contents                                                                                                                                                                                                                                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List | <b>of Figures</b> 1-19                                                                                                                                                                                                                                                                                                                  |

| List | of Tables1-23                                                                                                                                                                                                                                                                                                                           |

| CN8  | 236 Product Overview                                                                                                                                                                                                                                                                                                                    |

| 1.1  | Introduction                                                                                                                                                                                                                                                                                                                            |

| 1.2  | Service-Specific Performance Accelerators                                                                                                                                                                                                                                                                                               |

| 1.3  | Designer Toolkit                                                                                                                                                                                                                                                                                                                        |

| Arch | nitecture Overview                                                                                                                                                                                                                                                                                                                      |

| 2.1  | Introduction                                                                                                                                                                                                                                                                                                                            |

| 2.2  | High Performance Host Architecture with Buffer Isolation2-22.2.1 Multiple ATM Clients2-22.2.2 CN8236 Queue Structure2-32.2.3 Buffer Isolation Utilizing Descriptor-Based Buffer Chaining2-62.2.4 Status Queue Relation to Buffers and Descriptors2-82.2.5 Write-only Control/Status2-102.2.6 Scatter/Gather DMA2-102.2.7 Interrupts2-11 |

| 2.3  | Automated Segmentation Engine                                                                                                                                                                                                                                                                                                           |

| 2.4  | Automated Reassembly Engine                                                                                                                                                                                                                                                                                                             |

| 2.5  | Advanced xBR Traffic Management       2-16         2.5.1 CBR Traffic       2-18         2.5.2 VBR Traffic       2-18         2.5.3 ABR Traffic       2-19         2.5.4 UBR Traffic       2-19         2.5.5 GFR Traffic       2-19                                                                                                     |

|      | List CN8 1.1 1.2 1.3 Arch 2.1 2.2                                                                                                                                                                                                                                                                                                       |

|     |      | 2.5.6 xBR Cell Scheduler       2-20         2.5.7 ABR Flow Control Manager       2-21 |

|-----|------|---------------------------------------------------------------------------------------|

|     | 2.6  | Burst FIFO Buffers 2-22                                                               |

|     | 2.7  | Implementation of OAM-PM Protocols                                                    |

|     | 2.8  | Standards-Based I/O 2-23                                                              |

|     | 2.9  | Electrical/Mechanical 2-25                                                            |

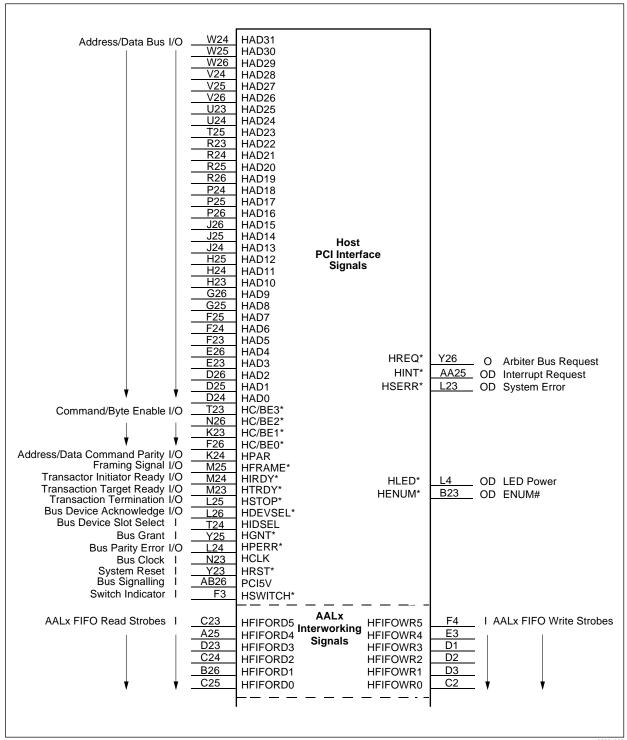

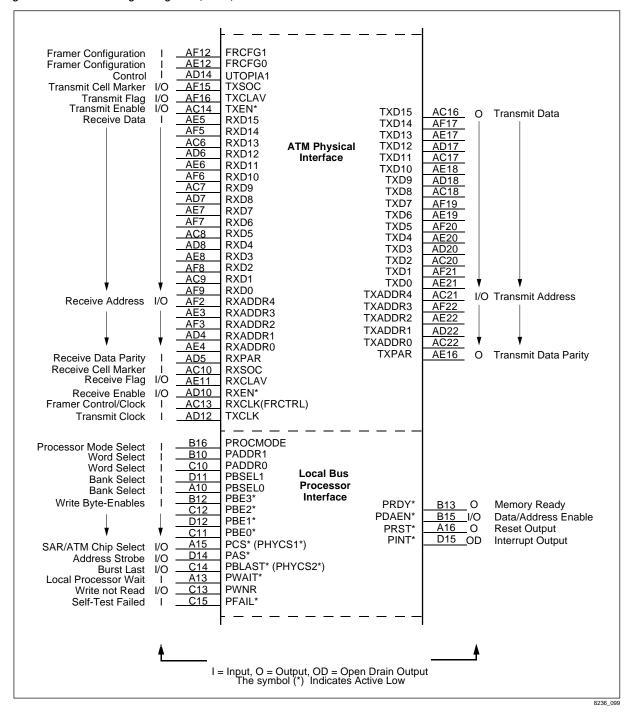

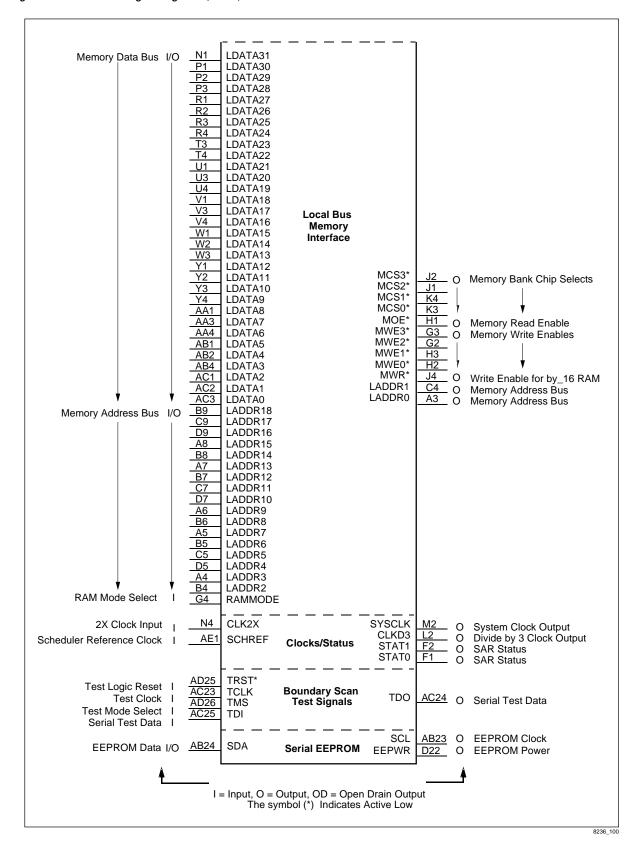

|     | 2.10 | Logic Diagram and Pin Descriptions                                                    |

|     | 2.10 | Logic Diagram and Pin Descriptions 2-25                                               |

| 3.0 | Host | <b>Interface</b>                                                                      |

|     | 3.1  | Overview                                                                              |

|     | 3.2  | Multiple Client Architecture                                                          |

|     |      | 3.2.1 Logical Clients                                                                 |

|     |      | 3.2.2 Resource Allocation                                                             |

|     |      | 3.2.3 Resource Isolation                                                              |

|     |      | 3.2.4 Peer-to-Peer Transfers                                                          |

|     |      | 3.2.5 Local Processor Clients                                                         |

|     | 3.3  | Write-only Control and Status                                                         |

|     |      | 3.3.1 Write-only Control Queues                                                       |

|     |      | 3.3.1.1 Control Variables                                                             |

|     |      | 3.3.1.2 Queue Management                                                              |

|     |      | 3.3.1.3 Underflow Conditions                                                          |

|     |      | 3.3.2 Write-only Status Queues                                                        |

|     |      | 3.3.2.1 Control Variables                                                             |

|     |      | 3.3.2.2 Queue Management                                                              |

|     |      | 3.3.2.4 Status Queue Interrupt Delay                                                  |

|     |      | 3.3.2.4 Status Quede Interrupt Delay                                                  |

| 4.0 | Segr | mentation Coprocessor                                                                 |

|     | 4.1  | <b>Overview</b>                                                                       |

|     | 4.2  | Segmentation Functional Description                                                   |

|     |      | 4.2.1 Segmentation VCCs                                                               |

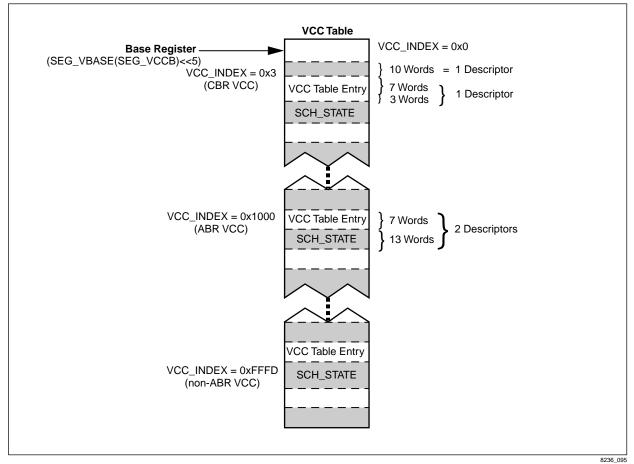

|     |      | 4.2.1.1 Segmentation VCC Table                                                        |

|     |      | 4.2.1.2 VCC Identification                                                            |

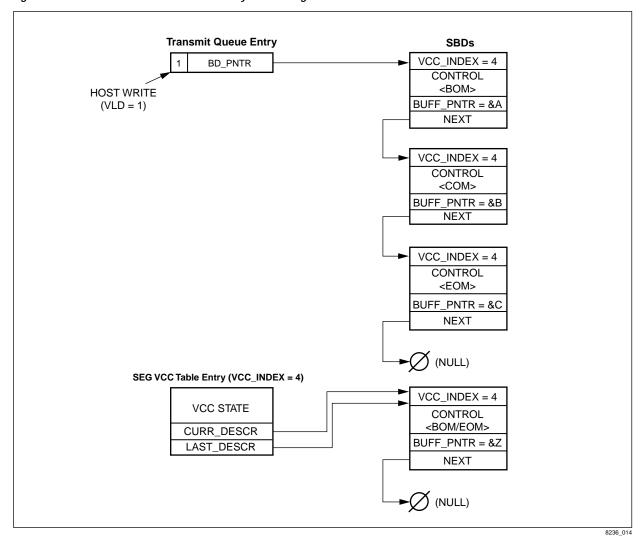

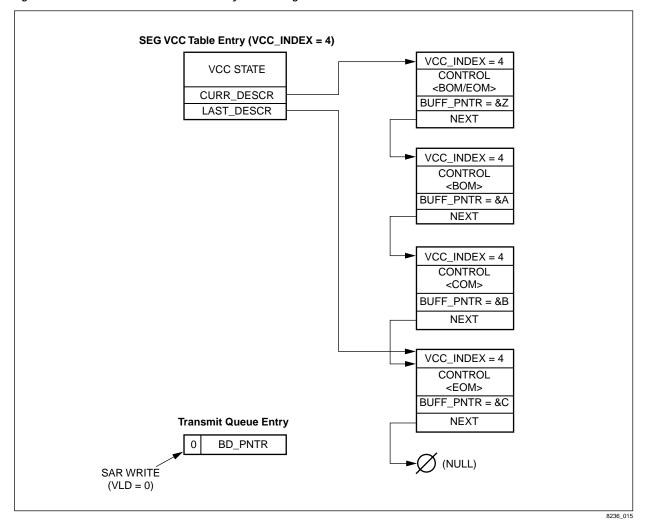

|     |      | 4.2.2 Submitting Segmentation Data                                                    |

|     |      | 4.2.2.1 User Data Format                                                              |

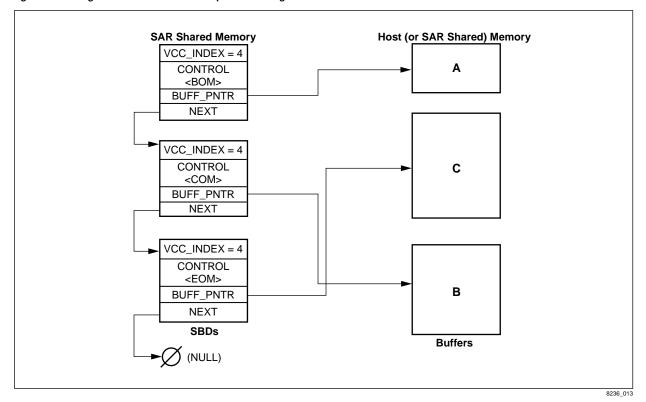

|     |      | 4.2.2.2 Buffer Descriptors                                                            |

|     |      | 4.2.2.3 Host Linked Segmentation Buffer Descriptors                                   |

|     |      | 4.2.2.4 Transmit Queues                                                               |

|     |     | 4.2.2.5 Partial PDUs                                           | 4-7    |  |  |  |  |  |

|-----|-----|----------------------------------------------------------------|--------|--|--|--|--|--|

|     |     | 4.2.2.6 Virtual Paths                                          | 4-7    |  |  |  |  |  |

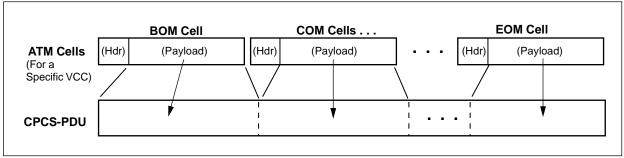

|     |     | 4.2.3 CPCS-PDU Processing                                      | 4-8    |  |  |  |  |  |

|     |     | 4.2.3.1 AAL5                                                   | 4-8    |  |  |  |  |  |

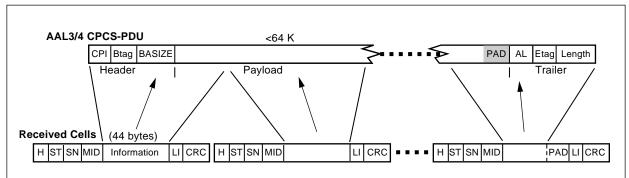

|     |     | 4.2.3.2 AAL3/4                                                 | 4-9    |  |  |  |  |  |

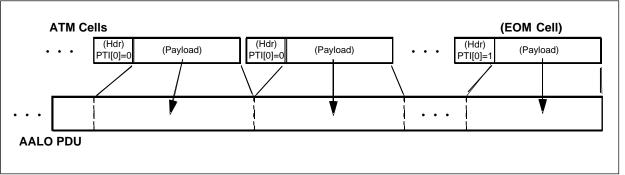

|     |     | 4.2.3.3 AALO                                                   | . 4-11 |  |  |  |  |  |

|     |     | 4.2.4 ATM PHY Layer Interface                                  | . 4-12 |  |  |  |  |  |

|     |     | 4.2.4.1 Head-of-Line Flushing (HoLF)                           | . 4-12 |  |  |  |  |  |

|     |     | 4.2.5 Status Reporting                                         | . 4-13 |  |  |  |  |  |

|     |     | 4.2.6 Virtual FIFO Buffers                                     | . 4-13 |  |  |  |  |  |

|     | 4.3 | Segmentation Control and Data Structures                       |        |  |  |  |  |  |

|     |     | 4.3.1 Segmentation VCC Table Entry                             |        |  |  |  |  |  |

|     |     | 4.3.2 Data Buffers                                             |        |  |  |  |  |  |

|     |     | 4.3.3 Segmentation Buffer Descriptors                          |        |  |  |  |  |  |

|     |     | 4.3.4 Transmit Queues                                          |        |  |  |  |  |  |

|     |     | 4.3.4.1 Entry Format                                           |        |  |  |  |  |  |

|     |     | 4.3.4.2 Transmit Queue Management                              |        |  |  |  |  |  |

|     |     | 4.3.5 Routing Tags                                             | . 4-25 |  |  |  |  |  |

|     |     | 4.3.6 Segmentation Status Queues                               | . 4-28 |  |  |  |  |  |

|     |     | 4.3.6.1 Entry Format                                           | . 4-28 |  |  |  |  |  |

|     |     | 4.3.6.2 Status Queue Management                                | . 4-30 |  |  |  |  |  |

|     |     | 4.3.6.3 Status Queue Overflow                                  | . 4-30 |  |  |  |  |  |

|     |     | 4.3.7 Segmentation Internal SRAM Memory Map                    | . 4-31 |  |  |  |  |  |

| 5.0 | Rea | Reassembly Coprocessor                                         |        |  |  |  |  |  |

|     | 5.1 | Overview                                                       |        |  |  |  |  |  |

|     | 5.2 | Reassembly Functional Description                              |        |  |  |  |  |  |

|     | 0.2 | 5.2.1 Reassembly VCCs                                          |        |  |  |  |  |  |

|     |     | 5.2.1.1 Relation to Segmentation VCCs                          |        |  |  |  |  |  |

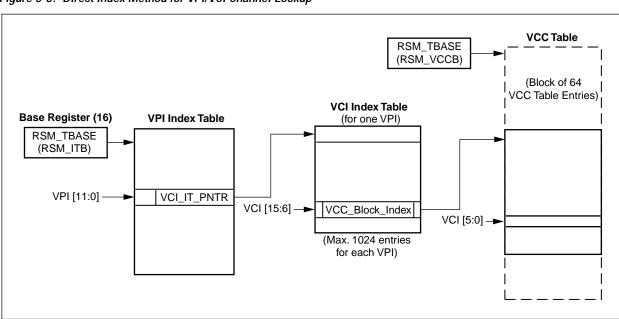

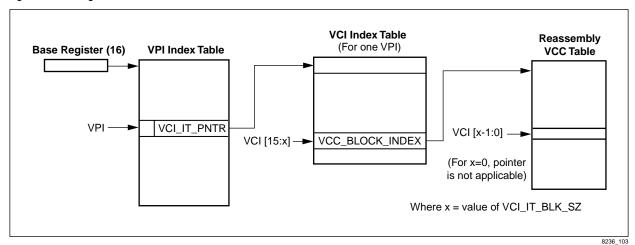

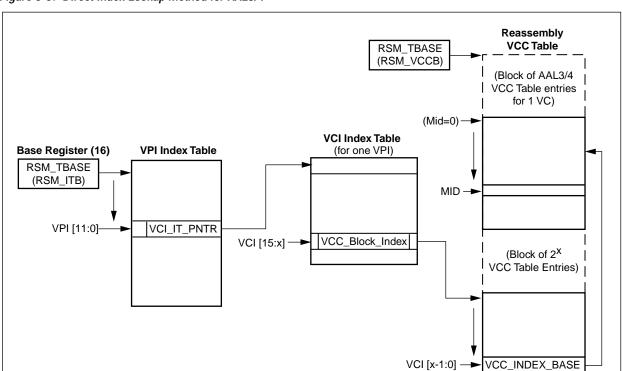

|     |     | 5.2.2 Channel Lookup                                           |        |  |  |  |  |  |

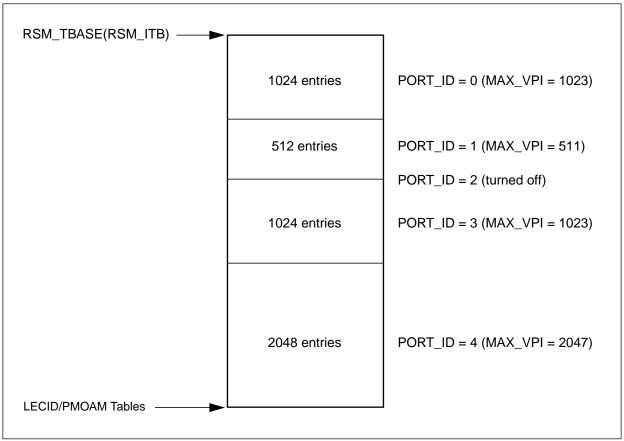

|     |     | 5.2.2.1 Programmable Block Size for VCC Table/ VCI Index Table |        |  |  |  |  |  |

|     |     | 5.2.2.2 Setup                                                  |        |  |  |  |  |  |

|     |     | 5.2.2.3 Operation                                              |        |  |  |  |  |  |

|     |     | 5.2.2.4 AAL3/4 Lookup                                          |        |  |  |  |  |  |

|     |     | 5.2.2.5 Variable VPI/PORT_ID Lookup (Multi-phy Support)        |        |  |  |  |  |  |

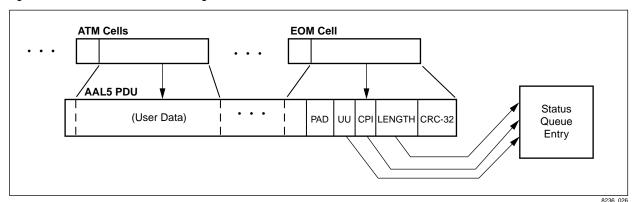

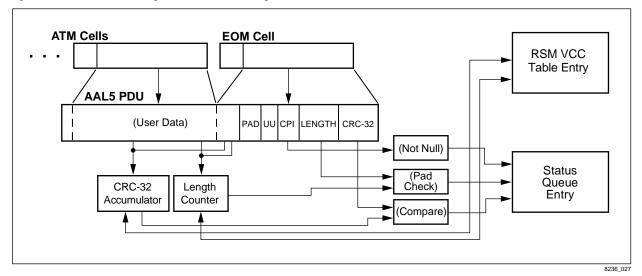

|     | 5.3 | CPCS-PDU Processing                                            | . 5-9  |  |  |  |  |  |

|     |     | 5.3.1 AAL5 Processing                                          |        |  |  |  |  |  |

|     |     | 5.3.1.1 AAL5 COM Processing                                    |        |  |  |  |  |  |

|     |     | 5.3.1.2 AAL5 EOM Processing                                    |        |  |  |  |  |  |

|     |     | 5.3.1.3 AAL5 Error Conditions                                  |        |  |  |  |  |  |

|     |     | 5.3.2 AAL3/4 Processing                                        |        |  |  |  |  |  |

|     |     | 5.3.2.1 AAL3/4 Per-Cell Processing                             |        |  |  |  |  |  |

|     |     | · · · · · · · · · · · · · · · · · · ·                          |        |  |  |  |  |  |

|     |     | 5.3.2.2 AAL3/4 Additional BOM/SSM Processing                   | . 5-14 |  |  |  |  |  |

|     |     | 5.3.2.2 AAL3/4 Additional BOM/SSM Processing                   |        |  |  |  |  |  |

|     |        | 5.3.2.4         | AAL3/4 Additional EOM/SSM Processing                                | 5-15 |

|-----|--------|-----------------|---------------------------------------------------------------------|------|

|     |        | 5.3.2.5         | AAL3/4 MIB Counters                                                 | 5-15 |

|     | 5.3.3  | AALO Proc       | essing                                                              | 5-16 |

|     |        | 5.3.3.1         | Termination Methods                                                 | 5-16 |

|     |        | 5.3.3.2         | AALO Error Conditions                                               | 5-16 |

|     | 5.3.4  | ATM Heade       | er Processing                                                       | 5-17 |

|     | 5.3.5  | <b>BOM Sync</b> | hronization Signal                                                  | 5-17 |

|     |        | 5.3.5.1         | Prepend Index                                                       | 5-17 |

| 5.4 | Buffer | Manageme        | ent                                                                 | 5-18 |

|     |        | •               | ocal Reassembly                                                     |      |

|     | 5.4.2  |                 | thod                                                                |      |

|     | 5.4.3  |                 | Queues                                                              |      |

|     |        |                 | a Buffers                                                           |      |

|     |        |                 | n of Buffer Structures                                              |      |

|     |        | 5.4.5.1         | Buffer Descriptors                                                  | 5-22 |

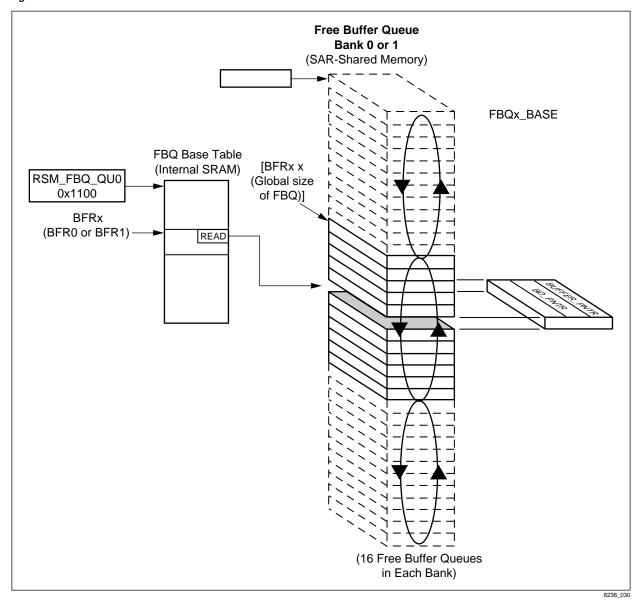

|     |        | 5.4.5.2         | Free Buffer Queue Base Table                                        |      |

|     |        | 5.4.5.3         | Free Buffer Queue Entries                                           | 5-22 |

|     |        | 5.4.5.4         | Other Initialization                                                | 5-22 |

|     | 5.4.6  | Buffer Allo     | cation                                                              | 5-23 |

|     | 5.4.7  | Error Cond      | litions                                                             | 5-23 |

|     | 5.4.8  | Early Pack      | et Discard                                                          | 5-24 |

|     |        | 5.4.8.1         | General Description                                                 | 5-24 |

|     |        | 5.4.8.2         | Frame Relay Packet Discard                                          | 5-24 |

|     |        | 5.4.8.3         | CLP Packet Discard                                                  |      |

|     |        | 5.4.8.4         | LANE-LECID Packet Discard—Echo Suppression on Multicast Data Frames | 5-25 |

|     |        | 5.4.8.5         | DMA FIFO Buffer Full                                                |      |

|     |        | 5.4.8.6         | AAL3/4 Early Packet Discard Processing                              |      |

|     |        | 5.4.8.7         |                                                                     |      |

|     | 5.4.9  | Hardware I      | PDU Time-Out                                                        |      |

|     |        | 5.4.9.1         | Reassembly Time-Out Process                                         |      |

|     |        | 5.4.9.2         | Halting Time-Out Processing.                                        |      |

|     |        | 5.4.9.3         | Timer Reset                                                         |      |

|     |        | 5.4.9.4         | Reassembly Time-Out Condition                                       |      |

|     |        |                 | Time-Out Period Calculation                                         |      |

|     | 5.4.10 |                 | D Buffer Mode                                                       |      |

|     |        |                 | Setup                                                               |      |

|     |        |                 | Operation                                                           |      |

|     |        |                 | Errors                                                              |      |

|     | 5.4.11 |                 | nctions                                                             |      |

|     |        |                 | Setup                                                               |      |

|     |        |                 | Operation                                                           |      |

|     |        | 5 4 11 3        | Credit Return                                                       | 5-29 |

|     | 5.5  | Global Statistics                                                                       | 5-31                 |  |  |

|-----|------|-----------------------------------------------------------------------------------------|----------------------|--|--|

|     | 5.6  | Status Queue Operation                                                                  | 5-32                 |  |  |

|     |      | 5.6.1 Structure                                                                         | . 5-32               |  |  |

|     |      | 5.6.1.1 Setup                                                                           | . 5-33               |  |  |

|     |      | 5.6.1.2 Operation                                                                       | . 5-34               |  |  |

|     |      | 5.6.1.3 Errors                                                                          | . 5-34               |  |  |

|     |      | 5.6.1.4 Host Detection of Status Queue Entries                                          | . 5-35               |  |  |

|     |      | 5.6.2 Status Queue Overflow or Full Condition                                           | . 5-36               |  |  |

|     | 5.7  | Reassembly Control and Data Structures                                                  | 5-37                 |  |  |

|     |      | 5.7.1 Channel Lookup Structures                                                         |                      |  |  |

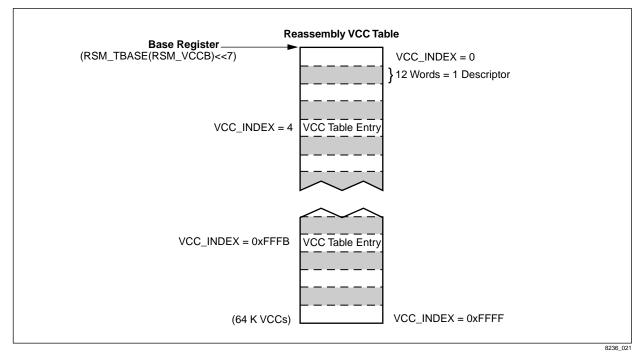

|     |      | 5.7.2 Reassembly VCC Table                                                              | . 5-39               |  |  |

|     |      | 5.7.2.1 AAL5, AAL0 and AAL3/4 VCC Table Entries                                         | . 5-40               |  |  |

|     |      | 5.7.2.2 AAL3/4 Head VCC Table Entry                                                     |                      |  |  |

|     |      | 5.7.3 Reassembly Buffer Descriptor Structure                                            |                      |  |  |

|     |      | 5.7.4 Free Buffer Queues                                                                |                      |  |  |

|     |      | 5.7.5 Reassembly Status Queues                                                          |                      |  |  |

|     |      | 5.7.6 LECID Table.                                                                      |                      |  |  |

|     |      | 5.7.7 Global Time-Out Table                                                             |                      |  |  |

|     |      | 5.7.8 Reassembly Internal SRAM Memory Map                                               | . 5-57               |  |  |

| 6.0 | Traf | fic Management                                                                          | 6-1                  |  |  |

|     | 6.1  | Overview                                                                                |                      |  |  |

|     |      | 6.1.1 xBR Cell Scheduler                                                                | 6-4                  |  |  |

|     |      | 6.1.2 ABR Flow Control Manager                                                          |                      |  |  |

|     | 6.2  | xBR Cell Scheduler Functional Description                                               | . 6-7                |  |  |

|     |      | 6.2.1 Scheduling Priority                                                               |                      |  |  |

|     |      | 6.2.1.1 16 Priority Levels + CBR                                                        |                      |  |  |

|     |      | 6.2.1.2 VCC Priority Assignment                                                         |                      |  |  |

|     |      | 6.2.2 Dynamic Schedule Table                                                            |                      |  |  |

|     |      | 6.2.2.1 Overview                                                                        | 6-7                  |  |  |

|     |      | 6.2.2.2 Schedule Table Slots                                                            | 6-8                  |  |  |

|     |      | 6.2.2.3 Schedule Slot Formats without USE_SCH_CTRL Asserted                             | . 6-10               |  |  |

|     |      | 6.2.2.4 Schedule Slot Formats with USE_SCH_CTRL Asserted                                | . 6-12               |  |  |

|     |      | 6.2.2.5 Some Scheduling Scenarios                                                       | . 6-13               |  |  |

|     |      | 6.2.3 CBR Traffic                                                                       | . 6-14               |  |  |

|     |      | 6.2.3.1 CBR Rate Selection                                                              | . <mark>6-1</mark> 4 |  |  |

|     |      | 6.2.3.2 Available Rates                                                                 | . <mark>6-1</mark> 5 |  |  |

|     |      | 6.2.3.3 CBR Cell Delay Variation (CDV)                                                  | . 6-16               |  |  |

|     |      | 6.2.3.4 CBR Channel Management                                                          | . 6-18               |  |  |

|     |      | 6.2.4 VBR Traffic                                                                       |                      |  |  |

|     |      | 6.2.4.1 Mapping CN8236 VBR Service Categories to <i>TM 4.1</i> VBR Service Categories . |                      |  |  |

|     |      | 6.2.4.2 Rate-Shaping vs. Policing                                                       |                      |  |  |

|     |      | 6.2.4.3 Single Leaky Bucket                                                             | . 6-19               |  |  |

**Table of Contents**

|     | 6.2.4.4 Dual Leaky Bucket                                          | . 6-19 |

|-----|--------------------------------------------------------------------|--------|

|     | 6.2.4.5 CLP-Based Buckets                                          | . 6-20 |

|     | 6.2.4.6 Rate Selection                                             | . 6-20 |

|     | 6.2.4.7 Real-Time VBR and CDV                                      | . 6-20 |

|     | 6.2.5 UBR Traffic                                                  | . 6-20 |

|     | 6.2.6 xBR Tunnels (Pipes)                                          | . 6-20 |

|     | 6.2.7 Guaranteed Frame Rate                                        | . 6-22 |

|     | 6.2.8 PCR Control for Priority Queues                              | . 6-23 |

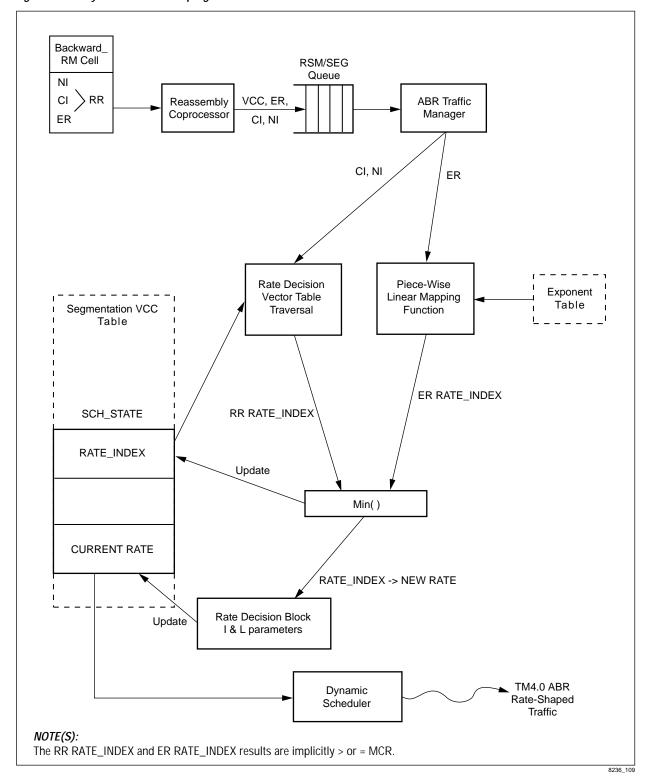

| 6.3 | ABR Flow Control Manager                                           |        |

|     | 6.3.1 A Brief Overview of <i>TM 4.1</i>                            | . 6-24 |

|     | 6.3.2 Internal ABR Feedback Control Loop                           |        |

|     | 6.3.2.1 Source Flow Control Feedback                               |        |

|     | 6.3.2.2 Destination Behavior.                                      |        |

|     | 6.3.2.3 Out-of-Rate Cells                                          |        |

|     | 6.3.3 Source and Destination Behaviors                             |        |

|     | 6.3.4 ABR VCC Parameters.                                          |        |

|     | 6.3.5 ABR Templates                                                |        |

|     | 6.3.6 Cell Type Decisions                                          |        |

|     | 6.3.6.1 In-rate Cell Streams                                       |        |

|     | 6.3.6.2 ABR Cell Decisions                                         |        |

|     | 6.3.7 Rate Decisions and Updates.                                  |        |

|     | 6.3.7.1 ABR Traffic Shaping                                        |        |

|     | 6.3.7.2 Rate Adjustment Overview                                   |        |

|     | 6.3.7.3 Backward RM Cell Flow Control                              |        |

|     | 6.3.7.4 Forward RM Cell Transmission Decisions                     |        |

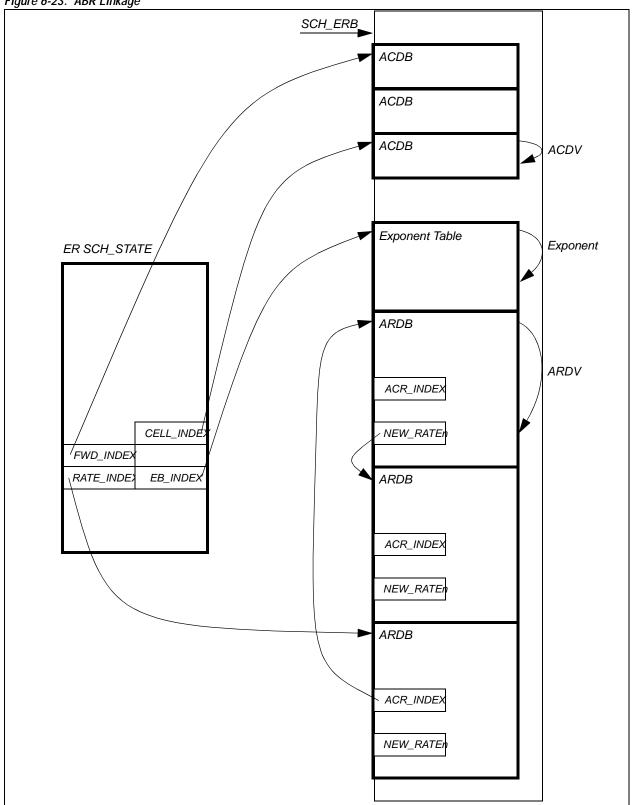

|     | 6.3.7.5 ACR Change Notification.                                   |        |

|     | 6.3.7.6 Rate Adjustment in Turnaround RM Cells                     |        |

|     | 6.3.7.7 Optional Rate Adjustment Due to Use-It-or-Lose-It Behavior |        |

|     | 6.3.8 Boundary Conditions and Out-of-Rate RM Cells                 |        |

|     | 6.3.8.1 Calculated Rate Boundaries.                                |        |

|     | 6.3.8.2 Out-of-Rate Forward RM Cell Generation.                    |        |

|     | 6.3.8.3 Out-of-Rate Backward RM Cells                              |        |

| 6.4 | GFC Flow Control Manager                                           | 6-42   |

|     | 6.4.1 A Brief Overview of GFC.                                     |        |

|     | 6.4.2 The CN8236's Implementation of GFC                           | . 6-42 |

|     | 6.4.2.1 Configuring the Link for GFC Operation                     | . 6-43 |

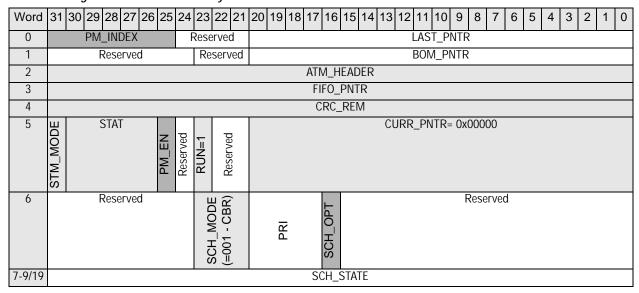

| 6.5 | Traffic Management Control and Status Structures                   | 6-44   |

|     | 6.5.1 Schedule Table                                               | . 6-44 |

|     | 6.5.2 CBR-Specific Structures                                      | . 6-44 |

|     | 6.5.2.1 CBR Traffic                                                | . 6-44 |

|     | 6.5.2.2 Tunnel Traffic                                             | . 6-44 |

|     | 6.5.2.3 SCH_STATE Fields For CBR                                   | . 6-45 |

|     | 6.5.3 VBR-Specific Structure                                       | . 6-46 |

|     | 6.5.3.1 VBR SCH_STATE                                              | . 6-46 |

| ATM ServiceSAR Plus with xBR Traffic Manageme | ATM | Service | SAR Plu | s with | xBRT | Traffic | Mana | gemei |

|-----------------------------------------------|-----|---------|---------|--------|------|---------|------|-------|

|-----------------------------------------------|-----|---------|---------|--------|------|---------|------|-------|

|     |     | 6.5.3.2 VBR1 or VBR2 Schedule State Table                          | . 6-46 |

|-----|-----|--------------------------------------------------------------------|--------|

|     |     | 6.5.3.3 Bucket Table for VBR2 and VBRC                             | . 6-48 |

|     |     | 6.5.4 GFR-Specific Structures                                      | . 6-49 |

|     |     | 6.5.4.1 GFR Schedule State Table                                   | . 6-49 |

|     |     | 6.5.4.2 GFR MCR Limit Bucket Table                                 | . 6-50 |

|     |     | 6.5.5 ABR-Specific Structures                                      | . 6-51 |

|     |     | 6.5.5.1 ABR Schedule State Table                                   | . 6-51 |

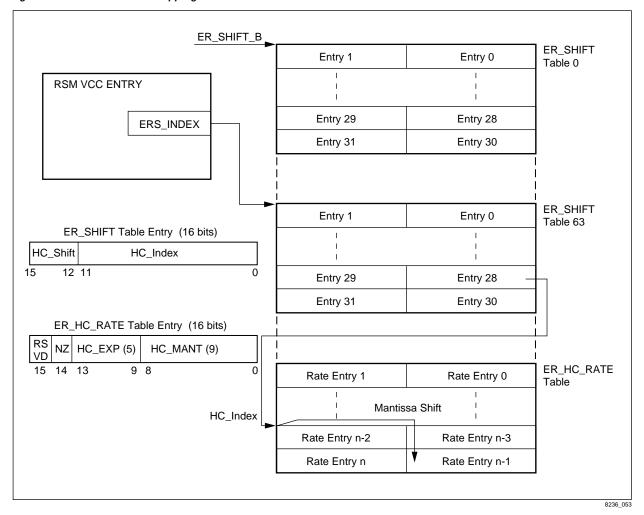

|     |     | 6.5.6 ABR Instruction Tables                                       | . 6-55 |

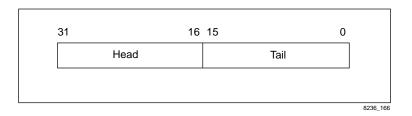

|     |     | 6.5.7 RS_QUEUE                                                     | . 6-59 |

|     |     | 6.5.8 Scheduler Internal SRAM Registers                            | . 6-60 |

| 7.0 | OAN | // Functions                                                       | 7-1    |

|     | 7.1 | OAM Overview                                                       |        |

|     |     | 7.1.1 OAM Functions Supported                                      |        |

|     |     | 7.1.2 OAM Flows Supported.                                         |        |

|     |     | 7.1.2.1 F4 OAM Flow                                                |        |

|     |     | 7.1.2.2 F5 OAM Flow                                                |        |

|     |     | 7.1.2.3 Performance Monitoring (PM)                                |        |

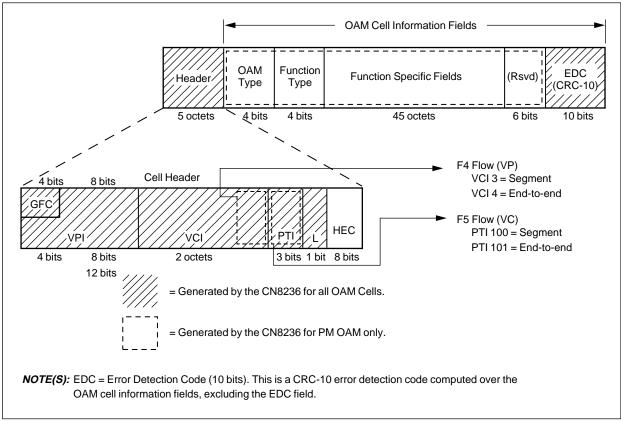

|     |     | 7.1.3 OAM Cell Format                                              |        |

|     |     | 7.1.4 Local vs. Host Processing of OAM                             |        |

|     | 7.2 | Segmentation of OAM Cells                                          | . 7-7  |

|     |     | 7.2.1 Key OAM-Related Fields for OAM Segmentation                  |        |

|     |     | 7.2.1.1 Segmentation Buffer Descriptors                            |        |

|     |     | 7.2.1.2 Low Latency Transmission                                   |        |

|     |     | 7.2.1.3 Segmentation Status Queue                                  |        |

|     |     | 7.2.1.4 F4 Flow                                                    |        |

|     |     | 7.2.2 Error Condition During OAM Segmentation                      |        |

|     | 7.3 | Reassembly of OAM Cells                                            | . 7-9  |

|     |     | 7.3.1 Key OAM-Related Fields for OAM Reassembly                    |        |

|     |     | 7.3.1.1 Reassembly VCC State Table                                 |        |

|     |     | 7.3.1.2 Reassembly Status Queue                                    |        |

|     |     | 7.3.1.3 F4 Flow                                                    |        |

|     |     | 7.3.2 OAM Reassembly Operation.                                    |        |

|     |     | 7.3.3 Error Conditions During OAM Reassembly                       |        |

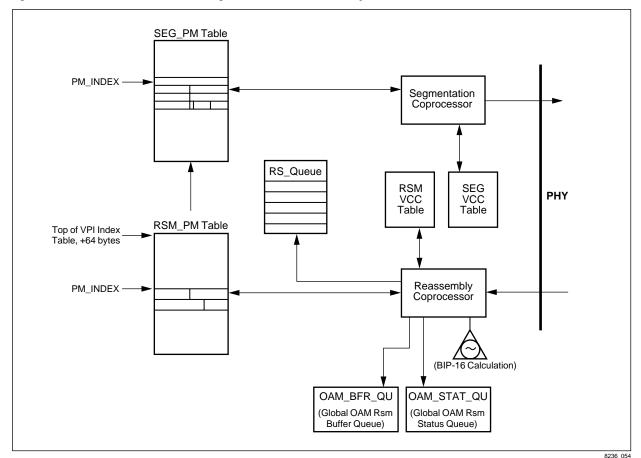

|     | 7.4 | PM Processing                                                      |        |

|     |     | 7.4.1 Initializing PM Operation                                    |        |

|     |     | 7.4.2 Setting Up Channels for PM Operation                         |        |

|     |     | 7.4.3 PM Operation                                                 |        |

|     |     | 7.4.3.1 Generation of Forward Monitoring PM Cells.                 |        |

|     |     | 7.4.3.2 Reassembly of Forward Monitoring PM Cells                  |        |

|     |     | 7.4.3.3 Reassembly of Backward Reporting PM Cells                  |        |

|     |     | 7.4.3.4 Turnaround and Segmentation of Backward Reporting PM Cells |        |

|     |     | 7.4.3.5 Turnaround of Backward Reporting PM Cells ONLY             |        |

|     |     | 7.4.4 Error Conditions During PM Processing                        |        |

|     |     | 7.4.5 PASS OAM Function                                            |        |

|      | 7.5  | OAM Control and Status Structures                                    |  |  |  |  |  |  |

|------|------|----------------------------------------------------------------------|--|--|--|--|--|--|

|      |      | 7.5.1 SEG_PM Structure                                               |  |  |  |  |  |  |

|      |      | 7.5.2 RSM_PM Table                                                   |  |  |  |  |  |  |

| 8.0  | DMA  | Coprocessor8-1                                                       |  |  |  |  |  |  |

|      | 8.1  | <b>Overview</b>                                                      |  |  |  |  |  |  |

|      | 8.2  | <b>DMA Read</b>                                                      |  |  |  |  |  |  |

|      | 8.3  | <b>DMA Write</b>                                                     |  |  |  |  |  |  |

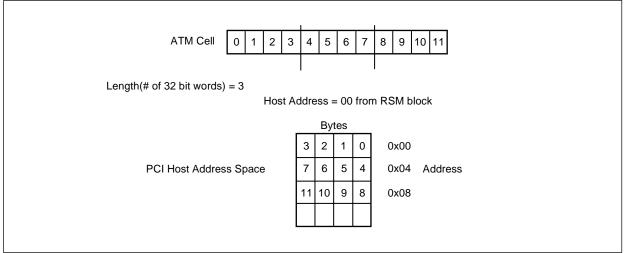

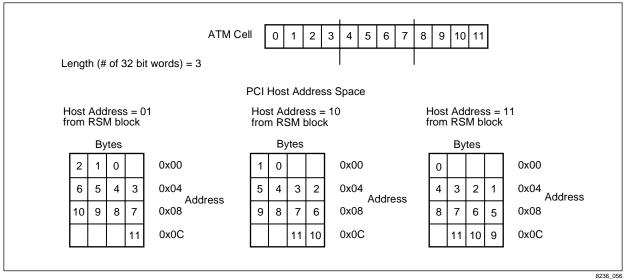

|      | 8.4  | Misaligned Transfers 8-2                                             |  |  |  |  |  |  |

|      | 8.5  | Control Word Transfers                                               |  |  |  |  |  |  |

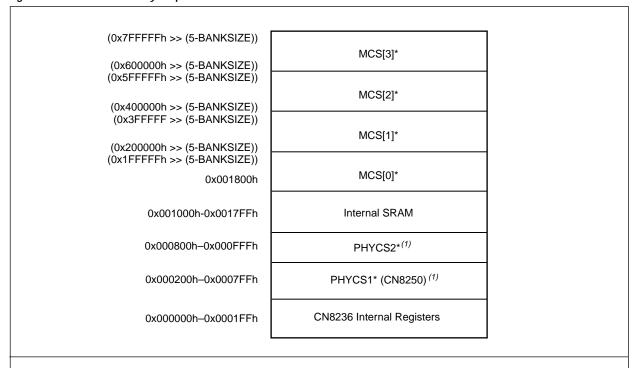

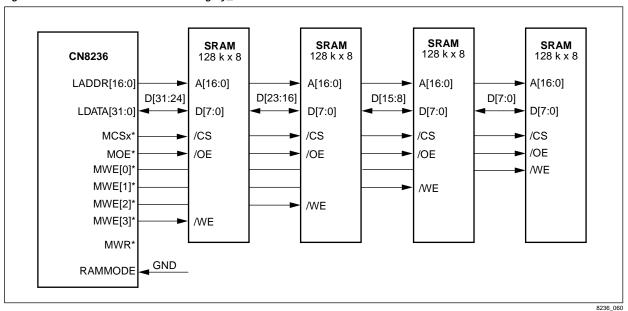

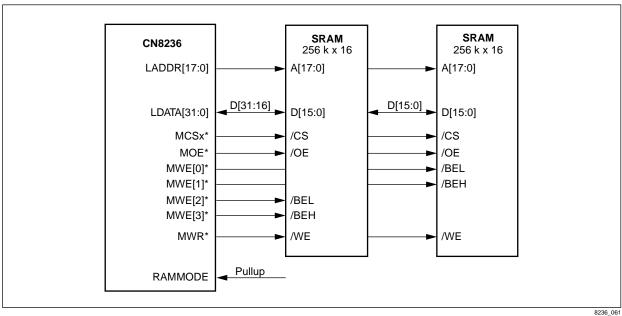

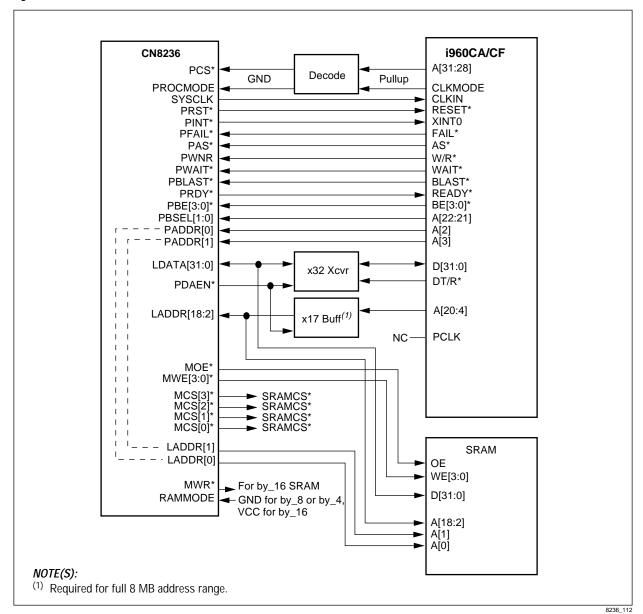

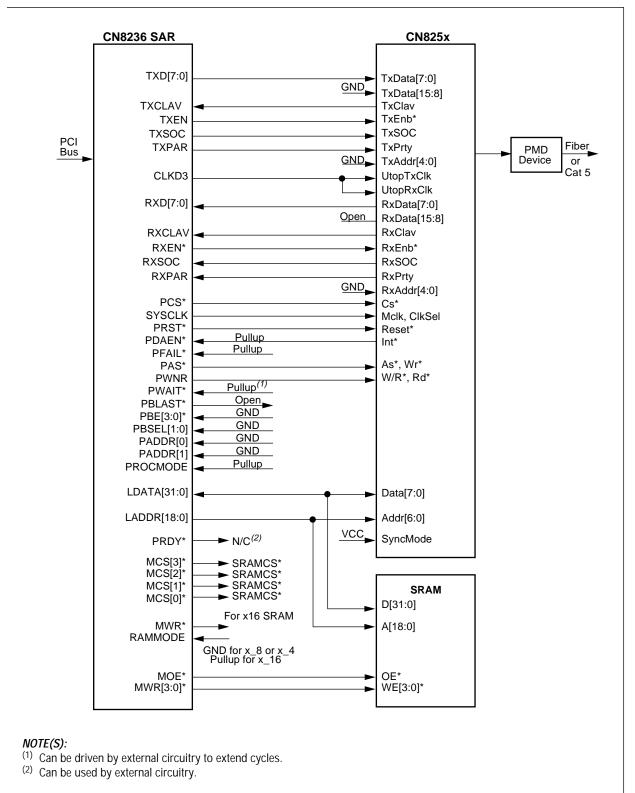

| 9.0  | Loca | Il Memory Interface                                                  |  |  |  |  |  |  |

|      | 9.1  | <b>Overview</b>                                                      |  |  |  |  |  |  |

|      | 9.2  | Memory Bank Characteristics                                          |  |  |  |  |  |  |

|      | 9.3  | Memory Size Analysis                                                 |  |  |  |  |  |  |

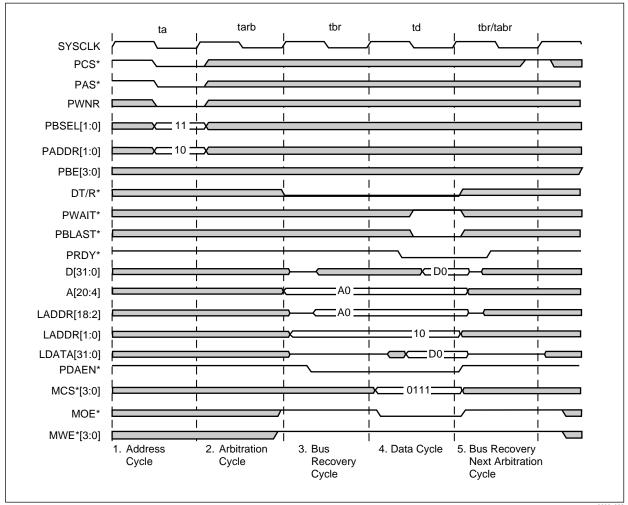

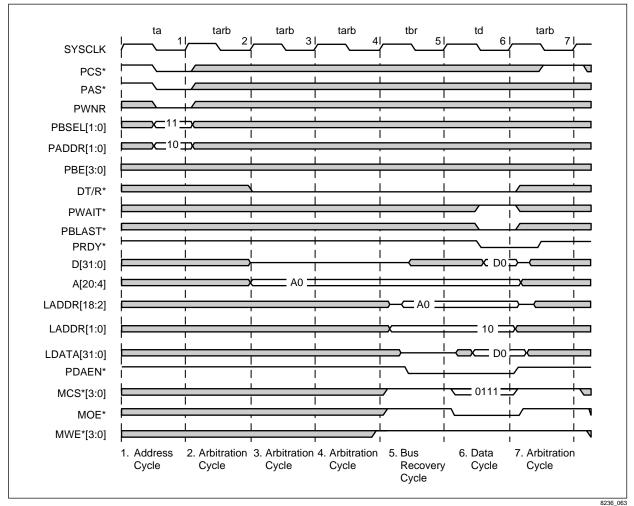

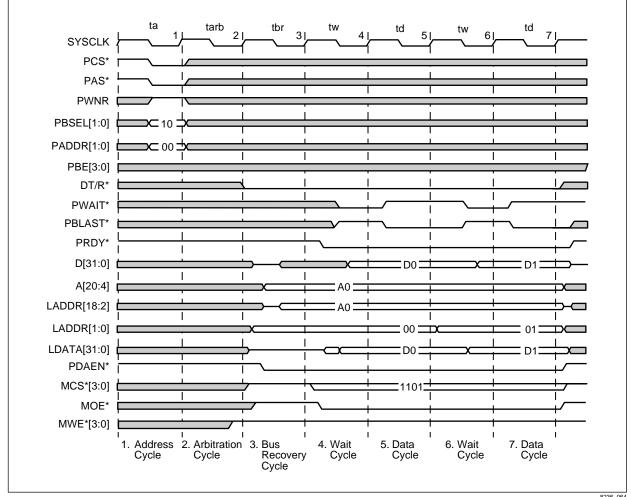

| 10.0 | Loca | Local Processor Interface                                            |  |  |  |  |  |  |

|      | 10.1 | <b>Overview</b>                                                      |  |  |  |  |  |  |

|      | 10.2 | Interface Pin Descriptions                                           |  |  |  |  |  |  |

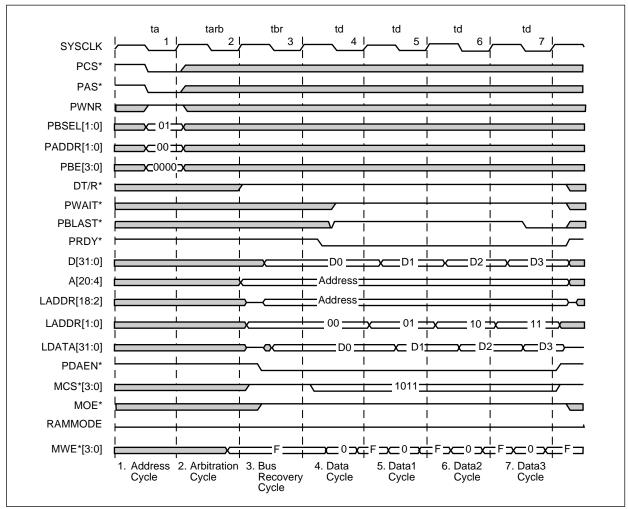

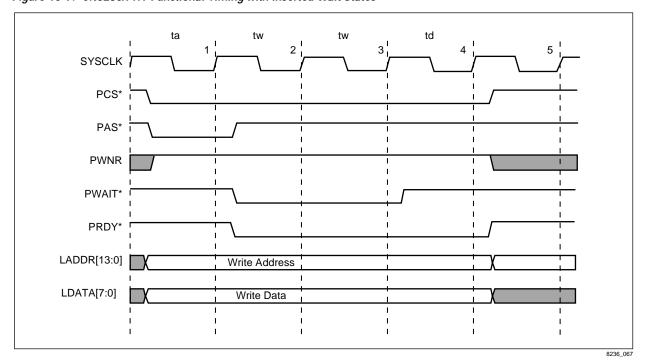

|      | 10.3 | Bus Cycle Descriptions                                               |  |  |  |  |  |  |

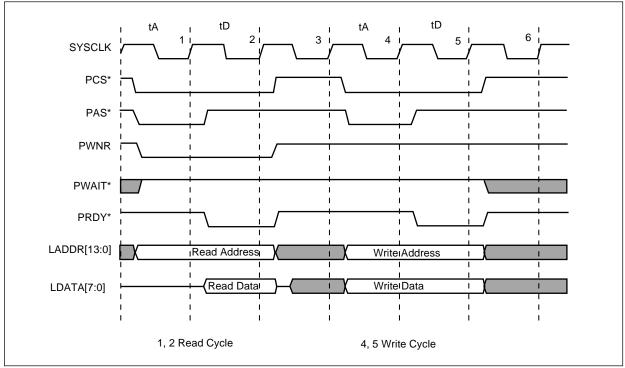

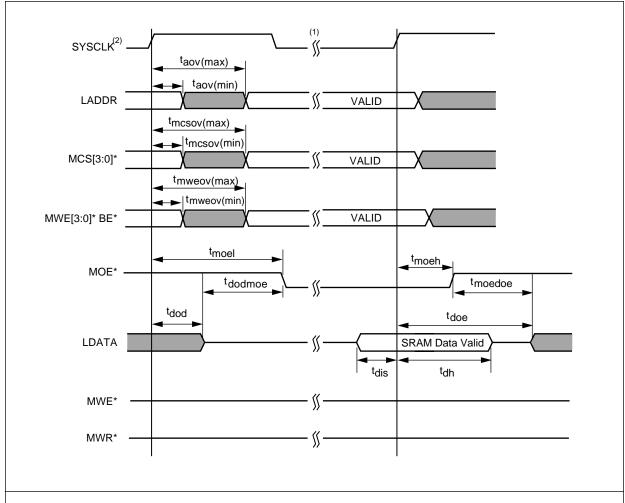

|      |      | 10.3.1 Single Read Cycle, Zero Wait State Example                    |  |  |  |  |  |  |

|      |      | 10.3.2 Single Read Cycle, Wait States Inserted By Memory Arbitration |  |  |  |  |  |  |

|      |      | 10.3.3 Double Read Burst With Processor Wait States                  |  |  |  |  |  |  |

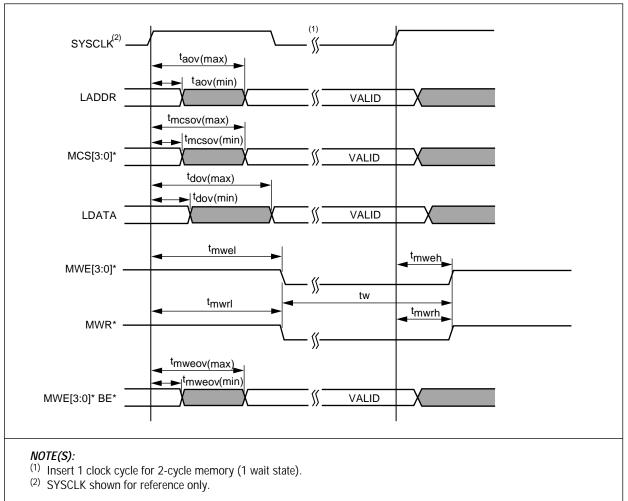

|      |      | 10.3.5 Quad Write Burst, No Wait States                              |  |  |  |  |  |  |

|      | 10.4 | Processor Interface Signals                                          |  |  |  |  |  |  |

|      | 10.5 | Local Processor Operating Mode                                       |  |  |  |  |  |  |

|      | 10.6 | Standalone Operation                                                 |  |  |  |  |  |  |

|      |      | 10.6.1 Microprocessor Interface for Multiple Physical Devices        |  |  |  |  |  |  |

|      | 10.7 | <b>System Clocking</b>                                               |  |  |  |  |  |  |

|      | 10.8 | Real-Time Clock Alarm                                                |  |  |  |  |  |  |

|      | 10.9 | CN8236 Reset                                                         |  |  |  |  |  |  |

| 11.0 | PCII | Bus Interface                                                        |  |  |  |  |  |  |

|      | 11.1 | <b>Overview</b>                                                      |  |  |  |  |  |  |

|      | 11.2 | Unimplemented PCI Bus Interface Functions                            |  |  |  |  |  |  |

|      | 11.3 | PCI Configuration Space                                              |  |  |  |  |  |  |

|      | 11.4 | PCI Bus Master Logic                                                 |  |  |  |  |  |  |

|      | 11.5 | Burst FIFO Buffers                                                   |  |  |  |  |  |  |

|      |      |                                                                      |  |  |  |  |  |  |

|      | 11.6  | PCI Bus Slave Logic                                             |

|------|-------|-----------------------------------------------------------------|

|      | 11.7  | Byte Swapping of Control Structures                             |

|      | 11.8  | Power Management                                                |

|      | 11.9  | Interface Module to Serial EEPROM                               |

|      |       | 11.9.1 EEPROM Format                                            |

|      |       | 11.9.2 Loading the EEPROM Data at Reset                         |

|      |       | 11.9.3 Accessing the EEPROM                                     |

|      |       | 11.9.4 Using the Subsystem ID Without an EEPROM                 |

|      | 11.10 | PCI Host Address Map                                            |

| 12.0 | ATM   | UTOPIA Interface                                                |

|      | 12.1  | Overview of ATM UTOPIA Interface                                |

|      | 12.2  | ATM UTOPIA Interface Logic                                      |

|      | 12.3  | ATM Physical I/O Pins                                           |

|      |       | 12.3.1 UTOPIA Interface                                         |

|      | 12.4  | UTOPIA Level 2 Interface                                        |

|      |       | 12.4.1 Cell Tagging                                             |

|      |       | 12.4.2 UTOPIA Configuration Control                             |

|      |       | 12.4.3 UTOPIA Level 2 Multi-Port Operation                      |

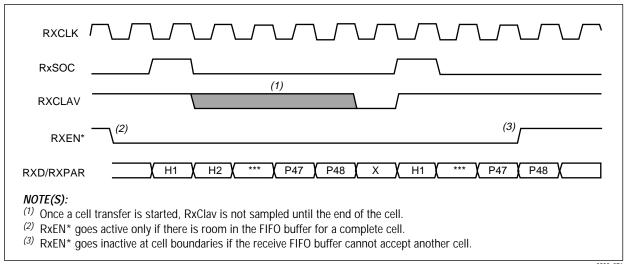

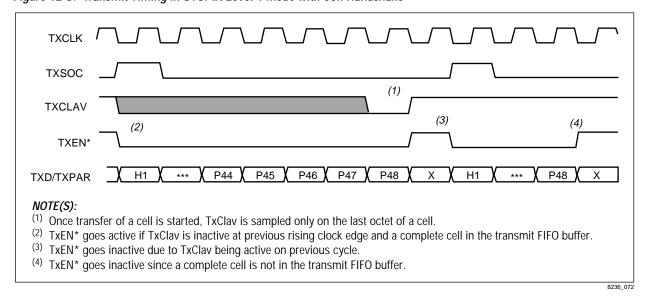

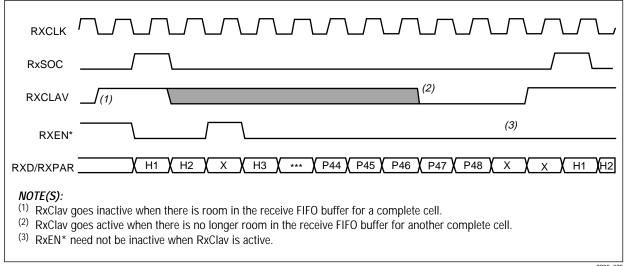

|      | 12.5  | UTOPIA Level 1 Mode Cell Handshake Timing                       |

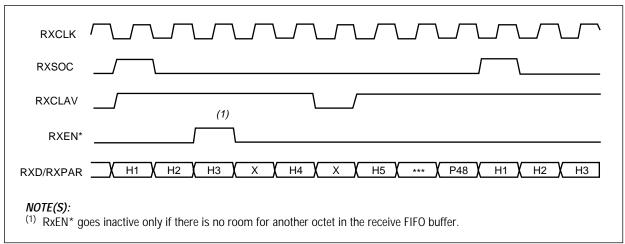

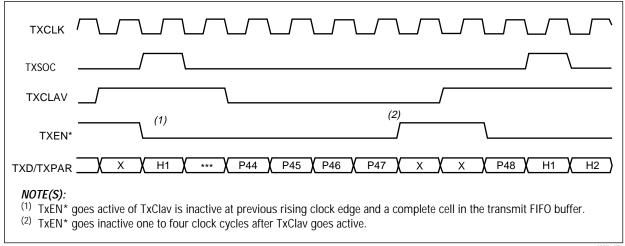

|      | 12.6  | UTOPIA Level 1 Mode Octet Handshake Timing                      |

|      | 12.7  | Slave Level 1 UTOPIA Mode                                       |

|      | 12.8  | <b>Loopback Mode</b>                                            |

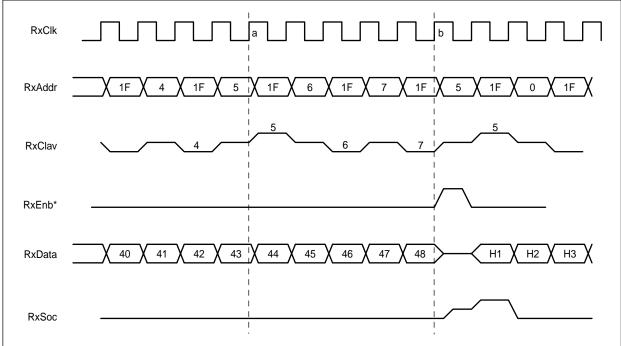

|      | 12.9  | Receive Cell Synchronization Logic                              |

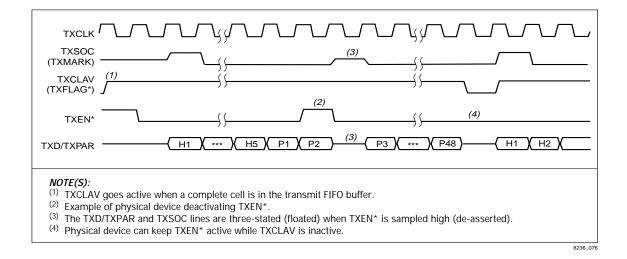

|      | 12.10 | Transmit Cell Synchronization Logic                             |

| 13.0 | AAL   | <b>( Interworking</b>                                           |

|      | 13.1  | AALx RSM Operation                                              |

|      | 13.2  | AALx SEG Operation                                              |

|      |       | 13.2.1 AALx Network Centric Operation—(EXTERNAL_SCH = 0)        |

|      |       | 13.2.2 AALx Voice Centric Operation—(EXTERNAL_SCH = 1)          |

| 14.0 | CN82  | 236 Registers                                                   |

|      | 14.1  | Control and Status Registers                                    |

|      | 14.2  | System Registers                                                |

|      | 14.3  | Segmentation Registers                                          |

|      | 14.4  | Scheduler Registers                                             |

|      |       | 14.4.1 0xc4—PCR Queue Interval 2 and 3 Register (PCR_QUE_INT23) |

|      | 14.5  | Reassembly Registers                                            |

|       | 14.6       | Counters and Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|       |            | 14.6.1 Host Interrupt Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|       | 117        | PCI Bus Interface Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|       | 14.7       | Poi bus illienace Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14-39 |

| 15.0  | SAR        | Initialization—Example Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15-1  |

|       | 15.1       | Segmentation Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|       |            | 15.1.1 Segmentation Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|       |            | 15.1.2 Segmentation Internal Memory Control Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|       |            | 15.1.3 Segmentation SAR Shared Memory Control Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

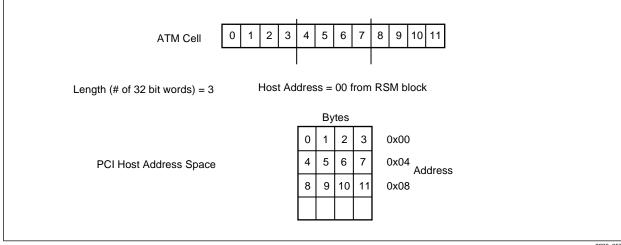

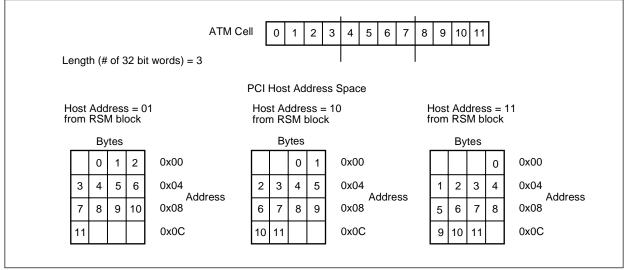

|       | 15.2       | Scheduler Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |