# RC6303 Triple Video Amplifier with Separate Enable Inputs

### Features

- · Triple video amplifier

- Independently enabled amplifiers

- 90 MHz -3 dB Bandwidth (Av = 2)

- 20 MHz ±0.1 dB gain flatness

- Stable at  $AV \ge 2$

- 0.06% differential gain (Av = 2,  $R_L = 150\Omega$ )

- $0.06^{\circ}$  differential phase (Av = 2, RL = 150 $\Omega$ )

- High CMRR (100dB), High PSRR (80 dB)

- Dual ±5V power supply

- Low offset 1.0 mV

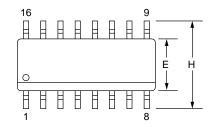

- 16-pin narrow SO package

- 300 V/µs slew rate

- Fast settling time: 0.1% in 35 ns

- TTL or CMOS compatible enable inputs

### Description

The RC6303 consists of three low power, wide band voltage feedback operational amplifiers. Each channel is capable of delivering a load current of at least 35mA. Each amplifier can be independently enabled or disabled with a TTL or CMOS signal. When disabled, the amplifier is in a high impedance output state, presenting a very high input to output isolation.

The amplifiers are optimized for video applications with gain  $\ge 2$  where low differential gain and low phase distortion are significant requirements.

The layout is optimized for minimal crosstalk between amplifiers.

## Applications

- RGB amplifier

- 3:1 crosspoint switch

- RGB switch

- Video instrumentation amplifier

- Selectable gain amplifier

- Active filter

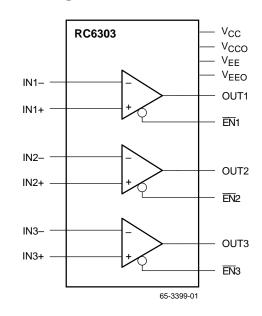

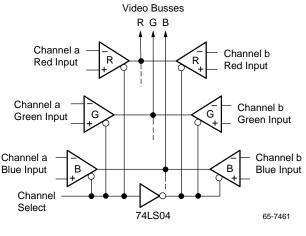

#### **Block Diagram**

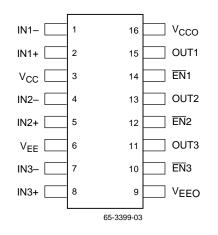

### **Pin Assignments**

#### **Pin Definitions**

| Pin<br>Name | Pin<br>Number | Pin Function Description          |  |  |  |

|-------------|---------------|-----------------------------------|--|--|--|

| EN1         | 14            | Enables amplifier 1 when low      |  |  |  |

| EN2         | 12            | Enables amplifier 2 when low      |  |  |  |

| EN3         | 10            | Enables amplifier 3 when low      |  |  |  |

| IN1–        | 1             | Amplifier 1 inverting input       |  |  |  |

| IN1+        | 2             | Amplifier 1 non-inverting input   |  |  |  |

| IN2-        | 4             | Amplifier 2 inverting input       |  |  |  |

| IN2+        | 5             | Amplifier 2 non-inverting input   |  |  |  |

| IN3–        | 7             | Amplifier 3 inverting input       |  |  |  |

| IN3+        | 8             | Amplifier 3 non-inverting input   |  |  |  |

| OUT1        | 15            | Amplifier 1 output                |  |  |  |

| OUT2        | 13            | Amplifier 2 output                |  |  |  |

| OUT3        | 11            | Amplifier 3 output                |  |  |  |

| Vcc         | 3             | Analog positive supply            |  |  |  |

| Vcco        | 16            | Positive supply for output stages |  |  |  |

| VEE         | 6             | Analog negative supply            |  |  |  |

| VEEO        | 9             | Negative supply for output stages |  |  |  |

### **Absolute Maximum Ratings**

(beyond which the device may be damaged)<sup>1</sup>

| Parameter                                               | Min                  | Тур | Max  | Units |

|---------------------------------------------------------|----------------------|-----|------|-------|

| Positive power supply, VCC                              |                      |     | 7    | V     |

| Negative power supply, VEE                              |                      |     | -7   | V     |

| Differential input voltage                              |                      |     | 10   | V     |

| Operating Temperature                                   | 0                    |     | +70  | °C    |

| Storage Temperature                                     | -40                  |     | +125 | °C    |

| Junction Temperature                                    |                      |     | 150  | °C    |

| Lead Soldering Temperature (10 seconds)                 |                      |     | 300  | °C    |

| Short circuit tolerance: No more than one output can be | e shorted to ground. |     |      |       |

Note:

1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

# **Operating Conditions**

| Parameter                            |                         | Min   | Тур  | Max   | Units |

|--------------------------------------|-------------------------|-------|------|-------|-------|

| V <sub>CC</sub> Power Supply Voltage |                         | 4.75  | 5.0  | 5.25  | V     |

| VEE                                  | Negative Supply Voltage | -4.75 | -5.0 | -5.25 | V     |

| θJA                                  | SO16 thermal resistance |       | 105  |       | °C/W  |

### **DC Characteristics**

$V_{CC} = 5V$ ,  $V_{EE} = -5V$ ,  $A_V = 2$ ,  $R_{LOAD} = 150\Omega$ ,  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ , unless otherwise specified. Open Loop.

| Parameter                 |                                                | Conditions               | Min  | Тур  | Max | Units |

|---------------------------|------------------------------------------------|--------------------------|------|------|-----|-------|

| Vos                       | Input Offset Voltage                           | No Load                  |      | 1.0  | ±5  | mV    |

| $\Delta VOS/\Delta T$     | Offset Voltage Drift <sup>1</sup>              |                          |      | 6.0  | ±50 | μV/°C |

| IB                        | Input Bias Current                             |                          |      | ±1.0 | ±5  | μΑ    |

| $\Delta I_{B} / \Delta T$ | Input Bias Current Drift <sup>1</sup>          |                          |      | ±8.0 | ±50 | nA/°C |

| Rin                       | Input Resistance <sup>1</sup>                  |                          | 1    |      |     | MΩ    |

| Cin                       | Input Capacitance <sup>1</sup>                 |                          |      | 0.5  | 2   | pF    |

| CMIR                      | Common Mode Input Range                        |                          | ±2.5 |      |     | V     |

| CMRR                      | Common Mode Rejection Ratio                    | No Load                  | 70   | 100  |     | dB    |

| PSRR                      | Power Supply Rejection Ratio                   | No Load                  | 60   | 80   |     | dB    |

| ls                        | Quiescent Supply Current                       | No Load, Whole IC        |      | 25   | 33  | mA    |

| lsd                       | Supply Current Disabled                        |                          |      | 3    | 4   | mA    |

| Rout                      | Output Impedance<br>(Closed Loop) <sup>1</sup> | Enabled, At DC           |      | 0.2  |     | Ω     |

|                           |                                                | Disabled, $V_O = \pm 2V$ | 10   | 200  |     | kΩ    |

| Соит                      | Output Capacitance <sup>1</sup>                | Disabled                 |      | 0.5  | 2   | pF    |

| IOUT                      | Output Current                                 |                          | 35   |      |     | mA    |

| Vout                      | Output Voltage Swing                           | No Load                  | ±2.5 | ±3.0 |     | V     |

|                           |                                                | RL = 150Ω                | ±2.5 | ±3.0 |     | V     |

| AVOL                      | Open-loop Gain                                 |                          | 58   | 68   |     | dB    |

| Venh                      | Enable High Voltage                            |                          | 2.4  |      |     | V     |

| Venl                      | Enable Low Voltage                             |                          |      |      | 0.8 | V     |

| len                       | Enable Input Current                           |                          |      | 3    | 10  | μΑ    |

| toff                      | Disable Time <sup>1</sup>                      |                          |      | 200  |     | ns    |

| ton                       | Enable Time <sup>1</sup>                       | Settling to 1%           |      | 160  |     | ns    |

| lso                       | Off Isolation (Input to Output) <sup>1</sup>   | @ 5 MHz                  |      | 60   |     | dB    |

Note:

1. Guaranteed by design.

### **AC Characteristics**

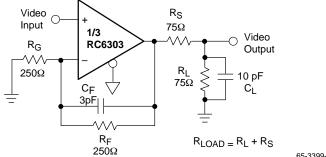

$V_{CC} = 5V, V_{EE} = -5V, A_V = 2, T_A = 0 \text{ to } 70^{\circ}C, R_{LOAD} = 150\Omega, R_G = R_F = 250\Omega, C_L = 10 \text{ pF}, C_F = 3 \text{ pF unless}$ otherwise specified. Closed Loop. See Typical Test Circuit.

| Parameter       |                                                 | Conditions              | Min | Тур  | Max | Units  |

|-----------------|-------------------------------------------------|-------------------------|-----|------|-----|--------|

| Frequer         | ncy Response                                    |                         |     | ļ    |     |        |

| BW              | -3 dB Bandwidth $(A \lor = 2)^1$                | VOUT = 0.4 Vpp          |     | 90   |     | MHz    |

|                 |                                                 | Vout = 0.8 Vpp          | 70  | 85   |     | MHz    |

| Flat            | ±0.1 dB Bandwidth <sup>1</sup>                  |                         | 15  | 20   |     | MHz    |

| Peak            | Maximum Small Signal AC<br>Peaking <sup>1</sup> |                         |     | 0.3  |     | dB     |

| XTALK           | Crosstalk Isolation <sup>1</sup>                | @ 5 MHz                 |     | 60   |     | dB     |

| Time Do         | main Response                                   |                         |     |      |     |        |

| tr1, tf1        | Rise and Fall Time 10% to 90% <sup>1</sup>      | 2V Output Step          |     | 6    | 8   | ns     |

| ts              | Settling Time to 0.1 % <sup>1</sup>             | 2V Output Step          |     | 35   |     | ns     |

| OS              | Overshoot <sup>1</sup>                          | 2V Output Step          |     | 13   |     | %      |

| US              | Undershoot <sup>1</sup>                         | 2V Output Step          |     | 4    |     | %      |

| SR              | Slew Rate <sup>1</sup>                          | $V_{OUT} = \pm 2.0 V$   | 200 | 300  |     | V/µs   |

| Distorti        | on                                              |                         |     |      |     |        |

| HD <sub>2</sub> | 2nd Harmonic Dist. @ 20 MHz <sup>1</sup>        | VOUT = 0.8 Vpp          |     | -50  |     | dB     |

| HD3             | 3nd Harmonic Dist. @ 20 MHz <sup>1</sup>        | VOUT = 0.8 Vpp          |     | -50  |     | dB     |

| Equival         | ent Input Noise                                 |                         |     |      |     |        |

| NF              | Noise Floor > 100 KHz <sup>1</sup>              |                         |     | -140 |     | dBm    |

| SND             | Spectral Noise Density <sup>1</sup>             | 100 kHz to 200 MHz      |     | 10   |     | nV/√Hz |

| Video P         | erformance                                      |                         | ·   |      |     |        |

| DG              | Diff. Gain (p-p), NTSC & PAL <sup>1</sup>       | RL = 150Ω, VOUT = ±1.5V |     | 0.06 |     | %      |

| DP              | Diff. Phase (p-p), NTSC & PAL <sup>1</sup>      | RL = 150Ω, VOUT = ±1.5V |     | 0.06 |     | Deg.   |

#### Note:

1. Guaranteed by design.

### **Test Circuit**

65-3399-02

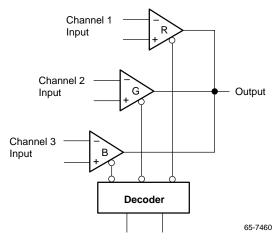

Each of the three sections of the RC6303 is provided with an Enable input, thus the part is useful for selecting and multiplexing. A three-channel video multiplexer can be built with just one RC6303 and a decoder, as shown in Figure 1.

Note that RC6303 enable time is shorter than its disable time, hence a make-before-break action is provided, minimizing switching transients on the signal output.

An RGB switch is shown in Figure 2.

#### **Capacitive Load**

The RC6303 can drive a capacitive load from 10 to over 100 pF. In back terminated video applications, bandwidth will only be limited by the RC time constants of the external output components. A minimum 10 pF capacitive load is required. When driving a 75 $\Omega$  cable, place the 75 $\Omega$  source termination resistor as close to the amplifier output as possible.

#### Enable/Disable

The enable pins (10, 12, 14), when pulled to a TTL or CMOS logic low or when tied to ground, activate each amplifier individually. When pulled to a TTL or CMOS logic high, the amplifier is tri-stated and presents a high impedance at its output. When disabled the amplifier's power consumption drops, and the non-inverting input signal is isolated from its respective output.

#### **DC Accuracy**

Since the RC6303 is a voltage-feedback amplifier, the inverting and non-inverting inputs have similar impedances and bias currents. To minimize offset voltage, match the source resistances seen by inverting and non-inverting inputs.

#### **Feedback Components**

Because the RC6303 is a voltage-feedback amplifier, it facilitates using reactive (capacitive and inductive) feedback components for implementing filters, integrators, sample/ hold circuits, etc. The feedback network and the parasitic capacitance at the inverting (summing junction) input create a pole and affect the transfer function of the circuit. For stable operation, minimize the parasitic capacitance and equivalent resistance of the components used in the feedback circuit.

#### **Circuit Board**

High-frequency applications require good grounding, power supply decoupling, low parasitic capacitance and inductance, and good isolation between the inputs to minimize their crosstalk. Avoid coupling from output to input to prevent positive feedback.

Figure 2.

#### Notes:

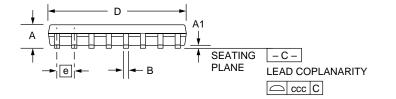

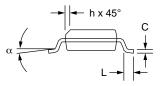

### Mechanical DImensions – 16-Lead SOIC Package

| Symbol | Inches |      | Millim   | Notes |       |

|--------|--------|------|----------|-------|-------|

| Symbol | Min.   | Max. | Min.     | Max.  | Notes |

| А      | .053   | .069 | 1.35     | 1.75  |       |

| A1     | .004   | .010 | 0.10     | 0.25  |       |

| В      | .013   | .020 | 0.33     | 0.51  |       |

| С      | .008   | .010 | 0.19     | 0.25  | 5     |

| D      | .386   | .394 | 9.80     | 10.00 | 2     |

| E      | .150   | .158 | 3.81     | 4.00  | 2     |

| е      | .050   | BSC  | 1.27 BSC |       |       |

| Н      | .228   | .244 | 5.80     | 6.20  |       |

| h      | .010   | .020 | 0.25     | 0.50  |       |

| L      | .016   | .050 | 0.40     | 1.27  | 3     |

| Ν      | 16     |      | 1        | 6     | 6     |

| α      | 0°     | 8°   | 0°       | 8°    |       |

| CCC    | _      | .004 | _        | 0.10  |       |

#### Notes:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 2. "D" and "E" do not include mold flash. Mold flash or protrusions shall not exceed .010 inch (0.25mm).

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. Terminal numbers are shown for reference only.

- 5. "C" dimension does not include solder finish thickness.

- 6. Symbol "N" is the maximum number of terminals.

#### **Ordering Information**

| Product Number | Temperature Range | Screening  | Package            | Package Marking |

|----------------|-------------------|------------|--------------------|-----------------|

| RC6303M        | 0° to 70°C        | Commercial | 16 Pin Narrow SOIC | RC6303M         |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- www.fairchildsemi.com

2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.