# $\begin{array}{r} \text{CMOS 40 MHz Monolithic} \\ \text{256} \times \text{24 Color Palette RAM-DAC} \end{array}$

**ADV453**

### 1.1 Scope.

This specification covers the detail requirements for Class B microcircuits in accordance with 1.2.1 of MIL-STD-883, provisions for the use of MIL-STD-883 in conjunction with complaint non-JAN devices. The device is a 40 MHz Monolithic 256  $\times$  24 Color Palette RAM-DAC.

#### 1.2 Part Number.

The complete part number per Table 1 of this specification is as follows:

#### Device Part Number

| -1 | ADV453TQ/883B |

|----|---------------|

| -2 | ADV453TE/883B |

### 1.2.3 Case Outline.

See Appendix 1 of General Specification ADI-M-1000: package outline:

| (X) | Package | Description                  | Lead Finish    |

|-----|---------|------------------------------|----------------|

| Q   | Q-40    | 40-Lead Dual-In-Line Package | Hot Solder DIP |

| Ε   | E-44A   | 44-Lead LCC                  | Hot Solder DIP |

### 1.3 Absolute Maximum Ratings.

| Supply Voltage $(V_{AA})$                                          |

|--------------------------------------------------------------------|

| Digital Input Voltage ( $V_{IN}$ ) to AGND                         |

| Analog Output Short Circuit Duration to Any Power Supply or Common |

| Power Dissipation                                                  |

| Storage Temperature                                                |

| L and Temperature (Soldering 10 sec) +300°C                        |

| Lunction Temperature (Soluting 10 000) + 175°C                     |

| Lead Temperature (Soldering 10 sec)                                |

### 1.5 Thermal Characteristics.

| Thermal Resistance $\theta_{IC} =$ | See MIL-M-38510 Appendix C |

|------------------------------------|----------------------------|

|                                    | 120°C/W for Q              |

| $\theta_{JA} =$                    | 50°C/W for E               |

DIGITAL-TO-ANALOG CONVERTERS 8-197

# ADV453-SPECIFICATIONS

Table 1.

| Test                                                            | Symbol            | L<br>Min | imit<br>Max | Group A<br>Subgroups | Conditions <sup>1</sup><br>(-55°C $\leq T_A \leq +125°C$<br>unless otherwise noted)                | Units        |

|-----------------------------------------------------------------|-------------------|----------|-------------|----------------------|----------------------------------------------------------------------------------------------------|--------------|

| Resolution (Each DAC)<br>Relative Accuracy (Each DAC)           |                   | 8.0      | 8.0         | 4                    |                                                                                                    | Bits         |

| Integral Nonlinearity                                           | IL                |          | ±2          | 1, 2, 3              |                                                                                                    | LSB          |

| Differential Nonlinearity                                       | DL                |          | ±l          | 1, 2, 3              | Conversion Rate is 1 MHz                                                                           | LSB          |

| Gray Scale Error                                                |                   |          | ±5          | 1, 2, 3              | White Level Relative to Blank                                                                      | % Gray Scale |

| Digital Input High Voltage                                      | VIH               | 2.4      |             | 7,8                  |                                                                                                    | v            |

| Digital Input Low Voltage                                       | V <sub>IL</sub>   |          | 0.8         | 7,8                  |                                                                                                    | v            |

| Digital Input Current                                           | I <sub>IN</sub>   | 1        | 10          | 1, 2, 3              | $V_{IN} = 0 V \text{ or } V_{AA}$                                                                  | μΑ           |

| Digital Input Capacitance <sup>2</sup>                          | C <sub>IN</sub>   | 1        | 10          | 4                    |                                                                                                    | pF           |

| Digital Output High Voltage                                     | V <sub>OH</sub>   | 2.4      |             | 1, 2, 3              | $I_{SOURCE} = 400 \ \mu A$                                                                         | v            |

| Digital Output Low Voltage                                      | V <sub>OL</sub>   |          | 0.4         | 1, 2, 3              | $I_{SINK} = 3.2 \text{ mA}$                                                                        | v            |

| Floating State Output Current                                   | I <sub>oz</sub>   |          | 10          | 1, 2, 3              | $V_{IN} = 0 V \text{ or } V_{AA}$                                                                  | μΑ           |

| Floating State Output Capacitance <sup>2</sup>                  | CD <sub>OUT</sub> |          | 20          | 4                    |                                                                                                    | pF           |

| Gray Scale Current Range                                        |                   | 15       | 22          | 1, 2, 3              |                                                                                                    | mA           |

| Output Current<br>White Level Relative to Blank                 |                   | 17.69    | 20.40       | 1, 2, 3              |                                                                                                    | mA           |

| White Level Relative to Black                                   |                   | 16.74    | 18.50       |                      | -                                                                                                  |              |

| Black Level Relative to Blank                                   | +                 | 0.95     | 1.90        |                      |                                                                                                    |              |

| Blank Level on IOR, IOB                                         |                   | 0        | 50          | 1, 2, 3              |                                                                                                    | μA           |

| Blank Level on IOG                                              |                   | 6.29     | 8.96        |                      |                                                                                                    | mA           |

| Sync Level on IOG                                               | <u> </u>          | 0        | 50          |                      |                                                                                                    | μΑ           |

| DAC to DAC Matching                                             |                   |          | 6           | 1, 2, 3              | White Level Relative to Blank                                                                      | %            |

| Output Compliance <sup>3</sup>                                  | V <sub>oc</sub>   | -1.0     | 1.4         | 1, 2, 3              |                                                                                                    | v            |

| Output Capacitance <sup>2</sup>                                 | CA <sub>OUT</sub> |          | 40          | 4                    | $I_{OUT} = 0 \text{ mA}$                                                                           | pF           |

| Voltage Reference Range <sup>3</sup>                            |                   | 1.14     | 1.26        | 1, 2, 3              |                                                                                                    | V            |

| Power Supply Current                                            | I <sub>AA</sub>   |          | 300         | 1, 2, 3              |                                                                                                    | mA           |

| Power Supply Rejection Ratio<br>(White Level Relative to Black) | PSRR              |          | 30          | 1, 2, 3              | $V_{AA} = 5.0 V$<br>Delta $V_{AA} = +5\%$ or $-5\%$<br>(0.5 V 1 kHz Sinewave Applied to $V_{AA}$ ) | dB           |

| CS C0, C1 Setup Time                                            | t <sub>1</sub>    | 35       |             | 9, 10, 11            |                                                                                                    | ns           |

| CS C0, C1 Hold Time                                             | t <sub>2</sub>    | 35       |             | 9, 10, 11            |                                                                                                    | ns           |

| RD, WR High Time                                                | t <sub>3</sub>    | 25       |             | 9, 10, 11            |                                                                                                    | ns.          |

| RD Assert to Data Bus Driven                                    | t <sub>4</sub>    | 2        |             | 9, 10, 11            |                                                                                                    | ns           |

| RD Assert to Data Valid                                         | t5                |          | 100         | 9, 10, 11            |                                                                                                    | ns           |

| RD Negated to Data Bus Three Stated                             | t <sub>6</sub>    |          | 20          | 9, 10, 11            |                                                                                                    | ns           |

| RD, WR Low Time                                                 | t <sub>7</sub>    | 50       |             | 9, 10, 11            |                                                                                                    | ns           |

8-198 DIGITAL-TO-ANALOG CONVERTERS

|                               |                 |           |            |                      |                                                                                     | ADV453 |  |

|-------------------------------|-----------------|-----------|------------|----------------------|-------------------------------------------------------------------------------------|--------|--|

| Test                          | Symbol          | Li<br>Min | mit<br>Max | Group A<br>Subgroups | Conditions <sup>1</sup><br>(-55°C $\leq T_A \leq +125°C$<br>unless otherwise noted) | Units  |  |

| Write Data Setup Time         | t <sub>8</sub>  | 35        |            | 9, 10, 11            |                                                                                     | ns     |  |

| Write Data Hold Time          | t9              | 10        |            | 9, 10, 11            |                                                                                     | ns     |  |

| Pixel and Control Setup Time  | t <sub>10</sub> | 7         |            | 9, 10, 11            |                                                                                     | ns     |  |

| Pixel and Control Hold Time   | t <sub>11</sub> | 3         |            | 9, 10, 11            |                                                                                     | ns     |  |

| Clock Cycle Time <sup>3</sup> | t <sub>12</sub> | 25        |            | 9, 10, 11            |                                                                                     | ns     |  |

| Clock Pulse Width High Time   | t <sub>13</sub> | 7         |            | 9, 10, 11            |                                                                                     | ns     |  |

| Clock Pulse Width Low Time    | t <sub>14</sub> | 7         |            | 9, 10, 11            |                                                                                     | ns     |  |

| Analog Output Delay           | t <sub>15</sub> |           | 30         | 9, 10, 11            | CLK = 4 MHz                                                                         | ns     |  |

| Analog Output Rise/Fall Time  | t <sub>16</sub> |           | 8          | 9, 10, 11            | CLK = 4 MHz                                                                         | ns     |  |

| Pipeline Delay <sup>3</sup>   | t <sub>PD</sub> |           | 2×t12      | 9, 10, 11            |                                                                                     | ns     |  |

| Analog Output Skew            | t <sub>SK</sub> |           | 2          | 9, 10, 11            | CLK = 4 MHz                                                                         | ns     |  |

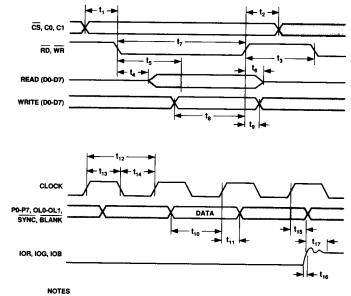

NOTES  $V_{AA} = +4.75$  V to +5.25 V,  $V_{REF} = 1.235$  V,  $R_{SET} = 280 \Omega$ ,  $I_{SYNC}$  connected to IOG, unless otherwise specified. <sup>2</sup>Tested on initial release and after any redesign which may affect this parameter. <sup>3</sup>These tests are done on a pass/fail basis only. Minimum and/or maximum conditions (as appropriate) are used as input conditions. <sup>4</sup>Digital input values are 0 to 3 V, with input rise/fall time, < 3 ns measured between the 10% and 90% points. Timing reference points are at 50% for inputs an outputs. See Figure 1.

REV. B

# **ADV453**

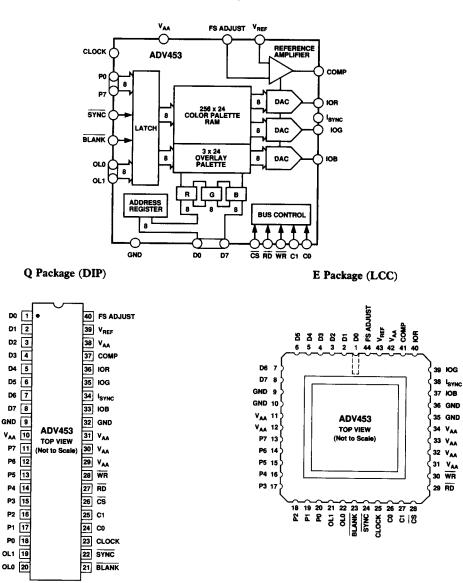

### 3.2.1 Functional Block Diagram and Terminal Assignments.

8-200 DIGITAL-TO-ANALOG CONVERTERS

REV. B

| Table 2. Electrical Test Requirements                         |                                        |  |  |  |  |

|---------------------------------------------------------------|----------------------------------------|--|--|--|--|

| MIL-STD-883 Test Requirements                                 | Subgroups<br>(Per Method 5005 Table 1) |  |  |  |  |

| Interim Electrical Parameters<br>(Method 5004)                | 1, 7, 9                                |  |  |  |  |

| Final Electrical Test Parameters<br>(Method 5004)             | 1*, 2, 3, 7, 8, 9, 10, 11              |  |  |  |  |

| Group A Test Requirements<br>(Method 5005)                    | 1, 2, 3, 7, 8A, 8B, 9, 10, 11          |  |  |  |  |

| Group C and D Endpoint Electrical<br>Parameters (Method 5005) | 1, 7, 9                                |  |  |  |  |

Table 2. Electrical Test Requirements

\*PDA applies to subgroup 1.

## 4.3.2 Group C and D Inspections

- a. Endpoint electrical parameters shall be as specified in Table 2 herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883. Test Condition A, B, C or D using the circuit in E Package Drawing.

$T_A = 125^{\circ}$ C, Min Test Duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

### 5. Packing

### 5.1 Packaging Requirements

The requirements for packaging shall be in accordance with MIL-M-38510.

DIGITAL-TO-ANALOG CONVERTERS 8-201

REV. B

# **ADV453**

### Table 3.

| Description    | IOG<br>(mA)  | IOR, IOB<br>(mA) | SYNC | BLANK | DAC<br>Input Data |

|----------------|--------------|------------------|------|-------|-------------------|

| White Level    | 26.67        | 19.05            | 1    | 1     | FFH               |

| Video          | Video + 9.05 | Video + 1.44     | 1    | 1     | Data              |

| Video to Blank | Video + 1.44 | Video + 1.44     | 0    | 1     | Data              |

| Black Level    | 9.05         | 1.44             | 1    | 1     | 00H               |

| Black to Blank | 1.44         | 1.44             | 0    | 1     | 00H               |

| Blank Level    | 7.62         | 0                | 1    | 0     | XXH               |

| SYNC Level     | 0            | 0                | 0    | 0     | ХХН               |

Notes 1. Typical with full scale IOG = 26.67 mA. 2.  $V_{REF}$  = +1.235 V,  $R_{SET}$  = 280  $\Omega$ .  $I_{SYNC}$  connected to IOG.

NOTES 1. OUTPUT DELAY ( $t_{15}$ ) MEASURED FROM THE 50% POINT OF THE RISING EDGE OF CLOCK TO THE 50% POINT OF FULL SCALE TRANSITION. 2. SETTLING TIME ( $t_{17}$ ) MEASURED FROM THE 50% POINT OF FULL SCALE TRANSITION TO THE OUTPUT REMAINING WITHIN ±11.58.

. OUTPUT INSUFALL TIME (1) MEASURED BETWEEN THE 10% AND 90% POINTS OF FULL SCALE TRANSITION.

Figure 1. Timing Diagrams

8-202 DIGITAL-TO-ANALOG CONVERTERS