# ANALOG DEVICES

# CMOS 80MHz Monolithic $256 \times 24(18)$ Color Palette RAM-DACs

# ADV478/ADV471

#### FEATURES

Personal System/2\* Compatible 80MHz Pipelined Operation Triple 8-Bit (6-Bit) D/A Converters 256 × 24(18) Color Palette RAM 15 × 24(18) Overlay Registers RS-343A/RS-170 Compatible Outputs Sync on All Three Channels Programmable Pedestal (0 or 7.5 IRE) External Voltage or Current Reference Standard MPU Interface + 5V CMOS Monolithic Construction 44-Pin PLCC Package Power Dissipation: 800mW

#### APPLICATIONS High Resolution Color Graphics CAE/CAD/CAM Applications Image Processing

Instrumentation Desktop Publishing

AVAILABLE CLOCK RATES 80MHz 66MHz 50MHz 35MHz

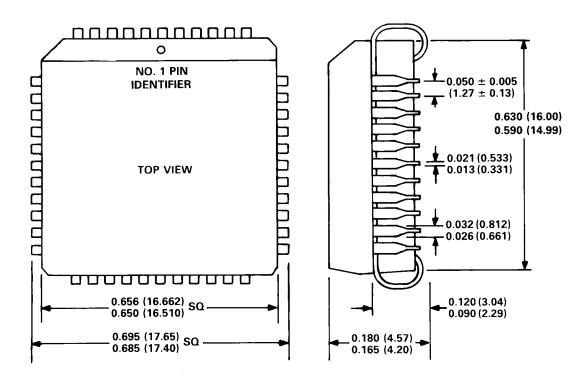

#### FUNCTIONAL BLOCK DIAGRAM

NOTES 1. NUMBERS IN PARENTHESIS INDICATE PIN NAMES FOR THE ADV471. 2. NC= NO CONNECT

#### **GENERAL DESCRIPTION**

The ADV478 (ADV®) and ADV471 are pin compatible and software compatible RAM-DACs designed specifically for Personal System/2 compatible color graphics.

The ADV478 has a  $256 \times 24$  color lookup table with triple 8-bit video D/A converters. It may be configured for either 6 bits or 8 bits per color operation. The ADV471 has a  $256 \times 18$  color lookup table with triple 6-bit video D/A converters.

Options on both parts include a programmable pedestal (0 or 7.5 IRE) and use of an external voltage or current reference.

Fifteen overlay registers provide for overlaying cursors, grids, menus, EGA emulation, etc. Also supported is a pixel read mask register and sync generation on all three channels.

The ADV478 and ADV471 generate RS-343A compatible video signals into a doubly terminated 75 $\Omega$  load, and RS-170 compatible video signals into a singly terminated 75 $\Omega$  load, without requiring external buffering. Differential and integral linearity errors are guaranteed to be a maximum of  $\pm$  1LSB for the ADV478 and  $\pm$  1/4LSB for the ADV471 over the full temperature range.

ADV is a registered trademark of Analog Devices, Inc. \*Personal System/2 is a trademark of International Business Machines Corp.

#### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:

617/329-4700

Fax:

617/326-8703

Telex:

924491

Cable:

ANALOG NORWOODMASS

#

| Parameter                                                                  | All Versions         | Units            | Test Conditions/Comments                       |

|----------------------------------------------------------------------------|----------------------|------------------|------------------------------------------------|

| STATIC PERFORMANCE                                                         |                      |                  | -                                              |

| Resolution (Each DAC) <sup>3</sup>                                         | 8(6)                 | Bits             |                                                |

| Accuracy (Each DAC) <sup>3</sup>                                           |                      |                  |                                                |

| Integral Nonlinearity                                                      | $\pm 1(1/4)$         | LSB max          |                                                |

| Differential Nonlinearity                                                  | $\pm 1(1/4)$         | LSB max          | Guaranteed Monotonic                           |

| Gray Scale Error                                                           | ± 5                  | % Gray Scale max |                                                |

| Coding                                                                     | Binary               |                  |                                                |

| DIGITAL INPUTS                                                             |                      |                  |                                                |

| Input High Voltage, V <sub>INH</sub>                                       | 2                    | Vmin             |                                                |

| Input Low Voltage, VINL                                                    | 0.8                  | V max            |                                                |

| Input Current, I <sub>IN</sub>                                             | ±1                   | μA max           | $V_{IN} = 0.4 V \text{ or } 2.4 V$             |

| Input Capacitance, C <sub>IN</sub>                                         | 7                    | pFmax            |                                                |

| DIGITALOUTPUTS                                                             |                      |                  |                                                |

| Output High Voltage, V <sub>OH</sub>                                       | 2.4                  | Vmin             | $I_{SOURCE} = 400 \mu A$                       |

| Output Low Voltage, VOL                                                    | 0.4                  | V max            | $I_{SINK} = 3.2 \text{mA}$                     |

| Floating-State Leakage Current                                             | 50                   | μA max           |                                                |

| Floating-State Output Capacitance                                          | 7                    | pFmax            |                                                |

| ANALOGOUTPUTS                                                              |                      |                  |                                                |

| Gray Scale Current Range                                                   | 20                   | mA max           |                                                |

| Output Current                                                             |                      |                  |                                                |

| White Level Relative to Blank                                              | 17.69                | mA min           | Typically 19.05mA                              |

|                                                                            | 20.40                | mA max           |                                                |

| White Level Relative to Black                                              | 16.74                | mA min           | Typically 17.62mA                              |

|                                                                            | 18.50                | mA max           |                                                |

| Black Level Relative to Blank                                              | 0.95                 | mA min           | Typically 1.44mA                               |

| $(SETUP = V_{AA})$                                                         | 1.90                 | mA max           |                                                |

| Black Level Relative to Blank                                              | 0                    | μA min           | Typically 5µA                                  |

| (SETUP = GND)                                                              | 50                   | μA max           |                                                |

| Blank Level                                                                | 6.29                 | mA min           | Typically 7.62mA                               |

|                                                                            | 8.96                 | mA max           |                                                |

| Sync Level                                                                 | 0                    | $\mu A \min$     | Typically 5µA                                  |

| T OD 0: 3                                                                  | 50                   | μA max           |                                                |

| LSB Size <sup>3</sup>                                                      | <b>69.</b> 1(279.68) | μA typ           | $8/\overline{6} = \text{Logical 1 for ADV478}$ |

| DAC to DAC Matching                                                        | 5                    | % max            | Typically 2%                                   |

| Output Compliance, V <sub>OC</sub>                                         | -1                   | Vmin             |                                                |

|                                                                            | +1.5                 | Vmax             |                                                |

| Output Impedance, R <sub>OUT</sub><br>Output Capacitance, C <sub>OUT</sub> | 10                   | kΩ typ           |                                                |

|                                                                            | 30                   | pFmax            | $I_{OUT} = 0mA$                                |

| VOLTAGE REFERENCE                                                          |                      |                  |                                                |

| Voltage Reference Range, V <sub>REF</sub>                                  | 1.14/1.26            | V min/V max      |                                                |

| Input Current, I <sub>VREF</sub>                                           | 10                   | μA typ           | Tested in Voltage Reference                    |

|                                                                            |                      |                  | Configuration with $V_{REF} = 1.235V$          |

| POWER SUPPLY                                                               |                      |                  |                                                |

| Supply Voltage, V <sub>AA</sub>                                            | 4.75/5.25            | V min/V max      | 80MHz and 66MHz Parts                          |

|                                                                            | 4.50/5.50            | V min/V max      | 50MHz and 35MHz Parts                          |

| Supply Current, I <sub>AA</sub>                                            | 220                  | mA max           | Typically 180mA                                |

| Power Supply Rejection Ratio                                               | 0.5                  | %/% max          | $f = 1 kHz, COMP = 0.1 \mu F$                  |

| Power Dissipation                                                          | 1100                 | mW max           | Typically 900mW, $V_{AA} = 5V$                 |

| DYNAMIC PERFORMANCE                                                        |                      |                  |                                                |

| Clock and Data Feedthrough <sup>4,5</sup>                                  | - 30                 | dB typ           |                                                |

| Glitch Impulse <sup>4,5</sup>                                              | 75                   | pV secs typ      |                                                |

| DAC to DAC Crosstalk <sup>6</sup>                                          | -23                  | dB typ           |                                                |

#### NOTES

$^{1} \pm 5\%$  for 80MHz and 66MHz parts;  $\pm 10\%$  for 50MHz and 35MHz parts.

<sup>2</sup>Temperature Range ( $T_{min}$  to  $T_{max}$ ); 0 to +70°C.

<sup>3</sup>Numbers in parentheses indicate ADV471 parameter value.

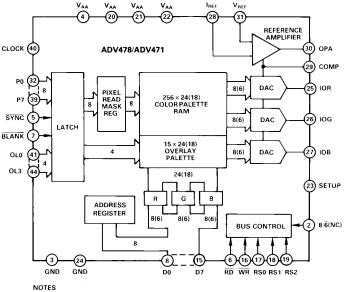

<sup>4</sup>Clock and data feedthrough is a function of the amount of overshoot and undershoot on the digital inputs. For this test, the digital inputs have a  $1k\Omega$  resistor to ground and are driven by 74HC logic. Glitch impulse includes clock and data feedthrough, -3dB test bandwidth  $= 2 \times \text{clock}$  rate. <sup>5</sup>TTL input values are 0 to 3 volts, with input rise/fall times  $\leq 3ns$ , measured between the 10% and 90% points. Timing reference points at 50% for inputs and outputs. Analog output load  $\leq 10pF$ , D0 - D7 output load  $\leq 50pF$ . See timing notes in Figure 2.

<sup>6</sup>DAC to DAC crosstalk is measured by holding one DAC high while the other two are making low to high and high to low transitions.

Specifications subject to change without notice.

| Parameter        | KP80 Version      | KP66 Version      | KP50 Version      | KP35 Version      | Units  | Conditions/Comments                                          |

|------------------|-------------------|-------------------|-------------------|-------------------|--------|--------------------------------------------------------------|

| f <sub>max</sub> | 80                | 66                | 50                | 35                | MHz    | Clock Rate                                                   |

| t <sub>1</sub>   | 10                | 10                | 10                | 10                | ns min | RS0 – RS2 Setup Time                                         |

| t <sub>2</sub>   | 10                | 10                | 10                | 10                | ns min | RS0 – RS2 Hold Time                                          |

| t <sub>3</sub>   | 5                 | 5                 | 5                 | 5                 | ns min | RD Asserted to Data Bus Driven                               |

| t <sub>4</sub>   | 40                | 40                | 40                | 40                | ns max | RD Asserted to Data Valid                                    |

| t <sub>5</sub>   | 20                | 20                | 20                | 20                | ns max | RD Negated to Data Bus 3-Stated                              |

| t <sub>6</sub>   | 10                | 10                | 10                | 10                | ns min | Write Data Setup Time                                        |

| <sup>1</sup> 7   | 10                | 10                | 10                | 10                | ns min | Write Data Hold Time                                         |

| 8                | 50                | 50                | 50                | 50                | ns min | $\overline{\text{RD}}, \overline{\text{WR}}$ Pulse Width Low |

| l9               | $6 \times t_{12}$ | $6 \times t_{12}$ | $6 \times t_{12}$ | $6 \times t_{12}$ | ns min | RD, WR Pulse Width High                                      |

| 10               | 3                 | 3                 | 3                 | 3                 | ns min | Pixel and Control Setup Time                                 |

| 11               | 3                 | 3                 | 3                 | 3                 | ns min | Pixel and Control Hold Time                                  |

| 12               | 12.5              | 15.3              | 20                | 28                | ns min | Clock Cycle Time                                             |

| 13               | 4                 | 5                 | 6                 | 7                 | ns min | Clock Pulse Width High Time                                  |

| <sup>1</sup> 14  | 4                 | 5                 | 6                 | 9                 | ns min | Clock Pulse Width Low Time                                   |

| L <sub>15</sub>  | 30                | 30                | 30                | 30                | ns max | Analog Output Delay                                          |

| 16               | 3                 | 3                 | 3                 | 3                 | nstyp  | Analog Output Rise/Fall Time                                 |

| 4                | 13                | 15.3              | 20                | 28                | nstyp  | Analog Output Settling Time                                  |

| 18               | 2                 | 2                 | 2                 | 2                 | nsmax  | Analog Output Skew                                           |

| t <sub>PD</sub>  | $4 \times t_{12}$ | $4 \times t_{12}$ | $4 \times t_{12}$ | $4 \times t_{12}$ | ns min | Pipeline Delay                                               |

## **TIMING CHARACTERISTICS**<sup>1</sup> ( $V_{AA}^2 = +5V$ , SETUP = $8/\overline{6} = V_{AA}$ , $V_{REF} = 1.235V$ . $R_{SET} = 147\Omega$ . All Specifications $T_{min}$ to $T_{max}^3$ .)

NOTES

<sup>1</sup>TTL input values are 0 to 3 volts, with input rise/fall times ≤3ns, measured between the 10% and 90% points. Timing reference

points at 50% for inputs and outputs. Analog output load  $\leq$ 10pF, 37.5 $\Omega$ . D0 – D7 output load  $\leq$ 50pF. See timing notes in Figure 2.

$\pm$  5% for 80MHz and 66MHz parts;  $\pm$  5% for 50MHz and 35MHz parts.

<sup>3</sup>Temperature Range ( $T_{min}$  to  $T_{max}$ ); 0 to +70°C.

<sup>4</sup>Settling time does not include clock and data feedthrough. For this test, the digital inputs have a 1k $\Omega$  resistor to ground and are driven by 74HC logic.

Specifications subject to change without notice

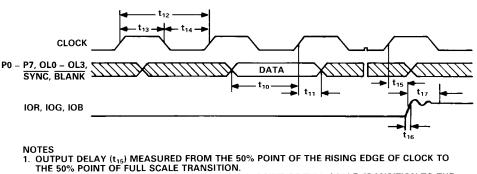

#### TIMING DIAGRAMS

- 2. SETTLING TIME (t17) MEASURED FROM THE 50% POINT OF FULL SCALE TRANSITION TO THE

- OUTPUT REMAINING WITHIN  $\pm$  1LSB (ADV478) OR  $\pm$  1/4LSB (ADV471). OUTPUT RISE/FALL TIME (t<sub>16</sub>) MEASURED BETWEEN THE 10% AND 90% POINTS OF FULL SCALE 3.

- TRANSITION.

Figure 2. Video Input/Output Timing

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                       | Symbol           | Min  | Тур   | Max  | Units |

|---------------------------------|------------------|------|-------|------|-------|

| Power Supply                    | V <sub>AA</sub>  |      |       |      |       |

| 80MHz, 66MHz Parts              |                  | 4.75 | 5.00  | 5.25 | Volts |

| 50, 35MHz Parts                 |                  | 4.5  | 5.00  | 5.5  | Volts |

| Ambient Operating Temperature   | T <sub>A</sub>   | 0    |       | + 70 | °C    |

| Output Load                     | R <sub>L</sub>   |      | 37.5  |      | Ω     |

| Voltage Reference Configuration | _                |      |       |      |       |

| Reference Voltage               | V <sub>REF</sub> | 1.14 | 1.235 | 1.26 | Volts |

| Current Reference Configuration |                  |      |       |      |       |

| Reference Current               | IREF             | -3   |       | - 10 | mA    |

#### CAUTION .

ESD (electrostatic discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

#### **ABSOLUTE MAXIMUM RATINGS\***

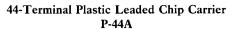

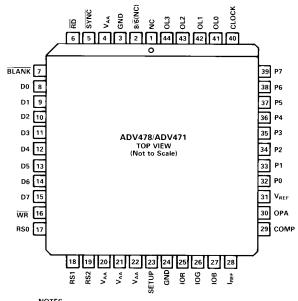

#### PLCC PIN CONFIGURATION

| $V_{AA}$ to GND $\hfill \ldots \hfill + 7V$                             |

|-------------------------------------------------------------------------|

| Voltage on Any Digital Pin GND $-0.5V$ to $V_{AA} + 0.5V$               |

| Ambient Operating Temperature $(T_A)$ $-55^{\circ}C$ to $+125^{\circ}C$ |

| Storage Temperature $(T_S)$                                             |

| Lead Temperature (Soldering, 10 secs) + 300°C                           |

| Junction Temperature $(T_J)$                                            |

| Vapor Phase Soldering (1 minute)                                        |

| IOR, IOB, IOG to $GND^1$                                                |

#### NOTES

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Analog output short circuit to any power supply or common can be of an indefinite duration.

NOTES 1. NUMBERS IN PARENTHESIS INDICATE PIN NAMES FOR THE ADV471. 2. NC=NO CONNECT

| Model      | Temperature<br>Range             | Color Palette<br>RAM | Speed | Package<br>Option* |

|------------|----------------------------------|----------------------|-------|--------------------|

| ADV471KP80 | $0^{\circ}$ C to $+70^{\circ}$ C | 256 × 18             | 80MHz | P-44A              |

| ADV471KP66 | $0^{\circ}$ C to + 70°C          | 256 	imes 18         | 66MHz | P-44A              |

| ADV471KP50 | 0°C to + 70°C                    | 256 	imes 18         | 50MHz | P-44A              |

| ADV471KP35 | 0°C to + 70°C                    | 256 × 18             | 35MHz | P-44A              |

| ADV478KP80 | 0°C to + 70°C                    | $256 \times 24$      | 80MHz | P-44A              |

| ADV478KP66 | $0^{\circ}$ C to + 70°C          | $256 \times 24$      | 66MHz | P-44A              |

| ADV478KP50 | $0^{\circ}$ C to + 70°C          | $256 \times 24$      | 50MHz | P-44A              |

| ADV478KP35 | $0^{\circ}$ C to + 70°C          | 256 × 24             | 35MHz | P-44A              |

#### **ORDERING GUIDE**

\*P = Plastic Leaded Chip Carrier (PLCC).

#### **PIN FUNCTION DESCRIPTION**

| Pin<br>Mnemonic  | Function                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BLANK            | Composite blank control input (TTL compatible). A logic zero drives the analog outputs to the blanking level as illustrated in Tables IV and V. It is latched on the rising edge of CLOCK. When BLANK is a logical zero, the pixel and overlay inputs are ignored                                                                                                                   |  |  |  |  |  |

| SETUP            | Setup control input. Used to specify either a 0 IRE (SETUP=GND) or 7.5 IRE (SETUP= $V_{AA}$ ) blanking pedestal.                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| SYNC             | Composite sync control input (TTL compatible). A logical zero on this input switches off a 40 IRE current source on the analog outputs (see Figures 3 and 4). SYNC does not override any other control or data input, as shown in Tables IV and V; therefore, it should be asserted only during the blanking interval. It is latched on the rising edge of CLOCK.                   |  |  |  |  |  |

| CLOCK            | Clock input (TTL compatible). The rising edge of CLOCK latches the P0 – P7, OL0 – OL3, $\overline{\text{SYNC}}$ , and $\overline{\text{BLANK}}$ inputs. It is typically the pixel clock rate of the video system. It is recommended that CLOCK be driven by a dedicated TTL buffer.                                                                                                 |  |  |  |  |  |

| P0 – P7          | Pixel select inputs (TTL compatible). These inputs specify, on a pixel basis, which one of the 256 entries in the color palette RAM is to be used to provide color information. They are latched on the rising edge of CLOCK. P0 is the LSB. Unused inputs should be connected to GND.                                                                                              |  |  |  |  |  |

| OL0 – OL3        | Overlay select inputs (TTL compatible). These inputs specify which palette is to be used to provide color information, as illustrated in Table III. When accessing the overlay palette, the P0 – P7 inputs are ignored. They are latched on the rising edge of CLOCK. OL0 is the LSB. Unused inputs should be connected to GND.                                                     |  |  |  |  |  |

| IOR, IOG, IOB    | Red, green, and blue current outputs. These high impedance current sources are capable of directly driving a doubly terminated 75 $\Omega$ coaxial cable (Figures 5 and 6).                                                                                                                                                                                                         |  |  |  |  |  |

| I <sub>REF</sub> | Full-scale adjust control. Note that the IRE relationships in Figures 3 and 4 are maintained, regardless of the full-scale output current.                                                                                                                                                                                                                                          |  |  |  |  |  |

|                  | When using an external voltage reference (Figure 5), a resistor ( $R_{SET}$ ) connected between this pin and GND controls the magnitude of the full-scale video signal. The relationship between $R_{SET}$ and the full-scale output current on each output is:                                                                                                                     |  |  |  |  |  |

|                  | $R_{SET} (\Omega) = K \star 1,000 \star V_{REF} (V)/I_{OUT} (mA)$                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                  | K is defined in the table below, along with corresponding $R_{SET}$ values for doubly terminated 75 $\Omega$ loads.                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                  | When using an external current reference (Figure 6), the relationship between $I_{REF}$ and the full-scale output current on each output is:                                                                                                                                                                                                                                        |  |  |  |  |  |

|                  | $I_{REF} (mA) = I_{OUT} (mA)/K$                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                  | Mode Pedestal K $R_{SET}(\Omega)$                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                  | 6-Bit         7.5 IRE         3.170         147                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                  | 8-Bit 7.5 IRE 3.195 147                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                  | 6-Bit 0 IRE 3.000 147                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                  | 8-Bit 0 IRE 3.025 147                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| СОМР             | Compensation pin. If an external voltage reference is used (Figure 5), this pin should be connected to OPA. If an external current reference is used, this pin should be connected to $I_{REF}$ . A 0.1µF ceramic capacitor must always be used to bypass this pin to $V_{AA}$ .                                                                                                    |  |  |  |  |  |

| V <sub>REF</sub> | Voltage reference input. If an external voltage reference is used (Figure 5), it must supply this input with a 1.2V (typical) reference. If an external current reference is used (Figure 6), this pin should be left floating, except for the bypass capacitor. A $0.1\mu$ F ceramic capacitor must always be used to decouple this input to $V_{AA}$ as shown in Figures 5 and 6. |  |  |  |  |  |

| OPA              | Reference amplifier output. If an external voltage reference is used (Figure 5), this pin must be connected to COMP. When using an external current reference (Figure 6), this pin should be left floating.                                                                                                                                                                         |  |  |  |  |  |

| V <sub>AA</sub>  | Analog power. All VAA pins must be connected to the Analog Power Plane.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| GND              | Analog ground. All GND pins must be connected to the Ground Plane.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| WR               | Write control input (TTL compatible). D0 – D7 data is latched on the rising edge of $\overline{WR}$ , and RS0 – RS2 are latched on the falling edge of $\overline{WR}$ during MPU write operations. See Figure 1.                                                                                                                                                                   |  |  |  |  |  |

n:\_

#### PIN FUNCTION DESCRIPTION (Continued)

| Pin<br>Mnemonic | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD              | Read control input (TTL compatible). To read data from the device, $\overline{RD}$ must be a logical zero. RS0 – RS2 are latched on the falling edge of $\overline{RD}$ during MPU read operations.                                                                                                                                                                                                                                                                                                                                               |

| RS0, RS1, RS2   | Register select inputs (TTL compatible). RS0 – RS2 specify the type of read or write operation being performed as illustrated in Tables I and II.                                                                                                                                                                                                                                                                                                                                                                                                 |

| D0 – D7         | Data bus (TTL compatible). Data is transferred into and out of the device over this 8-bit bidirectional data bus. D0 is the least significant bit.                                                                                                                                                                                                                                                                                                                                                                                                |

| 8/6             | 8-bit/6-bit select input (TTL compatible). This control input specifies whether the MPU is reading and writing<br>8-bits (logical one) or 6-bits (logical zero) of color information each cycle. For 8-bit operation, D7 is the most<br>significant data bit during color read/write cycles. For 6-bit operation, D5 is the most significant data bit<br>during color read/write cycles (D6 and D7 are ignored during color write cycles and are logical zero during<br>color read cycles). This control input is implemented only on the ADV478. |

#### TERMINOLOGY

#### **Blanking Level**

The level seperating the SYNC portion from the video portion of the waveform. Usually referred to as the front porch or back porch. At 0 IRE units, it is the level which will shut off the picture tube, resulting in the blackest possible picture.

#### Color Video (RGB)

This usually refers to the technique of combining the three primary colors of red, green and blue to produce color pictures within the usual spectrum. In RGB monitors, three DACs would be required, one for each color.

#### Composite SYNC Signal (SYNC)

The portion of the composite video signal which synchronizes the scanning process.

#### **Composite Video Signal**

The video signal with or without setup, plus the composite SYNC signal.

#### **Gray Scale**

The discrete levels of video signal between reference black and reference white levels. An 8-bit DAC contains 256 different levels while a 6-bit DAC contains 64.

#### **Raster Scan**

The most basic method of sweeping a CRT one line at a time to generate and display images.

#### **Reference Black Level**

The maximum negative polarity amplitude of the video signal.

#### **Reference White Level**

The maximum positive polarity amplitude of the video signal.

#### Setup

The difference between the reference black level and the blanking level.

#### SYNC Level

The peak level of the composite SYNC signal.

#### Video Signal

That portion of the composite video signal which varies in gray scale levels between reference white and reference black. Also referred to as the picture signal, this is the portion which may be visually observed.

#### CIRCUIT DESCRIPTION MPU Interface

As illustrated in the functional block diagram, the ADV478 and ADV471 support a standard MPU bus interface, allowing the MPU direct access to the color palette RAM and overlay color registers.

The RS0 – RS2 select inputs specify whether the MPU is accessing the address register, color palette RAM, overlay registers or read mask register, as shown in Table I. The 8-bit address register is used to address the color palette RAM and overlay registers, eliminating the requirement for external address multiplexers.

To write color data, the MPU writes to the address register (selecting RAM or overlay write mode) with the address of the color palette RAM location or overlay register to be modified. The MPU performs three successive write cycles (8 or 6 bits each of red, green and blue), using RS0 – RS2 to select either the color palette RAM or overlay registers. During the blue write cycle, the three bytes of color information are concatenated into a 24-bit word (18-bit word for the ADV471) and written to the location specified by the address register. The address register then increments to the next location which the MPU may modify by simply writing another sequence of red, green and blue data.

| RS2 | RS1 | RS0 | Addressed by MPU                      |

|-----|-----|-----|---------------------------------------|

| 0   | 0   | 0   | Address Register (RAM Write Mode)     |

| 0   | 1   | 1   | Address Register (RAM Read Mode)      |

| 0   | 0   | 1   | Color Palette RAM                     |

| 0   | 1   | 0   | Pixel Read Mask Register              |

| 1   | 0   | 0   | Address Register (Overlay Write Mode) |

| 1   | 1   | 1   | Address Register (Overlay Read Mode)  |

| 1   | 0   | 1   | Overlay Registers                     |

| 1   | 1   | 0   | Reserved                              |

Table I. Control Input Truth Table

To read color data, the MPU loads the address register (selecting RAM or overlay read mode) with the address of the color palette RAM location or overlay register to be read. The MPU performs three successive read cycles (8 or 6 bits each of red, green and blue), using RS0 – RS2 to select either the color palette RAM or overlay registers. Following the blue read cycle, the address register increments to the next location which the MPU may read by simply reading another sequence of red, green and blue data.

When accessing the color palette RAM, the address register resets to 00H following a blue read or write cycle to RAM location FFH. When accessing the overlay color registers, the address register increments following a blue read or write cycle. However, while accessing the overlay color registers, the four most significant bits of the address register (ADDR4 – 7) are ignored.

The MPU interface operates asynchronously to the pixel clock. Data transfers between the color palette RAM/overlay registers and the color registers (R, G and B in the block diagram) are synchronized by internal logic and occur in the period between MPU accesses. As only one pixel clock cycle is required to complete the transfer, the color palette RAM and overlay registers may be accessed at any time with no noticeable disturbance on the display screen.

To keep track of the red, green and blue read/write cycles, the address register has two additional bits (ADDRa, ADDRb) that count modulo three, as shown in Table II. They are reset to zero when the MPU writes to the address register and are not reset to zero when the MPU reads the address register. The MPU does not have access to these bits. The other eight bits of the address register, incremented following a blue read or write cycle (ADDR0 – 7), are accessible to the MPU and are used to address color palette RAM locations and overlay registers, as shown in Table II. ADDR0 is the LSB when the MPU is accessing the RAM or overlay registers. The MPU may read the address register at any time without modifying its contents or the existing read/write mode.

Figure 1 illustrates the MPU read/write timing.

|                           | Value     | RS2 | RS1 | RS0 | Addressed By MPU  |

|---------------------------|-----------|-----|-----|-----|-------------------|

| ADDRa,b (Counts Modulo 3) | 00        |     |     |     | Red Value         |

|                           | 01        |     |     |     | Green Value       |

|                           | 10        |     |     |     | Blue Value        |

| ADDR0 - 7 (Counts Binary) | 00H – FFH | 0   | 0   | 1   | Color Palette RAM |

|                           | XXXX 0000 | 1   | 0   | 1   | Reserved          |

|                           | XXXX 0001 | 1   | 0   | 1   | Overlay Color 1   |

|                           | XXXX 0010 | 1   | 0   | 1   | Overlay Color 2   |

|                           | •         | •   | •   | •   | •                 |

|                           | •         | •   | •   | •   | •                 |

|                           | XXXX 1111 | 1   | 0   | 1   | Overlay Color 15  |

Table II. Address Register (ADDR) Operation

#### **ADV478 Data Bus Interface**

On the ADV478, the  $8/\overline{6}$  control input is used to specify whether the MPU is reading and writing 8 bits ( $8/\overline{6}$  = logical one) or 6 bits ( $8/\overline{6}$  = logical zero) of color information each cycle.

For 8-bit operation, D0 is the LSB and D7 is the MSB of color data.

For 6-bit operation (and also when using the ADV471), color data is contained on the lower six bits of the data bus, with D0 being the LSB and D5 the MSB of color data. When writing color data, D6 and D7 are ignored. During color read cycles, D6 and D7 will be a logical zero.

#### **ADV471 Data Bus Interface**

Color data is contained on the lower six bits of the data bus, with D0 being the LSB and D5 the MSB of color data. When writing color data, D6 and D7 are ignored. During color read cycles, D6 and D7 will be a logical zero.

#### Frame Buffer Interface

The P0 – P7 and OL0 – OL3 inputs are used to address the color palette RAM and overlay registers, as shown in Table III.

| OL0 – OL3 | P0 – P7 | Addressed by Frame Buffer      |

|-----------|---------|--------------------------------|

| 0H        | 00H     | Color Palette RAM Location 00H |

| 0H        | 01H     | Color Palette RAM Location 01H |

| •         | •       | •                              |

| •         | •       | •                              |

| 0H        | FFH     | Color Palette RAM Location FFH |

| 1H        | XXH     | Overlay Color 1                |

| 2H        | ХХН     | Overlay Color 2                |

| •         | •       | •                              |

| •         | •       | •                              |

| FH        | ХХН     | Overlay Color 15               |

Table III. Pixel and Overlay Control Truth Table (Pixel ReadMask Register = FFH)

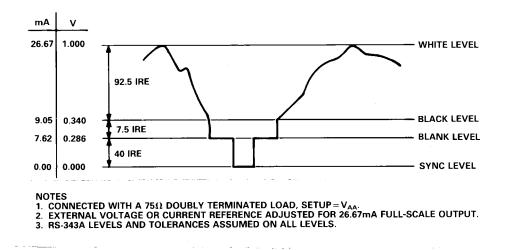

Figure 3. Composite Video Output Waveform (SETUP =  $V_{AA}$ )

| Description        | I <sub>OUT</sub> (mA) <sup>1</sup> | SYNC | BLANK | DAC<br>Input Data |

|--------------------|------------------------------------|------|-------|-------------------|

| WHITE LEVEL        | 26.67                              | 1    | 1     | FFH               |

| DATA               | data + 9.05                        | 1    | 1     | data              |

| DATA-SYNC          | data + 1.44                        | 0    | 1     | data              |

| BLACK LEVEL        | 9.05                               | 1    | 1     | 00H               |

| BLACK-SYNC         | 1.44                               | 0    | 1     | 00H               |

| <b>BLANK LEVEL</b> | 7.62                               | 1    | 0     | xxH               |

| SYNC LEVEL         | 0                                  | 0    | 0     | xxH               |

NOTES

<sup>1</sup>Typical with full-scale IOG = 26.67mA, SETUP =  $V_{AA}$ .

External voltage or current reference adjusted for 26.67mA full-scale output.

Table IV. Video Output Truth Table (SETUP =  $V_{AA}$ )

The contents of the pixel read mask register, which may be accessed by the MPU at any time, are bit-wise logically ANDed with the P0 - P7 inputs. Bit D0 of the pixel read mask register corresponds to pixel input P0. The addressed location provides 24 bits (18 bits for the ADV471) of color information to the three D/A converters.

For additional information on Pixel Mask Register, see application note "Animation Using the Pixel Read Mask Register of the ADV47X Series of Video RAM-DACs"(Publication Number E1316-15-10/89).

The  $\overline{SYNC}$  and  $\overline{BLANK}$  inputs, also latched on the rising edge

of CLOCK to maintain synchronization with the color data, add appropriately weighted currents to the analog outputs, producing the specific output levels required for video applications, as illustrated in Figures 3 and 4. Tables IV and V detail how the SYNC and BLANK inputs modify the output levels.

The SETUP input is used to specify whether a 0 IRE (SETUP = GND) or 7.5 IRE (SETUP =  $V_{AA}$ ) blanking pedestal is to be used.

The analog outputs of the ADV478 and ADV471 are capable of directly driving a 37.5 $\Omega$  load, such as a doubly terminated 75 $\Omega$ coaxial cable.

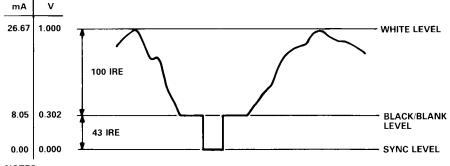

NOTES

CONNECTED WITH A 75Ω DOUBLY TERMINATED LOAD, SETUP=GND. EXTERNAL VOLTAGE OR CURRENT REFERENCE ADJUSTED FOR 26.67mA FULL-SCALE OUTPUT. 2.

3. RS-343A LEVELS AND TOLERANCES ASSUMED ON ALL LEVELS.

Figure 4. Composite Video Output Waveform (SETUP=GND)

| Description | I <sub>OUT</sub> (mA) <sup>1</sup> | SYNC | BLANK | DAC<br>Input Data |

|-------------|------------------------------------|------|-------|-------------------|

| WHITE LEVEL | 26.67                              | 1    | 1     | FFH               |

| DATA        | data + 8.05                        | 1    | 1     | data              |

| DATA-SYNC   | data                               | 0    | 1     | data              |

| BLACK LEVEL | 8.05                               | 1    | 1     | 00H               |

| BLACK-SYNC  | 0                                  | 0    | 1     | 00H               |

| BLANK LEVEL | 8.05                               | 1    | 0     | xxH               |

| SYNC LEVEL  | 0                                  | 0    | 0     | xxH               |

NOTES

<sup>1</sup>Typical with full-scale IOG = 26.67 mA, SETUP = GND

External voltage or current reference adjusted for 26.67mA full-scale output.

Table V. Video Output Truth Table (SETUP = GND)

#### PC BOARD LAYOUT CONSIDERATIONS

#### PC Board Considerations

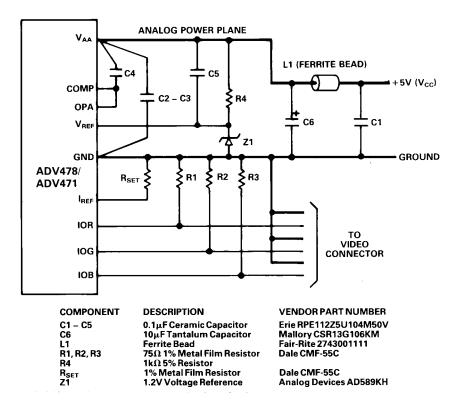

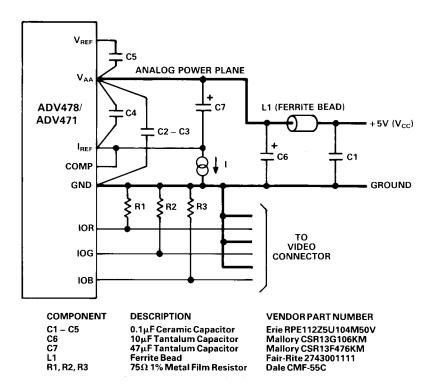

The layout should be optimized for lowest noise on the ADV478/ ADV471 power and ground lines by shielding the digital inputs and providing good decoupling. The lead length between groups of  $V_{AA}$  and GND pins should by minimized so as to minimize inductive ringing.

#### **Ground Planes**

The ground plane should encompass all ADV478/ADV471 ground pins, current/voltage reference circuitry, power supply bypass circuitry for the ADV478/ADV471, the analog output traces and all the digital signal traces leading up to the ADV478/ADV471.

#### **Power Planes**

The ADV478/ADV471 and any associated analog circuitry should have its own power plane, referred to as the analog power plane. This power plane should be connected to the regular PCB power plane ( $V_{CC}$ ) at a single point through a ferrite bead, as illustrated in Figures 5 and 6. This bead should be located within three inches of the ADV478/ADV471.

The PCB power plane should provide power to all digital logic on the PC board, and the analog power plane should provide power to all ADV478/ADV471 power pins and current/voltage reference circuitry.

Plane-to-plane noise coupling can be reduced by ensuring that portions of the regular PCB power and ground planes do not overlay portions of the analog power plane, unless they can be arranged such that the plane-to-plane noise is common mode.

#### Supply Decoupling

For optimum performance, bypass capacitors should be installed using the shortest leads possible, consistent with reliable operation, to reduce the lead inductance.

Best performance is obtained with a  $0.1\mu$ F ceramic capacitor decoupling each of the two groups of V<sub>AA</sub> pins to GND. These capacitors should be placed as close as possible to the device.

It is important to note that while the ADV478 and ADV471 contain circuitry to reject power supply noise, this rejection decreases with frequency. If a high frequency switching power supply is used, the designer should pay close attention to reducing power supply noise and consider using a three terminal voltage regulator for supplying power to the analog power plane.

Figure 5. Typical Connection Diagram and Component List (External Voltage Reference)

#### **Digital Signal Interconnect**

The digital inputs to the ADV478/ADV471 should be isolated as much as possible from the analog outputs and other analog circuitry. Also, these input signals should not overlay the analog power plane.

Due to the high clock rates involved, long clock lines to the ADV478/ADV471 should be avoided to reduce noise pickup.

Any active termination resistors for the digital inputs should be connected to the regular PCB power plane ( $V_{CC}$ ), and not the analog power plane.

#### **Analog Signal Interconnect**

The ADV478/ADV471 should be located as close as possible to the output connectors to minimize noise pickup and reflections due to impedance mismatch.

The video output signals should overlay the ground plane, and not the analog power plane, to maximize the high frequency power supply rejection.

For maximum performance, the analog outputs should each have a 75 $\Omega$  load resistor connected to GND. The connection between the current output and GND should be as close as possible to the ADV478/ADV471 to minimize reflections.

NOTE: Additional information on PC Board layout can be obtained in an application note entitled "Design and Layout of a Video Graphics System for Reduced EMI" from Analog Devices (Publication Note E1309–15–10/89).

Figure 6. Typical Connection Diagram and Component List (External Current Reference)

#### APPLICATION INFORMATION

**External Voltage vs. Current Reference**

The ADV478/ADV471 is designed to have excellent performance using either an external voltage or current reference. The voltage reference design (Figure 5) has the advantages of temperature compensation, simplicity, lower cost and provides excellent power supply rejection. The current reference design (Figure 6) requires more components to provide adequate power supply rejection and temperature compensation (two transistors, three resistors and additional capacitors).

#### **RS-170 Video Generation**

For generation of RS-170 compatible video, it is recommended that the DAC outputs be connected to a singly terminated 75 $\Omega$ load. If the ADV478/ADV471 is not driving a large capacitive load, there will be negligible difference in video quality between doubly terminated 75 $\Omega$  and singly terminated 75 $\Omega$  loads.

If driving a large capacitive load (load RC>  $1/(2\pi f_C)$ ), it is recommended that an output buffer (such as an AD848 or AD9617 with an unloaded gain>2) be used to drive a doubly terminated 75 $\Omega$  load.

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).