HIGH-VOLTAGE MIXED-SIGNAL IC

Product Specifications Revision 0.54 OCT 12, 2001

High-Voltage Mixed-Signal IC

©2000

65x102 Matrix LCD Controller-Drivers

# UC1602i

Single-Chip, Ultra-Low Power Passive Matrix LCD Controller-Driver

### INTRODUCTION

UC1602i is an advanced high-voltage mixedsignal CMOS IC, especially designed for the display needs of ultra-low power hand-held devices.

In addition to low power column and row drivers, these ICs contain all necessary circuits for high-V LCD power supply, bias voltage generation, timing generation and graphics data memory.

Advanced circuit design techniques are employed to minimize external component counts and reduce connector size while achieving extremely low power consumption.

### MAIN APPLICATIONS

- Cellular Phones or Smart Phones

- Pagers or other battery operated messaging devices

- Battery Powered Portable Instruments

### **FEATURE HIGHLIGHTS**

- Supports I<sup>2</sup>C 2-wire serial interface and 8bit parallel bus interface.

- Ultra-low power LCD controller-driver with built-in display RAM and timing generator to support compact LCD module using as few as 5 pins.

- V<sub>DD2/3</sub> voltage range: 2.4V ~ 3.3V

V<sub>DD1</sub> voltage range: 1.8V ~ 3.3V

LCD V<sub>OP</sub> range: 4.5V ~ 10.5V

- 6x, built-in self-configuring, charge pump allows the use of low V<sub>DD</sub> while produce high V<sub>LCD</sub> for driving LCD.

- On-chip charge pump pumping capacitors requires only 3 external capacitors.

- Two multiplexing rates: 1/65, 1/49.

- Four temperature compensations.

- Support both high speed parallel interfaces and compact serial interfaces.

- Flexible data addressing/mapping schemes to support wide ranges of software models and LCD layout placements.

| Symbol               |                              | Turn                    | Max.         | Unit                             |      |   |    |

|----------------------|------------------------------|-------------------------|--------------|----------------------------------|------|---|----|

| Symbol               | $V_{DD}$ : $V_{LCD}$         | Pump                    | Тур.         | wax.                             | Unit |   |    |

|                      | 2.7V : 8.5V                  | 4x                      | Blank        |                                  | 95   |   |    |

|                      | 2.7V : 8.5V                  | 4x                      | Checker      | 65x102, 12nF Panel <sup>\$</sup> | 105  |   |    |

|                      | 2.4V : 8.5V 5x Blank         |                         |              | 110                              |      |   |    |

| I <sub>DD(tot)</sub> | 2.4V : 8.5V                  | 5x                      | Checker      |                                  | 122  |   | μA |

|                      | 2.7V : 8.5V                  | V:8.5V 4x Blank/Checker |              | No load                          | 65   |   |    |

| -                    | 2.4V : 8.5V 5x Blank/Checker |                         | No load      | 70                               |      |   |    |

|                      | Sleep                        | Mode (D                 | Display Off) | N/A                              | 0.2  | 1 |    |

## **POWER CONSUMPTION**

<sup>\$</sup> LCD panel capacitance estimated when displaying checker pattern.

High-Voltage Mixed-Signal IC

©2000

#### **ORDERING INFORMATION**

| Nomenclature | Description                                                                                                                           |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| UC1602I-PP-M | PP:       Packaging         GU:       Gold bumped, face up         GD:       Gold bumped, face down         Fn:       Type n TCP film |

| Part Number | Memory   | Drivers          | Mux Rate Supported | Versions |

|-------------|----------|------------------|--------------------|----------|

| UC1602I     | 65 x 102 | 65 COM x 102 SEG | 1/65, 1/49         | G        |

#### **General Notes**

#### APPLICATION INFORMATION

For improved readability, the specification contains many application data points. When application information is given, it is advisory and does not form part of the specification for the device.

#### BARE DIE DISCLAIMER

All die are tested and are guaranteed to comply with all data sheet limits up to the point of wafer sawing for a period of ninety (90) days from the date of UltraChip's delivery. There is no post waffle saw/pack testing performed on individual die. Although the latest modern processes are utilized for wafer sawing and die pick-&-place into waffle pack carriers, UltraChip has no control of third party procedures in the handling, packing or assembly of the die. Accordingly, it is the responsibility of the customer to test and quality their application in which the die is to be used. UltraChip assumes no liability for device functionality or performance of the die or systems after handling, packing or assembly of the die.

#### LIFE SUPPORT APPLICATIONS

These devices are not designed for use in life support appliances, or systems where malfunction of these products can reasonably be expected to result in personal injuries. Customer using or selling these products for use in such applications do so at their own risk.

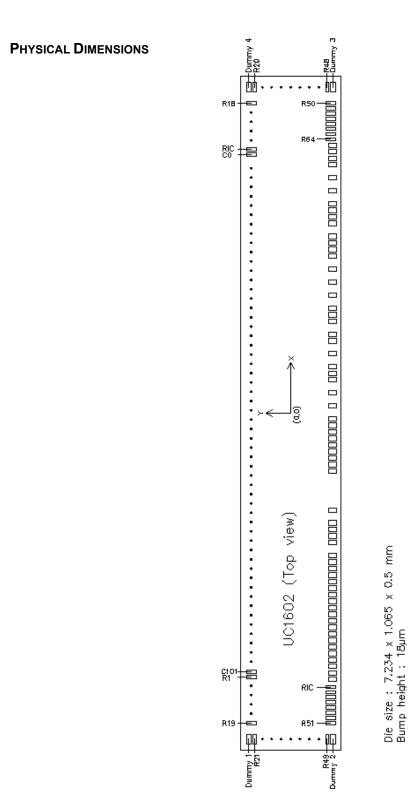

65x102 Matrix LCD Controller-Drivers

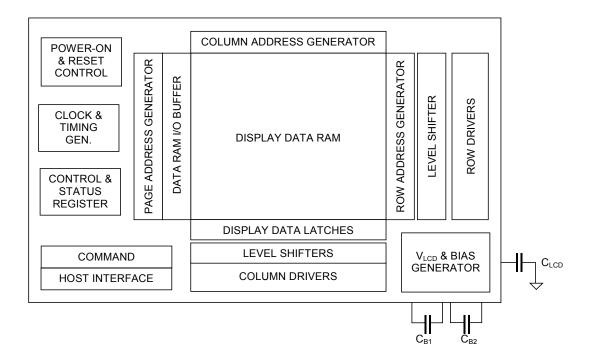

### **BLOCK DIAGRAM**

High-Voltage Mixed-Signal IC

### **PIN DESCRIPTION**

| Name                                                     | Туре              | Pins | Description                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|----------------------------------------------------------|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                          | MAIN POWER SUPPLY |      |                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| V <sub>DD1</sub>                                         |                   |      | $V_{\text{DD1}}$ supplies for display data RAM and digital logic, $V_{\text{DD2}}$ supplies for $V_{\text{LCD}}/V_{\text{B}}$ generator, $V_{\text{DD3}}$ supplies for $V_{\text{REF}}$ and other analog circuits.                                        |  |  |  |  |  |  |

| V <sub>DD2</sub>                                         | PWR               |      | $V_{DD2}/V_{DD3}$ should be connected to the same power source. But $V_{DD1}$ can be connected to a source voltage no higher than $V_{DD2}/V_{DD3}$ .                                                                                                     |  |  |  |  |  |  |

| V <sub>DD3</sub>                                         | V <sub>DD3</sub>  |      | In COG applications, always use separate ITO traces for $V_{\text{DD1}},V_{\text{DD2}}$ and $V_{\text{DD3}}$ to reduce noise coupling.                                                                                                                    |  |  |  |  |  |  |

| V <sub>SS</sub><br>V <sub>SS2</sub>                      | GND               |      | Ground. In COG applications, use separate ITO traces to connect $V_{\rm SS}$ and $V_{\rm SS2}$ to the separate GND pins or to the shared GND pin and minimize both ITO resistance.                                                                        |  |  |  |  |  |  |

|                                                          |                   |      | LCD POWER SUPPLY                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| V <sub>B1+</sub><br>V <sub>B1-</sub><br>V <sub>B0-</sub> | PWR               |      | LCD Offset Voltages. Connect two $C_B$ capacitors between $V_{B^+}$ to $V_{B0^+}$ and $V_{B0^-}$ to V $_{B}$ . For optimum operation result, minimize the ITO trace resistance of these nodes.                                                            |  |  |  |  |  |  |

| V <sub>B0+</sub>                                         |                   |      | Place $C_{B1}$ and $C_{B0}$ on the FPC or COF to reduce I/O pin count by 4.                                                                                                                                                                               |  |  |  |  |  |  |

| V <sub>LCD-IN</sub>                                      | PWR               |      | Main LCD Power Supply. When internal V <sub>LCD</sub> is used, connect these pins together. When external V <sub>LCD</sub> source is used, connect external V <sub>LCD</sub> source to V <sub>LCD-IN</sub> pins and leave V <sub>LCD-OUT</sub> pins open. |  |  |  |  |  |  |

| V <sub>LCD-OUT</sub>                                     |                   |      | A by-pass capacitor $C_L$ should be connected between $V_{LCD}$ and $V_{SS2}.$ Minimize the ITO trace resistance in COG applications.                                                                                                                     |  |  |  |  |  |  |

#### Νοτε

Recommended capacitor values:

$\begin{array}{l} C_{B:} 150{\sim}500x \ \ LCD \ \ load \ \ capacitance \ \ or \ \ 1.0uF \ \ (V_{BR} > 3V), \ whichever \ is \ higher. \\ C_{L:} 20{\sim}50x \ \ \ LCD \ \ load \ \ capacitance \ \ or \ \ 0.2uF \ \ (V_{BR} > V_{LCD}{+1V}), \ whichever \ \ is \ higher. \\ \end{array}$

| Name                            | I/O                               | Pins | Description                                                                                                                                                                            |  |  |  |  |  |

|---------------------------------|-----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                 | LCD DRIVE OUTPUT (UP TO 198 PINS) |      |                                                                                                                                                                                        |  |  |  |  |  |

| C0,<br>~<br>C101                | ΗV                                |      | LCD column driver outputs. Support up to 102 columns.<br>Leave unused drivers open-circuit.                                                                                            |  |  |  |  |  |

| RIC                             | HV                                |      | LCD icon driver outputs. RIC has two pads. These two pads are used to drive icons. Leave unused drivers open-circuit.                                                                  |  |  |  |  |  |

| R1,<br>R3,<br>R63<br>R2,<br>R4, | HV                                |      | LCD row driver outputs. Support up to 64 rows.<br>Drivers for even and odd row are group into two separate groups along<br>the two sides of the IC. Leave unused drivers open-circuit. |  |  |  |  |  |

65x102 Matrix LCD Controller-Drivers

| Name | I/O | Pins | Description |

|------|-----|------|-------------|

| R64  |     |      |             |

High-Voltage Mixed-Signal IC

©2000

| Name                                              | Туре | Pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|---------------------------------------------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                   |      |      | CONFIGURATION PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| PS[1:0]                                           | С    |      | Parallel/Serial.Serial modes:"LL": serial (S8)Parallel modes:"HL": 8080"HH": 6800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| V <sub>DD1</sub>                                  | S    |      | For configuration purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                                   |      |      | TEST PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| TP3                                               | Ι    |      | Test control. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| TP[2:0]                                           | Ι    |      | Test control. Leave these pins open during normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TST[3:1]                                          | I/O  |      | Test I/O pins. Leave these pins open during normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| HOST INTERFACE                                    |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| V <sub>DD1</sub> S Use for configuration purpose. |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| CS0/A0                                            |      |      | Chip Select or Chip Address. In parallel mode and S8 mode, chip is selected when CS0="L" and CS1="H".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| CS1/A1                                            | I    |      | In I <sup>2</sup> C mode, A[1:0] specifies bit 3~2 of UC1602I's device address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                                   |      |      | When the chip is not selected, D[7:0] will be high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RST                                               | I    |      | When RST="L", all control registers are re-initialized by their default states and/or by their pin configurations if applicable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                                                   |      |      | When RST is not used, connect the pin to V <sub>DD1</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| CD                                                | Ι    |      | Select Control data or Display data for read/write operation. CD pin is not used in $I^2$ C modes, connect it to V <sub>DD</sub> or V <sub>SS</sub> .<br>"L": Control data "H": Display data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                                                   |      |      | WR[1:0] controls the read/write operation of the host interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| WR0<br>WR1                                        | I    |      | In parallel mode, WR[1:0] meaning depends on whether the interface is in the 6800 mode or the 8080 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                                   |      |      | In serial interface modes, these two pins are not used. Connect to $V_{\mbox{\scriptsize SS}}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| D0~D7                                             | I/O  |      | In serial interface modes, these two pills are not used. Connect to $v_{SS}$ .Bi-directional bus for both serial and parallel host interfaces.In S8 mode, connect unused pins to $V_{DD}$ or $V_{SS}$ . In I2C mode, connectD[1:0] to SCK, and D[5:2] to SDA, and D[7:6] to $V_{DD}$ or $V_{SS}$ . $\boxed{\begin{array}{c c} PS=1x & PS=0x \\ D0 & D0 & SCK \\ D1 & D1 & \\ D2 & D2 & \\ D3 & D3 & SDA \\ D4 & D4 & \\ D5 & D5 & \\ D6 & D6 & - \\ D7 & D7 & - \\ \end{array}}$ In I <sup>2</sup> C mode, SDA and SCK are in open-drain mode. Pull up resistors an required on the bus. In COG applications, be careful to control ITO trace resistance, as it will affect effective output level of SDA. |  |  |  |  |  |

#### Νοτε

Unless otherwise specified, connect all unused input pins and control pins to V<sub>SS</sub>.

### **CONTROL REGISTERS**

UC1602I contains registers which controls the chip operation. These registers can be modified by commands. The commands supported by UC1602I are described in the next section.

- *Name:* The Symbolic reference of the register byte. Note that, some symbol names refers to collection of bits (flags) within one register byte.

- *Default:* Value after *Power-up-Reset* and *System-Reset*. "PIN" means default value depends on the connection of associated configuration pin(s).

| Name | Bits | Default | Description                                                                                                                                    |  |  |  |  |  |  |

|------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MR   | 1    | 1H      | Multiplexing Rate: Number of pixel rows plus icon row.                                                                                         |  |  |  |  |  |  |

|      |      |         | 0: 49 1: 65                                                                                                                                    |  |  |  |  |  |  |

| SL   | 6    | ОH      | Start Line. Mapping from Row0 to Display Data RAM.                                                                                             |  |  |  |  |  |  |

| CR   | 8    | ОH      | Return Column Address.                                                                                                                         |  |  |  |  |  |  |

| CA   | 8    | 0H      | Display Data RAM Column Address<br>(Used in Host to Display Data RAM access)                                                                   |  |  |  |  |  |  |

| PA   | 4    | 0H      | Display Data RAM Page Address<br>(Used in Host to Display Data RAM access)                                                                     |  |  |  |  |  |  |

| BR   | 2    | 2H      | Bias Ratio. The ratio between $V_{LCD}$ and $V_{D}$ .                                                                                          |  |  |  |  |  |  |

| тс   | 2    | 0H      | Temperature Compensation (per °C).           00:         0.0%         01:         -0.05%           10:         -0.1%         11:         -0.2% |  |  |  |  |  |  |

| GN   | 2    | 3H      | Gain = V <sub>D</sub> / V <sub>PM</sub>                                                                                                        |  |  |  |  |  |  |

| PM   | 6    | 10H     | Electronic Potential Meter to generate V <sub>PM</sub> from V <sub>REF</sub>                                                                   |  |  |  |  |  |  |

| ОМ   | 2    | 0       | Operating Modes10: Sleep11: Normal01: (Not used)00: Reset                                                                                      |  |  |  |  |  |  |

| BZ   | 1    | -       | Busy with internal processes (reset, changing mode, etc.)<br>OK for Display RAM read/write access.                                             |  |  |  |  |  |  |

| RS   | 1    |         | Reset in progress, Host Interface not ready                                                                                                    |  |  |  |  |  |  |

| PC   | 3    | 07H     | Power Control.<br>PC[0] 0: LCD load < 12nF 1: LCD load > 12nF                                                                                  |  |  |  |  |  |  |

|      |      |         | PC[2:1]         00:         External V <sub>LCD</sub> 01:         4x Pump           10:         5x Pump         11:         6x Pump            |  |  |  |  |  |  |

| APC0 | 8    | 6CH     | Advanced Program Control. Default value should work fine.                                                                                      |  |  |  |  |  |  |

High-Voltage Mixed-Signal IC

©2000

| Name | Bits | Default          | Description                                                                                                                                                                                                                                                 |

|------|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC   | 3    | 0H               | Display Control:                                                                                                                                                                                                                                            |

|      |      |                  | DC[0]: PXV: Pixels Inverse<br>DC[1]: APO: All Pixels ON<br>DC[2]: DE, Display Enable                                                                                                                                                                        |

| AC   | 4    | 0H               | Address Control:                                                                                                                                                                                                                                            |

|      |      |                  | AC[0]: WA: Automatic column/page Wrap Around<br>AC[1]: Reserved (always set to 0)<br>AC[2]: PID: PA (page address) auto increment direction (L:+1 H:-1)<br>AC[3]: CUM: Cursor update mode,<br>when CUM=1, CA increment on write only, wrap around suspended |

| LC   | 4    |                  | LCD Layout Control:                                                                                                                                                                                                                                         |

|      |      | 0<br>0<br>0<br>0 | LC[0]: MSF: MSB First mapping Option<br>LC[1]: Reserved (always set to 0)<br>LC[2]: MX, Mirror X (Column sequence inversion)<br>LC[3]: MY, Mirror Y (Row sequence inversion)                                                                                |

65x102 Matrix LCD Controller-Drivers

## COMMANDS

The following is a list of host commands support by UC1062I.

| C/D: | 0: Control,     | 1: Data       |

|------|-----------------|---------------|

| W/R: | 0: Write Cycle, | 1: Read Cycle |

# Useful Data bits

Don't Care

| Command                                                    | C/D    | W/R    | D7     | D6     | D5     | D4     | D3     | D2     | D1     | D0     | Action                                     |

|------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------------------------------------|

| Write Data Byte                                            | 1      | 0      | #      | #      | #      | #      | #      | #      | #      | #      | Write 1 byte @ PA/CA                       |

| Read Data Byte                                             | 1      | 1      | #      | #      | #      | #      | #      | #      | #      | #      | Read 1 byte @ PA/CA                        |

| Get Status                                                 | 0      | 1      | ΒZ     | MX     | DE     | RS     | 0      | 0      | 0      | 0      | Get Status Summary                         |

| Set Column Address LSB                                     | 0      | 0      | 0      | 0      | 0      | 0      | #      | #      | #      | #      | Set CA[3:0]=D[3:0]                         |

| Set Column Address MSB                                     | 0      | 0      | 0      | 0      | 0      | 1      | #      | #      | #      | #      | Set CA[7:4] =D[3:0]                        |

| Set Mux rate & Temperature<br>Compensation.                | 0      | 0      | 0      | 0      | 1      | 0      | 0      | #      | #      | #      | Set MR=D[2]<br>Set TC[1:0]=D[1:0]          |

| Set Power Control                                          | 0      | 0      | 0      | 0      | 1      | 0      | 1      | #      | #      | #      | Set PC[2:0]=D[2:0]                         |

| Set Adv. Program Control                                   | 0      | 0      | 0      | 0      | 1      | 1      | 0      | 0      | R      | R      | Set APC[R][7:0]=D[7:0],                    |

| (double byte command)                                      | 0      | 0      | #      | #      | #      | #      | #      | #      | #      | #      | where RR = 00, or 01                       |

| Set Start Line                                             | 0      | 0      | 0      | 1      | #      | #      | #      | #      | #      | #      | Set SL[5:0]=D[5:0]                         |

| Set V <sub>REF</sub> potential meter (double-byte command) | 0<br>0 | 0<br>0 | 1<br># | 0<br># | 0<br># | 0<br># | 0<br># | 0<br># | 0<br># | 1<br># | Set PM[5:0]=D[5:0]<br>Set GN[1:0]=D[7:6]   |

| Set RAM Address Control                                    | 0      | 0      | 1      | 0      | 0      | 0      | 1      | #      | #      | #      | Set AC[2:0]=D[2:0]                         |

| Set Column Mirroring                                       | 0      | 0      | 1      | 0      | 1      | 0      | 0      | 0      | 0      | #      | Set LC[2]=D0                               |

| Set All-Pixel-ON                                           | 0      | 0      | 1      | 0      | 1      | 0      | 0      | 1      | 0      | #      | Set DC[1]=D0                               |

| Set Inverse Display                                        | 0      | 0      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | #      | Set DC[0]=D0                               |

| Set Display ON/OFF                                         | 0      | 0      | 1      | 0      | 1      | 0      | 1      | 1      | 1      | #      | Set DC[2]=D0                               |

| Set Page Address                                           | 0      | 0      | 1      | 0      | 1      | 1      | #      | #      | #      | #      | Set PA[3:0]=D[3:0]                         |

| Set LCD to RAM Mapping                                     | 0      | 0      | 1      | 1      | 0      | 0      | #      | #      | 0      | #      | Set LC[3:0]=D[3:0]                         |

| Set Cursor Update Mode                                     | 0      | 0      | 1      | 1      | 1      | 0      | 0      | 0      | 0      | 0      | Set AC[3]=1, CR=CA;                        |

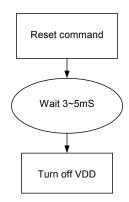

| System Reset                                               | 0      | 0      | 1      | 1      | 1      | 0      | 0      | 0      | 1      | 0      | System Reset sequence                      |

| NOP                                                        | 0      | 0      | 1      | 1      | 1      | 0      | 0      | 0      | 1      | 1      | No operation                               |

| Set LCD Bias Ratio                                         | 0      | 0      | 1      | 1      | 1      | 0      | 1      | 0      | #      | #      | Set BR[1:0]= D[1:0]                        |

| Set/Reset<br>Cursor-Update Mode                            | 0      | 0      | 1      | 1      | 1      | 0      | 1      | 1      | 1      | #      | Set AC[3]=D0; if (D0)<br>CR=CA else CA=CR; |

| Set Test Control<br>(double byte command)                  | 0<br>0 | 0<br>0 | 1<br># | 1<br># | 1<br># | 0<br># | 0<br># | 1<br># | Т<br># | T<br># | For testing only.<br>Do not use.           |

\* Other than commands listed above, all other bit patterns result in NOP (No Operation).

High-Voltage Mixed-Signal IC

### LCD VOLTAGE SETTINGS

#### **MULTIPLEX RATES**

Two multiplex rates are supported in UC1602I: 65 or 49. The default is 65 and it can be changed by programming.

#### **BIAS SELECTION**

Bias Ratio (*BR*) is defined as the ratio between  $V_{LCD}$  and  $V_{D}$ , i.e. *BR* =  $V_{LCD}/V_D$ , where  $V_D$  is the SEG data signal and its value is |  $V_{B1+} - V_{B1-}$  |

The optimum Bias Ratio can be calculated by:

$\sqrt{Mux+1}$

UC1602I supports four bias ratios as below.

| BR         | 0 | 1 | 2 | 3 |  |  |  |  |

|------------|---|---|---|---|--|--|--|--|

| Bias Ratio | 6 | 7 | 8 | 9 |  |  |  |  |

|            |   |   |   |   |  |  |  |  |

Table 2: BR vs. Mux rates

BR and MR can both be changed dynamically by software programming.

#### **V**<sub>D</sub> GENERATION

$V_D$  is generated internally by UC106. The value of  $V_D$  is determined by three control registers: *GN* (Gain), *PM* (Potential Meter), TC (Temperature Compensation) with the following relationship:

$$V_D = Gain \times V_{Pl}$$

where  $V_{PM}$  is the output of an internal Electronic Potential Meter. The maximum value for  $V_D$ depends on the value of  $V_{DD2}$ . At  $V_{DD2}$  = 2.4V,  $V_D$ should be kept under 1.2V.

The value of V<sub>PM</sub> is given by:

$$V_{PM} = \frac{600 + PM}{1200} \times V_{RE}$$

The value of *Gain* is controlled by GN[1:0]. Their relationship is shown below:

| GN[1:0] | 00   | 01   | 10   | 11   |

|---------|------|------|------|------|

| Gain    | 1.35 | 1.49 | 1.64 | 1.81 |

Table 3: Gain vs. GN value

#### **V**<sub>REF</sub> **TEMPERATURE COMPENSATION**

$V_{\text{REF}}$  is a temperature compensated reference voltage.  $V_{\text{REF}}$  increases automatically as ambient temperature cools down.

Four (4) different temperature compensated  $V_{\text{REF}}$  can be selected via pin wiring. The compensation coefficient is given by the following table:

| TC[1:0]              | 0   | 1     | 2     | 3     |

|----------------------|-----|-------|-------|-------|

| % per <sup>°</sup> C | 0.0 | -0.05 | -0.10 | -0.20 |

**Table 4:** Temperature Compensation

For all TC values,  $V_{\text{REF}}$  are normalized to 1.2V at 25 °C.

#### VLCD SELECTION

$V_{LCD}$  may be supplied either by internal charge pump or by external power supply. The source of  $V_{LCD}$  is controlled by PC[2:1].

When  $V_{LCD}$  is generated internally its value has the following relationship with  $V_D$ :

$$V_{LCD} = BiasRatio \times V_D$$

Given V<sub>REF</sub> = 1.2V at 25 °C, V<sub>LCD</sub> becomes:

$$V_{LCD} \cong BiasRatio \times Gain \times \frac{600 + PM}{1200} \times 1.2$$

(1)

When PM=0, then equation (1) becomes:

$$V_{LCD} \cong BiasRatio \times Gain \times 0.6$$

(1b)

#### LOAD DRIVING STRENGTH

UC106's drivers and power supply circuits are designed to handle panel capacitance load of 25nF at  $V_{LCD}$ =9V when  $V_{DD2}$ >= 2.4V.

UC1602I load driving strength is sensitive to ITO impedance of power supply circuits ( $V_{DD2}$ ,  $V_{SS2}$ ,  $V_{B0/B1}$ ,  $V_{LCD}$ .) Be sure to minimize the resistance of these ITO traces for COG applications.

#### **POWER SUPPLY CONFIGURATION**

UC1602I has built-in charge pump with on-chip pumping capacitors. The number of pump stages used can be programmed by setting PC[2:1] register. Make sure the chip is in Reset mode before changing the value of PC[2:0].

Given the same display quality, the lower the PC[2:1] setting the more efficient is UC1602I, but the weaker is the driving strength. In application, designer is recommended to verify the design with the highest setting first before trying lower settings to achieve better efficiency.

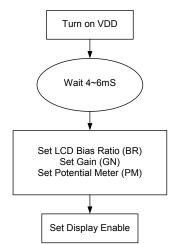

Due to the use of fully embedded power supply, built-in power ready detector, and drain circuit, there is no rigid power up or power down sequences for UC1602I controllers when using internal  $V_{LCD}$  generator.

On the other hand, caution must be exercised when external  $V_{\text{LCD}}$  source is used. The general rule of thumb is to make sure Display Enable is

OFF before connecting or disconnecting external  $V_{LCD}$  sources.

# LCD DISPLAY CONTROLS

#### **CLOCK & TIMING GENERATOR**

The nominal frequency of UC1602I built-in system clock is 166kHz, the LCD refresh frequency is 80Hz. All required components for the clock oscillator are built-in. No external parts are required.

#### **DRIVER MODES**

Row and column drivers can be in either Idle mode or Active mode, controlled by Display Enable flag (DC[2]). When column drivers are in idle mode, their outputs are high-impedance (open circuit). When row drivers are in idle mode, their outputs are connected to  $V_{SS}$ .

#### **DRIVER ARRANGEMENTS**

The naming conventions are: Rx (where x=1~64) refers to the row driver for the x-th row of pixels on the LCD panel; RIC refers to the icon driver.

Row drivers are clustered into "even row drivers" and "odd row drivers", along the two sides of the chip to enhance the symmetry of ITO layout.

The mapping of Rx to LCD pixel rows is the same for all MR settings. When MR setting is not 11, leave unused row drivers open.

### 65x102 Matrix LCD Controller-Drivers

#### **DISPLAY CONTROLS**

There are three display control flags in the control register DC: Display Enable (DE), All-Pixel-ON (APO) and Inverse (PXV). DE has the overriding effect over PXV and APO.

#### DISPLAY ENABLE (DE)

Display Enable is controlled by the Set Display ON command. When DE is set to OFF (logic "0"), both column and row drivers will become idle and the chip will put itself into Sleep Mode to conserve power.

When the DE is set to ON, the chip will first exit from Sleep mode by restoring the power ( $V_{LCD}$ ,  $V_D$  etc.). When the power is restored, column and row drivers will become active.

#### ALL PIXELS ON (APO)

When set, this flag will force all column drivers to output On signals, disregarding the data stored in the display buffer.

This flag has no effect when Display Enable is OFF and it has no effect on data stored in RAM.

#### INVERSE (PXV)

When this flag set to ON, column drivers will output the inverse of the value it received from the display buffer RAM. This flag has no impact on data stored in RAM.

High-Voltage Mixed-Signal IC

©2000

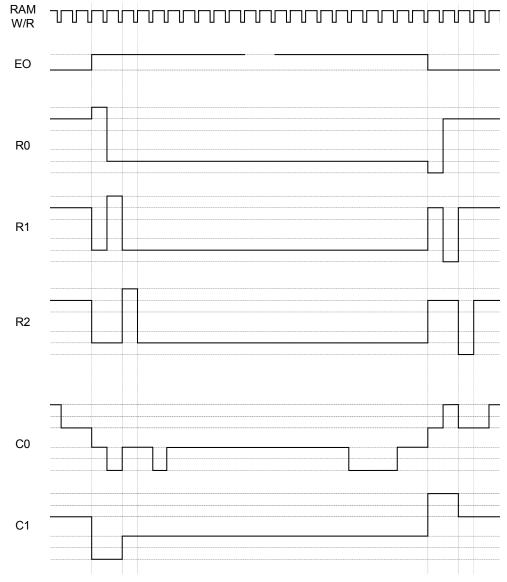

Fig. 4 Column and Row Driving Waveform

65x102 Matrix LCD Controller-Drivers

#### **HOST INTERFACE**

UC1602I series supports several parallel and serial host interface formats.

| Bus      | Bus Type                  | Access |  |  |  |

|----------|---------------------------|--------|--|--|--|

| Parallel | 8080                      | R/W    |  |  |  |

| Falalici | 6800                      | R/W    |  |  |  |

| Serial   | 4-wire (S8)               | W      |  |  |  |

| Sella    | 2-wire (I <sup>2</sup> C) | R/W    |  |  |  |

Table 5: Host interfaces Choices

System designers can use either the 8-bit parallel bus to achieve the high data transfer rate, or use serial bus to create LCD modules with as few as 9-pin connectors.

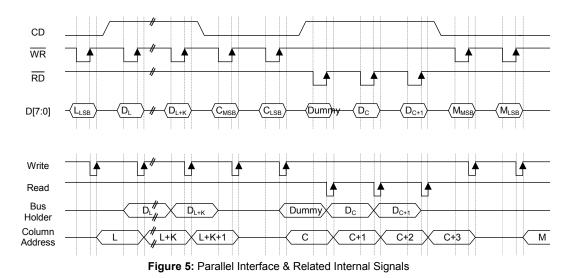

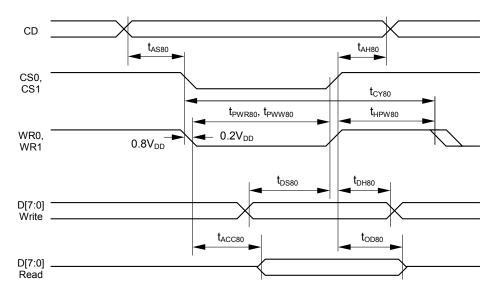

#### **PARALLEL INTERFACE**

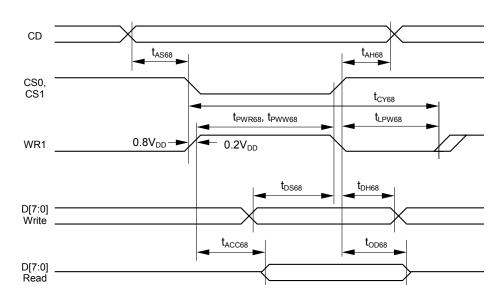

It is possible to interface UC1602I controllers directly to either an 8080-style MPU bus or a 6800-style MCU bus with the following connection.

| Bus Type | WR0 | WR1 |  |  |

|----------|-----|-----|--|--|

| 8080     | WR  | RD  |  |  |

| 6800     | R/W | Е   |  |  |

Table 6: MPU bus control signal interface

The timing relationship between UC1602I internal control signal RD, WR and their associated bus actions are shown in the figure below. The generation of UC1602I internal bus control signals WR and RD is shown in the table below.

| Bus Type | WR            | RD           |

|----------|---------------|--------------|

| 8080     | WR0           | WR1          |

| 6800     | !(WR1 & !WR0) | !(WR1 & WR0) |

Table 7: WR and RD signal generation

#### DISPLAY RAM DATA TRANSFER

UC1602I Display Data RAM (RAM) read interface is implemented as a two-stage pipe-line. This architecture requires that, every time memory address is modified, either in parallel mode or serial mode, all three commands (*Set CA-LSB, Set CA-MSB, Set PA*) need to be issued, and a dummy read cycle need to be performed before the actual data can propagate through the pipeline and be read from data port D[7:0].

There is no pipeline in write interface of RAM, and the data is transferred directly from data bus buffer to RAM.

High-Voltage Mixed-Signal IC

#### SERIAL INTERFACE

UC1602I supports two serial modes, 4-wire mode (PS=0), and 2-wire I<sup>2</sup>C mode (PS=1). The mode of interface is determined during power-up process by the value of PS[1:0].

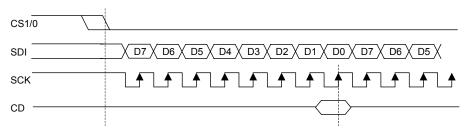

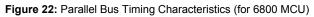

#### 4-WIER SERIAL INTERFACE (S8)

Only write operations are supported in 4-wire serial mode. Pin CS[1-0] are used for chip select and bus cycle reset. Pin CD is used to determine

the content of the data been transferred. On each write cycle, 8 bits of data, MSB first, are latched on eight (8) rising SCK edges into an 8-bit data holder. If CD=0, the data byte will be decoded as command. If CD=1, this 8-bit will be treated as data and transferred to proper address in the Display Data RAM at the rising edge of the last SCK pulse.

Pin CD is examined when SCK is pulled low for the LSB (D0) of each token.

Figure 6: 4-wire Serial Interface (S8)

### 2-WIRE SERIAL INTERFACE (I<sup>2</sup>C)

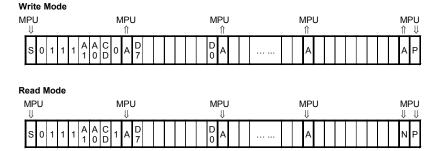

When PS[1-0] is set to "LH", UC1602I is configured as a slave receiver/transmitter, for industry standard I<sup>2</sup>C serial interface.

Each UC1602I  $I^2C$  interface sequence starts with a START condition (S) from the bus master, followed by a sequence header, containing a device address, the direction of transfer (RW, 0:Write, 1:Read) and mode of transfer (CD, 0:Control, 1:Data).

In this mode, CS[1:0] become A[1:0] and are used to configure UC1602I's device address. WR[1:0] and CD are not used and may be connected to GND.

#### Figure 7: 2-wire interface protocol

The direction and content of the bytes following each header byte are fixed for the sequence. To change the direction ( $R \Leftrightarrow W$ ) or the content type ( $C \Leftrightarrow D$ ), start a new interface sequence with a new header.

After receiving the header, the UC1602I will send out an acknowledge signal (A). Then, depends on the setting of the header, the transmitting device (either the bus master or UC1602I) will start placing data bits on the serial bus, MSB to LSB, and the sequence will repeat until a STOP signal (P, in WRITE), or a Not Acknowledge (N, in READ mode) is sent by the bus master.

Note that, for data read (CD=1), the first byte of data is dummy.

14

65x102 Matrix LCD Controller-Drivers

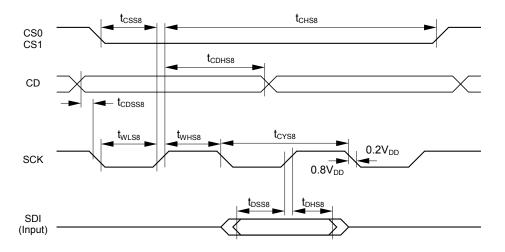

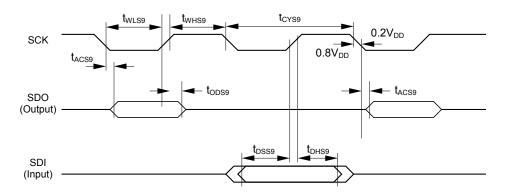

#### 2-WIRE INTERFACE TIMING

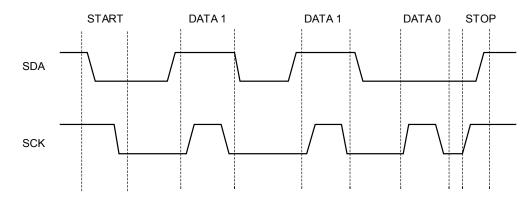

The 2-wire  $l^2C$  interface is a bidirectional interface. In order to properly communicate between all  $l^2C$  devices, certain timing protocols need to be satisfied.

There are always master and slave devices on an  $I^2C$  bus. The master device initiates an read or write action to the slave device with an address. The selected slave device to the action transimitting or receiving data. Without any action, the  $I^2C$  bus are pulled high by two pull-up resistors. A master or slave device initiates or responds to an action by pulling down the bus. UC1602I is a slave  $I^2C$  device.

In idle mode, the both wires, SDA and SCK are pulled high. When the SDA makes a HIGH to LOW transition while SCK remains high, this is the  $I^2C$  START condition. When the SDA makes a LOW to HIGH transition while SCK remain low, this is  $I^2C$  STOP condition. In between a START and STOP condition,  $I^2C$  transmits data bits by toggling SCK while SDA remains stable. These relations are shown in **Figure 8**.

Figure 8. I<sup>2</sup>C bus SDA and SCK timing relation.

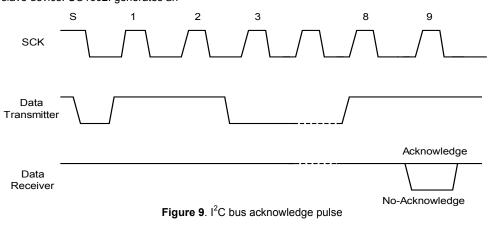

Each eight-bit of data is followed by an acknowledge pulse from the receiver as shown in **Figure 9**. The master device will generate an extra pulse during this time. It is the receiving device's responsibility to generate this acknowledge pulse regardless of being a master or slave device. UC1602I generates an

acknowledge pulse in the write mode. When the acknowledge pulse is HIGH, UC1602I has received write instruction or data correctly. When the acknowledge pulse is LOW, UC1602I has not correctly received instruction and the master device needs to resend.

High-Voltage Mixed-Signal IC

#### SERIAL INTERFACE EXAMPLES

The table below shows an example of UC1602I to support a 9-pin (or 4-pin, if  $C_{\text{LCD}}$  and  $C_{\text{Bx}}$  are mounted on FPC or COF) interface using I<sup>2</sup>C.

| Hard wired                                                                 | Comment                                                                            |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| RST="H"                                                                    | Use software Reset exclusively.                                                    |

| CA[1:0] ="XX"                                                              | Chip address                                                                       |

| SP="01"                                                                    | UC1602I will power up and reset to I <sup>2</sup> C interface mode                 |

| on FPC/COF                                                                 | Comment                                                                            |

| V <sub>B0+</sub> , V <sub>B0-</sub><br>V <sub>B1+</sub> , V <sub>B1-</sub> | Connect to proper capacitors.<br>These capacitors can be<br>mounted on FPC as SMD. |

| Interface                                                                  | Comment                                                                            |

| SCK                                                                        | Connect to clock                                                                   |

| SDA                                                                        | Serial I/O                                                                         |

| V <sub>DD1</sub> , V <sub>DD2</sub> ,<br>V <sub>DD3</sub>                  | Use three separate ITO traces to<br>one common node.                               |

| V <sub>SS1</sub> ,V <sub>SS2</sub>                                         | Use two separate ITO to one common node.                                           |

| V <sub>LCD</sub>                                                           | To V <sub>LCD</sub> bypass capacitor                                               |

Table 9: I<sup>2</sup>C Interface Example

The table below shows an example of UC1602I to support a 11-pin (or 6-pin, if  $C_{LCD}$  and  $C_{Bx}$  are mounted on FPC or COF), using S8, Write-only interface mode and CD pin for bus control.

| Hard wired                                                                 | Comment                                                 |  |  |  |  |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|--|

| RST="H"                                                                    | Use software Reset exclusively.                         |  |  |  |  |  |  |

| SP="00"                                                                    | UC1602I will power up and reset<br>to S8 interface mode |  |  |  |  |  |  |

| SDO                                                                        | Not used, Connect to GND                                |  |  |  |  |  |  |

| On FPC/COF                                                                 | Comment                                                 |  |  |  |  |  |  |

| V <sub>B0+</sub> , V <sub>B0-</sub><br>V <sub>B1+</sub> , V <sub>B1-</sub> | Connect to two capacitors, mounted on FPC as SMD.       |  |  |  |  |  |  |

| Interface                                                                  | Comment                                                 |  |  |  |  |  |  |

| CS0 (or CS1)                                                               | Chip select                                             |  |  |  |  |  |  |

| CD                                                                         | Control or Display.                                     |  |  |  |  |  |  |

| SCK                                                                        | Connect to clock                                        |  |  |  |  |  |  |

| SDA                                                                        | Serial Data IN                                          |  |  |  |  |  |  |

| V <sub>DD1</sub> , V <sub>DD2</sub> ,<br>V <sub>DD3</sub>                  | Use three separate ITO traces to<br>one common node.    |  |  |  |  |  |  |

| V <sub>SS1</sub> ,V <sub>SS2</sub>                                         | Use two separate ITO to one common node.                |  |  |  |  |  |  |

| V <sub>LCD</sub>                                                           | To $V_{LCD}$ bypass capacitor                           |  |  |  |  |  |  |

Table 10: S8 Interface Example

#### **DISPLAY DATA RAM**

#### DATA ORGANIZATION

The display data is one bit per pixel and stored in a dual port static RAM (RAM, for Display Data RAM). The RAM size is 65x102. This array of data bits are further organized into pages of 8 bit slices to facilitate parallel bus interface.

At the end of the graphics data, UC1602I contains an 1-bit wide page for icon data.

When Mirror X (MX, LC[2]) is OFF, the 1<sup>st</sup> column of LCD pixels will correspond to the bits of the first byte of each page, the 2<sup>nd</sup> column of LCD pixels correspond to the bits of the second byte of each page, etc.

MSB FIRST OR LSB FIRST

There are two options to map D[7:0] to RAM, MSB first (MSF=1), or LSB first (MSF=0), as illustrated below.

#### DISPLAY DATA RAM ACCESS

The memory used in UC1602I Display Data RAM (RAM) is a special purpose two port SRAM which allows asynchronous access to both its column and row data. Thus, RAM can be independently

accessed both for Host Interface and for display operations.

#### DISPLAY DATA RAM ADDRESSING

A Host Interface (HI) memory access operation starts with specifying Page Address (PA) and Column Address (CA) by issuing *Set Page Address* and *Set Column Address* commands.

If wrap-around (WA, AC[0]) is OFF (0), CA will stop incrementing after reaching the end of page (102), and system programmers need to set the values of PA and CA explicitly.

If WA is ON (1), after CA has reached the end of page (CA=101), CA will be rest to 0 and PA will increment or decrement, depending on the setting of Page Increment Direction (PID, AC[2]). When PA reaches the boundary of RAM (i.e. PA = 0 or 7), PA will be wrapped around to the other end of RAM and continue.

#### ICON DATA ADDRESSING

The Icon Page is addressed by explicitly setting PA to 8 (the 9<sup>th</sup> page). When addressing Icon page, auto wrap-around will be suspended and CA will stop when CA reaches 102.

High-Voltage Mixed-Signal IC

©2000

| PA[3:0] | М<br>0   | 5⊦<br>1  | Line<br>Adderss |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | SL=0       | /=0<br>SL=16 | SL=0       | SL=0       | /=1<br>SL=25 | SL=      |

|---------|----------|----------|-----------------|---|------|--------------|----------|----------|----------|----------|----------|-----|----------|----------|----------|-----|------|------|------------|--------------|------------|------------|--------------|----------|

|         | D0       | D7       | 00H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R1         | R49          | R64        | R48        | R25          | R        |

|         | D1       | D6       | 01H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R2         | R50          | R63        | R47        | R24          | R        |

|         | D2       | D5       | 02H             |   |      | -            |          |          |          |          |          |     |          |          |          |     |      |      | R3         | R51          | R62        | R46        | R23          | R7       |

| 0000    | D3       | D4       | 03H             | - |      | _            |          |          |          |          |          |     | Page 0   |          |          |     |      |      | R4         | R52          | R61        | R45        | R22          | R        |

|         | D4<br>D5 | D3<br>D2 | 04H<br>05H      |   |      | -            |          |          |          |          |          |     |          |          |          |     |      |      | R5<br>R6   | R53<br>R54   | R60<br>R59 | R44<br>R43 | R21<br>R20   | R:<br>R: |

|         | D5       | D2       | 06H             |   | _    | -            |          |          |          | _        |          |     |          |          |          |     | _    | _    | R7         | R55          | R58        | R43        | R19          | R        |

|         | D7       | D0       | 07H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R8         | R56          | R57        | R41        | R18          | R        |

|         | D0       | D7       | 08H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R9         | R57          | R56        | R40        | R17          | R        |

|         | D1       | D6       | 09H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R10        | R58          | R55        | R39        | R16          |          |

|         | D2       | D5       | 0AH             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R11        | R59          | R54        | R38        | R15          |          |

| 0001    | D3       | D4       | 0BH             |   |      |              |          |          |          |          |          |     | Page 1   |          |          |     |      |      | R12        | R60          | R53        | R37        | R14          |          |

|         | D4       | D3       | 0CH             |   |      |              |          |          |          |          |          |     | . ugo .  |          |          |     |      |      | R13        | R61          | R52        | R36        | R13          |          |

|         | D5       | D2       | 0DH             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R14        | R62          | R51        | R35        | R12          |          |

|         | D6       | D1       | 0EH             |   |      | _            |          |          |          |          |          |     |          |          |          |     |      |      | R15        | R63          | R50        | R34        | R11          |          |

|         | D7<br>D0 | D0<br>D7 | 0FH<br>10H      |   |      | -            |          |          |          |          |          |     |          | -        |          |     |      |      | R16<br>R17 | R64<br>R1    | R49<br>R48 | R33<br>R32 | R10<br>R9    |          |

|         | D0       | D7<br>D6 | 10H             | - |      | -            |          |          |          |          |          |     |          |          |          |     |      |      | R17        | R1<br>R2     | R48<br>R47 | R32<br>R31 | R9<br>R8     |          |

|         | D1<br>D2 | D0       | 12H             |   |      | -            |          |          |          |          |          |     |          |          |          |     |      |      | R19        | R3           | R46        | R30        | R7           |          |

|         | D3       | D4       | 13H             |   | -    | 1            |          |          |          | _        |          |     |          |          |          |     |      | _    | R20        | R4           | R45        | R29        | R6           |          |

| 0010    | D0       | D3       | 14H             | 1 | F    | t            |          | t –      |          |          |          |     | Page 2   |          |          |     |      |      | R21        | R5           | R44        | R28        | R5           |          |

|         | D5       | D2       | 15H             |   |      | 1            |          |          |          |          |          |     |          |          |          |     |      |      | R22        | R6           | R43        | R27        | R4           |          |

| į       | D6       | D1       | 16H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R23        | R7           | R42        | R26        | R3           |          |

|         | D7       | D0       | 17H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R24        | R8           | R41        | R25        | R2           |          |

| Ţ       | D0       | D7       | 18H             | _ |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R25        | R9           | R40        | R24        | R1           |          |

| ļ       | D1       | D6       | 19H             | - |      |              |          | <u> </u> |          |          |          |     |          |          |          |     |      |      | R26        | R10          | R39        | R23        | R64          | R4       |

| ļ       | D2       | D5       | 1AH             | - | -    | ┢            | -        | <u> </u> |          |          |          |     |          | -        |          |     |      |      | R27        | R11          | R38        | R22        | R63          | R4       |

| 0011    | D3       | D4       | 1BH             |   |      |              |          |          |          |          |          |     | Page 3   |          |          |     |      |      | R28        | R12          | R37        | R21        | R62          | R4       |

|         | D4       | D3       | 1CH             | - |      | -            |          |          |          |          |          |     | -        |          |          |     |      |      | R29        | R13          | R36        | R20        | R61          | R4       |

|         | D5<br>D6 | D2<br>D1 | 1DH<br>1EH      | - |      | -            |          |          |          |          |          |     |          |          |          |     |      |      | R30<br>R31 | R14<br>R15   | R35<br>R34 | R19<br>R18 | R60<br>R59   | R4<br>R4 |

|         | D0       | D0       | 1FH             |   |      | -            |          |          |          |          |          |     |          | -        |          |     |      |      | R31        | R16          | R33        | R17        | R58          | R4       |

|         | D0       | D7       | 20H             | 1 |      | -            |          | -        |          |          |          |     |          |          |          |     |      |      | R32        | R17          | R32        | R16        | R57          | R4       |

|         | D1       | D6       | 21H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R34        | R18          | R31        | R15        | R56          | R4       |

| l l     | D2       | D5       | 22H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R35        | R19          | R30        | R14        | R55          | R        |

| 0100    | D3       | D4       | 23H             |   |      |              |          |          |          |          |          |     | Page 4   |          |          |     |      |      | R36        | R20          | R29        | R13        | R54          | R        |

| 0100    | D4       | D3       | 24H             |   |      |              |          |          |          |          |          |     | Fage 4   |          |          |     |      |      | R37        | R21          | R28        | R12        | R53          | R        |

|         | D5       | D2       | 25H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R38        | R22          | R27        | R11        | R52          | R        |

|         | D6       | D1       | 26H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R39        | R23          | R26        | R10        | R51          | R        |

|         | D7       | D0       | 27H             |   | -    | -            |          |          |          |          |          |     |          | _        |          |     |      |      | R40        | R24          | R25        | R9         | R50          | R        |

|         | D0<br>D1 | D7<br>D6 | 28H<br>29H      | - | -    | $\vdash$     | -        | -        | $\vdash$ |          |          |     |          | -        |          |     |      |      | R41<br>R42 | R25<br>R26   | R24<br>R23 | R8<br>R7   | R49<br>R48   | R3<br>R3 |

| -       | D1<br>D2 | D6<br>D5 | 29H<br>2AH      | - | ⊢    | ┢            | -        | -        | $\vdash$ | $\vdash$ | $\vdash$ |     |          | -        |          |     |      | _    | R42<br>R43 | R26<br>R27   | R23<br>R22 | R7<br>R6   | R48<br>R47   | R        |

|         | D2<br>D3 | D5<br>D4 | 2AH<br>2BH      | 1 | ⊢    | $\vdash$     | -        | -        | $\vdash$ |          | -        |     | _        | ⊢        |          | _   |      | -    | R43        | R27<br>R28   | R22<br>R21 | R5         | R47<br>R46   | R        |

| 0101    | D3<br>D4 | D4       | 2DH<br>2CH      | 1 | ⊢    | $\vdash$     | -        | 1        |          |          |          |     | Page 5   | $\vdash$ |          | _   |      | -    | R44        | R20          | R21        | R4         | R40          | R        |

|         | D4<br>D5 | D3       | 2DH             | 1 | -    | 1            | 1        | 1        |          |          |          |     |          | $\vdash$ |          | _   |      | -    | R46        | R30          | R19        | R3         | R44          | R        |

|         | D6       | D1       | 2EH             | 1 | F    | t            |          | 1        |          |          |          |     |          | -        |          |     |      |      | R47        | R31          | R18        | R2         | R43          | R        |

|         | D7       | D0       | 2FH             |   |      | L            | L        |          |          |          |          |     |          |          |          |     |      |      | R48        | R32          | R17        | R1         | R42          | R        |

|         | D0       | D7       | 30H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R49        | R33          | R16        |            | R41          | Rź       |

| ĺ       | D1       | D6       | 31H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R50        | R34          | R15        |            | R40          | Rź       |

| ĺ       | D2       | D5       | 32H             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R51        | R35          | R14        |            | R39          | Rź       |

| 0110    | D3       | D4       | 33H             |   | -    | 1            |          | L        |          |          |          |     | Page 6   |          |          |     |      |      | R52        | R36          | R13        |            | R38          | R        |

|         | D4       | D3       | 34H             | - | L    | ┡            | <u> </u> | <u> </u> |          |          |          |     | <b>J</b> | -        |          |     |      |      | R53        | R37          | R12        |            | R37          | R        |

|         | D5       | D2       | 35H             | - | -    | $\vdash$     | -        | -        | $\vdash$ |          |          |     |          | -        |          |     |      |      | R54        | R38          | R11        |            | R36          | R        |

|         | D6<br>D7 | D1<br>D0 | 36H<br>37H      | - | -    | $\vdash$     | -        | -        |          |          |          |     |          | $\vdash$ |          |     |      |      | R55<br>R56 | R39<br>R40   | R10<br>R9  |            | R35<br>R34   | R'<br>R' |

|         | D7<br>D0 | D0       | 37H<br>38H      | - | ⊢    | ┢            | ┝        | ⊢        | $\vdash$ | $\vdash$ | -        | -   |          | ┢        | $\vdash$ | _   |      | _    | R56        | R40<br>R41   | R9<br>R8   |            | R34<br>R33   | R        |

| ł       | D0       | D7<br>D6 | 39H             | 1 | -    | $\mathbf{T}$ |          |          |          |          |          |     |          | -        |          | _   |      | -    | R58        | R42          | R7         |            | R32          | R        |

|         | D2       | D5       | 3AH             | 1 | F    | $\mathbf{t}$ | 1        | 1        |          |          |          |     |          | $\vdash$ |          | _   |      | -    | R59        | R43          | R6         |            | R31          | R        |

| 0114    | D3       | D0       | 3BH             | 1 |      | 1            |          | 1        |          |          |          |     | Dorrs 7  | -        |          |     |      |      | R60        | R44          | R5         |            | R30          | R        |

| 0111    | D4       | D3       | 3CH             |   |      | Ĺ            | L        |          |          |          |          |     | Page 7   |          |          |     |      |      | R61        | R45          | R4         |            | R29          | R        |

|         | D5       | D2       | 3DH             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R62        | R46          | R3         |            | R28          | R        |

| į       | D6       | D1       | 3EH             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R63        | R47          | R2         |            | R27          | R        |

|         | D7       | D0       | 3FH             |   |      |              |          |          |          |          |          |     |          |          |          |     |      |      | R64        | R48          | R1         |            | R26          | R        |

| 1000    | D0       | D7       | 40H             |   |      |              |          |          |          |          |          |     | Page 8   |          |          |     |      |      | RIC        | RIC          | RIC        | RIC        | RIC          | RI       |

|         |          |          |                 |   | _    | -            | -        | -        | -        | -        | -        | -   |          | -        | _        |     | _    |      |            |              | 65         | 49         | 65           |          |

|         |          |          |                 | 0 | 8    | ū            | 8        | ខ        | 2        | C5       | 8        | C1  |          | C97      | C98      | C99 | C100 | C101 |            |              |            | M          | UX           |          |

|         |          |          | XM              |   |      |              |          |          |          |          |          |     |          | 0        | 0        | 0   | C    | C    |            |              |            |            |              |          |

|         |          |          |                 |   | C101 | C100         | C 99     | C98      | C97      | C96      | C95      | C94 |          | 2        | C        | ß   | C1   | 8    |            |              |            |            |              |          |

65x102 Matrix LCD Controller-Drivers

#### **MX** IMPLEMENTATION

Column Mirroring (MX) is implemented by selecting either (CA) or (101–CA) as the RAM column address. Changing MX affects the data written to the RAM.

Since MX has no effect of the data already stored in RAM, changing MX does not have immediate effect on the displayed pattern. To refresh the display, refresh the data stored in RAM after setting MX.

#### DISPLAY SCANNING

During each field of display, depends on the setting of MR, row electrodes will be scanned in a fixed pattern at a rate of

(80 x Mux Rate) rows/second.