# R8A66174SP PARALLEL-IN SERIAL-OUT DATA BUFFER WITH FIFO

REJ03F0278-0101 Rev. 1.01 Oct.06.2008

#### DESCRIPTION

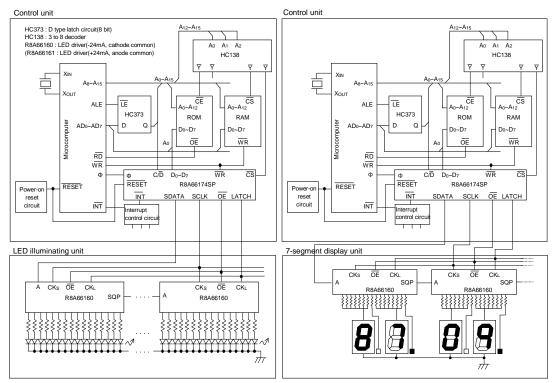

The R8A66174 is a CMOS LSI with 63-byte FIFO (First-In First-Out Memory). The commands or up to 63-bytes data can be stored from 8-bit data bus. The data stored in FIFO can be outputted as serial data by executing command, and when the stored data is outputted all, R8A66174 will output an interrupt request signal. R8A66174 has 2-bit output pins (/OE, LATCH) which can set/reset outside devices by the command, R8A66174 can be connected to peripheral circuits that have a serial latch structure. R8A66174 is the succession product of M66300.

#### **FEATURES**

- General-purpose 8-bit CPU bus compatible

- Built-in 63-byte FIFO

- High-speed output (10Mbps)

- It's able to connect to LED array driver such as R8A66160 or R8A66161 directly

- Low-noise, high-output circuit IOL=16mA, IOH=-16mA (IOL=4mA, IOH=-4mA for /INT)

- Schmitt input (/RESET)

- Wide operating supply voltage range (Vcc=3.0~3.6V or Vcc=4.5~5.5V)

- Wide operating temperature range (Ta=-40~85°C)

#### **APPLICATION**

General digital equipment for industrial and home use, panel display controllers, and eraser unit controller for copying machine.

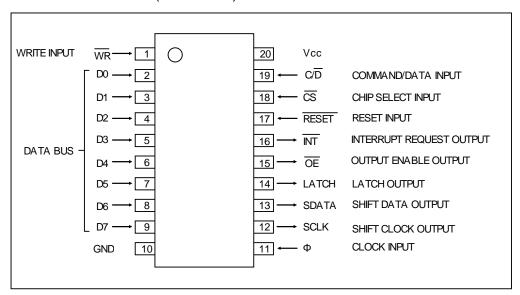

#### PIN CONFIGURATION (TOP VIEW)

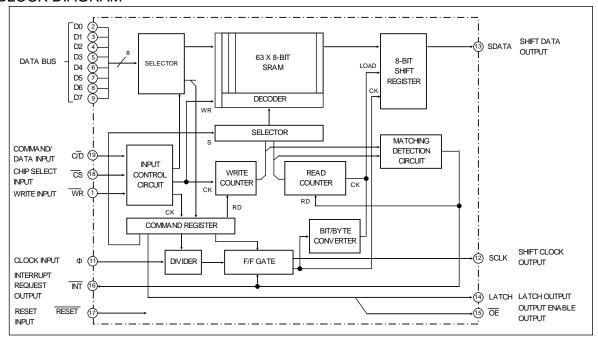

# **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

The information on data bus D0~D7 is loaded as command when C//D=1, and as data when C//D=0. There are four kinds of commands.

- (1) Command 1. Five kinds of division ratios of the clock input  $\Phi$  are set up.

- (2) Command 2. R8A66174 is set as write mode. The CPU is capable of writing 8-bit parallel data of up to 63 bytes into the internal memory (FIFO) of the R8A66174.

- (3) Command 3. R8A66174 is set as serial output mode. All data written in the internal memory (FIFO) is outputted as serial data in sync with the shift clock which is set by command 1. Then, each data is outputted from LSB. When all stored data has outputted, R8A66174 will output the interrupt request /INT to CPLI

- (4) Command 4. cancels the /INT and sets/resets the two control ports (LATCH, /OE).

After command4, if command3 is executed immediately, the data which is already written will be re-outputted.

#### **FUNCTION TABLE**

| Þ       |     |   |             |        |                |    | In | out |      |             |    |             |    |      | (     | Output | ts  |       |                          |                   |  |

|---------|-----|---|-------------|--------|----------------|----|----|-----|------|-------------|----|-------------|----|------|-------|--------|-----|-------|--------------------------|-------------------|--|

| Command |     | С | ontro       | l inpu | ts             |    |    |     | Data | inputs      | 3  |             |    | SCIK | SDATA | /INT   | /CE | LATCH | Rema                     | ark               |  |

| Con     | /I  | R | /CS         | C//D   | /WR            | D7 | D6 | D5  | D4   | D3          | D2 | D1          | D0 | SOLK | SDATA | /1111  | /OL | LATOI |                          |                   |  |

| _       | (   | 0 | ×           | ×      | ×              | ×  | ×  | ×   | ×    | ×           | ×  | ×           | ×  | 0    | 0     | 1      | 1   | 0     | Initialize               |                   |  |

| _       | 1   | 1 | 1           | ×      | ×              | ×  | ×  | ×   | ×    | ×           | ×  | ×           | ×  | * 1  | * 1   | * 1    | * 2 | * 2   | Memory contents not ch   | nanged            |  |

|         | 1   | 1 | 0           | 1      | <u>ا</u> حا    | 1  | 0  | 0   | 0    | ×           | ×  | ×           | ×  | 0    | 0     | 1      |     |       | Φ                        |                   |  |

|         |     |   |             |        |                | 1  | 0  | 0   | 1    |             |    |             |    | 0    | 0     | 1      |     |       | 1/2 division of Φ V      | alid when D7 is   |  |

| 1       | П   |   |             |        |                | 1  | 0  | 1   | 0    |             |    |             |    | 0    | 0     | 1      |     |       | 1/4 division of Φ h      | high-level        |  |

|         | П   |   |             |        |                | 1  | 0  | 1   | 1    |             |    |             |    | 0    | 0     | 1      |     |       | 1/8 division of Φ        |                   |  |

|         | П   |   |             | _ ↓    | ₩              | 1  | 1  | 0   | 0    | <b>&gt;</b> | ₩  | <b>&gt;</b> | \  | 0    | 0     | 1      |     |       | 1/16 division of Φ       |                   |  |

| 2       | Ш   |   |             | 1      | <sup> </sup> < | 0  | ×  | ×   | ×    | 0           | ×  | ×           | 0  | 0    | 0     | 1      |     |       | WRITE MODE setting       | WRITE MODE        |  |

|         | П   |   |             | 0      | <sup> </sup> < | ×  | ×  | ×   | ×    | ×           | ×  | ×           | ×  | 0    | 0     | 1      |     |       | WRITE operation          | WRITE WODE        |  |

|         | Ш   |   | <b>&gt;</b> | 1      | <u> </u>       | 0  | ×  | ×   | ×    | 0           | ×  | ×           | 1  | * 3  | * 4   | 1      |     |       | SERIAL OUT MODE setting  |                   |  |

| 3       | П   |   | * 5         | ×      | ×              | ×  | ×  | ×   | ×    | ×           | ×  | ×           | ×  | * 3  | * 4   | 1      |     |       | SERIAL OUT               | SERI. OUT<br>MODE |  |

|         |     |   | * 5         | ×      | ×              | ×  | ×  | ×   | ×    | ×           | ×  | ×           | ×  | 0    | 0     | 0      | →   | ₩     | SERIAL OUT end           |                   |  |

| 4       | \ \ | ' | 0           | 1      | 1              | 0  | ×  | ×   | ×    | 1           | D2 | D1          | ×  | 0    | 0     | 1      | D2  | D1    | set/reset the /OE and L/ | ATCH, cancel /INT |  |

Note1 \*1 : The same operation as \*3 and \*4 in the SERIAL OUT mode. The output is not changed in other modes.

- \*2 : The output is not changed.

- \*3 : The Φ division pulse which is set by command 1 is outputted on /WR rise.

- \*4 : SDATA (n) is output on SCLK fall (n-1).

- \*5 : Indicates 1 when /WR is 0, don't care when /WR is 1.

- X : Don't care

#### **BASIC OPERATION**

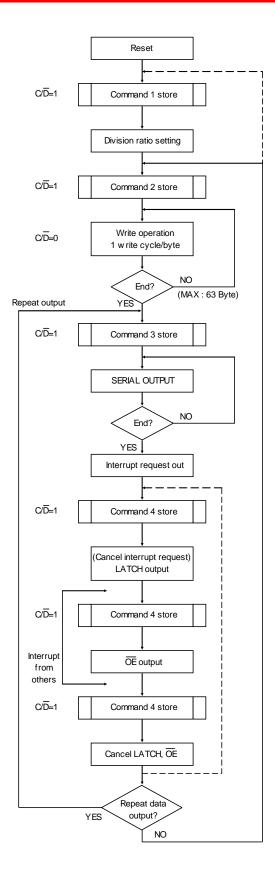

Fig. 1 shows the basic operation flowchart. Data inputs D0~D7 are switched among four commands and 8-bit parallel data by the C//D signal. When C//D is 1, the command is stored in sync with the rise of /WR.

For initiate to work this IC, at first command 1 should be stored. Command 1 sets the division ratio for clock input  $\Phi$  as 5 divisions of 1, 1/2, 1/4, 1/8 and 1/16. (The default ratio is 1.)

Then command 2 should be stored. When it is stored, 8-bit parallel data is written into the internal memory (FIFO) on the write cycle of the CPU. The maximum capacity of its FIFO is 63 bytes.

When the write operation has done, command 3 should be stored. For this action, all data in the internal memory is outputted as serial data (SDATA) in sync with the shift clock (SCLK output) which is set by command 1. Then, each data is outputted from LSB.

The SDATA changes on the fall of SCLK. When it finishes to output data, an interrupt request /INT is outputted to the CPU.

/INT is canceled by command 4 or command 2 and command 3. The command 4 sets/resets two control ports (LATCH, /OE) as well as canceling /INT. If command 3 is executed without executing command 2 after command 4, the already written-in data can be re-outputted. If it is not required to re-output the previous data, please execute command 2 before command 3 will be executed.

#### <Attention>

In spite of having stored write mode by command 2, when serial out mode is stored by command 3, without writing any parallel data to an internal memory (FIFO), an incorrect output appears in SDATA, SCLK, and /INT.

Please be careful.

(command 2 store ⇒ data is not written ⇒ command 3 store : Please avoid such usage. )

Fig. 1 Flowchart (Basic operation)

### PIN DESCRIPTION

| Pin name                       | Function                                                                                                                                                                                                                               |  |  |  |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| /RESET(Reset input)            | When this is low-level, it clears the command and shift register and initializes the address of the internal memory (FIFO).                                                                                                            |  |  |  |  |  |

| Φ(Clock input)                 | When the frequency of clock input $\Phi$ is fo,the frequency f of shift clock output SCLK is given by the following equation.                                                                                                          |  |  |  |  |  |

|                                | $f = (1/n) \cdot fo  (n = 1, 2, 4, 8, 16)$                                                                                                                                                                                             |  |  |  |  |  |

| /CS(Chip select input)         | When this is low-level, communication between the R8A66174 and the CPU becomes possible. When this is high-level, data from the CPU is ignored. However, data in the internal memory is maintained.                                    |  |  |  |  |  |

| C//D(Command/data input)       | The information on D0~D7 is regarded as commands when this is high-level and is regarded as data when this is low-level.                                                                                                               |  |  |  |  |  |

| /WR(Write input)               | On /WR rise, a command from the CPU is written into the command register and data is written into the internal memory. This input generates the serial data start signal, cancels /INT, and sets the 2-bit control ports (LATCH, /OE). |  |  |  |  |  |

| SCLK(Shift clock output)       | The clock frequency is determined by D6~D4 when D7 is 1, as shown in Table 3 and Fig.2. Clock output starts on /WR rise of command 3.                                                                                                  |  |  |  |  |  |

| SDATA(Shift data output)       | All data written in the internal memory are output as serial data in sync with the SCLK.                                                                                                                                               |  |  |  |  |  |

| /INT(Interrupt request output) | When output of all data in the internal memory ends, a low-level signal is output.                                                                                                                                                     |  |  |  |  |  |

| LATCH(Latch output)            | These two outputs are set/reset by command 4 on /WR rise. The signal was named after the IC                                                                                                                                            |  |  |  |  |  |

| /OE(Output enable output)      | connected in the next stage, but it can be used freely for other applications.                                                                                                                                                         |  |  |  |  |  |

#### **INSTRUCTION SET**

Four commands can be set by the 8-bit command words from the CPU.

Table 2 Command setting

| Command            | Command word                       | Function                                                      | Remark  |  |

|--------------------|------------------------------------|---------------------------------------------------------------|---------|--|

| 1                  | 80 <sub>16</sub> ~C0 <sub>16</sub> | Division ratio setting                                        | Note2   |  |

| 2                  | 00 <sub>16</sub>                   | Write mode from the CPU to the internal memory is set.        | Note 2  |  |

| 3 01 <sub>16</sub> |                                    | Data output mode from the internal memory (FIFO) is set.      | Note3   |  |

| 4                  | 08 <sub>16</sub> ∼0F <sub>16</sub> | Cancels the /INT and sets the two control ports (LATCH, /OE). | Note3,4 |  |

Note 2: Low er byte can be 0~F.

3 : Upper byte can be 1∼7. 4 : /INT can also be canceled by command 2 or command 3.

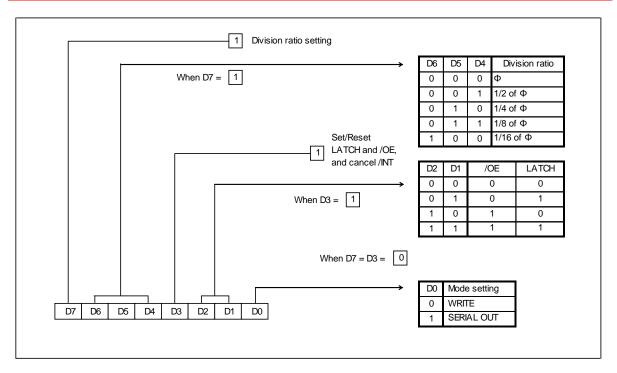

Fig. 2 shows the method for determining the command word for the instruction set. When D7 is 1, D3~D0 are masked and when D3 is 1, D0 is masked.

Table 3 Division ratio setting

| D7~D4 | Division  |

|-------|-----------|

| 8     | Φ         |

| 9     | 1/2 of Φ  |

| Α     | 1/4 of Φ  |

| В     | 1/8 of Φ  |

| С     | 1/16 of Φ |

Table 4 /OE, LATCH setting

| rable 1702; 27ti 011 cotting |        |       |                   |  |  |  |  |  |  |  |

|------------------------------|--------|-------|-------------------|--|--|--|--|--|--|--|

| D3~D0                        | /OE    | LATCH | /INT cancellation |  |  |  |  |  |  |  |

| 8, 9                         | 8, 9 0 |       | It is canceled    |  |  |  |  |  |  |  |

| A, B                         | 0      | 1     |                   |  |  |  |  |  |  |  |

| C, D                         | 1      | 0     |                   |  |  |  |  |  |  |  |

| E, F                         | 1      | 1     | ] ↓               |  |  |  |  |  |  |  |

Fig. 2 Instruction set

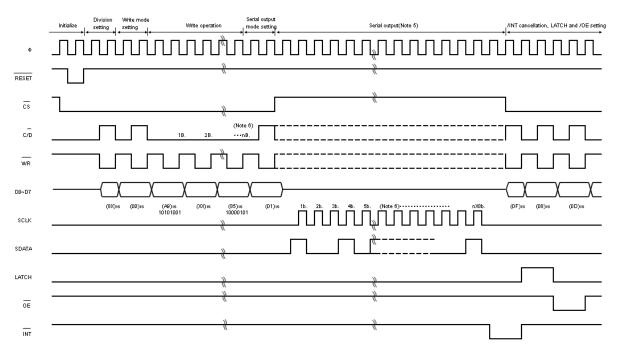

#### **EXAMPLE OF TIME CHART**

Note 5 : Always maintain AVR at high-level when ICS is low-level.

- 7: 0 need not be the CPU signal. (Φ and MR need not be synchronous.)

8: Φ indicates the value when division ratio is set 1. If the division ratio is other than 1, a similar time chart is obtained if Φ is regarded as the waveform divided.

#### ABSOLUTE MAXIMUM RATINGS

| Symbol | Parameter           | Conditions | Ratings      | Unit |

|--------|---------------------|------------|--------------|------|

| Vcc    | Supply voltage      |            | -0.5~+7.0    | V    |

| Vı     | Input voltage       |            | -0.5~Vcc+0.5 | V    |

| Vo     | Output voltage      |            | -0.5~Vcc+0.5 | V    |

| Pd     | Power dissipation   |            | 500          | mW   |

| Tstg   | Storage temperature |            | -65~150      | °C   |

#### RECOMMENDED OPERATING CONDITIONS (Ta=-40~85°C)

| Symbol | Parameter                   |                            |     | Limits |     |      |  |

|--------|-----------------------------|----------------------------|-----|--------|-----|------|--|

| Symbol | Falametei                   |                            |     | Тур    | Max | Unit |  |

| Vcc    | Supply voltage              | 5.0V                       | 4.5 | 5.0    | 5.5 | V    |  |

| VCC    | Supply voltage              | 3.3V                       | 3.0 | 3.3    | 3.6 | V    |  |

| GND    | Supply voltage              |                            |     | 0      |     | V    |  |

| VI     | Input voltage               |                            | 0   |        | Vcc | V    |  |

| Vo     | Output voltage              | 0                          |     | Vcc    | V   |      |  |

| Topr   | Operating temperature range | perating temperature range |     |        | 85  | °C   |  |

# **ELECTRICAL CHARACTERISTICS**

■ 5.0V version support specifications (Ta=-40~85°C, Vcc=4.5~5.5V)

| Cumbal | Parameter             |                     | Test conditions                        |          | Limits |          |      |  |

|--------|-----------------------|---------------------|----------------------------------------|----------|--------|----------|------|--|

| Symbol |                       | Parameter           | l est conditions                       | Min      | Тур    | Max      | Unit |  |

| VIH    | High-level input volt | tage                | Inputs except /RESET                   | 0.75XVcc |        |          | V    |  |

| VIL    | Low-level input volta | age                 | Inputs except /RESET                   |          |        | 0.25XVcc | V    |  |

| VT+    | Positive input thres  | hold voltage        |                                        | 0.35XVcc |        | 0.8XVcc  | V    |  |

| VT-    | Negative input thres  | shold voltage       | /RESET                                 | 0.2XVcc  |        | 0.65XVcc | V    |  |

| VH     | Hysteresis width      |                     |                                        | 0.4      |        |          | V    |  |

| Vou    | High-level output     | /INT                | IOH=-4mA                               | Vcc-0.8  |        |          | V    |  |

| Vон    | voltage               | Outputs except /INT | IOH=-16mA                              | Vcc-0.8  |        |          | V    |  |

| Vol    | Low-level output      | /INT                | IOL=4mA                                |          |        | 0.53     | V    |  |

| VOL    | voltage               | Outputs except /INT | IoL=16mA                               |          |        | 0.53     | V    |  |

| Icc    | Supply current        |                     | V <sub>I</sub> =V <sub>CC</sub> or GND |          |        | 50       | mA   |  |

| Iн     | High-level input cur  | rent                | Vi=Vcc                                 |          |        | +1       | μA   |  |

| I⊫     | Low-level input curr  | ent                 | VI=0V                                  |          |        | -1       | μA   |  |

■ 3.3V version support specifications(Ta=-40~85°C, Vcc=3.0~3.6V)

| Symbol |                                                                                 | Parameter           | Test conditions      |          | Limits |          |      |  |

|--------|---------------------------------------------------------------------------------|---------------------|----------------------|----------|--------|----------|------|--|

| Symbol |                                                                                 | Falameter           | rest conditions      | Min      | Тур    | Max      | Unit |  |

| VIH    | High-level input volt                                                           | tage                | Inputs except /RESET | 0.75XVcc |        |          | V    |  |

| VIL    | Low-level input voltage                                                         |                     | Inputs except /RESET |          |        | 0.25XVcc | V    |  |

| VT+    | Positive input threshold voltage                                                |                     |                      | 0.35XVcc |        | 0.8XVcc  | V    |  |

| VT-    | Negative input thres                                                            | shold voltage       | /RESET               | 0.2XVcc  |        | 0.65XVcc | V    |  |

| Vн     | Hysteresis width                                                                |                     |                      | 0.4      |        |          | V    |  |

| Vон    | High-level output                                                               | /INT                | Iон=-2mA             | Vcc-0.4  |        |          | V    |  |

| VOH    | voltage                                                                         | Outputs except /INT | Iон=-2mA<br>Iон=-8mA | Vcc-0.6  |        |          | V    |  |

| Vol    | Low-level output                                                                | /INT                | IoL=2mA              |          |        | 0.4      | V    |  |

| VOL    | voltage Outputs except /INT  Low-level output /INT  voltage Outputs except /INT | IOL=8mA             |                      |          | 0.5    | V        |      |  |

| Icc    | Supply current                                                                  | -                   | VI=Vcc or GND        |          |        | 50       | mA   |  |

| IIH    | High-level input cur                                                            | rent                | VI=Vcc               |          |        | +1       | μΑ   |  |

| I∟     | Low-level input curr                                                            | ent                 | Vi=0V                |          |        | -1       | μA   |  |

Note 9: The current flowing into the IC is positive (no sign).

# TIMING REQUIREMENTS (Ta=-40~85°C, Vcc=4.5~5.5V or 3.0~3.6V)

| Symbol        | Parameter                       | Test condition | Limits for 5.0V |     |     | L   | Unit |     |      |

|---------------|---------------------------------|----------------|-----------------|-----|-----|-----|------|-----|------|

| Symbol        | ,                               |                | Min             | Тур | Max | Min | Тур  | Max | Unit |

| tw(Φ)         | Clock pulse width               |                | 50              |     |     | 60  |      |     | ns   |

| tw(/W)        | Write pulse width               |                | 100             |     |     | 120 |      |     | ns   |

| tw(/R)        | Reset pulse width               |                | 100             |     |     | 120 |      |     | ns   |

| tsu(D-/W)     | Data setup time before write    | 1              | 50              |     |     | 60  |      |     | ns   |

| th(/W-D)      | Data hold time after write      | 1              | 0               |     |     | 0   |      |     | ns   |

| tsu(A-/W)     | Address setup time before write | 1              | 0               |     |     | 0   |      |     | ns   |

| th(/W-A)      | Address hold time after write   |                | 0               |     |     | 0   |      |     | ns   |

| trec(/W)      | Write recovery time             |                | 100             |     |     | 120 |      |     | ns   |

| trec(/INT-/W) | Write recovery time after /INT  |                | 100             |     |     | 120 |      |     | ns   |

| trec(/R-/W)   | Write recovery time after reset |                | 100             |     |     | 120 |      |     | ns   |

Note 10 : Increase of the input rise time (tr) and fall time (tf) of clock input  $\Phi$  may cause misoperation.

# SWITCHING CHARACTERISTICS(Ta=-40~85°C, Vcc=4.5~5.5V or 3.0~3.6V)

| Symbol        | Parameter T                                                        | Test condition | L   | imits for 5.0 | V       | L   | 単位  |         |     |

|---------------|--------------------------------------------------------------------|----------------|-----|---------------|---------|-----|-----|---------|-----|

| Symbol        | Farameter                                                          | rest condition | Min | Тур           | Max     | Min | Тур | Max     | 单位  |

| tc(Φ)         | Clock Cycle                                                        |                | 100 |               |         | 120 |     |         | ns  |

| tPLH(/W-/INT) | Propagation time between write and /INT                            | CL=50pF        |     |               | 100     |     |     | 120     | ns  |

| tplh(/R-/INT) | Propagation time between /RESET and /INT                           | CL=30pr        |     |               | 100     |     |     | 120     | ns  |

| tPLH(/W-/OE)  | Propagation time between write and /OE                             |                |     |               | 100     |     |     | 120     | ns  |

| tPHL(/W-/OE)  | Propagation time between write and /OE                             |                |     |               | 100     |     |     | 120     | ns  |

| tPLH(/W-LA)   | Propagation time between write and LATCH                           |                |     |               | 100     |     |     | 120     | ns  |

| tphl(/W-LA)   | Propagation time between write and LATCH                           |                |     |               | 100     |     |     | 120     | ns  |

| tplh(/W-SC)   | Propagation time between write and SCLK                            |                | 1xT | _             | 2×T+100 | 1xT | _   | 2xT+120 | ns  |

| tplh(Φ-SC)    | Propagation time between Φ and SCLK                                | CL=150pF       |     |               | 100     |     |     | 120     | ns  |

| tplh(Φ-SD)    | Propagation time between Φ and SDATA                               |                |     |               | 100     |     |     | 120     | ns  |

| tphl(Φ-SD)    | Flopagation time between $\Phi$ and 3DATA                          |                |     |               | 100     |     |     | 120     | ns  |

| tphl(Φ-/INT)  | Propagation time between Φ and /INT                                |                |     |               | 100     |     |     | 120     | ns  |

| tPLH(/R-/OE)  | Propagation time between /RESET and /OE                            |                |     |               | 100     |     |     | 120     | ns  |

| tphl(/R-LA)   | Propagation time between /RESET and LATCH                          |                |     |               | 100     |     |     | 120     | ns  |

| tтьн          | Low to high level output transition time (/INT)                    | CL=50pF        |     |               | 25      |     |     | 30      | ns  |

| tthl          | High to low level output transition time (/INT)                    | CL=30pr        |     |               | 25      |     |     | 30      | ns  |

| tтьн          | Low to high level output transition time                           |                |     |               | 25      |     |     | 30      | ns  |

| LILH          | (SCLK, SDATA, /OE, LATCH)                                          | CL=150pF       |     |               | 25      |     |     | 30      | 115 |

| tтнL          | High to low level output transition time (SCLK, SDATA, /OE, LATCH) | OL=150pF       |     |               | 25      |     |     | 30      | ns  |

Note 11 : T=(1/Φ)×(1/division ratio) [ns]

12 : AC test waveform

Input pulse level 0~Vcc

Input pulse rise time 6ns

Input pulse fall time 6ns

Reference voltage

Input voltage 0.5XVcc

Output voltage 0.5XVcc

tr, tf: These are recommended to be 20ns or less.

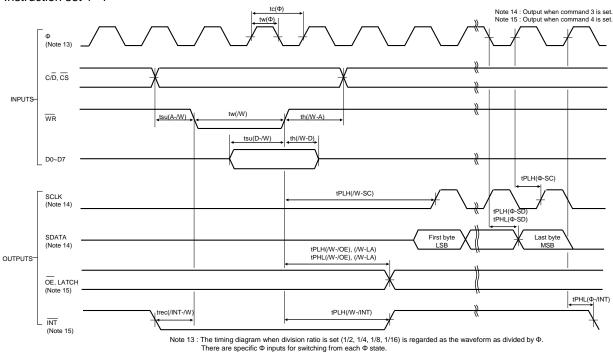

#### **TIMING DIAGRAM**

#### Instruction set 1~4

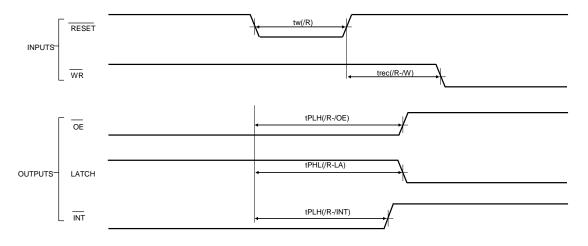

# Timing diagram when RESET

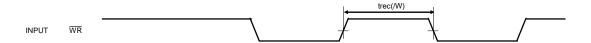

WR recovery time other than data reading

Fig. 3 Application example 1(PPC copying machine eraser circuit)

Fig. 4 Application example 2(Panel display circuit)

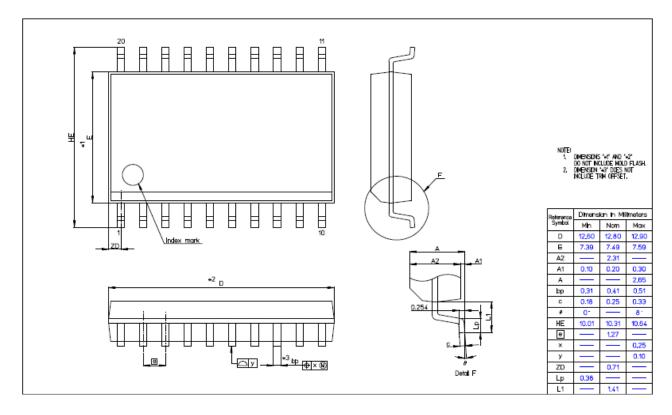

# PACKAGE OUTLINE

| Package   | RENESAS Code | Previous Code |

|-----------|--------------|---------------|

| 20pin SOP | PRSP0020DG-A | 20P2X-C       |

All trademarks and registered trademarks are the property of their respective owners.

#### Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

otes:

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document. Renesas shall have no liability for damages or infringement of any intellectual property or other nights arising out of the use of any information in this document, including, But not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to the disclosed by Renesas such as that disclosed through our website, (http://www.renesas.com.)

Renesas has used reasonable care in compliting the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

When using or otherwise relying on the information in this document.

When using or otherwise relying on the information in this document.

When using or otherwi

Notwithstanding the preceding paragraph, you should not use native as products provided the products described herein within the range specified by Renesas shall have no liability for damages arising out of the use set of the in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction revention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software aswallowing by infaints and small children is very high. You should implement safety measures products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

Please contact a Renesas se

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510