# RENESAS

## R8A66152SP

12-BIT I/O EXPANDER WITH LED DRIVE FUNCTION

REJ03F0259-0100 Rev. 1.00 Jan.9.2008

## DESCRIPTION

R8A66152 is a semiconductor integrated circuit which has 12-bit shift register function to execute serial in - parallel out conversion and parallel in - serial out conversion.

Built in two shift registers for serial in - parallel out and parallel in - serial out are constructed independently, This IC is able to read serial input data into a shift register while output the serial data converting from the parallel data input.

Also, parallel data I/O pins can be set to input mode or output mode by a bit.

R8A66152 is useful in a wide range of applications, such as MCU (micro controller unit) I/O port extension and serial bus system data communication.

Moreover, R8A66152 can be used as the anode common LED drive, too.

## FEATURES

- Bi-directional serial communication with MCU

- Serial data can be input during parallel to serial data conversion

- Parallel data I/O pins can be set input mode or output mode by a bit

- Schmitt input (DI, CLK, /S, /CS)

- N-ch open drain output (DO, D1~D12).

High output current IoL=24mA (at VCC=4.5V), IoL=15mA (at VCC=3.0V)

- Parallel data I/O pins (D1~D12)

- Wide supply voltage range (Vcc=2.0 to 6.0V)

- Wide operating temperature range (Ta=-40 to 85°C)

## APPLICATION

- Serial parallel or parallel serial data conversion for MCU peripheral.

- Serial bus control by MCU.

- LED array drive, The various LED display modules.

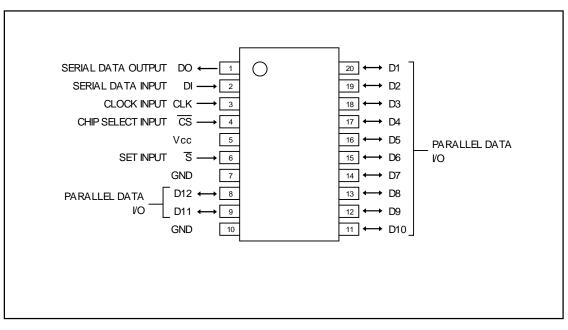

## PIN CONFIGURATION (TOP VIEW)

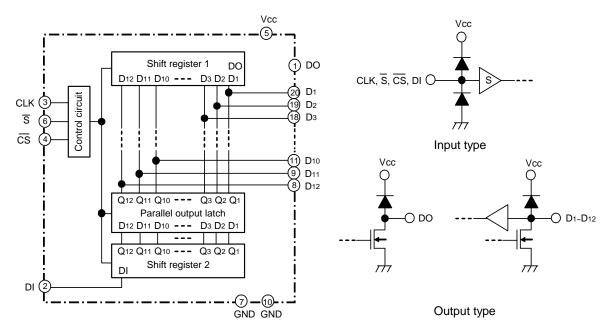

## **BLOCK DIAGRAM**

## FUNCTION

The R8A66152 is produced by using the silicon gate CMOS technology and has low power dissipation and high noise margin.

Built in two shift registers for serial in-parallel out (Shift register 2) and parallel in-serial out (Shift register 1) are constructed independently, R8A66152 is able to read serial input data into a shift register while output the serial data converting from the parallel data input.

Serial output operation of 12-bit parallel latched data and serial input operation from MCU are started when /CS is changed from "H" to "L".

12-bits parallel data are latched by the negative edge of /CS and are output from the DO terminal synchronously to the negative edge of CLK, and also the DI terminal read serial input data from MCU and are written into the internal shift register 2.

The 13th and following shift clock pulse are ignored and serial input data is masked, and DO terminal becomes high-impedance ("High-Z").

When /CS is changed from "L" to "H", 12-bits serial data which is read from the DI terminal are output to the D1~D12 terminals as parallel data.

As the output circuit type of D1~D12 terminals is N-ch open drain output, write data "H" for pins which should be set to input mode.

### DESCRIPTION OF OPERATION

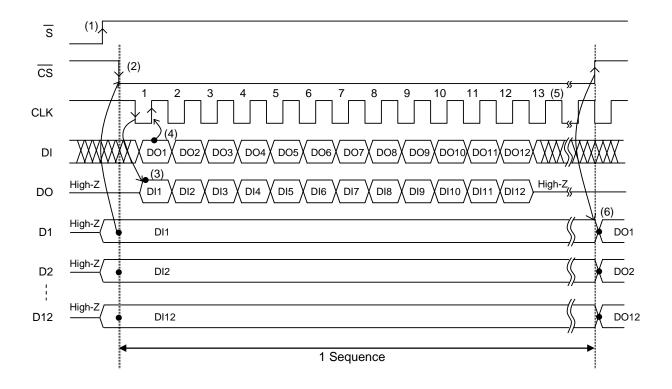

- (1) When power ON, the status of DO and D1~D12 terminals are not determined. These terminals are turn to high-impedance when "L" is input to the /S terminal.

- (2) By the negative edge of /CS, the status of D1~D12 terminals is loaded on shift register 1.

- (3) Synchronous to the negative edge of CLK, 12-bit loaded data is serial output from the DO terminal.

- (4) Synchronous to the positive edge of CLK, 12-bit serial input data from DI is write into the shift register 2.

- (5) The 13th and following shift clock pulse are ignored and the serial data input operation is stopped. And the DO terminal becomes high-impedance ("High-Z").

- (6) By the positive edge of /CS, input data described in (4) is output to D1~D12 terminals.

- (7) Shift register 1 loads the AND tie data of external parallel input data and latched data on parallel output latch.

- (8) If the /CS is changed from "L" to "H" before reaches the 12th bit of CLK, parallel output latch latches data which has been written on shift register 2 and output it to D1~D12 terminals. Serial data after this since is ignored and the DO terminal becomes high-impedance.

- (9) Input/output mode set to D1~D12 terminals is done by the serial input data to the DI terminal. Terminals which "H" is written are set to input, and "L" is written are set to output.

## **OPERATION TIMING CHART**

## ABSOLUTE MAXIMUM RATINGS

(Ta=-40~85°C, unless otherwise noted)

| Symbol | Parameter                     | Conditions | Ratings        | Unit |

|--------|-------------------------------|------------|----------------|------|

| VCC    | Supply voltage                |            | -0.5 ~ +7.0    | V    |

| VI     | Input voltage                 |            | -0.5 ~ Vcc+0.5 | V    |

| Vo     | Output voltage                |            | -0.5 ~ Vcc+0.5 | V    |

| ю      | Output current per output pin |            | 50             | mA   |

| ICC    | Supply / GND current          | VCC, GND   | 385            | mA   |

| Pd     | Power dissipation             | (Note)     | 500            | mW   |

| Tstg   | Storage temperature range     |            | -65 ~ 150      | °C   |

Note: R8A66152SP: Ta=-40 ~ +70°C. Ta=70 ~ 85°C are derated at -10 mW / °C

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol | Parameter                   |      | Unit |      |      |

|--------|-----------------------------|------|------|------|------|

| Symbol | Falameter                   | Min. | Тур. | Max. | Onit |

| Vcc    | Supply voltage              | 2.0  |      | 6.0  | V    |

| VI     | Input voltage               | 0    |      | Vcc  | V    |

| VO     | Output voltage              | 0    |      | Vcc  | V    |

| Topr   | Operating temperature range | -40  |      | 85   | °C   |

## ELECTRICAL CHARACTERISTICS (Vcc=2.0~6.0V, Ta=-40~85°C, unless otherwise noted)

| Symbol | Parameter                             | Test cor                         | aditiona |                | Limits |            | Unit |  |

|--------|---------------------------------------|----------------------------------|----------|----------------|--------|------------|------|--|

| Symbol | Faiametei                             | Test cor                         | IUILIONS | Min. Typ. Max. |        | Max.       | Unit |  |

| VT+    | Positive going threshold voltage (*1) |                                  |          | 0.35 x Vcc     |        | 0.80 x Vcc | V    |  |

| VT-    | Negative going threshold voltage (*1) | Vo=0.1V, Vcc-0.1V<br>I lo l=20uA |          | 0.20 x Vcc     |        | 0.65 x Vcc | V    |  |

| VIH    | "H" input voltage (*2)                |                                  |          | 0.75 x Vcc     |        |            | V    |  |

| VIL    | "L" input voltage (*2)                |                                  |          |                |        | 0.25 x Vcc | V    |  |

| VOL    | "L" output voltage                    | VI=VT+,VT-<br>Vcc=4.5V           | IOL=24mA |                |        | 0.5        | V    |  |

|        |                                       | VI=VT+,VT-<br>Vcc=3.0V           | IOL=15mA |                |        | 0.5        | V    |  |

| 10     | Output lookage ourrept                | Vcc=6V                           | Vo=Vcc   |                |        | 10         | uA   |  |

| 10     | Output leakage current                | VCC=0V                           | Vo=GND   |                |        | -10        | uA   |  |

| IIH    | "H" input current                     | VI=Vcc, Vcc=6V                   |          |                |        | 1          | uA   |  |

| IIL    | "L" input current                     | VI=GND, Vcc=6V                   |          |                |        | -1         | uA   |  |

| lcc    | Quiescent supply current              | VI=Vcc, GND<br>Vcc=6V            |          |                |        | 100        | uA   |  |

\*1 : DI, CLK, /CS, /S

\*2 : D1~D12

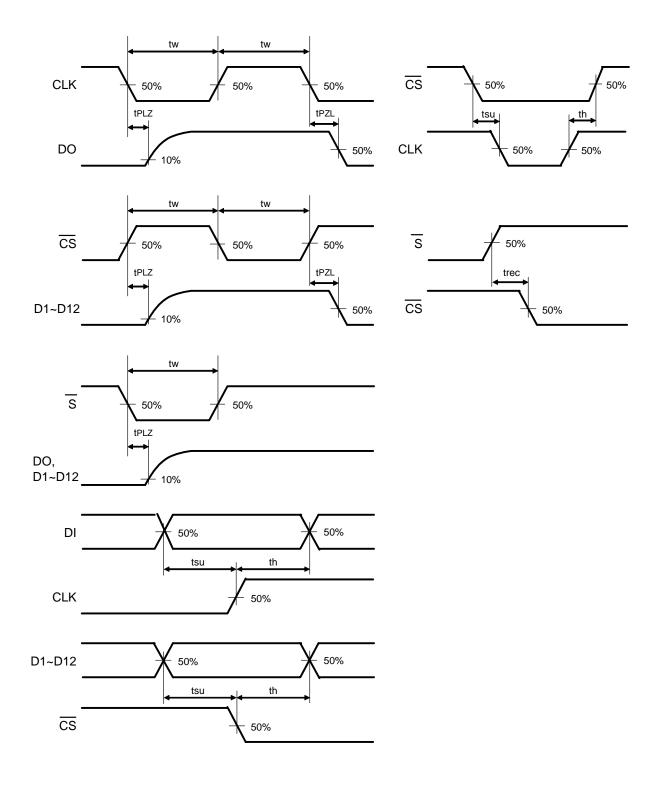

## SWITCHING CHARACTERISTICS

(Vcc=2.0~6.0V, Ta=-40~85°C, unless otherwise noted)

| Symbol | Parameter                                             | Test conditions | Limits |      |      | Unit |

|--------|-------------------------------------------------------|-----------------|--------|------|------|------|

| Symbol |                                                       |                 | Min.   | Тур. | Max. | Unit |

| fmax   | Maximum repeat frequency                              |                 |        |      | 1.9  | MHz  |

| tPLZ   | Output "L-Z" and "Z-L" propagation time               |                 |        |      | 400  | ns   |

| tPZL   | CLK - DO                                              | CL=50pF         |        |      | 400  | ns   |

| tPLZ   | Output "L-Z" and "Z-L" propagation time               | RL=1kΩ          |        |      | 400  | ns   |

| tPZL   | /CS - D1~D12                                          | (note1)         |        |      | 400  | ns   |

| tPLZ   | Output "L-Z" propagation time<br>/S - DO, /S - D1~D12 |                 |        |      | 400  | ns   |

### TIMING REQUIREMENTS

(Vcc=2.0~6.0V, Ta=-40~85°C, unless otherwise noted)

| Symbol | Parameter                   | Test conditions | Limits |      |      | Unit |

|--------|-----------------------------|-----------------|--------|------|------|------|

|        |                             | Test conditions | Min.   | Тур. | Max. | Unit |

| tw     | CLK, /CS, /S pulse width    |                 | 260    |      |      | ns   |

|        | Setup time of DI to CLK     |                 | 130    |      |      | ns   |

| tsu    | Setup time of /CS to CLK    |                 | 130    |      |      | ns   |

|        | Setup time of D1~D12 to /CS |                 | 130    |      |      | ns   |

|        | Hold time of DI to CLK      |                 | 130    |      |      | ns   |

| th     | Hold time of /CS to CLK     |                 | 130    |      |      | ns   |

|        | Hold time of D1~D12 to /CS  |                 | 130    |      |      | ns   |

| trec   | Recovery time of /CS to /S  |                 | 130    |      |      | ns   |

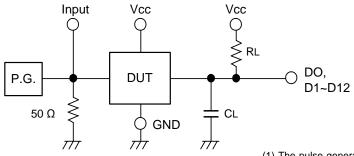

## NOTE1: TEST CIRCUIT

(1) The pulse generator (P.G.) has the following characteristics (10%~90%) tr=6ns, tf=6ns, Zo=50  $\Omega$

(2) The capacitance CL includes stray wiring capacitance and the probe input capacitance.

## TIMING DIAGRAM

REJ03F0259-0100 Rev.1.00 Jan.9.2008 Page 6 of 7

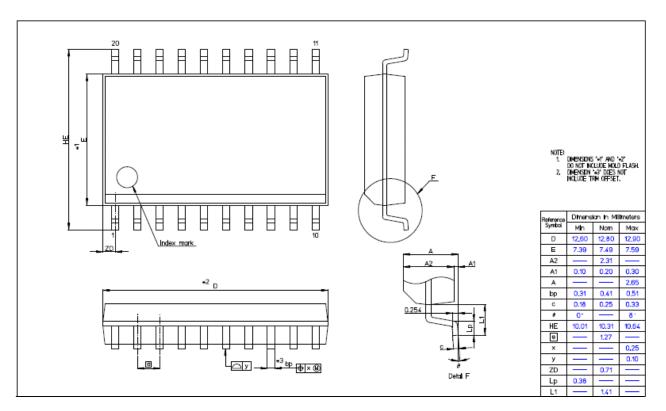

## PACKAGE OUTLINE

| Package   | RENESAS Code | Previous Code |

|-----------|--------------|---------------|

| 20pin SOP | PRSP0020DG-A | 20P2X-C       |

All trademarks and registered trademarks are the property of their respective owners.

### RenesasTechnology Corp. sales strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any infellectual property or completeness of the information contained in this document nor grants any license to any infellectual property or their rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application excute examples.

2. You should not use the products or the technology described in this document for the purpose of military applications such as the development of wasan degulations, and projectivomer sequence by such laws and regulations.

4. Adhormation inclust of any infectivation drag unified entities or guaranties inclusion accument, as of the data diagrams, charts, programs, algorithms, and application excut examples, is current as of the data the information in this document, busch, provide data, diagrams, that any information in the application excut examples, is current as of the data the information in this document, busch, provide data diagrams, that any information in the application excut examples, is current as of the data is disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

2. Renesas has used reasonable care in compiling the information in this document, but Renesas assoch as the disclosed through describing application and use of the information and additional system before deciding about the applications or otherwise in systems the failute to considering the underse state of the information in

### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com