CYM1838

# PRELIMINARY

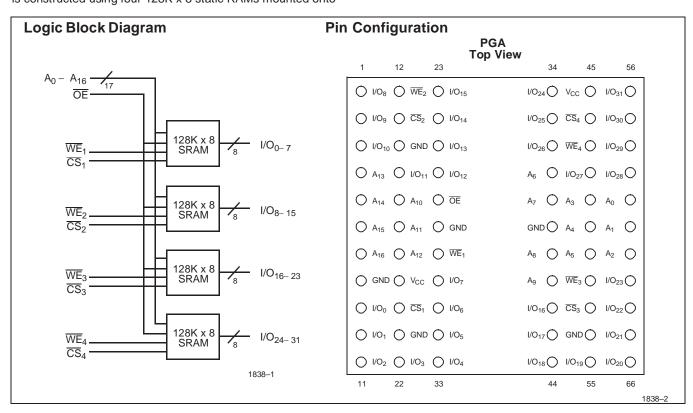

## 128K x 32 Static RAM Module

#### **Features**

- High-density 4-megabit SRAM module

- High-speed CMOS SRAMs

- Access time of 20 ns

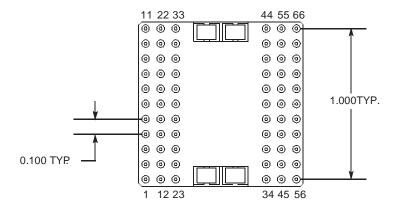

- 66-pin, 1.1-inch-square PGA package

- Low active power

- -4.0W (max.)

- Hermetic SMD technology

- . TTL-compatible inputs and outputs

- · Commercial and military temperature ranges

### **Functional Description**

The CYM1838 is a very high performance 4-megabit static RAM module organized as 128K words by 32 bits. The module is constructed using four 128K x 8 static RAMs mounted onto

a multilayer ceramic substrate. Four chip selects  $(\overline{CS}_1, \overline{CS}_2, \overline{CS}_3, \overline{CS}_4)$  are used to independently enable the four bytes. Reading or writing can be executed on individual bytes or any combination of multiple bytes through proper use of selects.

Writing to each byte is accomplished when the appropriate chip selects  $(\overline{CS})$  and write enable  $(\overline{WE})$  inputs are both LOW.Data on the input/output pins  $(I/O_\chi)$  is written into the memory location specified on the address pins  $(A_0$  through  $A_{16})$ .

Reading the device is accomplished by taking chip selects LOW while write enable remains HIGH. Under these conditions, the contents of the memory location specified on the address pins will appear on the data input/output pins.

The data input/output pins remain in a high-impedance state when write enable is LOW or the appropriate chip selects are HIGH.

#### **Selection Guide**

|                                |            | 1838-20 | 1838-25 | 1838-35 |

|--------------------------------|------------|---------|---------|---------|

| Maximum Access Time (ns)       |            | 20      | 25      | 35      |

| Maximum Operating Current (mA) | Commercial | 720     | 720     |         |

|                                | Military   | 720     | 720     | 720     |

| Maximum Standby Current (mA)   | Commercial | 240     | 240     |         |

|                                | Military   | 240     | 240     | 240     |

## **Maximum Ratings**

(Above which the useful life may be impaired.)

Storage Temperature ......-65°C to +150°C

Supply Voltage to Ground Potential ......-0.5V to +7.0V

DC Voltage Applied to Outputs

in High Z State ......-0.5V to +7.0V

DC Input Voltage .....-0.5V to +7.0V

## **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>CC</sub> |  |  |

|------------|------------------------|-----------------|--|--|

| Commercial | 0°C to +70°C           | 5V ± 10%        |  |  |

| Military   | –55°C to +125°C        | 5V ± 10%        |  |  |

## **Electrical Characteristics** Over the Operating Range

|                    |                                                     |                                                                                                                                                                                                                              | 1838 |      |      |

|--------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Parameter          | Description                                         | Test Conditions                                                                                                                                                                                                              | Min. | Max. | Unit |

| V <sub>OH</sub>    | Output HIGH Voltage                                 | $V_{CC} = Min., I_{OH} = -4.0 \text{ mA}$                                                                                                                                                                                    | 2.4  |      | V    |

| V <sub>OL</sub>    | Output LOW Voltage                                  | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8.0 mA                                                                                                                                                                             |      | 0.4  | V    |

| V <sub>IH</sub>    | Input HIGH Voltage                                  |                                                                                                                                                                                                                              | 2.2  | 6.0  | V    |

| V <sub>IL</sub>    | Input LOW Voltage                                   |                                                                                                                                                                                                                              | -0.3 | 0.8  | V    |

| I <sub>IX</sub>    | Input Load Current                                  | $GND \le V_I \le V_{CC}, V_{CC} = Max.$                                                                                                                                                                                      | -20  | +20  | μΑ   |

| I <sub>OZ</sub>    | Output Leakage Current                              | $GND \le V_O \le V_{CC}$ , Output Disabled                                                                                                                                                                                   | -10  | +10  | μΑ   |

| I <sub>CCx32</sub> | V <sub>CC</sub> Operating Supply Current by 32 Mode | $V_{CC} = Max., I_{OUT} = 0 \text{ mA}, \overline{CS} \le V_{IL}$                                                                                                                                                            |      | 720  | mA   |

| I <sub>CCx16</sub> | V <sub>CC</sub> Operating Supply Current by 16 Mode | $V_{CC} = Max., I_{OUT} = 0 \text{ mA}, \overline{CS} \le V_{IL}$                                                                                                                                                            |      | 480  | mA   |

| I <sub>CCx8</sub>  | V <sub>CC</sub> Operating Supply Current by 8 Mode  | $V_{CC} = Max., I_{OUT} = 0 \text{ mA}, \overline{CS} \le V_{IL}$                                                                                                                                                            |      | 360  | mA   |

| I <sub>SB1</sub>   | Automatic CS Power-Down Current <sup>[1]</sup>      | Max. V <sub>CC</sub> ; $\overline{\text{CS}}$ ≥ V <sub>IH</sub> , Min. Duty Cycle = 100%                                                                                                                                     |      | 240  | mA   |

| I <sub>SB2</sub>   | Automatic CS Power-Down Current <sup>[1]</sup>      | $\begin{aligned} &\text{Max. V}_{\text{CC}}; \overline{\text{CS}} \geq \text{V}_{\text{CC}} - 0.2\text{V}, \\ &\text{V}_{\text{IN}} \geq \text{V}_{\text{CC}} - 0.2\text{V or V}_{\text{IN}} \leq 0.2\text{V} \end{aligned}$ |      | 40   | mA   |

## Capacitance<sup>[2]</sup>

| Parameter        | Description Test Conditions |                                         | Max. | Unit |

|------------------|-----------------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance           | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 50   | pF   |

| C <sub>OUT</sub> | Output Capacitance          | $V_{CC} = 5.0V$                         | 50   | pF   |

#### Notes:

- 1. A pull-up resistor to V<sub>CC</sub> on the  $\overline{\text{CS}}$  input is required to keep the device deselected during V<sub>CC</sub> power-up, otherwise I<sub>SB</sub> will exceed values given.

- 2. Tested on a sample basis.

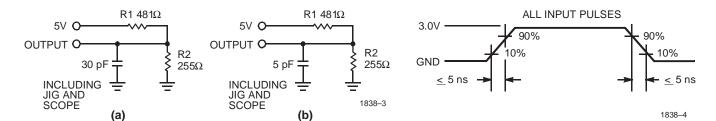

### **AC Test Loads and Waveforms**

Equivalent to: THÉVENIN EQUIVALENT

## Switching Characteristics Over the Operating Range [3]

|                   |                                    | 1838-20 1838-25<br>Min. Max. Min. Max. |    | 1838-25 |      | 1838-35 |      |    |

|-------------------|------------------------------------|----------------------------------------|----|---------|------|---------|------|----|

| Parameter         | Description                        |                                        |    | Max.    | Min. | Max.    | Unit |    |

| READ CYCLE        |                                    |                                        | •  | •       | •    | •       | •    |    |

| t <sub>RC</sub>   | Read Cycle Time                    | 20                                     |    | 25      |      | 35      |      | ns |

| t <sub>AA</sub>   | Address to Data Valid              |                                        | 20 |         | 25   |         | 35   | ns |

| t <sub>OHA</sub>  | Data Hold from Address Change      | 3                                      |    | 3       |      | 3       |      | ns |

| t <sub>ACS</sub>  | CS LOW to Data Valid               |                                        | 20 |         | 25   |         | 35   | ns |

| t <sub>DOE</sub>  | OE LOW to Data Valid               |                                        | 10 |         | 12   |         | 15   | ns |

| t <sub>LZOE</sub> | OE LOW to Low Z                    | 0                                      |    | 0       |      | 0       |      | ns |

| t <sub>HZOE</sub> | OE HIGH to High Z                  |                                        | 10 |         | 10   |         | 20   | ns |

| t <sub>LZCS</sub> | CS LOW to Low Z <sup>[4]</sup>     | 0                                      |    | 0       |      | 0       |      | ns |

| t <sub>HZCS</sub> | CS HIGH to High Z <sup>[4,5]</sup> |                                        | 12 |         | 15   |         | 20   | ns |

| WRITE CYCLE       | <b>[</b> 6]                        |                                        |    |         |      |         |      |    |

| t <sub>WC</sub>   | Write Cycle Time                   | 20                                     |    | 25      |      | 35      |      | ns |

| t <sub>SCS</sub>  | CS LOW to Write End                | 15                                     |    | 20      |      | 30      |      | ns |

| t <sub>AW</sub>   | Address Set-Up to Write End        | 15                                     |    | 20      |      | 30      |      | ns |

| t <sub>HA</sub>   | Address Hold from Write End        | 1.5                                    |    | 1.5     |      | 1.5     |      | ns |

| t <sub>SA</sub>   | Address Set-Up to Write Start      | 2.0                                    |    | 2.0     |      | 2.0     |      | ns |

| t <sub>PWE</sub>  | WE Pulse Width                     | 15                                     |    | 17      |      | 25      |      | ns |

| t <sub>SD</sub>   | Data Set-Up to Write End           | 10                                     |    | 12      |      | 15      |      | ns |

| t <sub>HD</sub>   | Data Hold from Write End           | 2                                      |    | 2       |      | 2       |      | ns |

| t <sub>LZWE</sub> | WE HIGH to Low Z                   | 0                                      |    | 0       |      | 0       |      | ns |

| t <sub>HZWE</sub> | WE LOW to High Z <sup>[5]</sup>    | 0                                      | 10 | 0       | 10   | 0       | 15   | ns |

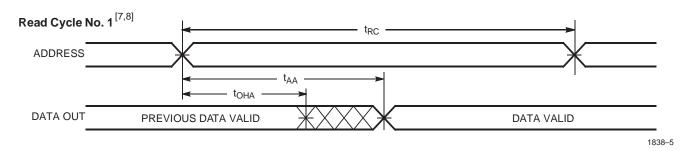

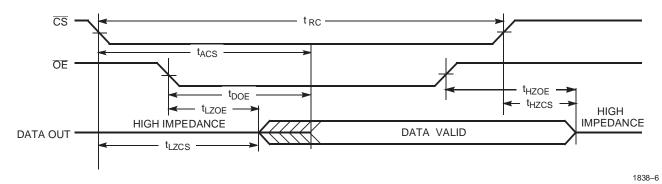

### **Switching Waveforms**

#### Notes

- Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 30-pF load capacitance.

- At any given temperature and voltage condition, t<sub>HZCS</sub> is less than t<sub>LZCS</sub> for any given device. These parameters are guaranteed by design and not 100% tested.

- t<sub>HZCS</sub> and t<sub>HZWE</sub> are specified with C<sub>L</sub> = 5 pF as in part (b) of AC Test Loads and Waveforms. Transition is measured ±500 mV from steady-state voltage.

The internal write time of the memory is defined by the overlap of CS LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can

- The internal write time of the memory is defined by the overlap of CS LOW and WE LOW. Both signals must be LOW to initiate a write and either signal ca terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

WE<sub>N</sub> is HIGH for read cycle.

- 8. Device is continuously selected,  $\overline{CS} = V_{IL}$  and  $\overline{OE} = V_{IL}$ .

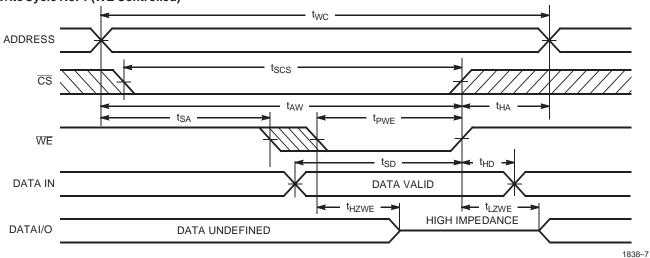

## Switching Waveforms (continued)

## Read Cycle No. 2 [7,9]

Write Cycle No. 1 (WE Controlled) [6,10]

#### Note:

- Address valid prior to or coincident with Stransition LOW.

Data I/O will be high impedance if SE = V<sub>IH</sub>.

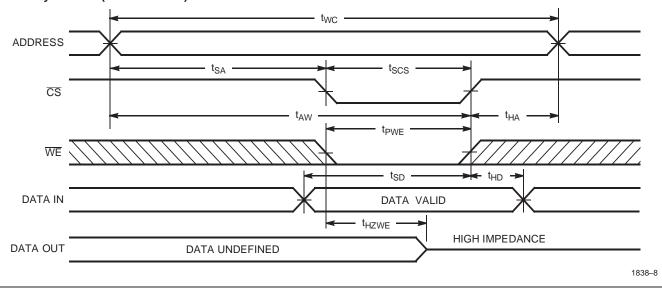

## Switching Waveforms (continued)

## Write Cycle No. 2 (CS Controlled) [6,10, 11]

#### Note:

### **Truth Table**

| CS <sub>N</sub> | ŌΕ | WEN | Input/Output | Mode                |

|-----------------|----|-----|--------------|---------------------|

| Н               | X  | Х   | High Z       | Deselect/Power-Down |

| L               | L  | Н   | Data Out     | Read                |

| L               | Х  | L   | Data In      | Write               |

| L               | Н  | Н   | High Z       | Deselect            |

## **Ordering Information**

| Speed (ns) | Ordering Code  | Package<br>Name | Package Type      | Operating<br>Range |

|------------|----------------|-----------------|-------------------|--------------------|

| 20         | CYM1838HG-20C  | HG01            | 66-Pin PGA Module | Commercial         |

|            | CYM1838HG-20M  | HG01            | 66-Pin PGA Module | Military           |

|            | CYM1838HG-20MB | HG01            | 66-Pin PGA Module |                    |

| 25         | CYM1838HG-25C  | HG01            | 66-Pin PGA Module | Commercial         |

|            | CYM1838HG-25M  | HG01            | 66-Pin PGA Module | Military           |

|            | CYM1838HG-25MB | HG01            | 66-Pin PGA Module |                    |

| 35         | CYM1838HG-35C  | HG01            | 66-Pin PGA Module | Commercial         |

|            | CYM1838HG-35M  | HG01            | 66-Pin PGA Module | Military           |

|            | CYM1838HG-35MB | HG01            | 66-Pin PGA Module |                    |

Document #: 38-M-00046-C

<sup>11.</sup> If  $\overline{\text{CS}}$  goes HIGH simultaneously with  $\overline{\text{WE}}$  HIGH, the output remains in a high-impedance state.

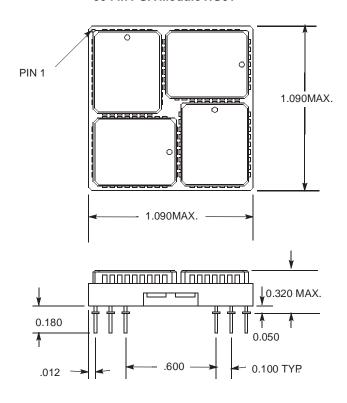

## **Package Diagram**

#### 66-Pin PGA Module HG01

<sup>©</sup> Cypress Semiconductor Corporation, 1997. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfurnion or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.