# TSC693E Memory Controller

User's Manual

For Embedded Real time 32-bit Computer (ERC32) for SPACE Applications

| TABLE (            | OF CONTENTS                                     | Page |

|--------------------|-------------------------------------------------|------|

| 1.                 | INTRODUCTION                                    | 4    |

| 1.1.               | Scope                                           | 4    |

| 1.2.               | Documents                                       |      |

| 1.2.1.             | Applicable Documents                            |      |

| 1.2.2.             | Reference Documents                             |      |

| 1.3.               | Glossary                                        | 6    |

| 1.4.               | Definitions                                     | 7    |

| 1.4.1.             | Bit Numbering                                   |      |

| 1.4.2.             | Signal Names                                    | 7    |

| 1.4.3.             | Registers                                       | 7    |

| 2.                 | GENERAL OVERVIEW OF ERC32                       | 8    |

| 2.1.               | ERC32 Overview                                  | 8    |

| 3.                 | MEMORY CONTROLLER FUNCTIONS                     | 10   |

| 3.1.               | Data Types                                      | 12   |

| 3.2.               | Memory Interface                                | 12   |

| 3.2.1.             | Memory Control Signals                          | 12   |

| 3.2.2.             | RAM                                             | 12   |

| 3.2.2.1.           | Extended RAM                                    |      |

| 3.2.3.             | Boot PROM                                       |      |

| 3.2.3.1.           | Extended PROM                                   |      |

| 3.2.4.             | Exchange Memory                                 |      |

| 3.2.5.             | I/O                                             |      |

| 3.2.5.1.<br>3.2.6. | Extended I/O                                    |      |

|                    | MEC Memory Map                                  |      |

| 3.3.               | DMA Interface.                                  |      |

| 3.4.               | Bus Arbiter                                     |      |

| 3.5.               | Execution Modes                                 |      |

| 3.5.1.             | Reset Mode                                      |      |

| 3.5.2.             | Run Mode                                        |      |

| 3.5.3.             | System Halt Mode                                |      |

| 3.5.4.<br>3.5.5.   | Power-Down Mode<br>Error Halt Mode              |      |

| 3.6.               |                                                 |      |

|                    | Wait-State and Timeout Generator                |      |

| 3.7.<br>3.7.1.     | Memory Access Protection                        |      |

| 3.7.1.<br>3.7.2.   | Unimplemented Areas RAM Write Access Protection |      |

| 3.7.2.<br>3.7.3.   | Boot PROM Write Protection                      |      |

| 3.8.               | Register Access Protection                      |      |

|                    |                                                 |      |

| 3.9.<br>3.9.1.     | EDAC Check Bit Generator                        |      |

| 3.9.1.<br>3.9.2.   |                                                 |      |

| 3.9.2.<br>3.9.3.   | Syndrome Detector                               |      |

| 5.7.3.             | Syndrome Detector                               | 30   |

# TEMIC

### Semiconductors

## **TSC693E**

| 3.9.4.<br>3.9.5.                                                                                          | Fault Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.9.3.<br>3.10.                                                                                           | Memory and I/O Parity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                           | Memory Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.11.                                                                                                     | Synchronous Traps 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.12.                                                                                                     | Interrupts (Asynchronous Traps)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.13.                                                                                                     | General Purpose and Real Time Clock Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.14.                                                                                                     | Watch Dog38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.15.                                                                                                     | UART40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.16.                                                                                                     | Parity Checking41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.17.                                                                                                     | Error Handler42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.18.                                                                                                     | System Availability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.19.                                                                                                     | Test mode and Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.19.1.                                                                                                   | EDAC Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.19.2.                                                                                                   | Parity Test47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.19.3.                                                                                                   | Interrupt Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.19.4.                                                                                                   | Error Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

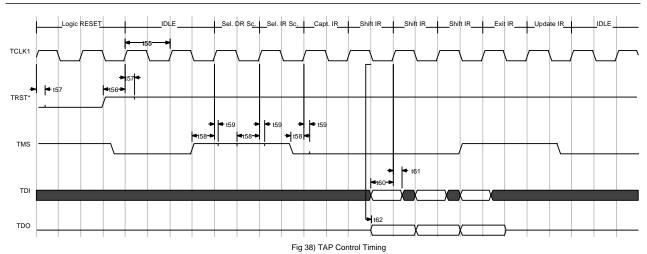

| 3.19.5.                                                                                                   | Test Access Port (TAP)48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.20.                                                                                                     | System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.21.                                                                                                     | MEC Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.21.1.                                                                                                   | Register Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.21.1.<br>3.21.2.                                                                                        | Register Address Map       49         Register Configuration and Bit Allocation       50                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.21.2.                                                                                                   | Register Configuration and Bit Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul><li>3.21.2.</li><li>4.</li></ul>                                                                      | Register Configuration and Bit Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul><li>3.21.2.</li><li>4.</li><li>4.1.</li></ul>                                                         | Register Configuration and Bit Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.21.2.<br>4.<br>4.1.<br>4.2.                                                                             | Register Configuration and Bit Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.21.2.<br>4.<br>4.1.<br>4.2.<br>4.2.1.                                                                   | Register Configuration and Bit Allocation 50  MEMORY CONTROLLER SIGNAL DESCRIPTIONS 63  Memory Controller Signal Summary 63  MEC Detailed Signal Descriptions 65  IU/FPU Interface Signals 65                                                                                                                                                                                                                                                                                                                                |

| 3.21.2.<br>4.<br>4.1.<br>4.2.<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>4.2.4.                                     | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77                                                                                                                                                                                                                                                   |

| 3.21.2.  4. 4.1. 4.2. 4.2.1. 4.2.2. 4.2.3. 4.2.4. 4.2.5.                                                  | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78                                                                                                                                                                                                                                   |

| 3.21.2.<br>4.<br>4.1.<br>4.2.<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>4.2.4.                                     | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77                                                                                                                                                                                                                                                   |

| 3.21.2.  4. 4.1. 4.2. 4.2.1. 4.2.2. 4.2.3. 4.2.4. 4.2.5.                                                  | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78                                                                                                                                                                                                                                   |

| 3.21.2.  4. 4.1. 4.2. 4.2.1. 4.2.2. 4.2.3. 4.2.4. 4.2.5. 4.2.6.                                           | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78Power and Clock Signals79                                                                                                                                                                                                          |

| 3.21.2.  4. 4.1. 4.2. 4.2.1. 4.2.2. 4.2.3. 4.2.4. 4.2.5. 4.2.6. 5.                                        | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78Power and Clock Signals79ELECTRICAL AND MECHANICAL SPECIFICATION80                                                                                                                                                                 |

| 3.21.2.  4. 4.1. 4.2. 4.2.1. 4.2.2. 4.2.3. 4.2.4. 4.2.5. 5. 5.1. 5.1.1. 5.1.2.                            | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78Power and Clock Signals79ELECTRICAL AND MECHANICAL SPECIFICATION80Maximum Rating and DC Characteristics80Maximum Ratings80Operating Range80                                                                                        |

| 3.21.2.  4.  4.1.  4.2.  4.2.1.  4.2.2.  4.2.3.  4.2.4.  4.2.5.  4.2.6.  5.  5.1.  5.1.1.  5.1.2.  5.1.3. | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78Power and Clock Signals79ELECTRICAL AND MECHANICAL SPECIFICATION80Maximum Rating and DC Characteristics80Maximum Ratings80Operating Range80DC Characteristics over the Operating Range80                                           |

| 3.21.2.  4. 4.1. 4.2. 4.2.1. 4.2.2. 4.2.3. 4.2.4. 4.2.5. 5. 5.1. 5.1.1. 5.1.2.                            | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78Power and Clock Signals79ELECTRICAL AND MECHANICAL SPECIFICATION80Maximum Rating and DC Characteristics80Maximum Ratings80Operating Range80DC Characteristics over the Operating Range80Capacitance Ratings81                      |

| 3.21.2.  4. 4.1. 4.2. 4.2.1. 4.2.2. 4.2.3. 4.2.4. 4.2.5. 4.2.6.  5. 5.1. 5.1.1. 5.1.2. 5.1.3. 5.1.4. 5.2. | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78Power and Clock Signals79ELECTRICAL AND MECHANICAL SPECIFICATION80Maximum Rating and DC Characteristics80Maximum Ratings80Operating Range80DC Characteristics over the Operating Range80Capacitance Ratings81Package Description81 |

| 3.21.2.  4. 4.1. 4.2. 4.2.1. 4.2.2. 4.2.3. 4.2.4. 4.2.5. 4.2.6.  5. 5.1. 5.1.1. 5.1.2. 5.1.3. 5.1.4.      | Register Configuration and Bit Allocation50MEMORY CONTROLLER SIGNAL DESCRIPTIONS63Memory Controller Signal Summary63MEC Detailed Signal Descriptions65IU/FPU Interface Signals65Memory System Interface Signals71Interrupt and Control Signals75Test Access Port Signals77UART Interface78Power and Clock Signals79ELECTRICAL AND MECHANICAL SPECIFICATION80Maximum Rating and DC Characteristics80Maximum Ratings80Operating Range80DC Characteristics over the Operating Range80Capacitance Ratings81                      |

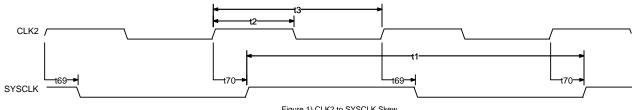

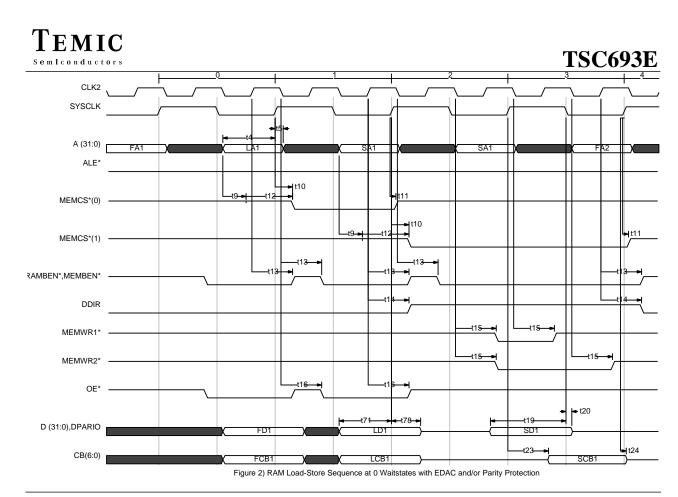

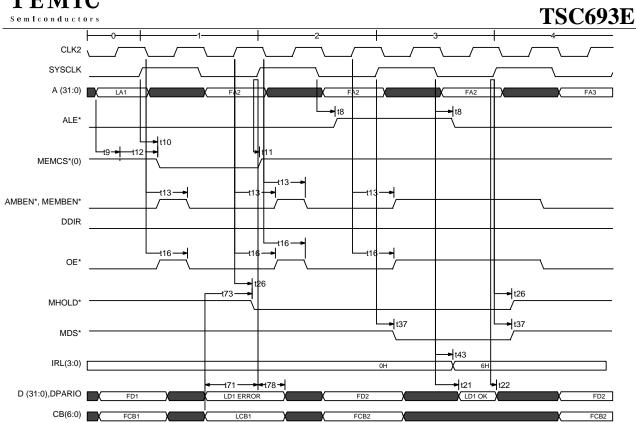

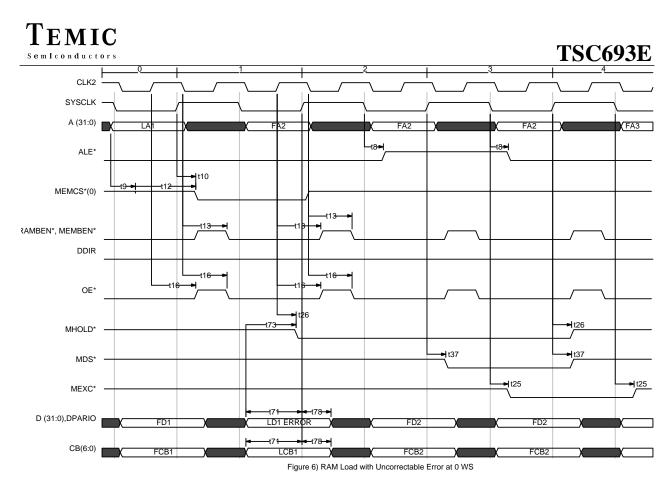

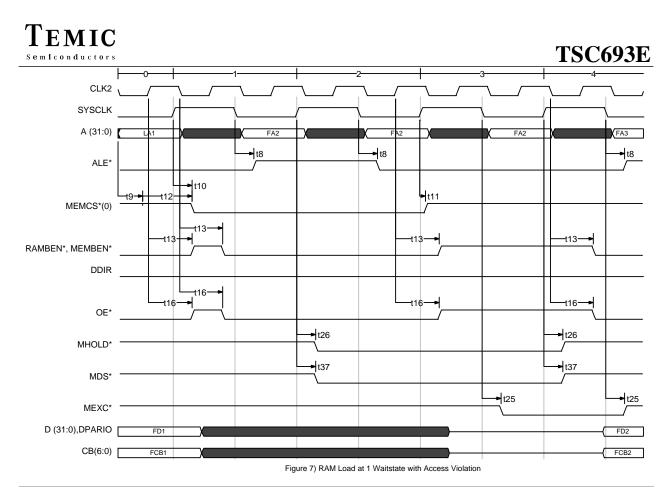

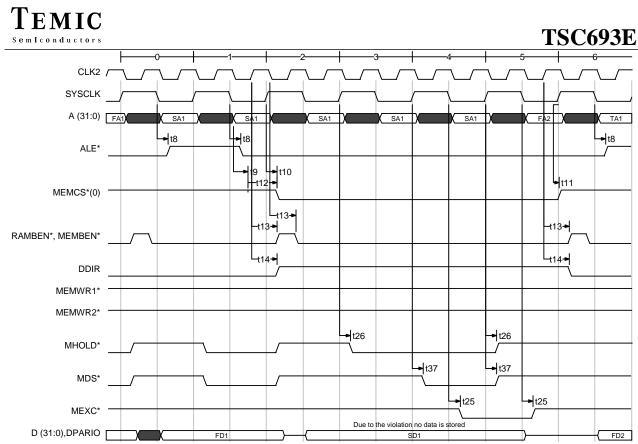

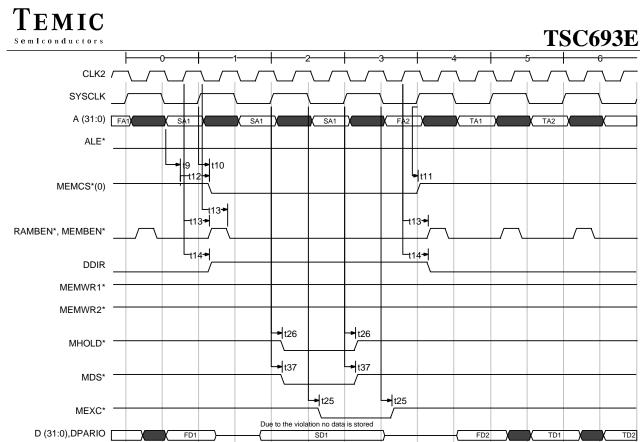

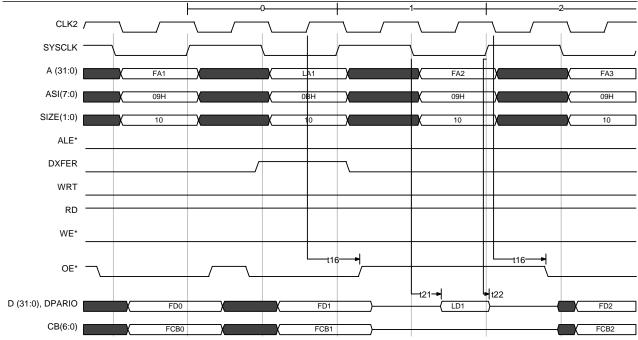

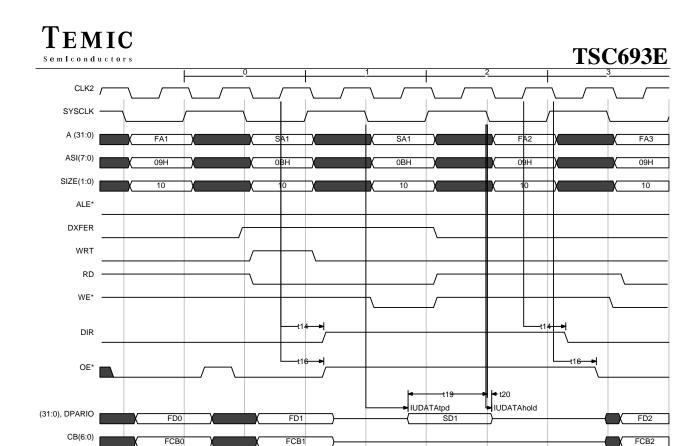

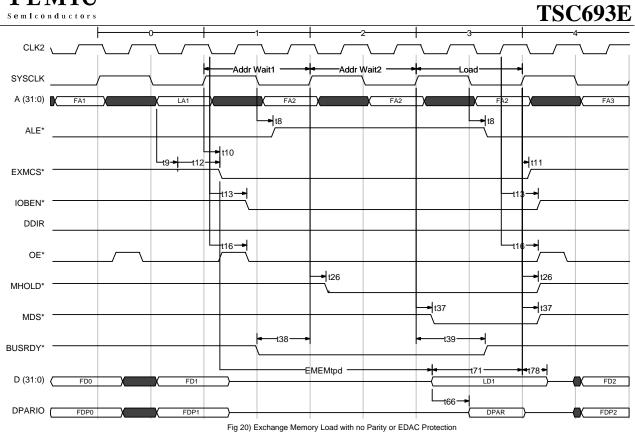

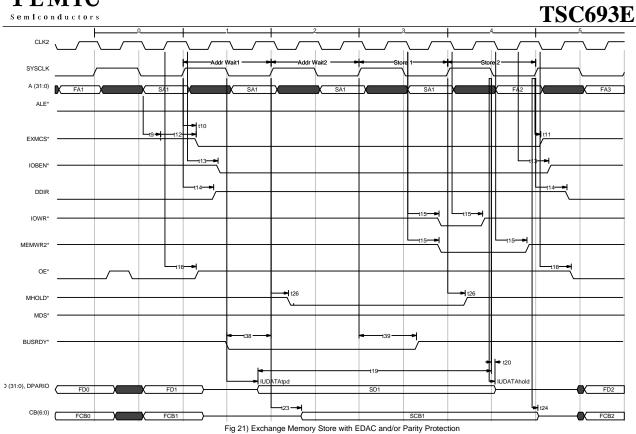

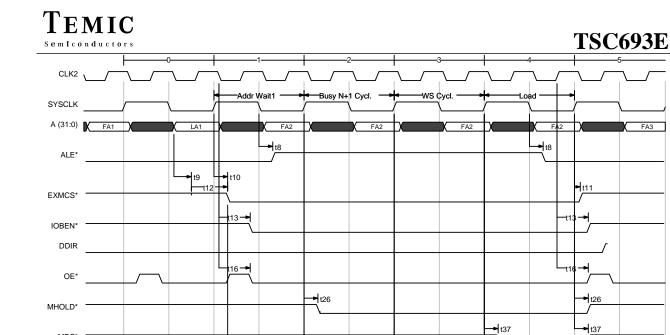

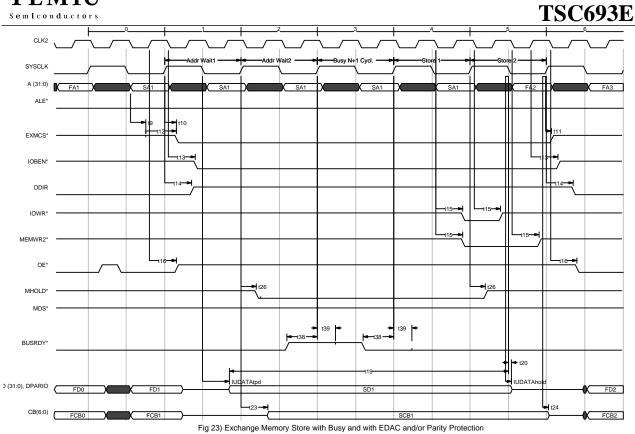

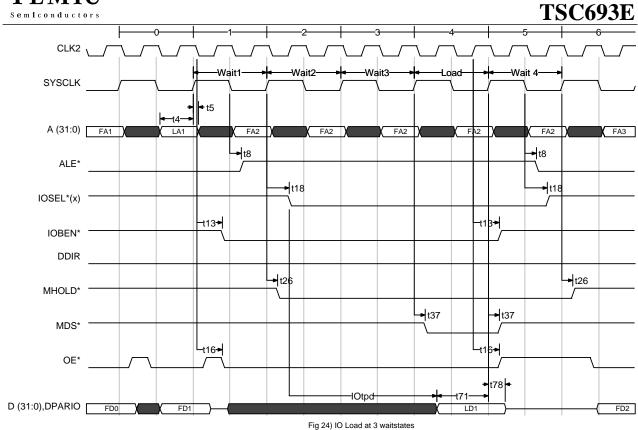

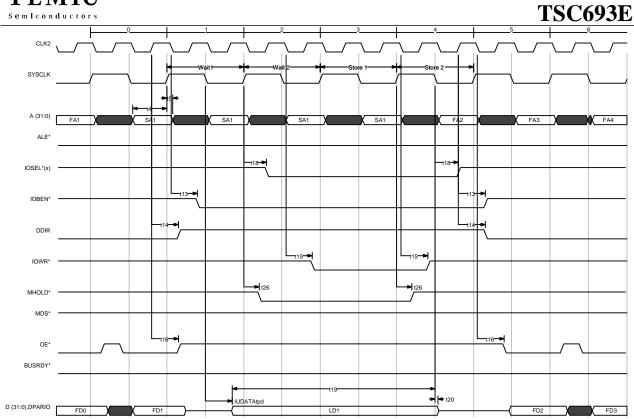

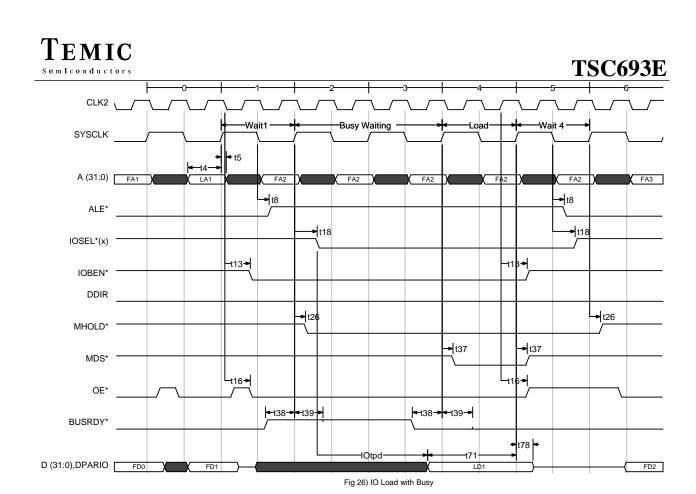

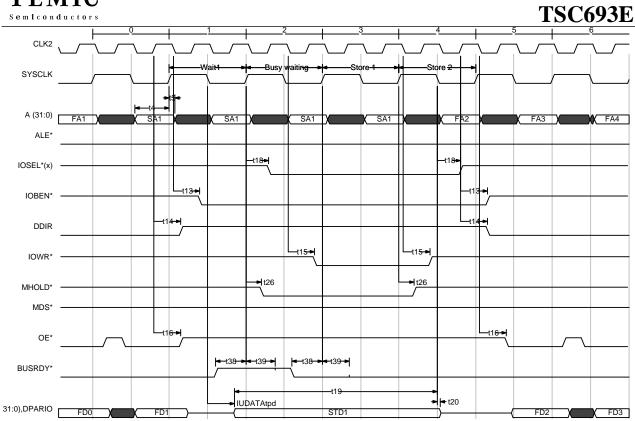

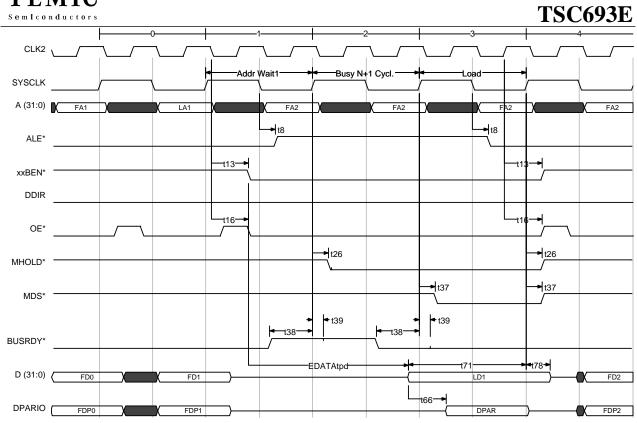

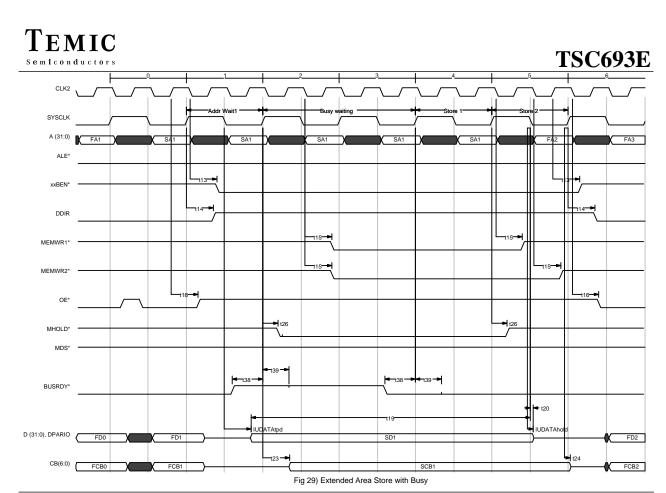

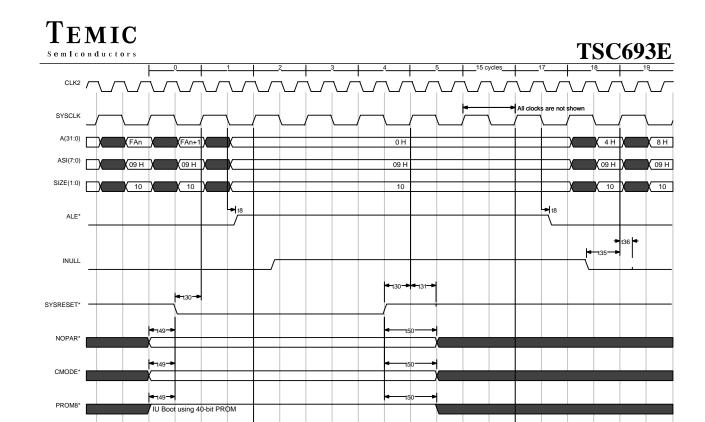

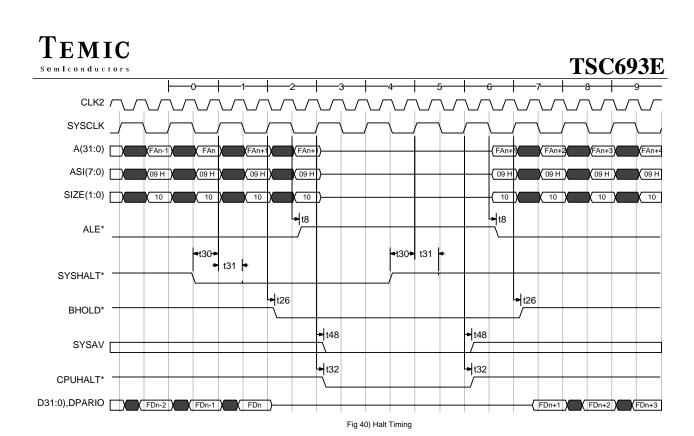

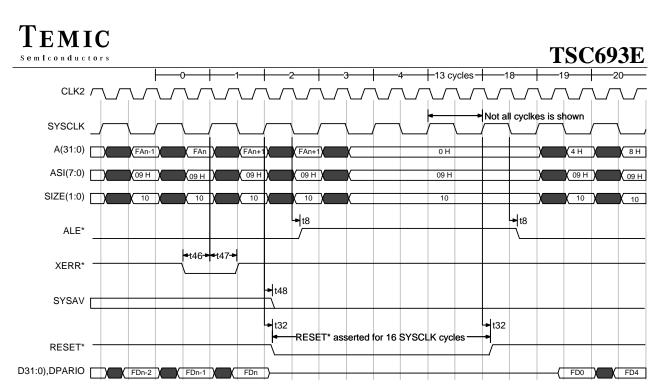

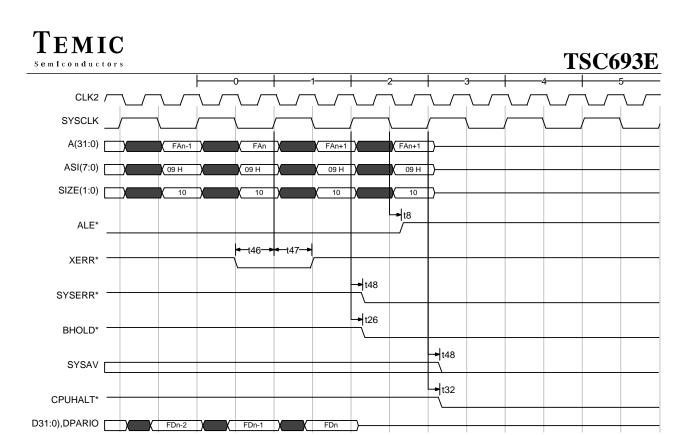

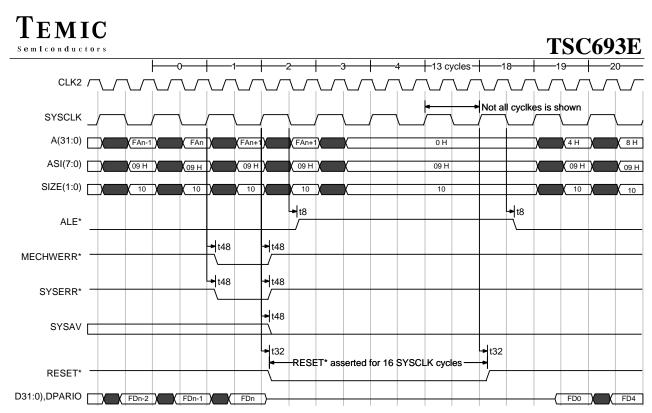

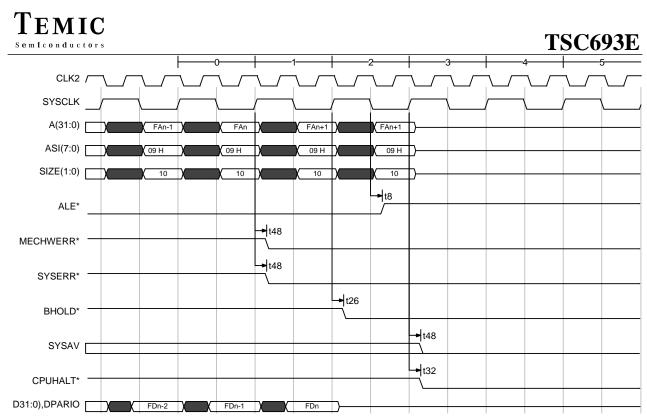

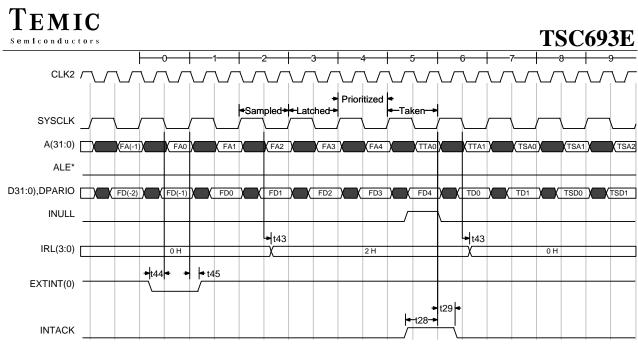

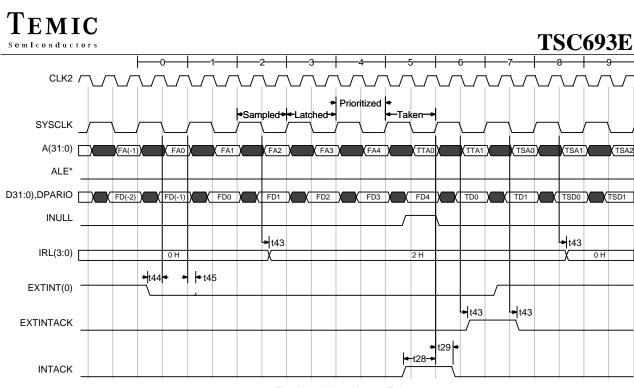

### APPENDIX 1 - TIMING DIAGRAMS

### 1. INTRODUCTION

### **1.1. Scope**

This document constitutes a functional specification of iteration two of the TSC693E Memory Controller (MEC) which is an element in the ERC32 microprocessor core. It is intended to function as a User's guide both for the software and hardware developers.

The document is divided into the following sections:

- GENERAL OVERVIEW OF ERC32

A short overview of a typical ERC32 based system.

- TSC693E MEMORY CONTROLLER FUNCTIONS

Detailed description of the MEC functions including software interface.

- TSC693E MEMORY CONTROLLER SIGNAL DESCRIPTIONS Functional description of MEC signals.

- TSC693E ELECTRICAL AND MECHANICAL SPECIFICATION

- TIMING DIAGRAMS (APPENDIX 1) Timing specifications and diagrams.

### 1.2. Documents

### 1.2.1. Applicable Documents

| AD1    | ESA 32-Bit Microprocessor and Computer Development Programme Statement of Work, WDI/JG/1317/NL, Issue 2.1, 28-05-1991. |

|--------|------------------------------------------------------------------------------------------------------------------------|

| AD2    | Specification for a 32-bit embedded computing core (ERC32), WDI/JG/1334/NL, Issue 3, 29-05-1991.                       |

| AD3    | 32-bit Microprocessor Software Tools Technical Requirements, WDI/1339/FGM/NL, 05-06-1991.                              |

| AD4    | ERC32 Technical Specification, MCD/SPC/0001/SE, issue 7, 1 Apr 1994.                                                   |

| 1.2.2. | Reference Documents                                                                                                    |

| RD1    | SPARC Standard Version 7                                                                                               |

| RD2    | TSC691E Integer Unit                                                                                                   |

| RD3    | TSC692E Floating Point Unit User's Manual                                                                              |

### **TSC693E**

### 1.3. Glossary

AD Applicable Document

ASI Address Space Identifier

ATAC Ada TAsking Coprocessor

CS Chip Select

DMA Direct Memory Access

EDAC Error Detection And Correction

EEPROM Electrically Erasable Programmable Read Only Memory

ERC32 32 bit Embedded Real-time Computing Core

EXM EXchange Memory

FAR Failing Address Register

FPU Floating Point Unit

I/O Input/Output

ICR Interrupt Clear Register

IFR Interrupt Force Register

IMR Interrupt Mask Register

IPR Interrupt Pending Register

IU Integer Unit

MEC MEmory Controller

PROM Programmable Read Only Memory

RAM Random Access Memory

RD Reference Document

ROM Read Only Memory

RTC Real Time Clock

SFSRSystem Fault Status Register

SW Software

TAP Test Access Port

TBC To Be Confirmed

TBD To Be Defined

UART Universal Asynchronous Receiver Transmitter

WD Watch Dog

### 1.4. Definitions

### 1.4.1. Bit Numbering

In this document the following conventions are used:

- The most significant bit in a vector has the highest bit number and the leftmost position in a field.

- The least significant bit in a vector has the lowest bit number and the rightmost position in a field.

### 1.4.2. Signal Names

The following conventions are used for signal names:

- Signal names are written in capital letters, SIGNALNAME.

- Active low signals are named, SIGNALNAME\*.

### 1.4.3. Registers

The following convention is used for registers.

- Register names are bolded, **Register Name**.

### 2. GENERAL OVERVIEW OF ERC32

### 2.1. ERC32 Overview

The objective of the ERC32 is to provide a high performance 32-bit computing core for on-board embedded real-time computers. The core is characterized by low circuit complexity and power consumption. Extensive concurrent error detection and support for fault-tolerance and reconfiguration is emphasized.

In addition to the main objective, the ERC32 core is possible to use for performance demanding research applications in deep space probes. In addition to the above characteristics the radiation tolerance and error masking are important. By including support for reconfigurable of the error handling the different demands from the applications can be optimized for the best purpose in each case.

The ERC32 is to be used as a building block only requiring memory and application specific peripherals to be added to form a complete on-board computer. All other system support functions are provided by the core.

The ERC32 incorporates the followings functions:

- Processor, which consists of one Integer Unit: TSC691E (called IU in this document) and one Floating Point Unit: TSC692E (called FPU in this document).

The processor includes concurrent error detection facilities.

- Memory Controller: TSC693E (called MEC in this document), which is a unit consisting of all necessary support functions such as memory control and protection, EDAC, wait state generator, timers, interrupt handler, watch dog, UARTs, and test support. The unit also includes concurrent error detection facilities.

- One or two oscillator(s).

- Buffers necessary to interface with memory and peripherals.

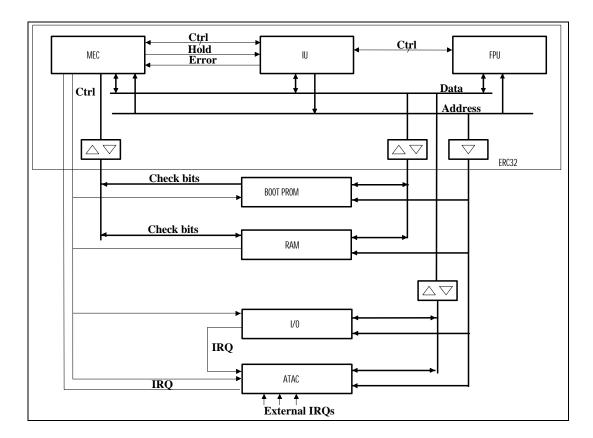

Figure 1 schematically shows a basic ERC32 computer with external functions added to form a complete system.

Figure 1 - ERC32 Computer with typical peripherals

### 3. MEMORY CONTROLLER FUNCTIONS

All support functions of the ERC32 except for the local clock/oscillator and address and data bus drivers (buffers and latches) are incorporated in one single chip memory controller unit (MEC).

The MEC is designed to interface the IU and the FPU to external memory and I/O units thus forming a system, with which computers for on-board embedded real-time applications can be built. In order to achieve this the MEC constitutes all necessary support and on-chip resources accordingly:

- System start up control and reset

- Power down mode control

- System clock

- Watchdog function

- Memory interface to RAM ranging from 256 Kbyte to 32 Mbyte

- Memory interface to PROM ranging from 128 Kbyte to 4 Mbyte

- I/O interface to exchange memory (e.g. DPRAM) ranging from 4 Kbyte to 512 Kbyte.

- I/O interface to four peripherals

- DMA interface

- Bus arbiter

- Programmable wait-state generator

- Programmable memory access protection

- Memory redundancy control

- EDAC, with byte and halfword write support

- Trap handler including 15-level interrupt controller

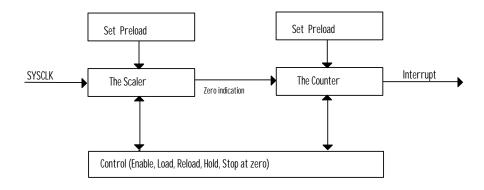

- One 32-bit general purpose timer with 16-bit scaler

- One 32-bit timer with 8-bit scaler (Real-Time-Clock)

- UART function with two serial channels

- Built-in concurrent error detection including support for master/slave checking of IU and FPU

- System error handler

- Parity control on system bus

- Test support including a minimal TAP interface

The MEC interfaces directly to the address, data, and control buses of the IU and FPU, requiring no additional components. It also interfaces directly to external memory and I/O units only requiring additional buffers for the address and data bus.

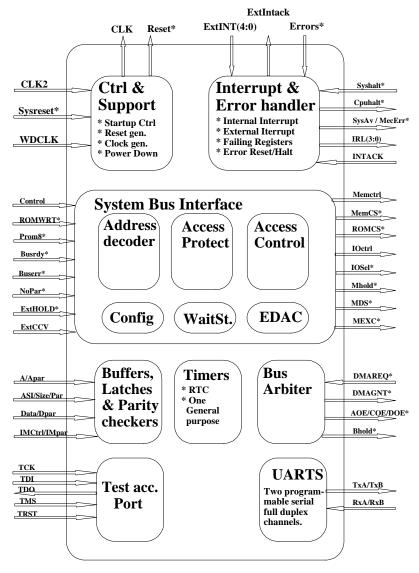

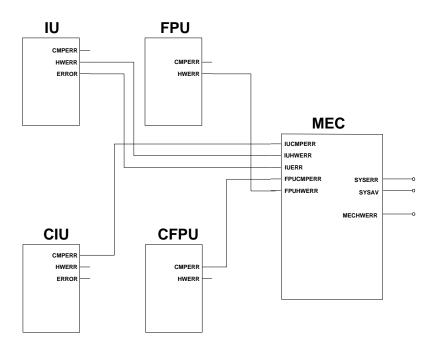

The architecture of the MEC is illustrated in Figure 2.

### **MEC Architecture**

Figure 2 - MEC architecture

### 3.1. Data Types

Data type definitions follow the SPARC standard version 7. A byte is 8 bits wide, a halfword is 16 bits wide, a word is 32 bits wide, and a double word is 64 bits wide. Organization and addressing of data in memory follow the "Big-Endian" convention wherein lower addresses contain the high-order bytes. For a stored word, address N corresponds to the most significant byte and N+3 corresponds to the least significant byte.

### 3.2. Memory Interface

### 3.2.1. Memory Control Signals

The MEC asserts a system address latch enable signal, ALE\*, when the IU address or the DMA address is valid. This signal is asserted once in every memory access cycle.

Four buffer enable signals are provided, RAMBEN\*, ROMBEN\*, MEMBEN\* and IOBEN\*. RAMBEN\* is asserted during RAM access. ROMBEN\* is asserted during boot PROM access. MEMBEN\* is asserted both during RAM and boot PROM access. IOBEN\* is asserted during I/O, Extended general area and exchange memory access.

DDIR and DDIR\* are output by the MEC to indicate buffer direction.

As RAM chip select signals MEMCS\*(9:0) are provided. The boot PROM chip select signal is ROMCS\*. Four I/O device chip select signals are provided, IOSEL(3:0). EXMCS\* is used as chip select signal for exchange memory.

For RAM and boot PROM write access two strobe pairs are provided, MEMWR1\*(1:0) and MEMWR2\*(1:0). MEMWR1\* is used to strobe data, D(31:0) into memory. MEMWR2\* is used to strobe check bits, CB(6:0) and parity, DPARIO, into memory.

For I/O and exchange memory write access the IOWR\* strobe is provided.

As output enable to memory during read access, OE\*(1:0) is provided.

BUSRDY\* is used to control access cycle length when accessing I/O, exchange memory and extended areas.

BUSERR\* is used to signal erroneous access to the MEC when accessing I/O, exchange memory and extended areas.

### 3.2.2. RAM

The MEC is reprogrammable to interface with a number of different RAM sizes and organisations. The table below shows all possible memory sizes and organisations:

| Tuble 1 Without Sizes and organizations, using o bit wide memory emps |                |                |               |               |

|-----------------------------------------------------------------------|----------------|----------------|---------------|---------------|

| RAM Size                                                              | Chip org.      | Chip org.      | Chip org.     | Chip org.     |

|                                                                       | 8 CS used =    | 4 CS used =    | 2 CS used =   | 1 CS used =   |

|                                                                       | 32 (+ 8) chips | 16 (+ 4) chips | 8 (+ 2) chips | 4 (+ 1) chips |

| 256 Kbyte                                                             | 8k chips       | 16k chips      | 32k chips     | 64k chips     |

| 512 Kbyte                                                             | 16k chips      | 32k chips      | 64k chips     | 128k chips    |

| 1 Mbyte                                                               | 32k chips      | 64k chips      | 128k chips    | 256k chips    |

| 2 Mbyte                                                               | 64k chips      | 128k chips     | 256k chips    | 512k chips    |

| 4 Mbyte                                                               | 128k chips     | 256k chips     | 512k chips    | 1M chips      |

| 8 Mbyte                                                               | 256k chips     | 512k chips     | 1M chips      | 2M chips      |

| 16 Mbyte                                                              | 512k chips     | 1M chips       | 2M chips      | 4M chips      |

| 32 Mbyte                                                              | 1M chips       | 2M chips       | 4M chips      | 8M chips      |

Table 1 - Memory sizes and organizations, using 8-bit wide memory-chips

Selection of RAM size is performed by programming the Memory Configuration Register (see page 52). The default value after system reset is 256 Kbytes.

It is possible to divide the selected RAM size into one, two, four, or eight equally sized memory blocks by programming the Memory Configuration Register. The default value after system reset is one block. A memory block is a block composed of 32-bit data, parity bit, and 7-bit check code and controlled with one chip select signal.

The MEC provides eight RAM memory chip selects. One, two, four, or eight chip selects are possible to use corresponding to the programmed number of memory blocks. The default value after system reset is one chip select. The MEC also provides two additional RAM chip selects to handle memory redundancy. See paragraph 3.10.

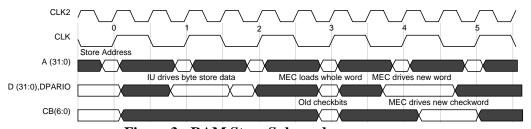

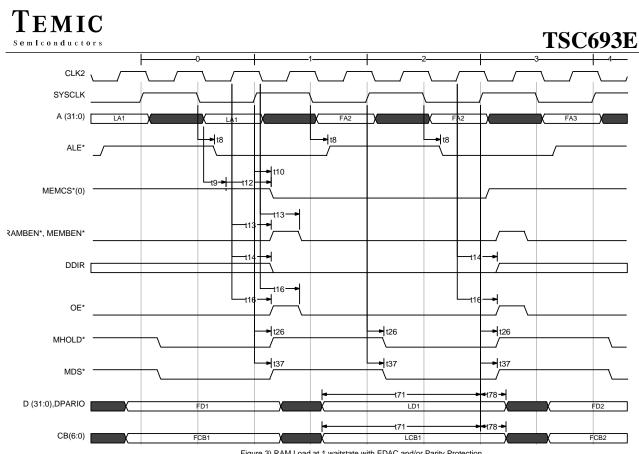

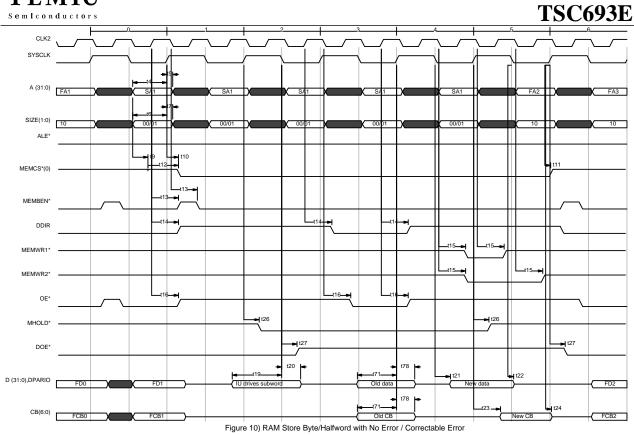

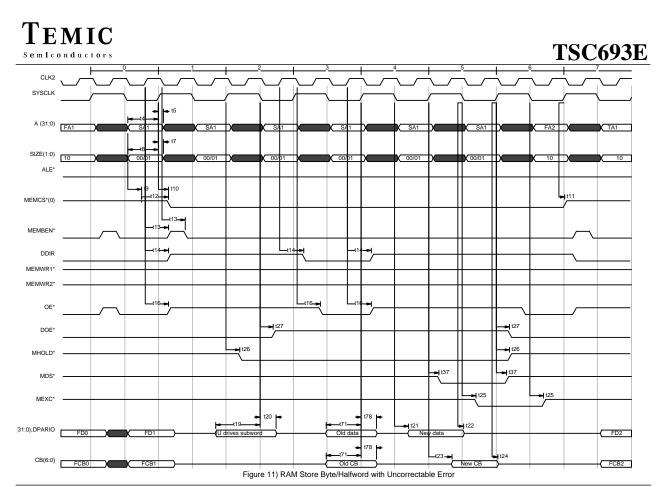

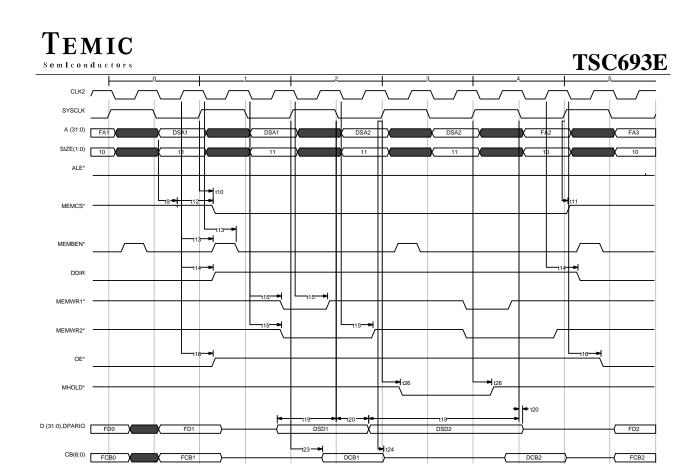

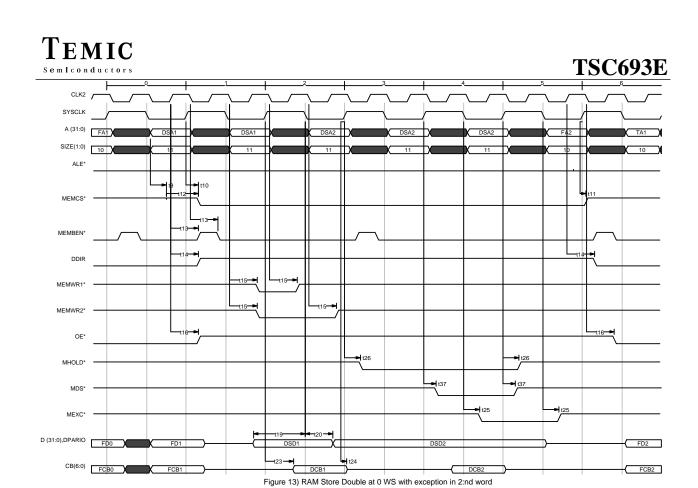

In the RAM area a store subword (byte or half-word) is implemented as a read-modify-write since check bits must be generated over the whole word, see Figure 3 below.

Figure 3 - RAM Store Subword sequence

### 3.2.2.1. Extended RAM

In addition to the nominal RAM area, an extended RAM area is reserved in the MEC memory map. The MEC does not provide any chip select signals for the extended RAM area, i.e. address decoding must be implemented with external logic. The extended RAM area is BUSRDY\* controlled with the same number of waitstates as the RAM

area. In addition, one extra clock cycle is always introduced in the beginning of the cycle for the external address decoding. Byte, halfword and word access is allowed.

### 3.2.3. Boot PROM

The MEC allows software to be executed from a single byte-wide PROM. Alternatively, a full wide EDAC protected (40 bits) PROM can be used. Hereafter this start-up PROM is called boot PROM.

One extra clock cycle is always introduced in the beginning of the cycle for the address decoding. The IU supports byte operations on data, but for instruction fetches it needs a full 32 bit wide word. In the case that byte-wide boot PROM is used (selected by asserting the PROM8\* input pin of the MEC), the MEC performs an 8 to 32 bit conversion of the boot PROM data during read access. This means that a word access to byte-wide boot PROM will correspond to four byte fetches. The total number of cycles required for each word read will then be equal to 4\*(1+ no. of boot PROM waitstates)+2.

When 32-bit wide PROM is used both EDAC and parity bits **must** be supplied to the MEC.

During read operations, byte, halfword and word access is allowed. If the boot PROM is based on EEPROM devices, the MEC supports write access, but note that only byte write is supported if byte-wide EEPROM is used. The write access possibility is enabled by asserting the Prom Write Control signal (ROMWRT\*).

The following sizes of the boot PROM are allowed: 128 Kbytes, 256 Kbytes, 512 Kbytes, 1 Mbytes, 2 Mbytes, 4 Mbytes, 8 Mbytes and 16 Mbytes. Selection of PROM size is to be performed by programming the **Memory Configuration Register** (see page 51). The default size of the boot PROM after system reset is the minimum size, 128 Kbytes. The MEC provides one PROM chip select output.

### 3.2.3.1. Extended PROM

In addition to the boot PROM area, an extended PROM area is reserved in the MEC memory map. The MEC does not provide any chip select signals for the extended PROM area, i.e. address decoding must be implemented with external logic. The extended PROM area is BUSRDY\* controlled with the same number of waitstates as the boot PROM area. In addition, one extra clock cycle is always introduced in the beginning of the cycle for the external address decoding. The number of cycles is however always at least two even if the PROM area waitstate value has been programmed to zero. The same restrictions as for boot PROM apply regarding data width and write access.

### 3.2.4. Exchange Memory

The MEC supports a dedicated exchange memory area that can be used for system bus interchange of data.

The following sizes of the exchange memory are allowed: 4 Kbytes, 8 Kbytes, 16 Kbytes, 32 Kbytes, 64 Kbytes, 128 Kbytes, 256 Kbytes, and 512 Kbytes. Selection of exchange memory size is done by programming the **Memory Configuration Register** (see page 52). The default value of the exchange memory size after system reset is the minimum size, 4 Kbytes. The MEC provides one exchange memory chip select output.

Only word access is allowed in the exchange memory area. Any attempt to access byte or halfword data in the exchange memory will cause a memory exception.

In case the exchange memory includes EDAC check bits and parity bits, these protection bits will be treated in the same manner as for the main memory. If the exchange memory does not include any check bits, the MEC will generate the parity to the IU. The default is that no EDAC or parity is implemented in the exchange memory. If the exchange memory implements check bits, this must be defined in the **Memory Configuration Register** in the MEC during start up and initialization.

The MEC is designed to allow implementation of the exchange memory with a DPRAM. The BUSY signal from the DPRAM can then be connected to the BUSRDY\* signal of the MEC. The MEC waits one cycle at the start of the access for the assertion of the BUSRDY\* signal. If the BUSRDY\* signal is asserted in the beginning of the second cycle, the normal data wait-state controlled access continues. If the BUSRDY\* signal is deasserted during the wait-states, the MEC will delay the access until the BUSRDY\* signal has been asserted and then continue with the normal data wait-state controlled access. If a cycle is prolonged to more than 256 clock cycles, the Bus Timeout function will signal a system bus error.

The minimum length of an exchange memory access is three clock cycles.

### 3.2.5. I/O

Four address decoded I/O select outputs are provided in the MEC.

The minimum length of an I/O access for each I/O select is programmable in the MEC. The BUSRDY\* signal is used to prolong I/O access for devices with variable access time. The BUSERR\* signal is used to signal to the MEC that a bus error has occurred.

Table 2 gives the encoding for the system bus transaction response signals. The transactions that signal a system bus error, set the corresponding bit in the **System Fault Status Register** (SFSR) of the MEC, which then responds by asserting Error to the interrupt logic. These bits describe system bus error cases, in addition the bus timeout is set if the internal bus time out timer causes abortion.

| Tubic 2 Dub Trumbuction Tresponde Signals |         |                     |  |  |

|-------------------------------------------|---------|---------------------|--|--|

| BUSERR*                                   | BUSRDY* | Action              |  |  |

| Н                                         | Н       | Nothing (not ready) |  |  |

| Н                                         | L       | Data Strobe (ready) |  |  |

| L                                         | Н       | Nothing (not ready) |  |  |

System Bus Error

**Table 2 - Bus Transaction Response Signals**

An I/O cycle which is to be extended beyond that of the number of wait-states set in the MEC for the corresponding I/O select output, requires that the BUSRDY\* signal is deasserted as input to the MEC. The BUSRDY\* signal must be deasserted no later than the number of system clock cycles equal to the wait-states set in the MEC after start of the access.

The actual length of an IO cycle will equal the number of programmed waitstates, possibly extended a number of clock cycles by deassertion of the BUSRDY\* signal. If a cycle is prolonged to more than 256 clock cycles, the Bus Timeout function will signal a system bus error. As the BUSRDY\* signal is used to extend the IO cycle, one waitstate is minimum for I/O access. Programming the no. of IO waitstates to zero will have no effect, i.e. one waitstate is inserted anyway.

Each I/O unit is enabled by programming the **I/O Configuration Register** (see page 54). The default value after system reset is no I/O unit enabled.

Each of the four I/O units is programmable to following sizes: 512 bytes, 1 Kbyte, 2 Kbytes, 4 Kbytes, 8 Kbytes, 16 Kbytes, 32 Kbytes, 64 Kbytes, 128 Kbytes, 256 Kbytes, 512 Kbytes, 1 Mbyte, 2 Mbytes, 4 Mbytes, 8 Mbytes, 16 Mbytes.

Selection of each individual I/O unit size is performed by programming the **I/O Configuration Register** (see page 54). The default value after system reset is 512 bytes for all units.

In case the I/O unit includes a parity bit, the parity will be treated in the same manner as for the main memory. If the I/O unit does not include parity, the MEC will generate parity to the IU. The **I/O Configuration Register** (see page 54) is used to determine for each individual I/O unit if the MEC shall use parity checking and generation. The default is no parity is implemented for the I/O units.

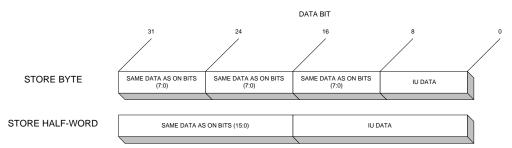

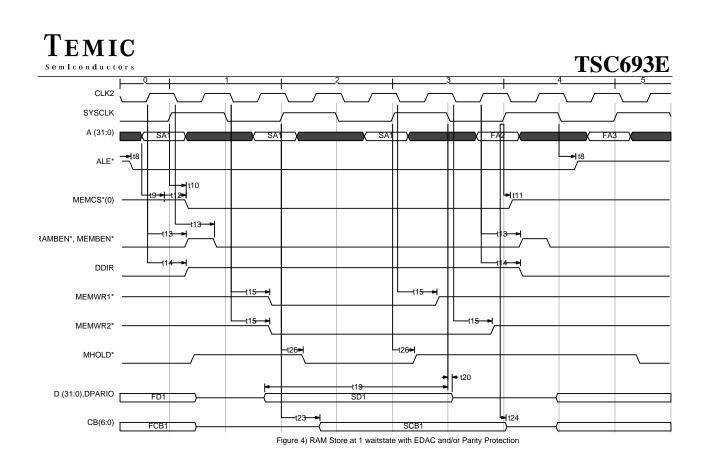

Since the I/O unit never includes EDAC check bits, the store subword (half-word or byte) instruction in the I/O area is different from the store subword in the RAM area. In the RAM area a store subword is implemented as a read-modify-write since check bits must be generated over the whole word. In the I/O area a store subword is implemented as a store word from a timing point of view, but the subword (byte or halfword) is repeated by the IU on the other subwords in the full word, see Figure 4.

<sup>\*</sup> denotes an active low signal

Figure 4 - Store Subword Data Layout

### 3.2.5.1. Extended I/O

In addition to the nominal I/O area, an extended I/O area is reserved in the MEC memory map. The MEC does not provide any chip select signals for the extended I(O area, i.e. address decoding must be implemented with external logic. The extended I/O area is BUSRDY\* controlled with the same number of waitstates as the nominal I/O area. The number of waitstates is however always at least one even if the I/O area waitstate value has been programmed to zero. The same no. of waitstates and parity option as for I/O area 3 apply.

3.2.6. MEC Memory Map

The MEC memory map is shown in Table 3.

Table 3 - MEC Memory map

|               | e 3 - MEC Memory map             | 1                | <u> </u>                 |

|---------------|----------------------------------|------------------|--------------------------|

| Address       | Memory contents                  | Size (Bytes)     | Data size and parity     |

| (hexadecimal) |                                  |                  | options                  |

| 0x00000000    | Boot PROM                        | 128k - 16M       | * 8-bit mode             |

|               |                                  |                  | 8 to 32 bit conversion   |

|               |                                  |                  | No parity                |

|               |                                  |                  | Only byte write          |

|               |                                  |                  | * 40-bit mode            |

|               |                                  |                  | Parity+EDAC mandatory    |

|               |                                  |                  | Only word write          |

| 0x01000000    | Extended PROM area               | 15M              | The same settings as for |

|               | BUSRDY* controlled <sup>1)</sup> |                  | Boot PROM                |

| 0x01F00000    | Exchange memory                  | 4k - 512k        | Parity/EDAC options      |

|               | BUSRDY* controlled               |                  | Only word accesses       |

| 0x01F80000    | MEC Registers                    | 512k (136 used)  | Parity only              |

|               |                                  |                  | Word write and Word/     |

|               |                                  |                  | Hword/ Byte read         |

| 0x02000000    | RAM Memory                       | 8 * 32k - 8 * 4M | Parity/EDAC options      |

|               | (8 blocks)                       |                  | All data sizes allowed   |

| 0x04000000    | Extended RAM area                | 192M             | The same settings as for |

|               | BUSRDY* controlled <sup>1)</sup> |                  | RAM Memory               |

| 0x10000000    | I/O area 0                       | 0 - 16M          | Parity option            |

|               |                                  |                  | All data sizes allowed   |

| 0x11000000    | I/O area 1                       | 0 - 16M          | As above                 |

| 0x12000000    | I/O area 2                       | 0 - 16M          | As above                 |

| 0x13000000    | I/O area 3                       | 0 - 16M          | As above                 |

| 0x14000000    | Extended I/O area                | 1728M            | The same settings as for |

|               | $BUSRDY* controlled^{1)}$        |                  | I/O area 3               |

| 0x80000000    | Extended general area            | 2G               | No parity/EDAC           |

|               | $BUSRDY* controlled^{1)}$        |                  | All data sizes allowed   |

1) Neither access protection nor chip select generation is performed by the MEC for the extended areas. Note that these areas are only controlled by the BUSRDY\* signal.

In the *I/O areas* and in the *Extended areas* one waitstate is always inserted, since the MEC has to wait for the BUSRDY\* signal. In the *Exchange Memory area* two waitstates are always inserted to wait for the BUSRDY\* signal. In the *I/O areas* and in the *Extended areas* the BUSRDY\* signal works as a ready signal to tell the accessing unit that data is ready. In the *Exchange Memory area* the BUSRDY\* signal works as a busy signal to tell the accessing unit that the access can not yet start.

### 3.3. DMA Interface

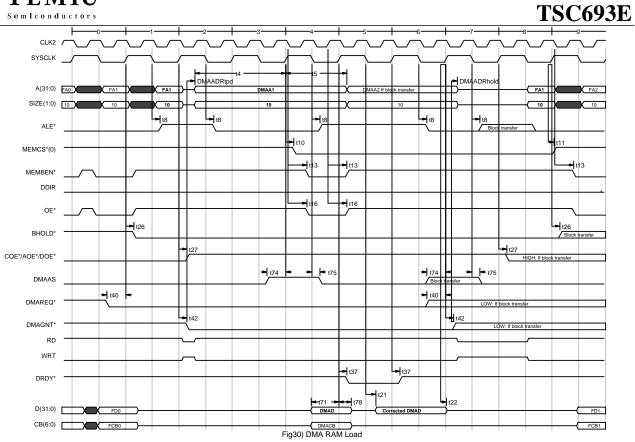

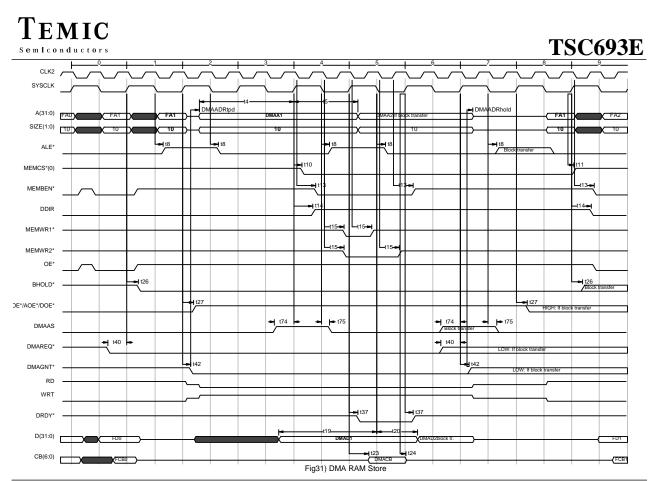

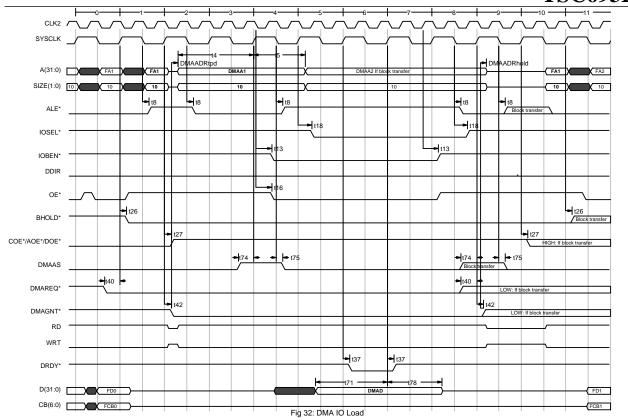

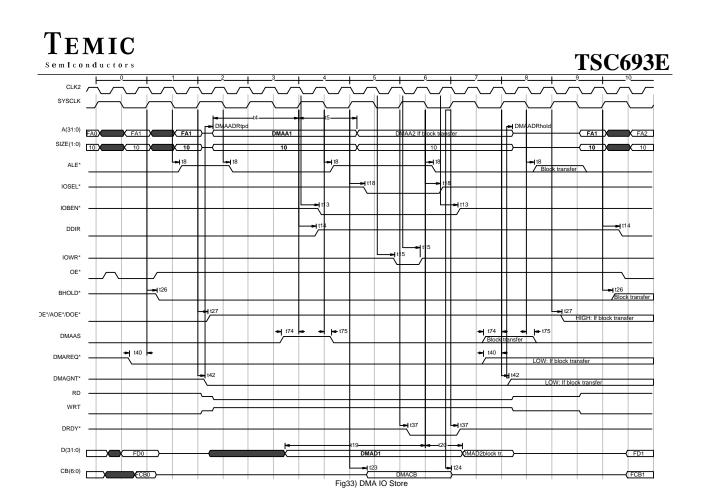

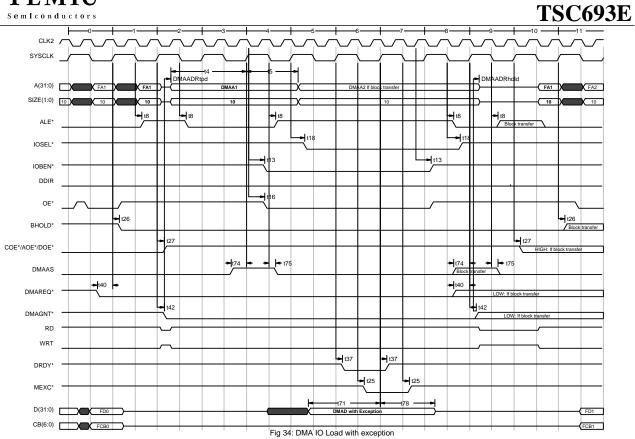

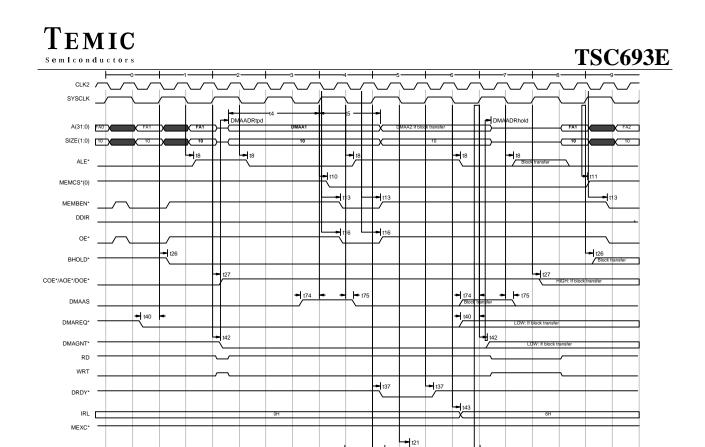

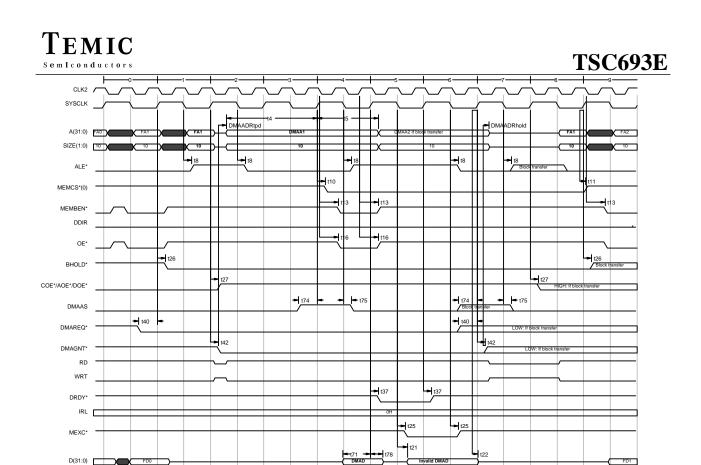

The MEC supports Direct Memory Access (DMA). The DMA unit requests access to the processor bus by asserting the DMA request signal, DMAREQ\*. When the DMA unit receives the DMAGNT\* signal in response, the processor bus is granted. In case the processor is in the power down mode the IU is permanent three-stated, and a DMAREQ\* will directly give a DMAGNT\*. The detailed timing for DMA accesses is defined in Appendix A.

It is possible to enable/disable DMA access to the system bus by programming the **MEC Control Register** (see page 51). The default status after system reset is DMA enabled (i.e. permitted).

If DMA is enabled, the MEC asserts BHOLD\* and deasserts AOE\*, COE\*, and DOE\* following an DMA Request and then asserts DMA Grant.

A memory cycle started by the processor is not interrupted by a DMA access before it is finished. The following signals shall be used by the DMA unit during the access:

- DMAREQ\* to be generated by the DMA unit asking for access

- DMAGNT\* generated by the MEC when DMA access is granted

- SYSCLK from the MEC to be used as synchronizing clock

- A[31:0], ASI[3:0] address and SIZE[1:0], WRT, WE\*, RD, DXFER, LDSTO, LOCK to be generated by the DMA unit.

- SIZE0 and SIZE1, to be driven by the DMA during DMA transfers. Note that only word transfers are allowed in DMA mode, which means that the values of the size bits must always be driven to SIZE0 = 0 and SIZE1 = 1 in DMA mode.

- APAR, ASPAR and IMPAR parity bits, to be generated by the DMA unit in case parity is enabled for the DMA

- D[31:0] data generated by the DMA unit in case of write cycle or fetched by the DMA unit during read cycle

- DPARIO, data parity, to be generated and possibly checked by the DMA unit in case parity is enabled for the DMA

- DMAAS line used for address strobe to be generated by the DMA unit when the address is valid. Assertion of this signal will initiate the memory access.

- DRDY\* line used for indicating data ready for the DMA unit or data written on write. It is generated by the MEC

- MEXC\* generated by the MEC indicating a memory access exception when no valid data can be supplied from the memory system, e.g. access violation or error.

If no subsequent DMA cycles are to be issued the DMA unit shall remove the DMAREQ\* signal as soon as it has fetched the data on read after that it has received

DRDY\*, or when DRDY\* is removed on write. The MEC will then remove the DMAGNT\* signal.

It is possible to enable/disable DMA parity by programming the **MEC Control Register** (see page 54). The default status after system reset is that DMA parity is disabled. If DMA parity is enabled it has to be generated during write and possibly checked by the DMA during read. If DMA parity is not enabled the MEC generates the parity bit to be stored in the memory in case of write accesses.

Memory access protection is active also during DMA, i.e. attempted write access to protected memory segments will lead to a memory exception, depending on how the ASI bits are driven by the DMA unit (user or supervisor mode).

Normally, the same restrictions apply to DMA access of MEC registers as for the IU in User mode, see page 49. However during system halt (i.e. CPUHALT signal active), the DMA has the same access rights as the IU in supervisor mode for MEC register access. With register write access, memory protection could be changed to permit DMA to access all areas.

The MEC includes a DMA session timeout function preventing the DMA unit to lockout the IU/FPU by asserting DMAREQ\* for a long time. If the DMA Request input is not deasserted within 1024 system clock cycles after the assertion of DMA Grant, the memory exception output is asserted and the DMA Grant is removed. The DMA session timeout function is possible to enable or disable by programming the **MEC Control Register** (see page 54). After system reset the timeout function is enabled.

Note that the DMA session timeout function is <u>not</u> the same as a bus timeout, rather an session scheme timeout. In case of a bus timeout during DMA, the MEC asserts the Memory Exception output and removes the Bus Grant. For further actions taken see paragraph 3.17.

### 3.4. Bus Arbiter

The IU and the FPU always have the lowest priority to the system bus and are denied access to memory in case of a request from a DMA unit, unless the IU is performing a locked access or after a DMA exception cycle to allow interrupt handling.

Thus the DMA is granted access to the system bus provided this has been enabled by the IU in the MEC. In other words the IU has the capability to prevent DMA accesses by disabling DMA in the MEC.

### 3.5. Execution Modes

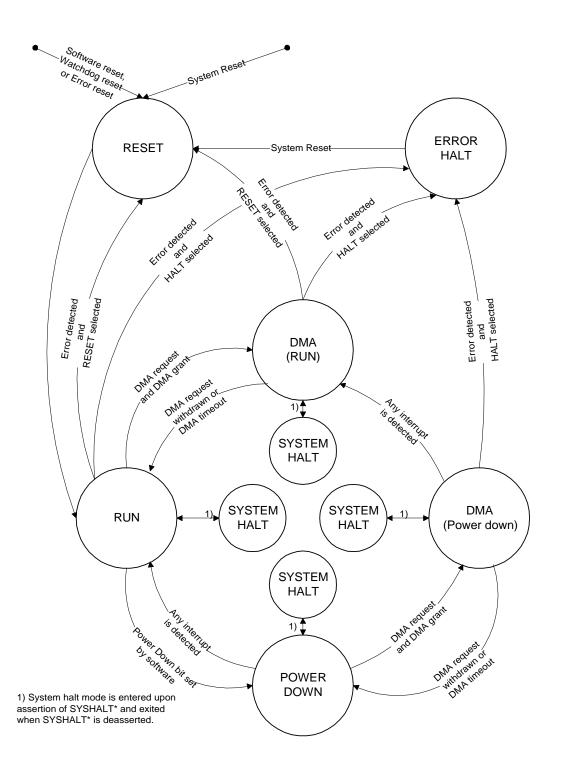

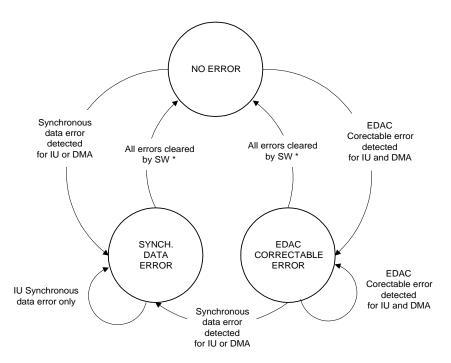

The execution modes of the ERC32 as controlled by the MEC is shown in Figure 5.

**Figure 5 - ERC32 Execution Modes**

#### 3.5.1. Reset Mode

When the SYSRES\* input is asserted, the MEC issues a reset of itself and asserts the RESET\* output which is intended be used as reset signal to all other components in the system (e.g. IU and FPU). The SYSRES\* signal shall be applied for at least four clock cycles.

After the assertion of SYSRES\*, the MEC starts the ERC32 system in the reset mode which means that all MEC registers will be initialized to their reset contents.

The reset signal from the MEC to the IU/FPU etc., RESET\*, is minimum 16 clock cycles long, i.e. it will remain asserted 16 system clock cycles after SYSRES\* has been deasserted.

Reset mode is also entered when the RESET\* output of the MEC is asserted from any other reason than SYSRES\*:

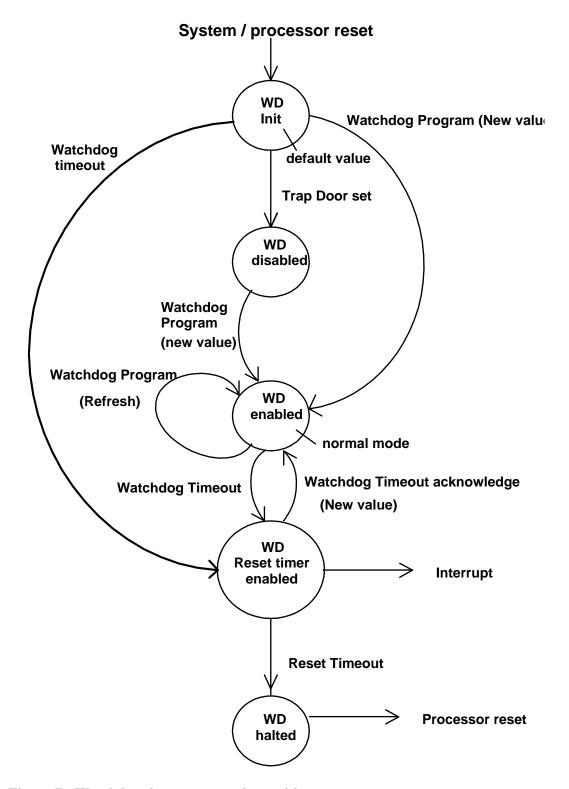

- Software reset which is caused by the software writing to a **Software Reset Register** (see page 52).

- Watchdog reset which is caused by a Watchdog counter timeout (see paragraph 3.14.)

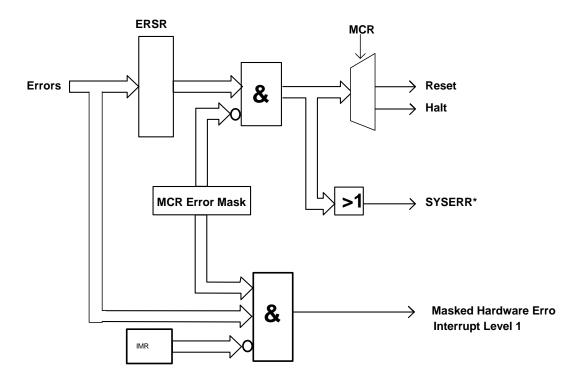

- Error reset which is caused by a hardware parity error, EDAC uncorrectable error or a comparison error (see paragraph 3.17.)

When the reset cause is one of the above, all MEC registers will be initialized to their reset contents except the **Error and Reset Status Register** (see page 61) which contains the source of the last processor reset (System reset, software reset, error reset, watch dog reset). By reading that register upon reset, the IU can determine the cause of the reset.

### 3.5.2. Run Mode

In this mode the IU/FPU is executing, all timers of the MEC are running (if software enabled) and the UART is running.

### 3.5.3. System Halt Mode

System Halt mode is entered when the SYSHALT\* input of the MEC is asserted. The CPUHALT\* output is asserted, freezing IU/FPU execution. All timers are halted and the UART operation is stopped.

The MEC allows DMA accesses during system halt mode, in which DMA has permanent access to the system, i.e. DMAGNT\* is asserted immediately on DMA request.

When SYSHALT\* is deasserted, the previous mode is entered.

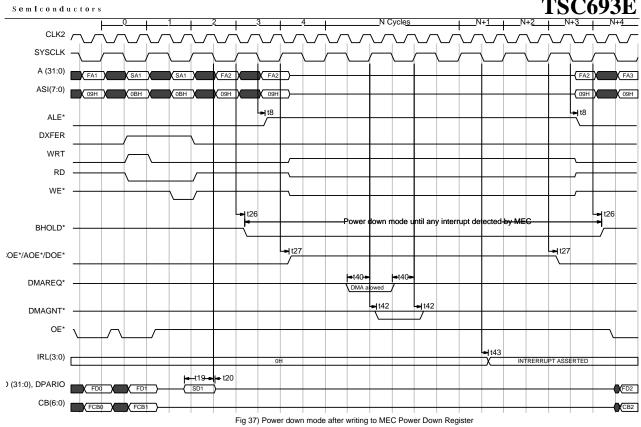

### 3.5.4. Power-Down Mode

This mode is entered by writing to the **Power Down Register** (see page 52) in the MEC, which will cause the MEC bus arbiter to remove the bus ownership from the IU. The entering of power-down mode must first permitted by programming the **MEC Control Register** (see page 51).

In power-down mode the MEC asserts and maintains the BHOLD\* and deasserts and maintains the AOE\*, COE\*, and DOE\* output signals. If an external interrupt is asserted whilst being in power down mode the MEC deasserts the BHOLD\* and asserts the AOE\*, COE\*, and DOE\* output signals. And thereafter ensures that all data at all inputs to the IU/FPU are the same as it was before BHOLD\* was asserted. The IU gets back the bus ownership and the MEC leaves the power-down mode.

The MEC allows DMA accesses during power-down mode, in which DMA has permanent access to the system, i.e. DMAGNT\* is asserted immediately on DMA request.

### 3.5.5. Error Halt Mode

Error Halt mode is entered under the following circumstances:

- A hardware parity error, EDAC uncorrectable error or a comparison error (see paragraph 3.17.) has occurred.

- The IU enters error mode (by asserting the ERROR\* output)

In Error Halt mode, the CPUHALT\* and SYSERR\* outputs of the MEC are asserted (note that SYSERR\* is also asserted if a masked error occurs even though Error Halt mode is not entered in this case). All timers are halted and the UART operation is stopped in this mode. The only way to exit Error Halt Mode is through Cold Reset by asserting SYSRES\*.

The MEC allows DMA accesses during error halt mode, in which DMA has permanent access to the system, i.e. DMAGNT\* is asserted immediately on DMA request.

Error Halt Mode can be induced by software by first setting the EWE bit in the **Test Control Register** (see page 61) and then write an error to the **Error and Reset Status Register** (see page 61). Note however that this also requires that the Reset/Halt bit for the chosen error is set to halt in the **MEC Control Register**.

### 3.6. Wait-State and Timeout Generator

It is possible to control the wait state generation by programming a **Waitstate Configuration Register** (see page 55) in the MEC. The maximum programmable number of wait-states is applied as default at reset.

It is possible to program the number of wait states for the following combinations:

- RAM read

- RAM write

- PROM read

- PROM write (i.e. EEPROM write)

- ExM read/write (i.e. Exchange memory read/write)

- Four individual I/O peripherals read/write

The MEC supports wait state generation by asserting the MHOLD\* output in the second memory access cycle.

On exchange memory accesses the MEC will sense the bus ready signal (BUSRDY\*) after the first two cycles of the access. If the bus ready signal is asserted at this time the MEC will continue with the programmed no. of wait states. However, if the bus ready signal is deasserted, the start of the access is put on hold. Once the bus ready signal is asserted again, the access will start with the programmed no. of waitstates.

On I/O and extended area accesses the MEC will sense the bus ready signal (BUSRDY\*) after the first cycle of the access. If the bus ready signal is asserted at this time the MEC will continue with the programmed no. of wait states. If the bus ready signal is deasserted at this time, the MEC will introduce wait states until the bus ready signal is again asserted.

Note the difference between wait state handling for exchange memory and wait state handling for I/O. For exchange memory, the access will *start* when BUSRDY\* is asserted, i.e. after BUSRDY\* is asserted an access with the programmed no. of wait states will be performed. BUSRDY\* is then handled as for the I/O and extended area. On the other hand, during I/O and extended area access, assertion of BUSRDY\* signals the *end* of the access, i.e. the access will finish one cycle after BUSRDY\* has been asserted (at the earliest after the programmed no. of wait states).

A bus timeout function of 256 or 1024 system clock cycles is provided for the bus ready controlled memory areas, 256 system clocks in the Extended RAM, Extended General and Extended I/O areas and 1024 system clocks in the Extended PROM area. The **MEC Control Register** (see page 51) is used to select this function. The default after system reset is that the bus timeout function is enabled.

The bus timeout counter will start when the access is initiated. If the bus ready signal is not asserted before a valid number of system clock cycles, a memory exception will occur. For further actions taken see paragraph 3.17.

### 3.7. Memory Access Protection

### 3.7.1. Unimplemented Areas

Accesses to all unimplemented memory areas are handled by the MEC and detected as illegal, according to Table 3 (page 18). The memory and I/O configuration registers define the size of memory and I/O areas. The unused area of the memory space, dependent on the programming of the memory size, is decoded as illegal.

If an access from the IU is attempted to an illegal area, the memory exception output is asserted. If an access from the DMA is attempted to an illegal area, the memory exception output (MEXC\*) and the DMA access error interrupt output are asserted.

For the extended areas no access protection is implemented. However, since these areas are bus ready(BUSRDY\*) controlled the bus timeout function will detect an access to an unimplemented extended area.

When the IU issues the trap service routine, the contents of the MEC **System Fault Status Register** (SFSR) give the cause of the exception.

When a memory data access violation error occurs (RAM write protection or illegal area) the associated bus address is latched in a separate register, MEC **Failing Address Register** (FAR). With memory data access is meant IU operand fetch or DMA. An IU instruction fetch error will not latch the bus address.

For further actions taken see paragraph 3.17.

### 3.7.2. RAM Write Access Protection

In addition to the access protection defined by the fixed memory map in the MEC which will detect any access to unimplemented and illegal addresses, the MEC can be programmed to detect and mask write accesses in any part of the RAM. The protection scheme is enabled *only for data area*, not for the instruction area.

The programmable write access protection is segment based. A segment defines an area where write cycles are allowed. Any write cycle outside a segment is trapped and does not change the memory contents. Two segments are implemented. Each segment is implemented with two registers: the **Segment Base Register** and the **Segment End Register**. The segment base register contains the start address of the segment, and enabling bits for supervisor/user mode (SE/UE). The segment end register contains the first address outside the segment, i.e. last address of segment plus one word. Only word aligned addresses are supported. The segments are only active during RAM access, i.e. they can only be mapped to the RAM area.

If both the SE and UE bits of the **Segment Base Register** are cleared, write protection is effectively disabled for that segment.

### **TSC693E**

The segment access protection can also be used as a block protect function by setting the BP bit in the **MEC Control Register**. The BP bit inverts the address criterion for the protection function so that any access *within* the segment is detected.

If a write access protection error is detected a memory exception is generated and the **SFSR** and **Failing Address Register** is updated as for unimplemented area accesses, see also paragraph 3.17.

In normal mode, (BP=0), a memory exception is generated only if *both* segments indicated a write protection error. In block protect mode (BP=1), a memory exception is generated if *any* of the segments indicate a write protection error.

#### 3.7.3. Boot PROM Write Protection

The MEC supports PROM write only when it is qualified by the external enable signal ROMWRT and the enable bit in the **Memory Configuration Register** (see page 52). The MEC only supports byte write operations for an 8-bit wide PROM and only word write operations for a 40-bit wide PROM.

If a write access to PROM is attempted when any of the above conditions are not fulfilled, the **SFSR** and **Failing Address Register** is updated as for unimplemented area accesses, see also paragraph 3.17.

### 3.8. Register Access Protection

All MEC registers except the UART RX and TX registers are readable in all access modes: user, supervisor, and DMA. The UART RX and TX registers are only readable in supervisor mode. The MEC allows word, halfword and byte accesses when a register is read. The total 32-bit data (together with the parity bit) are thus always issued on the data bus.

All MEC registers which are writeable, are writeable only in supervisor mode or in DMA mode if the CPUHALT\* is active and only as full 32-bit size data write accesses to the registers.

If a register access violation is performed by the IU, the memory exception output is asserted. If a register access violation is performed by the DMA, the memory exception output (MEXC\*) and the DMA access error interrupt output are asserted.

### **3.9. EDAC**

The MEC includes a 32-bit EDAC (Error Detection And Correction). Seven bits (CB[6:0]) are used as check bits over the data bus. The Data Bus Parity Input/Output signal (DPARIO) is used to check and generate the odd parity over the 32-bit data bus. This means that altogether 40 bits are used when the EDAC is enabled.

The MEC EDAC uses a seven bit Hamming code which detects any double bit error on the 40-bit bus as a non-correctable error. In addition, the EDAC detects all bits stuck-atone and stuck-at-zero failure for any nibble in the data word as a non-correctable error. Stuck-at-one and stuck-at-zero for all 32 bits of the data word is also detected as a non-correctable error.

The EDAC corrects any single bit data error on the 40-bit bus. However, in order to correct any error in memory (e.g. Single Event Upset induced) the data has to be read and re-written by software as the MEC does not automatically write back the corrected data.

MATRA MHS Rev. D (10 Apr. 97)

<sup>&</sup>lt;sup>1</sup> A nibble is defined as a bit group of four within the data word, D(3:0), D(7:4) etc.

### 3.9.1. Check Bit Generator

The Check Bit Generator generates the seven check bits plus parity bit that is to be fed to a multiplexer. The output from the multiplexer is either the check bits generated by the Check Bit Generator or the contents of the check bits in the **Test Control register**.

(CB = checkbit, DPARIO = parity bit)

| CB0 = | D31 xor D30 xor D29 xor D28 xor D24 xor D21 xor D20 xor D19 xor      |

|-------|----------------------------------------------------------------------|

|       | D15 xor D11 xor D10 xor D09 xor D08 xor D05 xor D04 xor D01          |

| CB1 = | D30 xor D28 xor D25 xor D24 xor D20 xor D17 xor D16 xor D15 xor      |

|       | D13 xor D12 xor D09 xor D08 xor D07 xor D06 xor D04 xor D03          |

| CB2 = | not (D31 xor D26 xor D22 xor D19 xor D18 xor D16 xor D15 xor D14 xor |

|       | D10 xor D08 xor D06 xor D05 xor D04 xor D03 xor D02 xor D01)         |

| CB3 = | D31 xor D30 xor D27 xor D23 xor D22 xor D19 xor D15 xor D14 xor      |

|       | D13 xor D12 xor D10 xor D09 xor D08 xor D07 xor D04 xor D00          |

| CB4 = | not (D30 xor D29 xor D27 xor D26 xor D25 xor D24 xor D21 xor D19 xor |

|       | D17 xor D12 xor D10 xor D09 xor D04 xor D03 xor D02 xor D00)         |

| CB5 = | D31 xor D26 xor D25 xor D23 xor D21 xor D20 xor D18 xor D14 xor      |

|       | D13 xor D11 xor D10 xor D09 xor D08 xor D06 xor D05 xor D00          |

| CB6 = | D31 xor D30 xor D29 xor D28 xor D27 xor D23 xor D22 xor D19 xor      |

| CB0 - | D18 xor D17 xor D16 xor D15 xor D11 xor D07 xor D02 xor D01          |

|       |                                                                      |

DPARIO = Odd parity over D31 to D0 = not (D31 xor D30 xor .... xor D01 xor D00)

# **TSC693E**

### 3.9.2. Syndrome Generator

The Syndrome Generator generates the internally used and externally observable syndrome bits (SY(7:0)). It uses the read data bits and the eight read check bits. The coding of the syndrome is given below:

| SY7 =         | CB6(Read Data) xor CB5(Read Data) xor not(CB4(Read Data)) xor CB3(Read Data) xor not(CB2(Read Data)) xor CB1(Read Data) xor CB0(Read Data) xor Read Parity |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>SY</b> 6 = | CB6(Read Data) xor Read Checkbit6                                                                                                                          |

| SY5 =         | CB5(Read Data) xor Read Checkbit5                                                                                                                          |

| SY4 =         | CB4(Read Data) xor Read Checkbit4                                                                                                                          |

| SY3 =         | CB3(Read Data) xor Read Checkbit3                                                                                                                          |

| SY2 =         | CB2(Read Data) xor Read Checkbit2                                                                                                                          |

| SY1 =         | CB1(Read Data) xor Read Checkbit1                                                                                                                          |

| SY0 =         | CB0(Read Data) xor Read Checkbit0                                                                                                                          |

### 3.9.3. Syndrome Detector

If there is a correctable error in the read data word, the correction is performed according to the following procedure:

In case of Syndrome(7:0)

### A correctable error is detected if

```

\label{eq:Syndrome} Syndrome (7:0) = "00111000" \mid "010000101" \mid "01010100" \mid "00010110" \mid "00011111" \\ \mid "00100101" \mid "00100110" \mid "01001010" \mid "001011111" \mid "001111011" \\ \mid "00111101" \mid "01100001" \mid "00011010" \mid "00101010" \mid "00101110" \\ \mid "01001111" \mid "01000110" \mid "01010010" \mid "01100100" \mid "01011101" \\ \mid "00100011" \mid "00110001" \mid "01011000" \mid "01101000" \mid "00010011" \\ \mid "00110010" \mid "00110100" \mid "01011000" \mid "010000011" \mid "01010001" \\ \mid "01011011" \mid "01101101" \mid "000000000" \mid "10000001" \mid "10000000" \\ \mid "10000100" \mid "10001000" \mid "10010000" \mid "10100000" \mid "11000000".

```

The non correctable error is detected if

```

Syndrome(7:0) are not equal to "00111000" | "01000101" | "01010100" | "00010110" | "00100101" | "00100101" | "01001010" | "00101111" | "00111101" | "00111101" | "00111101" | "00101110" | "00101110" | "00101110" | "01001111" | "01000110" | "01010010" | "01100100" | "01011101" | "00100011" | "00110001" | "01011000" | "01101000" | "00010011" | "00110010" | "01011010" | "01011000" | "10000001" | "10000001" | "10000000" | "10000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000" | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "1100000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "11000000 | "11000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "110000000 | "1100000000 | "1100000000 | "110000000 | "1100000000 | "1100000000 | "1100000000 | "1100000000 |

```

### 3.9.4. Fault Injection

Moved to paragraph 3.19.

### 3.9.5. Memory and I/O Parity

The MEC handles parity towards memory and I/O in a special way. The MEC can be programmed to use no parity, only parity or parity and EDAC protection towards memory. Towards I/O, the MEC can be programmed to use no parity or only parity.