# 54LS168 Synchronous Bi-Directional **BCD Decade Counter**

# **General Description**

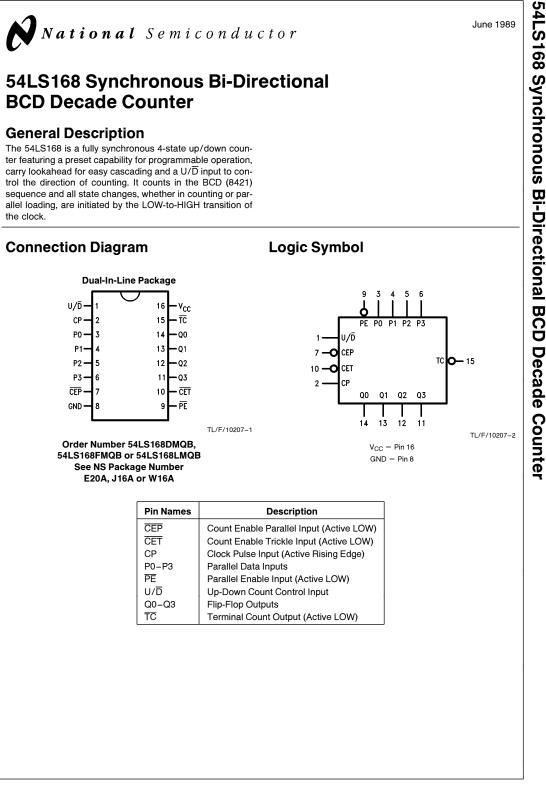

The 54LS168 is a fully synchronous 4-state up/down counter featuring a preset capability for programmable operation, carry lookahead for easy cascading and a  $U/\overline{D}$  input to control the direction of counting. It counts in the BCD (8421) sequence and all state changes, whether in counting or parallel loading, are initiated by the LOW-to-HIGH transition of the clock.

© 1995 National Semiconductor Corporation TL/F/10207 RRD-B30M105/Printed in U. S. A.

June 1989

# Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage                       | 7V                                  |

|--------------------------------------|-------------------------------------|

| Input Voltage                        | 5.5V                                |

| Operating Free Air Temperature Range |                                     |

| 54LS                                 | -55°C to +125°C                     |

| Storage Temperature Range            | $-65^{\circ}$ C to $+150^{\circ}$ C |

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# **Recommended Operating Conditions**

| Symbol                                                                                           | Parameter                  | 54LS168  |     |      | Units |

|--------------------------------------------------------------------------------------------------|----------------------------|----------|-----|------|-------|

| Symbol                                                                                           |                            | Min      | Nom | Max  |       |

| V <sub>CC</sub>                                                                                  | Supply Voltage             | 4.5      | 5   | 5.5  | V     |

| V <sub>IH</sub>                                                                                  | High Level Input Voltage   | 2        |     |      | V     |

| V <sub>IL</sub>                                                                                  | Low Level Input Voltage    |          |     | 0.7  | V     |

| I <sub>OH</sub>                                                                                  | High Level Output Current  |          |     | -0.4 | mA    |

| I <sub>OL</sub> Low Level Output Current                                                         |                            |          |     | 4    | mA    |

| T <sub>A</sub> Free Air Operating Temperature                                                    |                            | -55      |     | 125  | °C    |

| t <sub>s</sub> (H) Setup Time HIGH or LOW   t <sub>s</sub> (L) P <sub>n</sub> , CEP or CET to CP |                            | 15<br>15 |     |      | ns    |

| $t_h$ (H) Hold Time HIGH or LOW $t_h$ (L) $P_n$ , $\overline{CEP}$ or $\overline{CET}$ to CP     |                            | 5<br>5   |     |      | ns    |

| t <sub>s</sub> (H) Setup Time HIGH or LOW<br>t <sub>s</sub> (L) PE to CP                         |                            | 20<br>20 |     |      | ns    |

| th (H) Hold Time HIGH or LOW   th (L) PE to CP                                                   |                            | 0<br>0   |     |      | ns    |

| t <sub>s</sub> (H) Setup Time HIGH or LOW   t <sub>s</sub> (L) U/D to CP                         |                            | 25<br>25 |     |      | ns    |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L)                                                         |                            |          |     | ns   |       |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L)                                                         | CP Pulse Width HIGH or LOW | 20<br>20 |     |      | ns    |

| Symbol          | Parameter                            | Conditions                                                                                                                                        |                  |      | Typ<br>(Note 1) | Мах   | Unite |

|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----------------|-------|-------|

| VI              | Input Clamp Voltage                  | $V_{CC} = Min, I_I = -18 \text{ mA}$                                                                                                              |                  |      |                 | -1.5  | V     |

| V <sub>OH</sub> | High Level Output Voltage            | $\label{eq:V_CC} \begin{split} V_{CC} &= \text{Min}, \text{I}_{OH} = \text{Max}, \\ V_{IL} &= \text{Max}, \text{V}_{IH} = \text{Min} \end{split}$ | 2.5              |      |                 | v     |       |

| V <sub>OL</sub> | Low Level Output Voltage             | $\label{eq:V_CC} \begin{split} V_{CC} &= \text{Min}, \text{I}_{OL} = \text{Max}, \\ V_{IH} &= \text{Min}, \text{V}_{IL} = \text{Max} \end{split}$ |                  |      | 0.4             | v     |       |

| I               | Input Current @ Max<br>Input Voltage | $V_{CC} = Max, V_I = 10.0V$                                                                                                                       |                  |      | 0.1             | mA    |       |

| IIH             | High Level Input Current             | $V_{CC} = Max, V_I = 2.7V$                                                                                                                        | Inputs           |      |                 | 20    | μA    |

|                 |                                      |                                                                                                                                                   | CET              |      |                 | 40    | μ     |

| IL              | Low Level Input Current              | $V_{CC} = Max, V_I = 0.5V$                                                                                                                        | Data             | -0.5 |                 | -400  |       |

|                 |                                      |                                                                                                                                                   | CP, PE, U/D, CEP | -30  |                 | -400  | μΑ    |

|                 |                                      |                                                                                                                                                   | CET              | -60  |                 | -800  |       |

| los             | Short Circuit Output Current         | V <sub>CC</sub> = Max (Note 2)                                                                                                                    |                  | -20  |                 | - 100 | mA    |

| lcc             | Supply Current                       | V <sub>CC</sub> = Max (Note 3)                                                                                                                    |                  |      |                 | 34    | mA    |

Note 1: All typicals are at V\_{CC} = 5V, T\_A = 25 ^{\circ}C.

Note 2: Not more than one output should be shorted at a time, and the duration should not exceed one second. Note 3:  $I_{CC}$  is measured with all outputs open and all inputs grounded.

Switching Characteristics  $V_{CC} = +5.0V$ ,  $T_A = +25^{\circ}C$  (See Section 1 for test waveforms and output load)

|                                      |                                           | 54L                    |          |       |

|--------------------------------------|-------------------------------------------|------------------------|----------|-------|

| Symbol                               | Parameter                                 | C <sub>L</sub> = 15 pF |          | Units |

|                                      |                                           | Min                    | Мах      |       |

| f <sub>Max</sub>                     | Maximum Clock Frequency                   | 25                     |          | MHz   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to Q <sub>n</sub> |                        | 20<br>20 | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CP to $\overline{TC}$   | 30<br>30               | ns       |       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CET to TC            |                        |          | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>U/D to TC            |                        | 25<br>25 | ns    |

3

# **Functional Description**

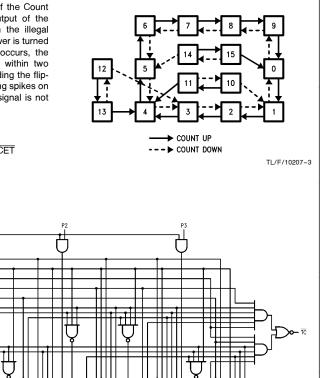

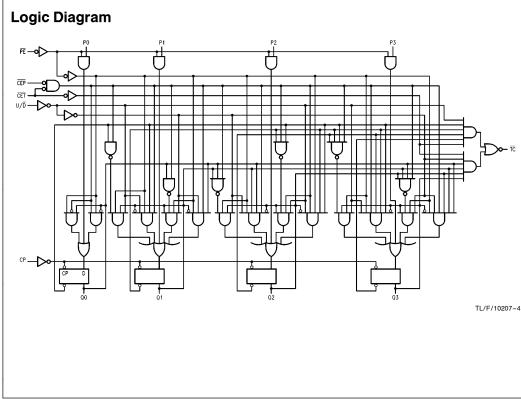

The 'LS168 uses edge-triggered D-type flip-flops and has no constraints on changing the control or data input signals in either state of the Clock. The only requirement is that the various inputs attain the desired state at least a setup time before the rising edge of the clock and remain valid for the recommended hold time thereafter. The parallel load operation takes precedence over the other operations, as indicated in the Mode Select Table. When  $\overline{PE}$  is LOW, the data on the P0–P3 inputs enters the flip-flops on the next rising edge of the Clock. In order for counting to occur, both  $\overrightarrow{\text{CEP}}$ and  $\overline{\text{CET}}$  must be LOW and  $\overline{\text{PE}}$  must be HIGH. The U/D input then determines the direction of counting. The Terminal Count (TC) output is normally HIGH and goes LOW, provided that CET is LOW, when a counter reaches zero in the COUNT DOWN mode or reaches 9 in the COUNT UP mode. The  $\overline{\text{TC}}$  output state is not a function of the Count Enable Parallel  $(\overline{CEP})$  input level. The  $\overline{TC}$  output of the 'LS168 decade counter can also be LOW in the illegal states 11, 13 and 15, which can occur when power is turned on or via parallel loading. If an illegal state occurs, the 'LS168 will return to the legitimate sequence within two counts. Since the  $\overline{\text{TC}}$  signal is derived by decoding the flipflop states, there exists the possibility of decoding spikes on  $\overline{\text{TC}}.$  For this reason the use of  $\overline{\text{TC}}$  as a clock signal is not recommended (see logic equation below). 1. Count Enable =  $\overline{\text{CEP}} \bullet \overline{\text{CET}} \bullet \overline{\text{PE}}$

2. Up:

$$\overline{TC} = Q0 \bullet Q3 \bullet (U/\overline{D}) \bullet \overline{CET}$$

3. Down:  $\overline{TC} = Q0 \bullet Q1 \bullet Q2 \bullet Q3 \bullet (U/\overline{D}) \bullet \overline{CET}$

### 'LS168 Mode Select Table

| PE | CEP | CET | U/D | Action on Rising Clock Edge                            |

|----|-----|-----|-----|--------------------------------------------------------|

| L  | х   | Х   | х   | Load ( $P_n \rightarrow Q_n$ )                         |

| н  | L   | L   | Н   | Load ( $P_n \rightarrow Q_n$ )<br>Count Up (Increment) |

| н  | L   | L   | L   | Count Down (Decrement)                                 |

| н  | н   | x   | х   | No Change (Hold)                                       |

| н  | x   | н   | Х   | No Change (Hold)                                       |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

### State Diagram

4

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications