# IXLD02SI

#### Differential 2A Ultra Fast Laser Diode Driver

#### **Features**

- · Ultra Fast Pulsed Current Source

- High Output Currents >2A Peak

- 17MHz Max Operating Frequency

- <1.5ns Minimum Pulse Width

- 600ps Rise And Fall Times

- · Pulse Width and Frequency Agile

- Real Time Electronic Programming of Current and Pulse Width

- Low Inductance High Power Package Design

- Simultaneous Frequency, Pulse Width and Amplitude Modulation

#### **Applications**

- · High Speed Laser Diode Drivers

- · High Power Ultra Fast Line Drivers

- Differential Power Drivers

- · High Power Pulse Generators

- High Speed High Frequency Modulators

### **General Description**

The IXLD02 is an ultra high-speed differential laser diode driver. The IXLD02 is designed specifically to drive single junction laser diodes in a differential fashion. A Q output and a Q-Bar output are provided via a low inductance multi-pin topology. These two signals make their transitions at the same time with transition times in the picoseconds. This technique provides the highest possible slew rate across the diode. In addition the IXLD02 is capable of currents exceeding 2A.

These performance features are combined with frequency agility to a maximum operating frequency of 17MHz, a minimum pulse width of <1.5ns and rise and fall times of approximately 600ps. In addition, the pulse width and the current programming can be modulated in real time to >10MHz. The IXLD02 is assembled in a high power SO-28 surface mount package.

For additional operational instructions, see the IXLD02 Evaluation Board application note on the DEI web site at www.directedenergy.com

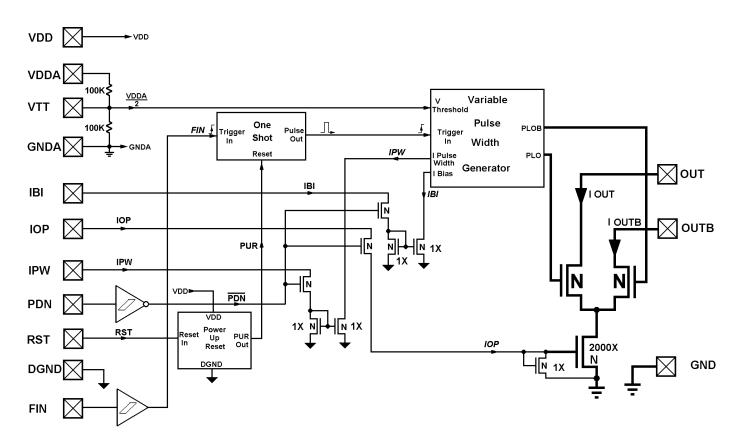

Figure 1 - Functional Diagram

## **Absolute Maximum Ratings** (Note 1)

| Name              | Definition                                      | Min  | Тур    | Max       | Units | Test Conditions                                                   |

|-------------------|-------------------------------------------------|------|--------|-----------|-------|-------------------------------------------------------------------|

| VDD               | Logic supply input voltage                      | -0.4 |        | 5.5       | V     |                                                                   |

| VDDA              | Analog bias supply input voltage                | -0.4 |        | 5.5       | V     |                                                                   |

| VTT               | Internal bias voltage input                     | -0.4 | VDDA/2 | VDDA+.5   | V     |                                                                   |

| IBI               | Internal bias current input                     | -10  | 0.1    | 10        | mA    |                                                                   |

| $V_{IBI}$         | Applied IBI terminal voltage                    | -0.4 |        | VDDin+0.5 | V     |                                                                   |

| IPW               | Pulse width programming current input           | -10  | 0.1    | 10        | mA    |                                                                   |

| $V_{IPW}$         | Applied IPW terminal voltage                    | -0.4 |        | VDDin+0.5 | V     |                                                                   |

| IOP               | Output current programming input                | -10  | 1      | 10        | mA    |                                                                   |

| $V_{IOP}$         | Applied IOP terminal voltage                    | -0.4 |        | VDDin+0.5 | V     |                                                                   |

| $V_{PDN}$         | Power-down logic input                          | -0.4 |        | VDDin+0.5 | V     |                                                                   |

| $V_{RST}$         | Reset logic input                               | -0.4 |        | VDDin+0.5 | V     |                                                                   |

| $V_{FIN}$         | Pulse frequency logic input                     | -0.4 |        | VDDin+0.5 | V     |                                                                   |

| $V_{OUT}$         | Pulse current true output                       | -0.1 |        | 3         | Amps  |                                                                   |

| $V_{OUT}$         | OUT terminal voltage                            | -0.4 |        | 9         | V     |                                                                   |

| ОИТВ              | Pulse current complement output                 | -0.1 |        | 3         | Amps  |                                                                   |

| $V_{OUTB}$        | OUTB terminal voltage                           | -0.4 |        | 9         | V     |                                                                   |

| T <sub>C</sub>    | Device Case Temperature                         | -40  | 25     | 85        | °C    | Measured at the bottom of the SO28 package heat slug insert.      |

| $P_{D}$           | Package power dissipation @ T <sub>c</sub> =85C |      |        | 32        | Watts | SO28 package<br>heat slug insert<br>held at T <sub>C</sub> =85°C. |

| R <sub>THJC</sub> | Thermal resistance, junction to case            |      |        | 2         | °C/W  |                                                                   |

| T <sub>J</sub>    | Junction Temperature                            |      |        | 150       | °C    |                                                                   |

| Ts                | Storage temperature                             | -55  |        | 150       | °C    |                                                                   |

| T <sub>L</sub>    | Lead temperature (soldering, 10 sec)            |      |        | 300       | °C    |                                                                   |

**Note 1:** Operating the device beyond parameters with listed "Absolute Maximum Ratings" may cause permanent damage to the device. Typical values indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. The guaranteed specifications apply only for the test conditions listed. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper ESD procedures when handling and assembling this component.

| Ordering Information |              |                |            |  |  |

|----------------------|--------------|----------------|------------|--|--|

| Part Number          | Package Type | Temp. Range    | Grade      |  |  |

| IXLD02SI             | 28-Pin SOIC  | -40°C to +85°C | Industrial |  |  |

# Recommended Operating Conditions Unless otherwise noted, VDD=VDDA=5V, $T_c$ =25C

| Name                             | Definition                                                                                                       | Min     | Тур             | Max    | Units | Test Conditions                                                                                                        |

|----------------------------------|------------------------------------------------------------------------------------------------------------------|---------|-----------------|--------|-------|------------------------------------------------------------------------------------------------------------------------|

| VDD                              | Logic supply input voltage                                                                                       | 4.5     |                 | 5.5    | V     |                                                                                                                        |

|                                  | Analog bias supply input voltage                                                                                 | 4.5     |                 | 5.5    | V     |                                                                                                                        |

|                                  | Internal bias voltage input                                                                                      | 2       | VDDA/2          | 3      | V     | Measured with Zin>10meg DVM.                                                                                           |

| $R_{VTT}$                        | VTT terminal resistance                                                                                          | 30      | 50              | 70     | Kohms | Measured with VDDin=VDDA=0V.                                                                                           |

| I <sub>IBI</sub>                 | Internal bias current input range                                                                                | 10      | 100             | 300    | uA    | External current source between VDDA and IBI terminal.                                                                 |

| $V_{IBI}$                        | Measured IBI terminal voltage                                                                                    | 0.6     |                 | 1.7    | V     | I <sub>IBI</sub> =100uA.                                                                                               |

| I <sub>IPW</sub>                 | Pulse width programming current input range.                                                                     | -1      | 100             | 400    | uA    | External current source between VDDA and IPW terminal.                                                                 |

| $V_{\text{IPW}}$                 | Measured IPW terminal voltage                                                                                    | 0.6     |                 | 1.7    | V     | I <sub>IPW</sub> =100uA.                                                                                               |

| t <sub>PW</sub>                  | I <sub>OUT</sub> =2A peak, Output current pulse width                                                            |         | 1               |        | ns    | I <sub>IBI</sub> =400uA, I <sub>IPW</sub> =300uA, I <sub>IOP</sub> =1mA.                                               |

| I <sub>IOP</sub>                 | OUT and OUTB output current, I <sub>OUT</sub> , programming current.                                             | 0       | 1               | 3      | mA    | External current source between VDDA and IBI terminals.                                                                |

| $V_{IOP}$                        | Measured IOP terminal voltage                                                                                    | 0.6     |                 | 1.7    | V     | IBI=100uA.                                                                                                             |

| <sub>OUT</sub> /I <sub>IOP</sub> | Output current to programming current gain                                                                       | 1800    | 2000            | 2200   | 1/1   | I <sub>IOP</sub> =1mA, V <sub>OUT</sub> =V <sub>OUTB</sub> =10V.                                                       |

| V <sub>IH</sub>                  | Logic input high threshold for PDN, RST, & FIN inputs.                                                           | 0.7*VDD |                 |        | V     |                                                                                                                        |

| V <sub>IL</sub>                  | Logic input high threshold for PDN, RST, & FIN inputs.                                                           |         |                 | .3*VDD | V     |                                                                                                                        |

| I <sub>LIN</sub>                 | Logic input bias current for PDN, RST, & FIN inputs.                                                             | -10     |                 | 10     | uA    | For logic inputs, PDN, RST, & FIN held at:-0.5V <v<sub>LIN<vdd< td=""></vdd<></v<sub>                                  |

| t <sub>PDN</sub>                 | IXLD02 power down delay, V <sub>PDN</sub> logical low to high transition.                                        |         | 50              |        | ns    |                                                                                                                        |

|                                  | IXLD02 power up delay, V <sub>PDN</sub> logical high to low transition.                                          |         | 30              |        | ns    |                                                                                                                        |

| t <sub>RST</sub>                 | IXLD02 reset logic delay, V <sub>RST</sub> logical low to high transition.                                       |         | 100             |        | ns    |                                                                                                                        |

|                                  | IXLD02 reset logic delay, V <sub>RST</sub> logical low to high transition.                                       |         | 100             |        | ns    |                                                                                                                        |

| t <sub>FIN</sub>                 | IXLD02 pulse frequency input, V <sub>FIN</sub> , logical low to high transition to I <sub>OUT</sub> pulse delay. |         | 50              |        | ns    | I <sub>IBI</sub> =400uA, I <sub>IPW</sub> =300uA, I <sub>IOP</sub> =1mA                                                |

| f <sub>FINmax</sub>              | Maximum pulse frequency, FIN, logic input.                                                                       | 17      |                 |        | MHz   | I <sub>IBI</sub> =400uA, I <sub>IPW</sub> =300uA, I <sub>IOP</sub> =1mA                                                |

|                                  | Peak true pulse current output.                                                                                  | 1.6     | 2               | 2.4    | Amps  | I <sub>IBI</sub> =400uA, I <sub>IPW</sub> =300uA, I <sub>IOP</sub> =1mA.,<br>V <sub>OUT</sub> =V <sub>OUTB</sub> =10V. |

|                                  | Rise time                                                                                                        |         | 600             |        | ps    |                                                                                                                        |

| $t_{F}$                          | Fall time                                                                                                        |         | 600             |        | ps    |                                                                                                                        |

| T <sub>ONDLY</sub>               | On-time propagation delay                                                                                        |         | 30              |        | ns    |                                                                                                                        |

|                                  | Off-time propagation delay                                                                                       |         | 30              |        | ns    |                                                                                                                        |

| $P_{Wmax}$                       | Pulse width maximum                                                                                              |         | >1              |        | us    |                                                                                                                        |

| Tj                               | Jitter                                                                                                           |         | <u>&lt;</u> 300 |        | ps    |                                                                                                                        |

| V <sub>OUT</sub>                 | OUT terminal voltage                                                                                             | 8       |                 | 12     | V     | I <sub>IBI</sub> =400uA, I <sub>IPW</sub> =300uA, I <sub>IOP</sub> =1mA, 1.4A <i<sub>OUT&lt;2.6A peak.</i<sub>         |

| I <sub>OUTB</sub>                | Minimum complement pulse current output.                                                                         | 0       | 0.2             | 0.4    | Amps  | I <sub>IBI</sub> =400uA, I <sub>IPW</sub> =300uA, I <sub>IOP</sub> =1mA.,<br>V <sub>OUT</sub> =V <sub>OUTB</sub> =10V. |

| $V_{\text{OUTB}}$                | OUTB terminal voltage                                                                                            | 8       |                 | 12     | V     | $I_{\text{IBI}}$ =400uA, $I_{\text{IPW}}$ =300uA, $I_{\text{IOP}}$ =1mA, 0A< $I_{\text{OUT}}$ <0.6A minimum.           |

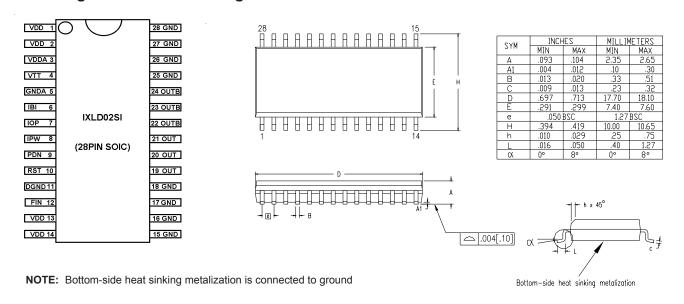

# **Pin Configurations And Package Outline**

## **Pin Description**

| Pins                                    | Name | Description                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2,<br>13, 14                          | VDD  | This pin is a high current, low inductance pin designed to accept peaks of 2Amps at 5V.                                                                                                                                                                                                                                                              |

| 3                                       | VDDA | This is a low current analog power input. Circuit components sensitive to the noise present on VDD in are supplied by this pin.                                                                                                                                                                                                                      |

| 4                                       | VTT  | This pin is the 1/2VDDA internal analog comparator reference point.                                                                                                                                                                                                                                                                                  |

| 5                                       | GNDA | Low current, low noise analog return. Noise sensitive circuit components are returned here.                                                                                                                                                                                                                                                          |

| 6                                       | IBI  | The current, $I_{\text{IBI}}$ , flowing into the IBI pin acts as a baseline current with respect to $I_{\text{IPW}}$ current to compensate for internal delays. See Figure 2.                                                                                                                                                                        |

| 7                                       | IOP  | A current, I <sub>IOP</sub> , into the IOP pin programs the laser diode output<br>switches, pin 19 through pin 24. The program ratio is 1:1000X. This<br>means a 1mA current will produce 1Amp. See Figure 2.                                                                                                                                        |

| 8                                       | IPW  | A current, $I_{IPW}$ , flowing into the IPW pin determines the output current pulse width, $t_{PW}$ , with respect to $I_{IBI}$ . If $I_{IPW}$ = $I_{IBI}$ , the pulse width is 0. As $I_{IPW}$ approaches $I_{IBI}$ but less than $I_{IBI}$ , the pulse width becomes nonzero. See Figure 2 for $t_{PW}$ as a function of $I_{IBI}$ and $I_{IPW}$ . |

| 9                                       | PDN  | A TTL high on this pin will power down the device so that only leakage current will flow from VDD to DGND. A TTL low will turn on the device within 30ns. See Figure 3.                                                                                                                                                                              |

| 10                                      | RST  | A system reset pin, which initializes the device so that it starts in a predetermined initial state.                                                                                                                                                                                                                                                 |

| 11                                      | DGND | This pin is the return for the input logic, $I_{\rm IBI}$ , $I_{\rm IOP}$ , and $I_{\rm IPW}$ currents. It is internally connected to the other grounds, AGND or GND, through the substrate.                                                                                                                                                         |

| 12                                      | FIN  | With PDN low, a positive edge of a TTL compatible signal here will produce the pulse current output available at the OUT and a complement of it at OUTb pins. Refer to Figure 3 for FIN and PDN timing.                                                                                                                                              |

| 15, 16,<br>17, 18,<br>25, 26,<br>27, 28 | GND  | Output ground pins designed for low inductance.                                                                                                                                                                                                                                                                                                      |

| 19, 20.<br>21                           | OUT  | True laser diode drive output current. Designed for low inductance and output voltage compliance to +12V.                                                                                                                                                                                                                                            |

| 22, 23,<br>24                           | OUTb | Complementary laser diode drive output current. Designed for low inductance and output voltage compliance to +12V.                                                                                                                                                                                                                                   |

400 uA I<sub>IBI</sub>=400uA 200 uA I<sub>IBI</sub>+200uA 100uA l<sub>IBI</sub>≡100uA 40uA 20uA 10uA 4uA 2uA 1uA 1ns 10ns 40ns 100ns 400ns 0.1ns 0.4ns 4ns

Figure 2 - Programmed  $I_{OUT}$  pulse width,  $t_{PW}$  as a function of  $I_{IPW}$  and  $I_{IBI}$

Figure 2 is an illustration of the pulse width vs. programming current. The programming current is typically a DC level, however it could just as well be a time varying signal. The bandwidth of this portion of the IXLD02 is equivalent to the maximum operating frequency of 17MHz. For the fastest response time this pin should be driven from a low source impedance.

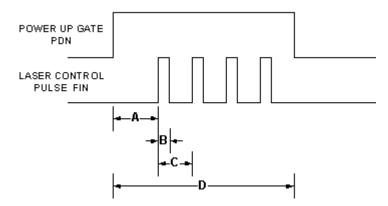

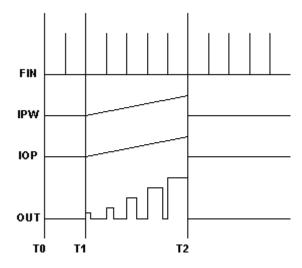

Figure 3 - Control Gate Timing Diagram

Figure 3 is a timing chart for the IXLD02. The proper gating of the IXLD02 is extremely important. The device is capable of 2A of current and may consume in excess of 3A during the pulse. If the supply voltage is at 7V with 3A of current, the total power dissipated is 21W. Therefore ample heat sinking must be provided, and/or the duty cycle must be limited so that the power dissipation capability of the device is not exceeded.

The Power Up Gate (PDN) is applied to activate the device. Time interval " $\bf A$ " can be >30ns. At the end of this time period the control gate " $\bf B$ " (FIN), can be applied. The range of " $\bf B$ " is from 1ns to several  $\mu s$ . The maximum frequency 1/C is approximately 17MHz.

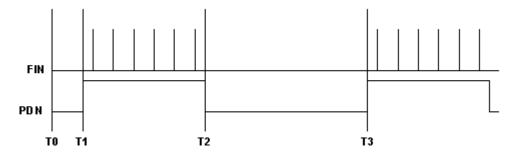

Figure 4 - Duty Cycle

Figure 4 illustrates the Duty Cycle (DC), FIN and PDN relation ships. The PDN command must be in a TTL "High" state 30ns prior to the first FIN pulse. It must stay in this state for the duration of the laser light burst, T1 to T2.

The Duty cycle is defined as:  $DC = \frac{T2 - T1}{T3 - T1}$

Power in the IC is: Total dc Power X DC

Figure 5 - IPW And IOP Modulation

Figure 5 illustrates the simultaneous modulation of both the IPW control current and the IOP control current. The FIN frequency in this figure is held constant. At T0 the IPW and the IOP signals are near zero, both begin to ramp up at T1 and reach their maximums at T2. As illustrated, the output current rises in amplitude with the increasing IOP and the pulse width widens with the IPW ramp.

An additional mode of modulation can be added to the two above by also modulating the frequency of the FIN signal. This will allow three mode of simultaneous modulation. The three modes do not have to be used together; each is fully independent. The obvious caveat is that the pulse width must be consistent with the chosen frequency. This agility provides the designer with a broad range of design choices.

Directed Energy, Inc. An IXYS Company 2401 Research Blvd. Ste. 108 Ft. Collins, CO 80526

Tel: 970-493-1901; Fax: 970-493-1903 e-mail: deiinfo@directedenergy.com

www.directedenergy.com

Doc #9200-0258 Rev 2