### **INTEGRATED CIRCUITS**

## DATA SHEET

### **SAA5288**

TV microcontroller with full screen On Screen Display (OSD)

Preliminary specification File under Integrated Circuits, IC02 1997 Jun 24

**SAA5288**

| CONTEN                     | NTS                                                 | 7.9          | Cursor                                          |

|----------------------------|-----------------------------------------------------|--------------|-------------------------------------------------|

| 1                          | FEATURES                                            | 7.10<br>7.11 | Other display features                          |

| 1.1                        | General                                             | 7.11<br>7.12 | Display timing<br>Horizontal timing             |

| 1.1                        | Microcontroller                                     | 7.12         | Vertical timing                                 |

| 1.3                        | Display                                             | 7.14         | Display position                                |

| 2                          | GENERAL DESCRIPTION                                 | 7.15         | Clock generator                                 |

| 3                          | QUICK REFERENCE DATA                                | 8            | CHARACTER SETS                                  |

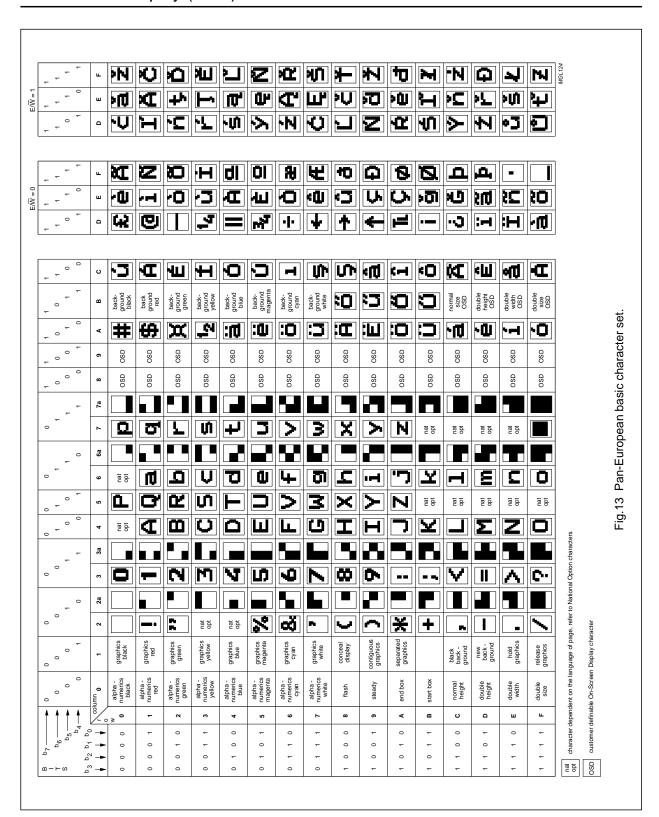

|                            |                                                     | 8.1          | Pan-European                                    |

| 4                          | ORDERING INFORMATION                                | 8.2          | Russian                                         |

| 5                          | BLOCK DIAGRAM                                       | 8.3          | Greek/Turkish                                   |

| 6                          | PINNING INFORMATION                                 | 8.4          | Arabic/English/French                           |

| 6.1                        | Pinning                                             | 8.5          | Thai                                            |

| 6.2                        | Pin description                                     | 8.6          | Arabic/Hebrew                                   |

| 7                          | FUNCTIONAL DESCRIPTION                              | 9            | LIMITING VALUES                                 |

| 7.1                        | Microcontroller                                     | 10           | CHARACTERISTICS                                 |

| 7.2                        | 80C51 features not supported                        | 11           | CHARACTERISTICS FOR THE I <sup>2</sup> C-BUS    |

| 7.2.1                      | Interrupt priority                                  |              | INTERFACE                                       |

| 7.2.2                      | Off-chip memory                                     | 12           | QUALITY SPECIFICATIONS                          |

| 7.2.3                      | Idle and Power-down modes                           | 13           | APPLICATION INFORMATION                         |

| 7.2.4                      | UART function                                       |              |                                                 |

| 7.3                        | Additional features                                 | 14           | EMC GUIDELINES                                  |

| 7.3.1<br>7.3.2             | Interrupts Bit Level I <sup>2</sup> C-bus Interface | 15           | PACKAGE OUTLINE                                 |

| 7.3.2                      | Byte Level I <sup>2</sup> C-bus Interface           | 16           | SOLDERING                                       |

| 7.3.4                      | LED support                                         | 16.1         | Introduction                                    |

| 7.3.5                      | 6-bit PWM DACs                                      | 16.2         | Soldering by dipping or by wave                 |

| 7.3.6                      | 14-bit PWM DAC                                      | 16.3         | Repairing soldered joints                       |

| 7.3.7                      | Software ADC                                        | 17           | DEFINITIONS                                     |

| 7.4                        | Microcontroller Interfacing                         | 18           | LIFE SUPPORT APPLICATIONS                       |

| 7.4.1                      | Special Function Register map                       | _            |                                                 |

| 7.4.2                      | Special Function Registers bit description          | 19           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS |

| 7.5                        | The display                                         |              |                                                 |

| 7.5.1                      | Introduction                                        |              |                                                 |

| 7.5.2                      | Character matrix                                    |              |                                                 |

| 7.5.3<br>7.5.4             | Page attributes East/west selection                 |              |                                                 |

| 7.5. <del>4</del><br>7.5.5 | National option characters                          |              |                                                 |

| 7.6                        | The twist attribute                                 |              |                                                 |

| 7.6.1                      | On screen display symbols                           |              |                                                 |

| 7.6.2                      | Language group identification                       |              |                                                 |

| 7.6.3                      | 525-line operation                                  |              |                                                 |

| 7.6.4                      | Control characters                                  |              |                                                 |

| 7.6.5                      | Display modes                                       |              |                                                 |

| 7.7                        | On Screen Display boxes                             |              |                                                 |

| 7.8                        | Screen colour                                       |              |                                                 |

## TV microcontroller with full screen On Screen Display (OSD)

**SAA5288**

### 1 FEATURES

#### 1.1 General

- On-chip TV control tuning

- Hardware and software compatible with SAA5290, SAA5291 and SAA5296

- Single +5 V power supply

- RGB interface to standard decoder ICs, push-pull output drive

- SDIP52 package

- Single crystal oscillator for display and microcontroller.

#### 1.2 Microcontroller

- 80C51 microcontroller core

- 16 kbyte mask programmed ROM

- 256 bytes of microcontroller RAM

- Eight 6-bit Pulse Width Modulator (PWM) outputs for control of TV analog signals

- One 14-bit PWM for Voltage Synthesis tuner control

- Four 8-bit Analog-to-Digital Converters (ADCs)

- 2 high current open-drain outputs for directly driving LED's etc.

- Switchable bit or byte-oriented I<sup>2</sup>C-bus interface.

### 1.3 Display

- Single page (1024 x 8) on-board On Screen Display (OSD) memory

- Double size width and height capability for OSD

- Enhanced display features including meshing, shadowing and additional display attributes

- 260 characters in mask programmed ROM

- Display clock derived internally to reduce peripheral components to a minimum

- · Automatic FRAME output control with manual override

- Standby mode for display hardware

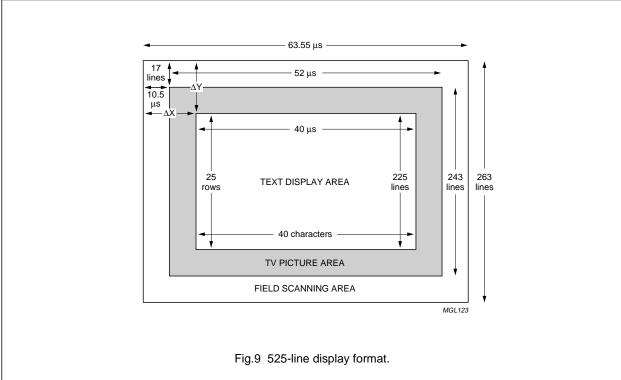

- 525-line and 625-line display

- 12 × 10 character matrix

- Stable Display via slave synchronization to Horizontal Sync and Vertical Sync.

### 2 GENERAL DESCRIPTION

The SAA5288 is a microcontroller for use in televisions with an OSD generator compatible with the Economy Teletext/TV microcontroller family (SAA5290, SAA5291, SAA5296 etc.). TV control facilities are provided by an on-chip industry standard 80C51 microcontroller and a 1 kbyte DRAM is included for OSD memory.

Hardware and software compatibility with the Economy Teletext/TV microcontroller family minimizes the changes required to develop a TV control function for areas where teletext is not broadcast.

The device cannot acquire Teletext but is based on a Teletext device. Therefore, throughout this document references are made to Teletext especially when describing the Display/OSD section. The Display/OSD section is fully compatible with a Teletext display and has all the features associated with Teletext (i.e. double height/width, flash, teletext boxes, graphics, etc.). The Display section is described with reference to Teletext to allow software compatibility with the Economy Teletext/TV microcontroller family.

### 3 QUICK REFERENCE DATA

| SYMBOL            | PARAMETER                      | MIN. | TYP. | MAX. | UNIT |

|-------------------|--------------------------------|------|------|------|------|

| $V_{DD}$          | supply voltage (all supplies)  | 4.5  | 5.0  | 5.5  | V    |

| I <sub>DDM</sub>  | microcontroller supply current | _    | 15   | 30   | mA   |

| I <sub>DDA</sub>  | analogue supply current        | _    | 8    | 15   | mA   |

| I <sub>DDT</sub>  | display supply current         | _    | 15   | 30   | mA   |

| f <sub>xtal</sub> | crystal frequency              | _    | 12   | _    | MHz  |

| T <sub>amb</sub>  | operating ambient temperature  | -20  | _    | +70  | °C   |

# TV microcontroller with full screen On Screen Display (OSD)

**SAA5288**

### 4 ORDERING INFORMATION

| TYPE NUMBER   |        | PACKAGE     |         |  |  |  |

|---------------|--------|-------------|---------|--|--|--|

| TIPE NOWIBER  | NAME   | DESCRIPTION | VERSION |  |  |  |

| SAA5288PS/nnn | SDIP52 | SOT247-1    |         |  |  |  |

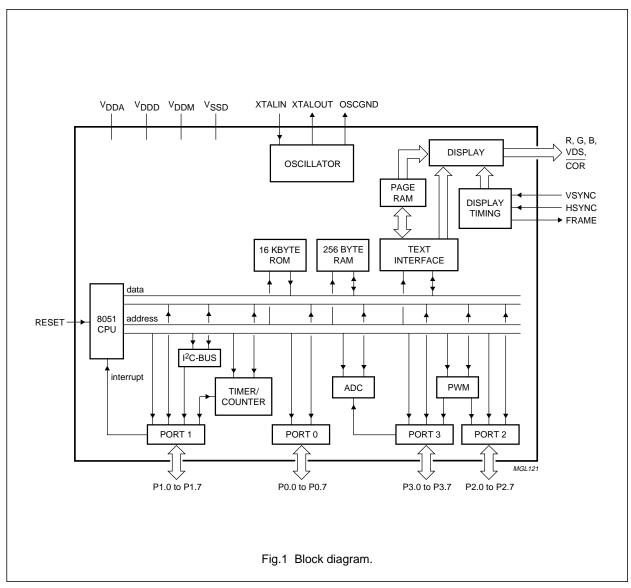

### 5 BLOCK DIAGRAM

**SAA5288**

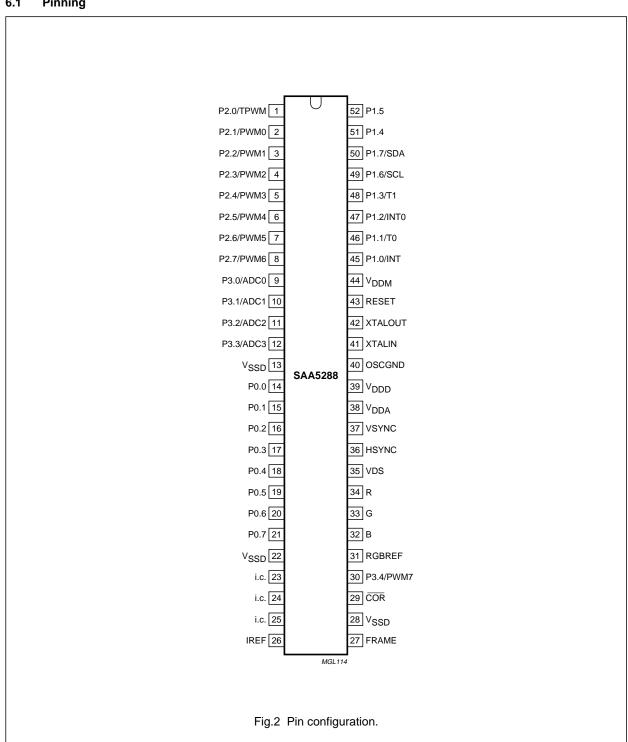

#### PINNING INFORMATION 6

#### 6.1 **Pinning**

1997 Jun 24 5

# TV microcontroller with full screen On Screen Display (OSD)

**SAA5288**

### 6.2 Pin description

Table 1 SDIP52 package

| SYMBOL           | PIN | DESCRIPTION                                                                                                      |

|------------------|-----|------------------------------------------------------------------------------------------------------------------|

| P2.0/TPWM        | 1   | Port 2. 8-bit open-drain bidirectional port with alternative functions.                                          |

| P2.1/PWM0        | 2   | P2.0/TPWM is the output for the 14-bit high precision PWM.                                                       |

| P2.2/PWM1        | 3   | P2.1/PWM0 to P2.7/PWM6 are the outputs for the 6-bit PWMs 0 to 6.                                                |

| P2.3/PWM2        | 4   | 1 2.1/1 Willio to 1 2.1/1 Willio are the outputs for the o-bit 1 Willis o to 0.                                  |

| P2.4/PWM3        | 5   |                                                                                                                  |

| P2.5/PWM4        | 6   |                                                                                                                  |

| P2.6/PWM5        | 7   |                                                                                                                  |

| P2.7/PWM6        | 8   |                                                                                                                  |

| P3.0/ADC0        | 9   | Port 3. 8-bit open-drain bidirectional port with alternative functions.                                          |

| P3.1/ADC1        | 10  | P3.0/ADC0 to P3.3/ADC3 are the inputs for the software ADC facility.                                             |

| P3.2/ADC2        | 11  | P3.4/PWM7 is the output for the 6-bit PWM7.                                                                      |

| P3.3/ADC3        | 12  | 1 3.4/1 WWIT IS the output for the o-bit I WWIT.                                                                 |

| P3.4/PWM7        | 30  |                                                                                                                  |

| V <sub>SSD</sub> | 13  | Digital ground                                                                                                   |

| P0.0             | 14  | Port 0. 8-bit open-drain bidirectional port.                                                                     |

| P0.1             | 15  | P0.5 and P0.6 have 10 mA current sinking capability for direct drive of LEDs.                                    |

| P0.2             | 16  |                                                                                                                  |

| P0.3             | 17  |                                                                                                                  |

| P0.4             | 18  |                                                                                                                  |

| P0.5             | 19  |                                                                                                                  |

| P0.6             | 20  |                                                                                                                  |

| P0.7             | 21  |                                                                                                                  |

| V <sub>SSD</sub> | 22  | Digital ground.                                                                                                  |

| i.c.             | 23  | Internally connected; this pin should be connected to digital ground.                                            |

| i.c.             | 24  | Internally connected; this pin should be connected to digital ground.                                            |

| i.c.             | 25  | Internally connected; this pin should be connected to digital ground.                                            |

| IREF             | 26  | Reference current input for analog current generator, connected to $V_{\text{SSA}}$ via a 27 $k\Omega$ resistor. |

**SAA5288**

| SYMBOL           | PIN | DESCRIPTION                                                                                                                                                                                                   |  |  |  |  |

|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| FRAME            | 27  | De-interlace output synchronised with the VSYNC pulse to produce a non-interlaced display by adjustment of the vertical deflection circuits.                                                                  |  |  |  |  |

| V <sub>SSD</sub> | 28  | Internally connected; this pin should be connected to digital ground.                                                                                                                                         |  |  |  |  |

| COR              | 29  | Open-drain, active LOW output which allows selective contrast reduction of the TV picture to enhance a mixed mode display.                                                                                    |  |  |  |  |

| RGBREF           | 31  | DC input voltage to define the output HIGH level on the RGB pins.                                                                                                                                             |  |  |  |  |

| В                | 32  | Pixel rate output of the BLUE colour information.                                                                                                                                                             |  |  |  |  |

| G                | 33  | Pixel rate output of the GREEN colour information.                                                                                                                                                            |  |  |  |  |

| R                | 34  | Pixel rate output of the RED colour information.                                                                                                                                                              |  |  |  |  |

| VDS              | 35  | Video/data switch push-pull output for dot rate fast blanking.                                                                                                                                                |  |  |  |  |

| HSYNC            | 36  | Schmitt trigger input for a TTL level version of the horizontal sync pulse; the polarity of this pulse is programmable by register bit TXT1.H POLARITY.                                                       |  |  |  |  |

| VSYNC            | 37  | Schmitt trigger input for a TTL level version of the vertical sync pulse; the polarity of this pulse is programmable by register bit TXT1.V POLARITY.                                                         |  |  |  |  |

| $V_{DDA}$        | 38  | +5 V display power supply.                                                                                                                                                                                    |  |  |  |  |

| $V_{DDD}$        | 39  | +5 V display power supply.                                                                                                                                                                                    |  |  |  |  |

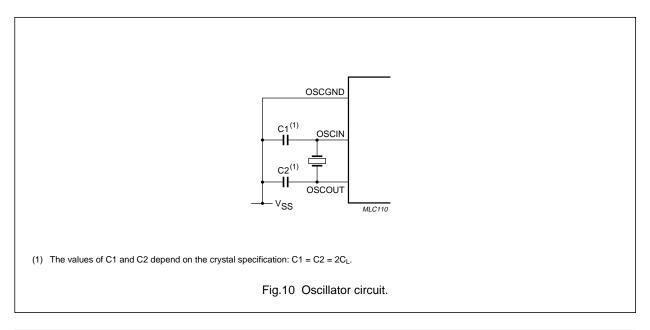

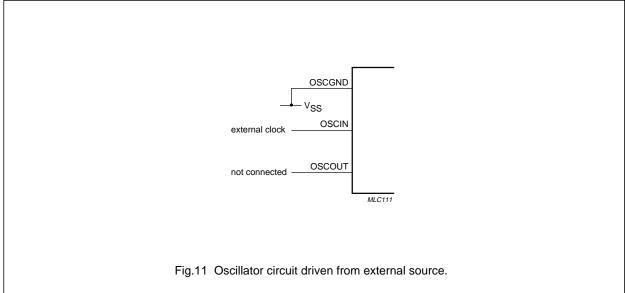

| OSCGND           | 40  | Crystal oscillator ground.                                                                                                                                                                                    |  |  |  |  |

| XTALIN           | 41  | 12 MHz crystal oscillator input.                                                                                                                                                                              |  |  |  |  |

| XTALOUT          | 42  | 12 MHz crystal oscillator output.                                                                                                                                                                             |  |  |  |  |

| RESET            | 43  | If the reset input is HIGH for at least 3 machine cycles (36 oscillator periods) while the oscillator is running, the device is reset; this pin should be connected to $V_{DDM}$ via a 2.2 $\mu$ F capacitor. |  |  |  |  |

| $V_{DDM}$        | 44  | +5 V microcontroller power supply.                                                                                                                                                                            |  |  |  |  |

| P1.0/INT1        | 45  | Port 1. 8-bit open-drain bidirectional port with alternative functions.                                                                                                                                       |  |  |  |  |

| P1.1/T0          | 46  | P1.0/INT1 is external interrupt 1, can be triggered on the rising/falling edge of pulse.                                                                                                                      |  |  |  |  |

| P1.2/INT0        | 47  | P1.1/T0 is the counter/timer 0.                                                                                                                                                                               |  |  |  |  |

| P1.3/INT1        | 48  |                                                                                                                                                                                                               |  |  |  |  |

| P1.6/SCL         | 49  | P1.2/INT0 is the external interrupt 0.                                                                                                                                                                        |  |  |  |  |

| P1.7/SDA         | 50  | P1.3/T1 is the counter/timer 1.                                                                                                                                                                               |  |  |  |  |

| P1.4             | 51  | P1.7/SDA is the serial data port for the I <sup>2</sup> C-bus.                                                                                                                                                |  |  |  |  |

| P1.5             | 52  | P1.6/SCL is the serial clock input for the I <sup>2</sup> C-bus.                                                                                                                                              |  |  |  |  |

### TV microcontroller with full screen On Screen Display (OSD)

SAA5288

### 7 FUNCTIONAL DESCRIPTION

#### 7.1 Microcontroller

The functionality of the microcontroller used with this family is described with reference to the industry-standard 80C51 microcontroller. A full description of its functionality can be found in "80C51-Based; 8-bit Microcontrollers, Data Handbook IC20". Using the 80C51 as a reference, the changes made to this family fall into two categories:

- · Features not supported by the SAA5288

- Features found on the SAA5288 but not supported by the 80C51.

### 7.2 80C51 features not supported

### 7.2.1 INTERRUPT PRIORITY

The IP SFR is not implemented and all interrupts are treated with the same priority level. The normal priority of interrupts is maintained within the level.

Table 2 Interrupts and vector address

| INTERRUPT SOURCE          | VECTOR ADDRESS<br>(HEX) |

|---------------------------|-------------------------|

| Reset                     | 000                     |

| External INT0             | 003                     |

| Timer 0                   | 00B                     |

| External INT1             | 013                     |

| Timer 1                   | 01B                     |

| Byte I <sup>2</sup> C-bus | 02B                     |

| Bit I <sup>2</sup> C-bus  | 053                     |

### 7.2.2 OFF-CHIP MEMORY

The SAA5288 does not support the use of off-chip program memory or off-chip data memory.

### 7.2.3 IDLE AND POWER-DOWN MODES

Idle and Power-down modes are not supported. Consequently, the respective bits in PCON are not available.

### 7.2.4 UART FUNCTION

The 80C51 UART is not available. As a consequence the SCON and SBUF SFRs are removed and the ES bit in the IE SFR is unavailable.

### 7.3 Additional features

The following features are provided in addition to the standard 80C51 features.

#### 7.3.1 INTERRUPTS

The external INT1 interrupt is modified to generate an interrupt on both the rising and falling edges of the INT1 pin, when EX1 bit is set. This facility allows for software pulse-width measurement for handling of a remote control.

#### 7.3.2 BIT LEVEL I<sup>2</sup>C-BUS INTERFACE

For reasons of compatibility with the SAA5290, SAA5291, SAA5291A and SAA5491 all contain a bit level serial I/O which supports the I<sup>2</sup>C-bus. P1.6/SCL and P1.7/SDA are the serial I/O pins. These two pins meet the I<sup>2</sup>C-bus specification concerning the input levels and output drive capability see "The I<sup>2</sup>C-bus and how to use it (including specifications)". Consequently, these two pins have an open-drain output configuration. All the four following modes of the I<sup>2</sup>C-bus are supported.

- · Master transmitter

- Master receiver

- · Slave transmitter

- · Slave receiver.

Three SFRs support the function of the bit-level I<sup>2</sup>C-bus hardware: S1INT, S1BIT and S1SCS and are enabled by setting register bit TXT8.I<sup>2</sup>C SELECT to logic 0.

### 7.3.3 BYTE LEVEL I<sup>2</sup>C-BUS INTERFACE

The byte level serial I/O supports the I $^2$ C-bus protocol. P1.6/SCL and P1.7/SDA are the serial I/O pins. These two pins meet the I $^2$ C-bus specification concerning the input levels and output drive capability. Consequently, these two pins have an open-drain output configuration.

The byte level I<sup>2</sup>C-bus serial port is identical to the I<sup>2</sup>C-bus serial port on the 8xC552. The operation of the subsystem is described in detail in the 8xC552 data sheet described in "80C51-Based; 8-bit Microcontrollers Data Handbook IC20".

Four SFRs support the byte level I<sup>2</sup>C-bus hardware: S1CON, S1STA, S1DAT and S1ADR. They are enabled by setting register bit TXT8. I<sup>2</sup>C SELECT to logic 1.

### 7.3.4 LED SUPPORT

Port pins P0.5 and P0.6 have a 10 mA current sinking capability to enable LEDs to be driven directly.

### TV microcontroller with full screen On Screen Display (OSD)

**SAA5288**

### 7.3.5 6-BIT PWM DACS

Eight 6-bit DACs are available to allow direct control of analogue sections of the television.

Each low resolution 6-bit DAC is controlled by its associated Special Function Register (PWM0 to PWM7). The PWM outputs are alternative functions of Port 2 and P3.4. The PWE bit in the SFR for the port corresponding to the PWM should be set to logic 1 for correct operation of the PWM, e.g. if PWM0 is to be used, P2.1 should be set to logic 1 setting the port pin to high-impedance.

### 7.3.5.1 Pulse Width Modulator Registers (PWM0 to PWM7)

Table 3

Pulse Width Modulator Registers (see Table 10 for addresses)

| 7   | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|---|-----|-----|-----|-----|-----|-----|

| PWE | _ | PV5 | PV4 | PV3 | PV2 | PV1 | PV0 |

**Table 4** Description of PWMn bits (n = 0 to 7)

| BIT | SYMBOL | DESCRIPTION                                                                                                                                                                                       |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PWE    | If PWE is set to a logic 1, the corresponding PWM is active and controls its assigned port pin. If PWE is set to la logic 0, the port pin is controlled by the corresponding bit in the port SFR. |

| 6   | _      | not used                                                                                                                                                                                          |

| 5   | PV5    | The output of the PWM is a pulse of period 21.33 μs with a pulse HIGH time determined                                                                                                             |

| 4   | PV4    | by the binary value of these 6-bits multiplied by 0.33 μs. PV5 is the most significant bit.                                                                                                       |

| 3   | PV3    |                                                                                                                                                                                                   |

| 2   | PV2    |                                                                                                                                                                                                   |

| 1   | PV1    |                                                                                                                                                                                                   |

| 0   | PV0    |                                                                                                                                                                                                   |

### TV microcontroller with full screen On Screen Display (OSD)

**SAA5288**

### 7.3.6 14-BIT PWM DAC

One 14-bit DAC is available to allow direct control of analogue sections of the television. The 14-bit PWM is controlled using Special Function Registers TDACL and TDACH.

The output of the TPWM is a pulse of period 42.66  $\mu$ s. The 7 most significant bits, TDACH.TD13 (MSB) to TDACH.TD8 and TDACL.TD7, alter the pulse width between 0 and 42.33  $\mu$ s, in much the same way as in the 6-bit PWMs. The 7 least significant bits, TDACL.TD6 to TDACL.TD0 (LSB), extend certain pulses by a further 0.33  $\mu$ s, e.g. if the 7 least significant bits are given the value 01H, then 1 in 128 cycles is extended. If the 7 least significant bits are given the value 02H, then 2 in 128 cycles is extended, and so forth.

The TPWM will not start to output a new value until after writing a value to TDACH. Therefore, if the value is to be changed, TDACL should be written to before TDACH.

### 7.3.6.1 TPWM High Byte Register (TDACH)

### Table 5 TPWM High Byte Register (SFR address D3H)

| 7   | 6 | 5    | 4    | 3    | 2    | 1   | 0   |

|-----|---|------|------|------|------|-----|-----|

| PWE | _ | TD13 | TD12 | TD11 | TD10 | TD9 | TD8 |

### Table 6 Description of TDACH bits

| BIT | SYMBOL | DESCRIPTION                                                                                                                                                                  |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PWE    | If PWE is set to a logic 1, the TPWM is active and controls port line P2.0. If PWE is set to a logic 0, the port pin is controlled by the corresponding bit in the port SFR. |

| 6   | _      | not used                                                                                                                                                                     |

| 5   | TD13   | These 6-bits along with bit TD7 in the TDACL register control the pulse width period.                                                                                        |

| 4   | TD12   | TD13 is the most significant bit.                                                                                                                                            |

| 3   | TD11   |                                                                                                                                                                              |

| 2   | TD10   |                                                                                                                                                                              |

| 1   | TD9    |                                                                                                                                                                              |

| 0   | TD8    |                                                                                                                                                                              |

### 7.3.6.2 TPWM Low Byte Register (TDACL)

### Table 7 TPWM Low Byte Register (SFR address D2H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| TD7 | TD6 | TD5 | TD4 | TD3 | TD2 | TD1 | TD0 |

### Table 8 Description of TDACL bits

| BIT    | SYMBOL     | DESCRIPTION                                                                                     |

|--------|------------|-------------------------------------------------------------------------------------------------|

| 7      | TD7        | This bit is used with bits TD13 to TD8 in the TDACH register to control the pulse width period. |

| 6 to 0 | TD6 to TD0 | These 7-bits extend certain pulses by a further 0.33 μs.                                        |

## TV microcontroller with full screen On Screen Display (OSD)

**SAA5288**

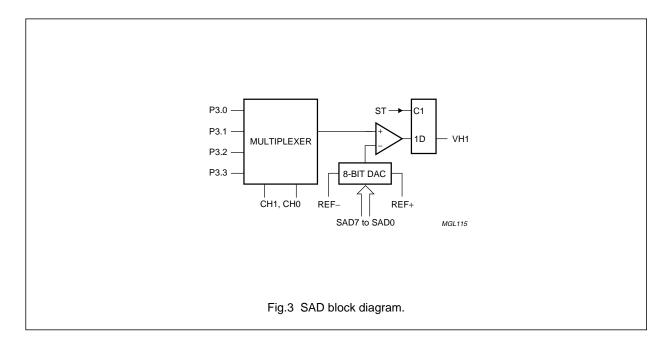

### 7.3.7 SOFTWARE ADC

Up to 4 successive approximation ADCs can be implemented in software by making use of the on-chip 8-bit DAC and multiplexed voltage comparator. The software ADC uses 4 analog inputs which are multiplexed with P3.0 to P3.3.

Table 9 ADC input channel selection

| CH1 | СН0 | INPUT PIN |

|-----|-----|-----------|

| 0   | 0   | P3.3/ADC3 |

| 0   | 1   | P3.0/ADC0 |

| 1   | 0   | P3.1/ADC1 |

| 1   | 1   | P3.2/ADC2 |

The control of the ADC is achieved using the Special Function Registers SAD and SADB.

SAD.CH1 and SAD.CH0 select one of the four inputs to pass to the comparator. The other comparator input comes from the DAC, whose value is set by SAD.SAD7 (MSB) to SAD.SAD4 and SADB.SAD3 to SADB.SAD0 (LSB). The setting of the value SAD.SAD7 to SAD.SAD4 must be performed at least 1 instruction cycle before the setting of SAD.ST to ensure comparison is made using the correct SAD.SAD7 to SAD.SAD4 value.

The output of the comparator is SAD.VHI, and is valid after 1 instruction cycle following the setting of SAD.ST to logic 1.

Preliminary specification

TV microcontroller with full screen On Screen Display (OSD)

SAA5288

#### 7.4 Microcontroller Interfacing

The 80C51 communicates with the peripheral functions using Special Function Registers which are addressed as RAM locations. The registers in the teletext decoder appear as normal SFRs in the microcontroller memory map, but are written to using an internal serial bus. The SFR map is given in Section 7.4.1 and the SFR bit description is given in Section 7.4.2.

### SPECIAL FUNCTION REGISTER MAP

Table 10 Special Function Register map; note 1

| SYMBOL                         |                            | DIRECT        |    | BIT AD | DRESS, SY | MBOL OR | ALTERNAT | IVE PORT FU | JNCTION |     | RESET |    |

|--------------------------------|----------------------------|---------------|----|--------|-----------|---------|----------|-------------|---------|-----|-------|----|

|                                | NAME                       | ADDRESS (HEX) | 7  | 6      | 5         | 4       | 3        | 2           | 1       | 0   | (HEX) |    |

| ACC <sup>(2)</sup> Accumulator | Accumulator                | E0            | E7 | E6     | E5        | E4      | E3       | E2          | E1      | E0  | 00    |    |

|                                |                            | _             | -  | -      | -         | _       | -        | -           | -       | 7   |       |    |

| B <sup>(2)</sup>               | B register                 | F0            | F7 | F6     | F5        | F4      | F3       | F2          | F1      | F0  | 00    |    |

|                                |                            |               | _  | -      | -         | -       | -        | -           | -       | -   | 7     |    |

| DPTR:                          | Data Pointer<br>(2 bytes): |               |    |        |           |         |          |             |         |     |       |    |

| DPH                            | High byte                  | 83            | _  | _      | _         | -       | _        | _           | _       | _   | 00    |    |

| DPL                            | Low byte                   | 82            | _  | _      | _         | -       | _        | _           | _       | _   | 00    |    |

| IE <sup>(2)(3)</sup>           | Interrupt                  | Interrupt     | A8 | AF     | AE        | AD      | AC       | AB          | AA      | A9  | A8    | 00 |

| Enable                         | Enable                     |               | EA | ES1    | ES2       | *       | ET1      | EX1         | ET0     | EX0 | 7     |    |

| P0 <sup>(2)</sup>              | Port 0                     | 80            | 87 | 86     | 85        | 84      | 83       | 82          | 81      | 80  | FF    |    |

|                                |                            |               | -  | -      | -         | -       | -        | -           | -       | -   | 7     |    |

| P1 <sup>(2)</sup>              | Port 1                     | 90            | 97 | 96     | 95        | 94      | 93       | 92          | 91      | 90  | FF    |    |

|                                |                            |               | _  | -      | -         | -       | _        | -           | -       | -   | 7     |    |

| P2 <sup>(2)</sup>              | Port 2                     | A0            | A7 | A6     | A5        | A4      | A3       | A2          | A1      | A0  | FF    |    |

|                                |                            |               | _  | -      | -         | -       | _        | -           | -       | -   | 7     |    |

| P3 <sup>(2)(3)</sup>           | Port 3                     | В0            | _  | -      | -         | -       | В3       | B2          | B1      | В0  | FF    |    |

|                                |                            |               | _  | _      | -         | -       | _        | -           | _       | _   | 1     |    |

| PCON(3)                        | Power Control              | 87            | _  | *      | -         | *       | GF1      | GF0         | _       | -   | 10    |    |

| PSW <sup>(2)</sup>             | Program                    | D0            | D7 | D6     | D5        | D4      | D3       | D2          | D1      | D0  | 00    |    |

| Status Word                    |                            | CY            | AC | F0     | RS1       | RS0     | OV       | *           | Р       |     |       |    |

SAA5288

|                      |                                          | DIRECT           |         | BIT AD | DRESS, SY | MBOL OR | ALTERNAT | IVE PORT FU | JNCTION |      | RESET<br>VALUE<br>(HEX) |

|----------------------|------------------------------------------|------------------|---------|--------|-----------|---------|----------|-------------|---------|------|-------------------------|

| SYMBOL               | NAME                                     | ADDRESS<br>(HEX) | 7       | 6      | 5         | 4       | 3        | 2           | 1       | 0    |                         |

| PWM0 <sup>(3)</sup>  | Pulse Width<br>Modulator 0               | D5               | PWE     | *      | PV5       | PV4     | PV3      | PV2         | PV1     | PV0  | 40                      |

| PWM1 <sup>(3)</sup>  | Pulse Width<br>Modulator 1               | D6               | PWE     | *      | PV5       | PV4     | PV3      | PV2         | PV1     | PV0  | 40                      |

| PWM2 <sup>(3)</sup>  | Pulse Width<br>Modulator 2               | D7               | PWE     | *      | PV5       | PV4     | PV3      | PV2         | PV1     | PV0  | 40                      |

| PWM3 <sup>(3)</sup>  | Pulse Width<br>Modulator 3               | DC               | PWE     | *      | PV5       | PV4     | PV3      | PV2         | PV1     | PV0  | 40                      |

| PWM4 <sup>(3)</sup>  | Pulse Width<br>Modulator 4               | DD               | PWE     | *      | PV5       | PV4     | PV3      | PV2         | PV1     | PV0  | 40                      |

| PWM5 <sup>(3)</sup>  | Pulse Width<br>Modulator 5               | DE               | PWE     | *      | PV5       | PV4     | PV3      | PV2         | PV1     | PV0  | 40                      |

| PWM6 <sup>(3)</sup>  | Pulse Width<br>Modulator 6               | DF               | PWE     | *      | PV5       | PV4     | PV3      | PV2         | PV1     | PV0  | 40                      |

| PWM7 <sup>(3)</sup>  | Pulse Width<br>Modulator 7               | D4               | PWE     | *      | PV5       | PV4     | PV3      | PV2         | PV1     | PV0  | 40                      |

| S1ADR <sup>(3)</sup> | Serial I <sup>2</sup> C-bus address      | DB               | ADR6    | ADR5   | ADR4      | ADR3    | ADR2     | ADR1        | ADR0    | GC   | 00                      |

| S1CON                | Serial I <sup>2</sup> C-bus              | D8               | DF      | DE     | DD        | DC      | DB       | DA          | D9      | D8   |                         |

| (2)(3)(4)            | control                                  |                  | CR2     | ENSI   | STA       | STO     | SI       | AA          | CR1     | CR0  | 00                      |

| S1SCS                | Serial I <sup>2</sup> C-bus              | D8               | DF      | DE     | DD        | DC      | DB       | DA          | D9      | D8   |                         |

| (2)(3)(5)            | control                                  |                  | SDI     | SCI    | CLH       | BB      | RBF      | WBF         | STR     | ENS  | E0                      |

| S1DAT<br>(3)(4)      | Serial I <sup>2</sup> C-bus<br>data      | DA               | DAT7    | DAT6   | DAT5      | DAT4    | DAT3     | DAT2        | DAT1    | DAT0 | 00                      |

| S1INT<br>(3)(5)      | Serial I <sup>2</sup> C-bus<br>Interrupt | DA               | SI      | -      | _         | -       | -        | -           | -       | -    | 7F                      |

| S1STA<br>(3)(4)      | Serial I <sup>2</sup> C-bus status       | D9               | STAT4   | STAT3  | STAT2     | STAT1   | STAT0    | 0           | 0       | 0    | F8                      |

| S1BIT<br>(3)(5)      | Serial I <sup>2</sup> C-bus data         | D9               | SDO/SDI | -      | -         | -       | -        | -           | -       | -    | 7F                      |

TV microcontroller with full screen On Screen Display (OSD)

Philips Semiconductors

4

| Preliminary specification |

|---------------------------|

| lion                      |

SAA5288

|                     |                        | DIRECT           |              |          |               |                   |                                  |                   |                   |                  |                |  |

|---------------------|------------------------|------------------|--------------|----------|---------------|-------------------|----------------------------------|-------------------|-------------------|------------------|----------------|--|

| SYMBOL              | NAME                   | ADDRESS<br>(HEX) | 7            | 6        | 5             | 4                 | 3                                | 2                 | 1                 | 0                | VALUE<br>(HEX) |  |

| SAD(2)(3)           | Software ADC           | E8               | EF           | EE       | ED            | EC                | EB                               | EA                | E9                | E8               | 00             |  |

|                     | (MSB)                  |                  | VHI          | CH1      | CH0           | ST                | SAD7                             | SAD6              | SAD5              | SAD4             |                |  |

| SADB                | Software ADC           | 98               | 9F           | 9E       | 9D            | 9C                | 9B                               | 9A                | 99                | 98               | 00             |  |

| (2)(3)              | (LSB)                  |                  | -            |          | _             | -                 | SAD3                             | SAD2              | SAD1              | SAD0             |                |  |

| SP                  | Stack Pointer          | 81               | 8F           | 8E       | 8D            | 8C                | 8B                               | 8A                | 89                | 88               | 07             |  |

| TCON <sup>(2)</sup> | Timer/counter control  | 88               | TF1          | TR1      | TF0           | TR0               | IE1                              | IT1               | IE0               | IT0              | 00             |  |

| TDACH               | TPWM High byte         | D3               | PWE          | *        | TD13          | TD12              | TD11                             | TD10              | TD9               | TD8              | 40             |  |

| TDACL               | TPWM Low<br>byte       | D2               | TD7          | TD6      | TD5           | TD4               | TD3                              | TD2               | TD1               | TD0              | 00             |  |

| TH0                 | Timer 0 High byte      | 8C               | TH07         | TH06     | TH05          | TH04              | TH03                             | TH02              | TH01              | TH00             | 00             |  |

| TH1                 | Timer 1 High byte      | 8D               | TH17         | TH16     | TH15          | TH14              | TH13                             | TH12              | TH11              | TH10             | 00             |  |

| TL0                 | Timer 0 Low byte       | 8A               | TL07         | TL06     | TL05          | TL04              | TL03                             | TL02              | TL01              | TL00             | 00             |  |

| TL1                 | Timer 1 Low byte       | 8B               | TL17         | TL16     | TL15          | TL14              | TL13                             | TL12              | TL11              | TL10             | 00             |  |

| TMOD                | Timer/counter          | 89               | GATE         | C/T      | M1            | M0                | GATE                             | C/T               | M1                | M0               | 00             |  |

|                     | mode                   |                  |              | Time     | r 1           |                   |                                  |                   |                   |                  |                |  |

| TXT0 <sup>(3)</sup> | Teletext<br>Register 0 | C0               | *            | *        | AUTO<br>FRAME | *                 | DISPLAY<br>STATUS<br>ROW<br>ONLY | DISABLE<br>FRAME  | *                 | *                | 00             |  |

| TXT1 <sup>(3)</sup> | Teletext<br>Register 1 | C1               | *            | *        | *             | *                 | *                                | FIELD<br>POLARITY | H<br>POLARITY     | V<br>POLARITY    | 00             |  |

| TXT4 <sup>(3)</sup> | Teletext<br>Register 4 | C4               | *            | *        | EAST/<br>WEST | DISABLE<br>DBL HT | B MESH<br>ENABLE                 | C MESH<br>ENABLE  | TRANS<br>ENABLE   | SHADOW<br>ENABLE | 00             |  |

| TXT5 <sup>(3)</sup> | Teletext<br>Register 5 | C5               | BKGND<br>OUT | BKGND IN | COR<br>OUT    | COR IN            | TEXT<br>OUT                      | TEXT IN           | PICTURE<br>ON OUT | PICTURE<br>ON IN | 03             |  |

15

SAA5288

|                      |                         | DIRECT           |                            | BIT AD           | DRESS, SY      | MBOL OR        | ALTERNAT         | IVE PORT FL    | JNCTION           |                  | RESET          |

|----------------------|-------------------------|------------------|----------------------------|------------------|----------------|----------------|------------------|----------------|-------------------|------------------|----------------|

| SYMBOL               | NAME                    | ADDRESS<br>(HEX) | 7                          | 6                | 5              | 4              | 3                | 2              | 1                 | 0                | VALUE<br>(HEX) |

| TXT6 <sup>(3)</sup>  | Teletext<br>Register 6  | C6               | BKGND<br>OUT               | BKGND IN         | COR<br>OUT     | COR IN         | TEXT<br>OUT      | TEXT IN        | PICTURE<br>ON OUT | PICTURE<br>ON IN | 03             |

| TXT7 <sup>(3)</sup>  | Teletext<br>Register 7  | C7               | STATUS<br>ROW<br>TOP       | CURSOR<br>ON     | REVEAL         | TOP/<br>BOTTOM | DOUBLE<br>HEIGHT | BOX ON<br>24   | BOX ON<br>1–23    | BOX ON<br>0      | 00             |

| TXT8 <sup>(3)</sup>  | Teletext<br>Register 8  | C8               | I <sup>2</sup> C<br>SELECT | *                | *              | *              | *                | *              | *                 | *                | 00             |

| TXT9 <sup>(3)</sup>  | Teletext<br>Register 9  | C9               | CURSOR<br>FREEZE           | CLEAR<br>MEMORY  | *              | R4             | R3               | R2             | R1                | R0               | 00             |

| TXT10 <sup>(3)</sup> | Teletext<br>Register 10 | CA               | *                          | *                | C5             | C4             | C3               | C2             | C1                | C0               | 00             |

| TXT11 <sup>(3)</sup> | Teletext<br>Register 11 | СВ               | D7                         | D6               | D5             | D4             | D3               | D2             | D1                | D0               | 00             |

| TXT12 <sup>(3)</sup> | Teletext<br>Register 12 | CC               | *                          | ROM VER<br>R4    | ROM<br>VER R3  | ROM<br>VER R2  | ROM<br>VER R1    | ROM VER<br>R0  | TXT ON            | *                | 0XXXX<br>X00B  |

| TXT13                | Teletext                | B8               | BF                         | BE               | BD             | BC             | BB               | BA             | B9                | B8               | 00             |

| (2)(3)               | Register 13             |                  | *                          | PAGE<br>CLEARING | 525<br>DISPLAY | *              | *                | *              | *                 | OSD I/F<br>busy  |                |

| TXT16 <sup>(3)</sup> | Teletext<br>Register 16 | CF               | *                          | Y2               | Y1             | Y0             | *                | *              | X1                | X0               | 00             |

| TXT17 <sup>(3)</sup> | Teletext<br>Register 17 | B9               | *                          | *                | *              | FORCE<br>625   | FORCE<br>525     | SCREEN<br>COL2 | SCREEN<br>COL1    | SCREEN<br>COL0   | 00             |

### Notes

- 1. The asterisk (\*) indicates these bits are inactive and must be written to logic 0 for future compatibility.

- 2. SFRs are bit addressable.

- 3. SFRs are modified or added to the 80C51 SFRs.

- 4. This register is used for Byte Orientated  $I^2C$ -bus, TXT8.  $I^2C$  SELECT = 1.

- 5. This register is used for Bit Orientated  $I^2C$ -bus, TXT8.  $I^2C$  SELECT = 0.

**SAA5288**

### 7.4.2 SPECIAL FUNCTION REGISTERS BIT DESCRIPTION

### Table 11 SFR bit descriptions

| REGISTER               | FUNCTION                                                                           |  |  |  |  |  |  |  |

|------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Interrupt Enable Regi  | ister (IE)                                                                         |  |  |  |  |  |  |  |

| EA                     | disable all interrupts (logic 0) or use individual interrupt enable bits (logic 1) |  |  |  |  |  |  |  |

| ES1                    | t I <sup>2</sup> C-bus interrupt enable (logic 1)                                  |  |  |  |  |  |  |  |

| ES2                    | byte I <sup>2</sup> C-bus interrupt enable (logic 1)                               |  |  |  |  |  |  |  |

| ET1                    | enable Timer 1 overflow interrupt (logic 1)                                        |  |  |  |  |  |  |  |

| EX1                    | enable external interrupt 1 (logic 1)                                              |  |  |  |  |  |  |  |

| ET0                    | enable Timer 0 overflow interrupt (logic 1)                                        |  |  |  |  |  |  |  |

| EX0                    | enable external interrupt 0 (logic 1)                                              |  |  |  |  |  |  |  |

| Power Control Regist   | ter (PCON)                                                                         |  |  |  |  |  |  |  |

| GF1                    | general purpose flag 1                                                             |  |  |  |  |  |  |  |

| GF0                    | general purpose flag 0                                                             |  |  |  |  |  |  |  |

| Program Status Word    | d (PSW)                                                                            |  |  |  |  |  |  |  |

| CY                     | carry flag                                                                         |  |  |  |  |  |  |  |

| AC                     | auxiliary carry flag                                                               |  |  |  |  |  |  |  |

| F0                     | flag 0                                                                             |  |  |  |  |  |  |  |

| RS1, RS0               | register bank select control bits                                                  |  |  |  |  |  |  |  |

| OV                     | overflow flag                                                                      |  |  |  |  |  |  |  |

| Р                      | parity flag                                                                        |  |  |  |  |  |  |  |

| 6-bit Pulse Width Mod  | dulator Control Registers (PWM0 to PWM7)                                           |  |  |  |  |  |  |  |

| PWE                    | activate this PWM and take control of respective port pin (logic 1)                |  |  |  |  |  |  |  |

| PV5 to PV0             | binary value sets high time of PWM output                                          |  |  |  |  |  |  |  |

| Serial Interface Slave | Address Register (S1ADR)                                                           |  |  |  |  |  |  |  |

| ADR6 to ADR0           | I <sup>2</sup> C-bus slave address to which the device will respond                |  |  |  |  |  |  |  |

| GC                     | enables response to the I <sup>2</sup> C-bus general call address                  |  |  |  |  |  |  |  |

| Serial Interface Contr | rol Register (S1CON)                                                               |  |  |  |  |  |  |  |

| CR2 to CR0             | clock rate bits                                                                    |  |  |  |  |  |  |  |

| ENSI                   | I <sup>2</sup> C-bus interface enable                                              |  |  |  |  |  |  |  |

| STA                    | start condition flag                                                               |  |  |  |  |  |  |  |

| STO                    | stop condition flag                                                                |  |  |  |  |  |  |  |

| SI                     | interrupt flag                                                                     |  |  |  |  |  |  |  |

| AA                     | assert acknowledge flag                                                            |  |  |  |  |  |  |  |

**SAA5288**

| REGISTER                                             | FUNCTION                                                                                    |  |  |  |  |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Serial Interface Data                                | Register (S1DAT)                                                                            |  |  |  |  |  |  |  |

| DAT7 to DAT0                                         | DATO I <sup>2</sup> C-bus data                                                              |  |  |  |  |  |  |  |

| Serial Interface Status Register (S1STA) - READ only |                                                                                             |  |  |  |  |  |  |  |

| STAT4 to STAT0                                       | I <sup>2</sup> C-bus interface status                                                       |  |  |  |  |  |  |  |

| Serial Interface Data I                              | Register (S1BIT) - READ                                                                     |  |  |  |  |  |  |  |

| SDI                                                  | I <sup>2</sup> C-bus data bit input                                                         |  |  |  |  |  |  |  |

| Serial Interface Data I                              | Register (S1BIT) - WRITE                                                                    |  |  |  |  |  |  |  |

| SDO                                                  | I <sup>2</sup> C-bus data bit output                                                        |  |  |  |  |  |  |  |

| Serial Interface Interr                              | upt Register (S1INT)                                                                        |  |  |  |  |  |  |  |

| SI                                                   | I <sup>2</sup> C-bus interrupt flag                                                         |  |  |  |  |  |  |  |

| Serial Interface Contr                               | ol Register (S1SCS) - READ                                                                  |  |  |  |  |  |  |  |

| SDI                                                  | serial data input at SDA                                                                    |  |  |  |  |  |  |  |

| SCI                                                  | serial clock input at SCL                                                                   |  |  |  |  |  |  |  |

| CLH                                                  | clock LOW-to-HIGH transition flag                                                           |  |  |  |  |  |  |  |

| BB                                                   | bus busy flag                                                                               |  |  |  |  |  |  |  |

| RBF                                                  | read bit finished flag                                                                      |  |  |  |  |  |  |  |

| WBF                                                  | write bit finished flag                                                                     |  |  |  |  |  |  |  |

| STR                                                  | clock stretching enable (logic 1)                                                           |  |  |  |  |  |  |  |

| ENS                                                  | enable serial I/O (logic 1)                                                                 |  |  |  |  |  |  |  |

| Serial Interface Contr                               | ol Register (S1SCS) - WRITE                                                                 |  |  |  |  |  |  |  |

| SDO                                                  | serial data output at SDA                                                                   |  |  |  |  |  |  |  |

| SCO                                                  | serial clock output at SCL                                                                  |  |  |  |  |  |  |  |

| CLH                                                  | clock LOW-to-HIGH transition flag                                                           |  |  |  |  |  |  |  |

| STR                                                  | clock stretching enable (logic 1)                                                           |  |  |  |  |  |  |  |

| ENS                                                  | enable serial I/O (logic 1)                                                                 |  |  |  |  |  |  |  |

| Software ADC Contro                                  | ol Register (SAD)                                                                           |  |  |  |  |  |  |  |

| VHI                                                  | comparator output indicating that analogue input voltage greater than DAC voltage (logic 1) |  |  |  |  |  |  |  |

| CH1 and CH0                                          | ADC input channel selection bits, see Table 11                                              |  |  |  |  |  |  |  |

| ST                                                   | initiate voltage comparison (logic 1); this bit is automatically reset to logic 0           |  |  |  |  |  |  |  |

| SAD7 to SAD4                                         | 4 MSB's of DAC input value                                                                  |  |  |  |  |  |  |  |

| Software ADC Contro                                  | ol Register (SADB)                                                                          |  |  |  |  |  |  |  |

| SAD3 to SAD0                                         | 4 LSB's of DAC input value                                                                  |  |  |  |  |  |  |  |

**SAA5288**

| REGISTER                   | FUNCTION                                                                 |  |  |  |  |  |  |  |  |

|----------------------------|--------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Timer/Counter Contr        | Fimer/Counter Control Register (TCON)                                    |  |  |  |  |  |  |  |  |

| TF1                        | Timer 1 overflow flag                                                    |  |  |  |  |  |  |  |  |

| TR1                        | Timer 1 run control bit                                                  |  |  |  |  |  |  |  |  |

| TF0                        | Timer 0 overflow flag                                                    |  |  |  |  |  |  |  |  |

| TR0                        | Timer 0 run control bit                                                  |  |  |  |  |  |  |  |  |

| IE1                        | Interrupt 1 edge flag                                                    |  |  |  |  |  |  |  |  |

| IT1                        | Interrupt 1 type control bit                                             |  |  |  |  |  |  |  |  |

| IE0                        | Interrupt 0 edge flag                                                    |  |  |  |  |  |  |  |  |

| IT0                        | Interrupt 0 type control bit                                             |  |  |  |  |  |  |  |  |

| 14-bit PWM MSB Reg         | gister (TDACH)                                                           |  |  |  |  |  |  |  |  |

| PWE                        | activate this 14-bit PWM and take over port pin (logic 1)                |  |  |  |  |  |  |  |  |

| TD13 to TD8                | 6 MSBs of 14-bit number to be output by the 14-bit PWM                   |  |  |  |  |  |  |  |  |

| 14-bit PWM LSB Reg         | ister (TDACL)                                                            |  |  |  |  |  |  |  |  |

| TD7 to TD0                 | 8 LSBs of 14-bit number to be output by the 14-bit PWM                   |  |  |  |  |  |  |  |  |

| Timer 0 High byte (T       | Н0)                                                                      |  |  |  |  |  |  |  |  |

| TH07 to TH00               | 8 MSBs of Timer 0 16-bit counter                                         |  |  |  |  |  |  |  |  |

| Timer 1 High byte (T       | H1)                                                                      |  |  |  |  |  |  |  |  |

| TH17 to TH10               | 8 MSBs of Timer 1 16-bit counter                                         |  |  |  |  |  |  |  |  |

| Timer 0 Low byte (TL       | .0)                                                                      |  |  |  |  |  |  |  |  |

| TL07 to TL00               | 8 LSBs of Timer 0 16-bit counter                                         |  |  |  |  |  |  |  |  |

| Timer 1 Low byte (TL       | .1)                                                                      |  |  |  |  |  |  |  |  |

| TL17 to TL10               | 8 LSBs of Timer 1 16-bit counter                                         |  |  |  |  |  |  |  |  |

| Timer/Counter Mode         | Control Register (TMOD)                                                  |  |  |  |  |  |  |  |  |

| GATE                       | gating control                                                           |  |  |  |  |  |  |  |  |

| C/T                        | counter or timer selector                                                |  |  |  |  |  |  |  |  |

| M1, M0                     | mode control bits                                                        |  |  |  |  |  |  |  |  |

| Teletext Register 0 (7     | TXT0) - WRITE only                                                       |  |  |  |  |  |  |  |  |

| AUTO FRAME                 | FRAME output switched off automatically if any video displayed (logic 1) |  |  |  |  |  |  |  |  |

| DISPLAY STATUS<br>ROW ONLY | display row 24 only (logic 1)                                            |  |  |  |  |  |  |  |  |

| DISABLE FRAME              | FRAME output always low (logic 1)                                        |  |  |  |  |  |  |  |  |

**SAA5288**

| REGISTER                | FUNCTION                                                                                                                                               |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Teletext Register 1 (T) | XT1) - WRITE only                                                                                                                                      |

| FIELD POLARITY          | VSYNC in first half of the line (logic 0) or second half of the line (logic 1) at start of even field                                                  |

| H POLARITY              | HSYNC input positive-going (logic 0) or negative-going (logic 1)                                                                                       |

| V POLARITY              | VSYNC input positive-going (logic 0) or negative-going (logic 1)                                                                                       |

| PRD4 to PRD0            | page request data                                                                                                                                      |

| Teletext Register 4 (T) | XT4) - WRITE only                                                                                                                                      |

| EAST/ WEST              | western languages selected (logic 0) or Eastern languages selected (logic 1)                                                                           |

| DISABLE DBL HGHT        | disable display of double height teletext control codes (logic 1) in OSD boxes                                                                         |

| B MESH ENABLE           | enable meshing of area with black background (logic 1)                                                                                                 |

| C MESH ENABLE           | enable meshing of area with other background colours (logic 1)                                                                                         |

| TRANS ENABLE            | set black background to transparent i.e. video is displayed (logic 1)                                                                                  |

| SHADOW ENABLE           | enable south-east shadowing (logic 1)                                                                                                                  |

| Teletext Register 5 (T) | XT5) - WRITE only                                                                                                                                      |

| BKGND OUT               | background colour displayed outside teletext boxes (logic 1)                                                                                           |

| BKGND IN                | background colour displayed inside teletext boxes (logic 1)                                                                                            |

| COR OUT                 | COR output active outside teletext boxes (logic 1)                                                                                                     |

| COR IN                  | COR output active inside teletext boxes (logic 1)                                                                                                      |

| TEXT OUT                | text displayed outside teletext boxes (logic 1)                                                                                                        |

| TEXT IN                 | text displayed inside teletext boxes (logic 1)                                                                                                         |

| PICTURE ON OUT          | video picture displayed outside teletext boxes (logic 1)                                                                                               |

| PICTURE ON IN           | video picture displayed inside teletext boxes (logic 1)                                                                                                |

| Teletext Register 6 (TX | XT6) - WRITE only                                                                                                                                      |

| See TXT5                | this register has the same meaning as TXT5 but is only invoked if either newsflash (C5) or subtitle (C6) bit in row 25 of the basic page memory is set |

| Teletext Register 7 (T) | XT7) - WRITE only                                                                                                                                      |

| STATUS ROW TOP          | display row 24 below (logic 0) or above (logic 1) teletext page                                                                                        |

| CURSOR ON               | display cursor at location pointed to by TXT9 and TXT10 (logic 1)                                                                                      |

| REVEAL                  | display characters in areas with the conceal attribute set (logic 1)                                                                                   |

| TOP/BOTTOM              | display rows 0 to 11 (logic 0) or 12 to 23 (logic 1) when the double height bit is set                                                                 |

| DOUBLE HEIGHT           | display each character as twice normal height (logic 1)                                                                                                |

| BOX ON 24               | enable teletext boxes in memory row 24 (logic 1)                                                                                                       |

| BOX ON 1-23             | enable teletext boxes in memory rows 1 to 23 (logic 1)                                                                                                 |

| BOX ON 0                | enable teletext boxes in memory row 0 (logic 1)                                                                                                        |

**SAA5288**

| REGISTER                                                                                               | FUNCTION                                                                                       |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Teletext Register 8 (T                                                                                 | Teletext Register 8 (TXT8)                                                                     |  |  |  |  |  |  |  |  |  |

| <sup>2</sup> C SELECT select bit I <sup>2</sup> C-bus (logic 0) or byte I <sup>2</sup> C-bus (logic 1) |                                                                                                |  |  |  |  |  |  |  |  |  |

| Teletext Register 9 (T                                                                                 | Teletext Register 9 (TXT9) - WRITE only                                                        |  |  |  |  |  |  |  |  |  |

| CURSOR FREEZE                                                                                          | locks current cursor position (logic 1)                                                        |  |  |  |  |  |  |  |  |  |

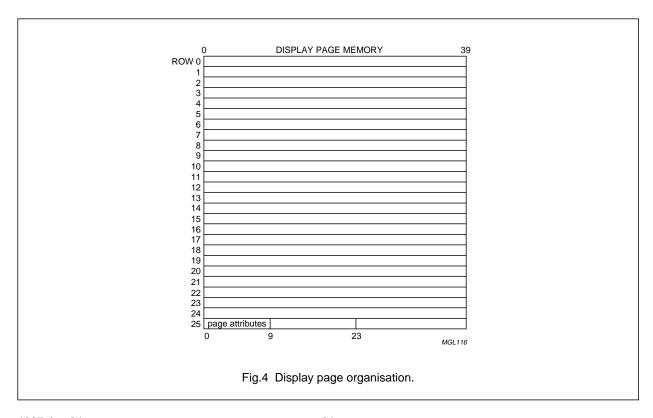

| CLEAR MEMORY                                                                                           | write 20H into every location in display memory (logic 1)                                      |  |  |  |  |  |  |  |  |  |

| R4 to R0                                                                                               | memory row to be accessed by TXT11                                                             |  |  |  |  |  |  |  |  |  |

| Teletext Register 10 (                                                                                 | TXT10) - WRITE only                                                                            |  |  |  |  |  |  |  |  |  |

| C5 to C0                                                                                               | memory column to be accessed by TXT11                                                          |  |  |  |  |  |  |  |  |  |

| Teletext Register 11 (                                                                                 | (TXT11)                                                                                        |  |  |  |  |  |  |  |  |  |

| D7 to D0                                                                                               | data byte written to, or read from display memory                                              |  |  |  |  |  |  |  |  |  |

| Teletext Register 12 (                                                                                 | TXT12) - READ only                                                                             |  |  |  |  |  |  |  |  |  |

| ROM VER R4 to R0                                                                                       | mask programmable identification for character set                                             |  |  |  |  |  |  |  |  |  |

| DISPLAY ON                                                                                             | power has been applied to the display hardware (logic 1)                                       |  |  |  |  |  |  |  |  |  |

| Teletext Register 13 (                                                                                 | (TXT13)                                                                                        |  |  |  |  |  |  |  |  |  |

| PAGE CLEARING                                                                                          | set when software requested page clear in progress                                             |  |  |  |  |  |  |  |  |  |

| 525 DISPLAY                                                                                            | set to logic 1 when 525-line syncs are driving the display                                     |  |  |  |  |  |  |  |  |  |

| OSD I/F Busy                                                                                           | OSD interface busy; logic 1 indicates that TXT Registers 0 to 16 can not currently be accessed |  |  |  |  |  |  |  |  |  |

| Teletext Register 16 (                                                                                 | TXT16) - WRITE only                                                                            |  |  |  |  |  |  |  |  |  |

| Y2 to Y0                                                                                               | sets vertical position of display area                                                         |  |  |  |  |  |  |  |  |  |

| X1 to X0                                                                                               | sets horizontal position of display area                                                       |  |  |  |  |  |  |  |  |  |

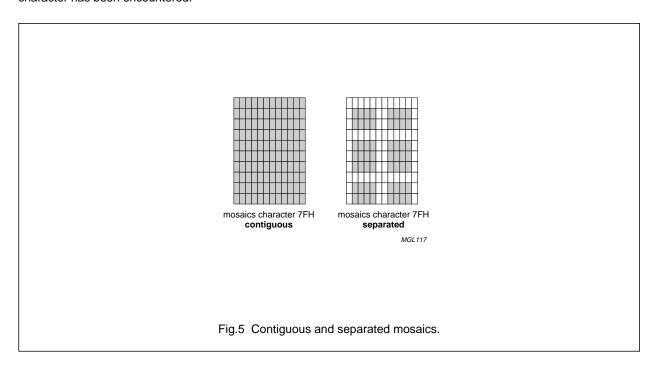

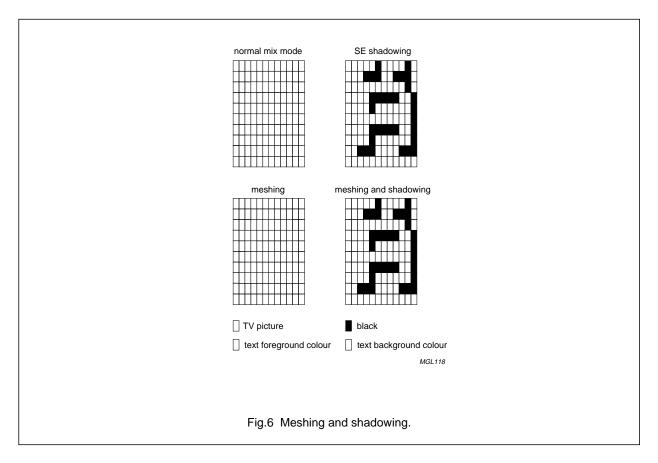

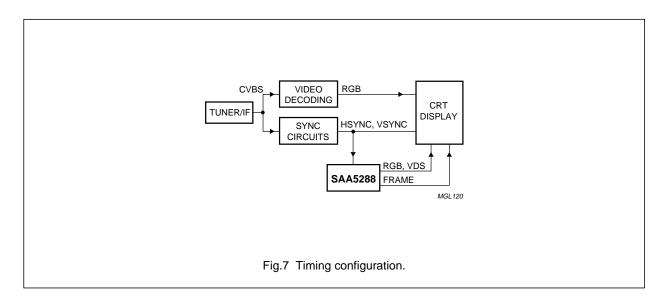

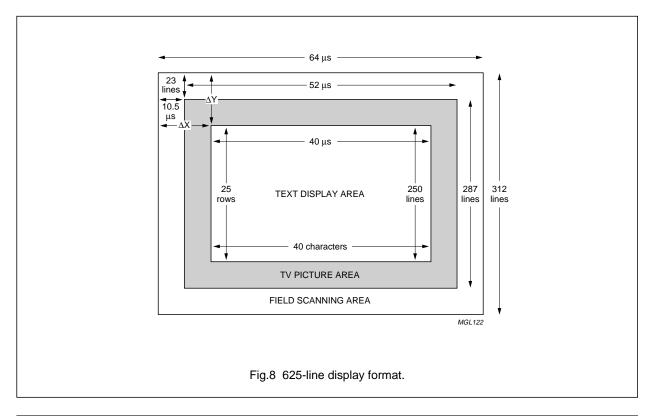

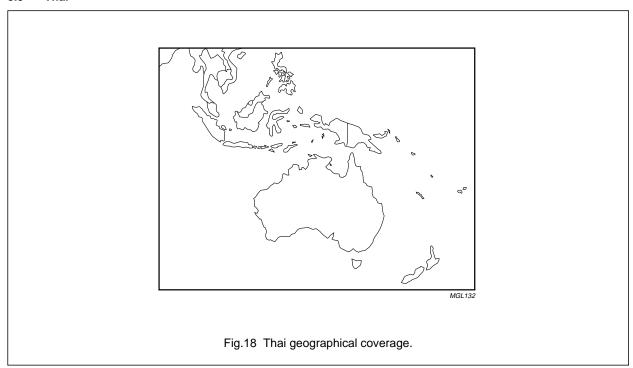

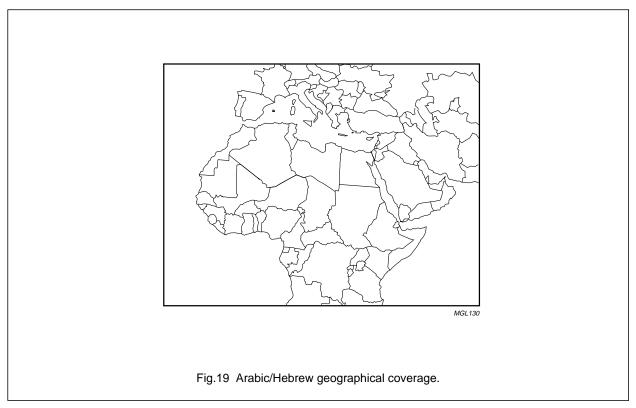

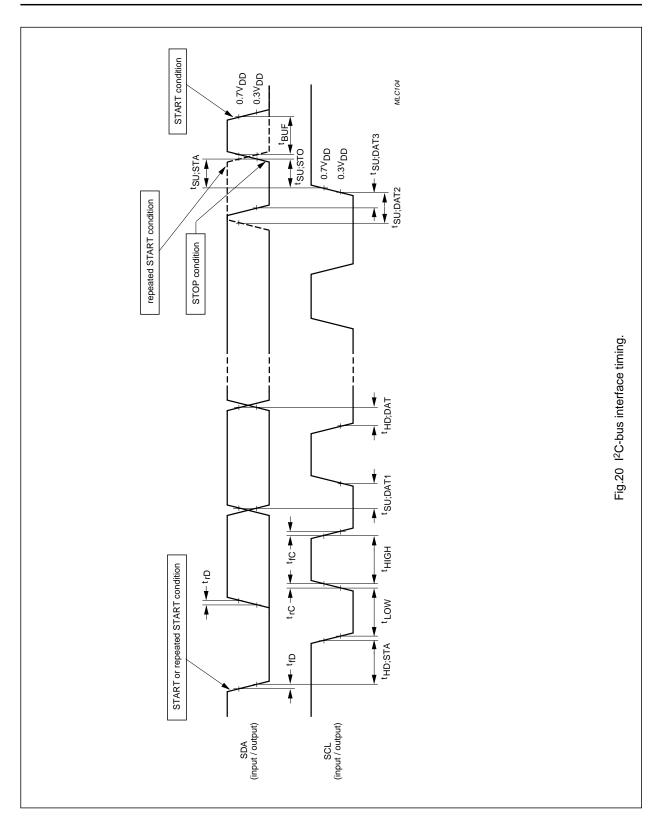

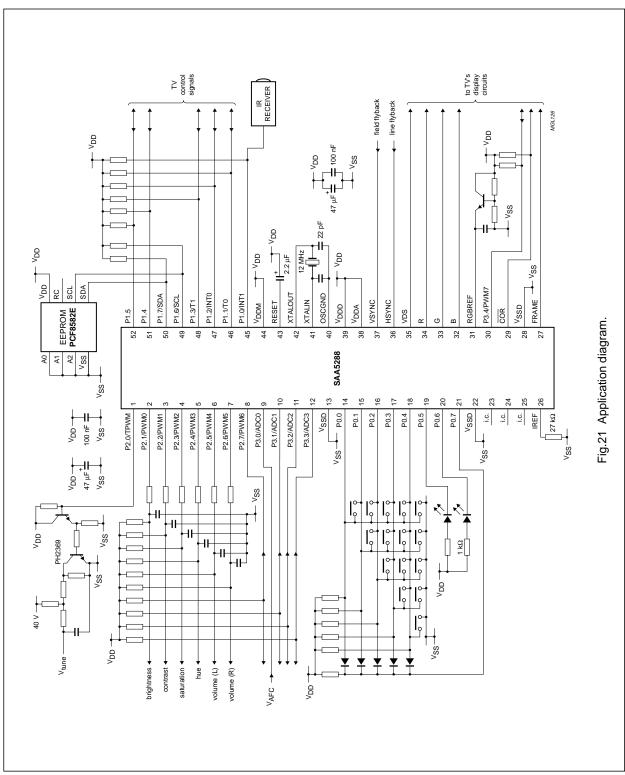

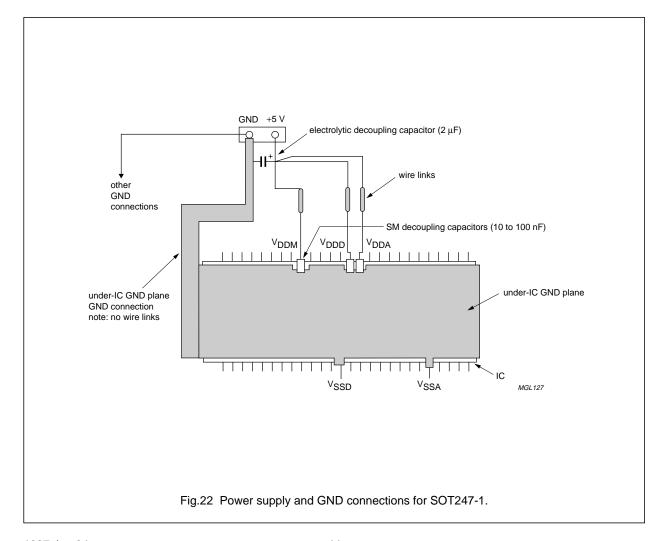

| Teletext Register 17 (                                                                                 | (TXT17) - Write only                                                                           |  |  |  |  |  |  |  |  |  |