### INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC02 March 1992

**Semiconductors**

Philips

### Integrated VIP and teletext decoder (IVT1.1)

#### FEATURES

- Complete teletext decoder including page memory in a single 40-pin DIL package

- Single +5 V power supply

- Digital data slicer and display clock phase-locked loop reduces peripheral components to a minimum

- Both video and scan related synchronization modes are supported

- On board single page memory including extension packets for FASTEXT

- Single page acquisition system

- RGB interface to standard colour decoder ICs, push-pull output drive

- Data capture performance similar to SAA5231 (VIP2)

- Simple software control via I<sup>2</sup>C-bus

- Option for five national languages

- 32 supplementary characters for on-screen displays

- Optional storage of packet 24 in the display memory

- Page links in packets 27 and 8/30 are Hamming decoded

- Separate text and video signal quality detectors, 625/525 video status and language version all readable via l<sup>2</sup>C-bus

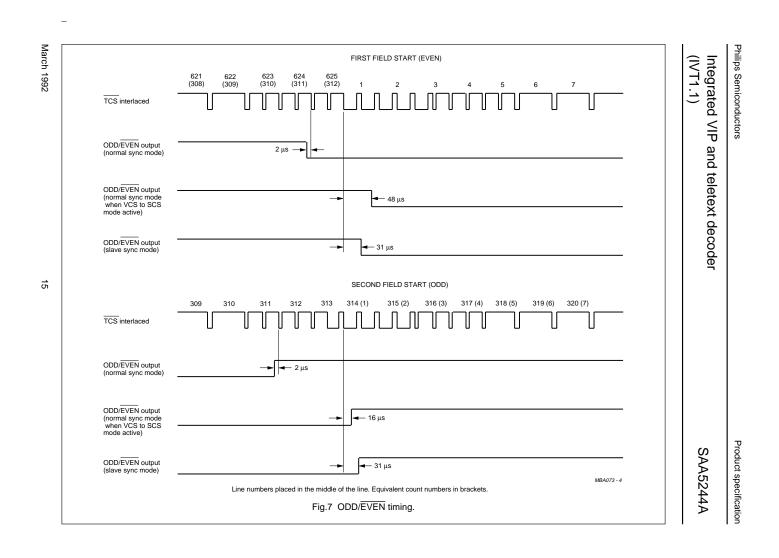

- Automatic ODD/EVEN output control with manual override

- Control of display PLL free-run and rolling header via  ${\rm I}^2 {\rm C}\text{-}{\rm bus}$

- VCS to SCS mode for stable 525 line status display

#### DESCRIPTION

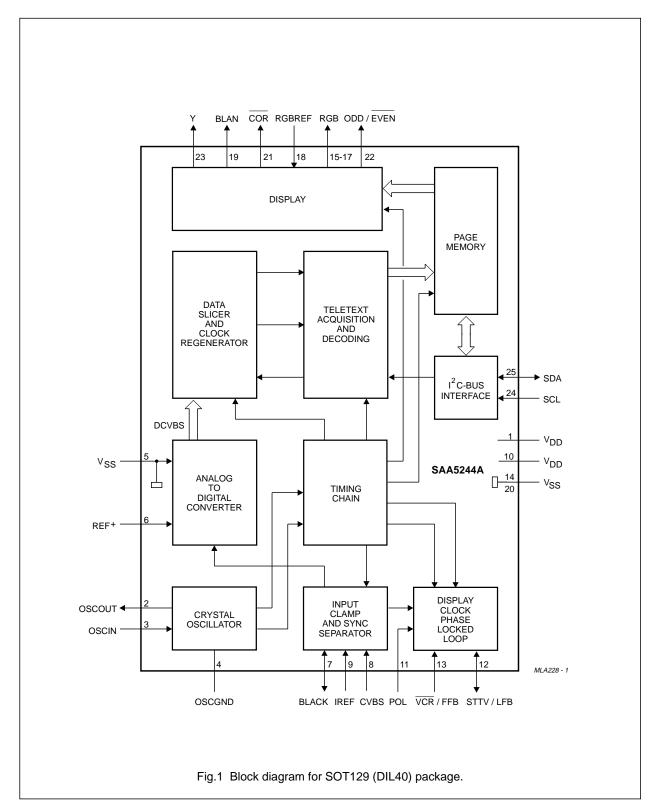

The Integrated VIP and Teletext (IVT1.1) is a teletext decoder (contained within a single-chip package) for decoding 625-line based World System Teletext transmissions. The teletext decoder hardware is based on a reduced function version of the device SAA5246 (IVT1.0).

The Video Input Processor (VIP) section of the device uses mixed analog and digital designs for the data slicer and the display clock phase-locked loop functions. As a result the number of external components is greatly reduced and no critical or adjustable components are required. A single page static RAM is incorporated in the device thereby giving a genuine single-chip teletext decoder device.

### ORDERING INFORMATION

| EXTENDED TYPE |                                 | P   | ACKAGE  |                        |  |

|---------------|---------------------------------|-----|---------|------------------------|--|

| NUMBER        | PINS PIN POSITION MATERIAL CODE |     |         |                        |  |

| SAA5244AP     | 40                              | DIL | plastic | SOT129 <sup>(1)</sup>  |  |

| SAA5244AGP    | 44                              | QFP | plastic | SOT205A <sup>(2)</sup> |  |

#### Notes

- 1. SOT129-1; 1996 December 16.

- 2. SOT205-1; 1996 December 16.

## Integrated VIP and teletext decoder (IVT1.1)

#### QUICK REFERENCE DATA

| SYMBOL            | PARAMETER                           | MIN. | TYP. | MAX. | UNIT |

|-------------------|-------------------------------------|------|------|------|------|

| V <sub>DD</sub>   | positive supply voltage             | 4.5  | 5    | 5.5  | V    |

| I <sub>DD</sub>   | supply current                      | -    | 74   | 148  | mA   |

| V <sub>syn</sub>  | sync amplitude                      | 0.1  | 0.3  | 0.6  | V    |

| V <sub>vid</sub>  | video amplitude                     | 0.7  | 1    | 1.4  | V    |

| f <sub>XTAL</sub> | crystal frequency                   | -    | 27   | -    | MHz  |

| T <sub>amb</sub>  | operating ambient temperature range | -20  | -    | 70   | °C   |

# Integrated VIP and teletext decoder (IVT1.1)

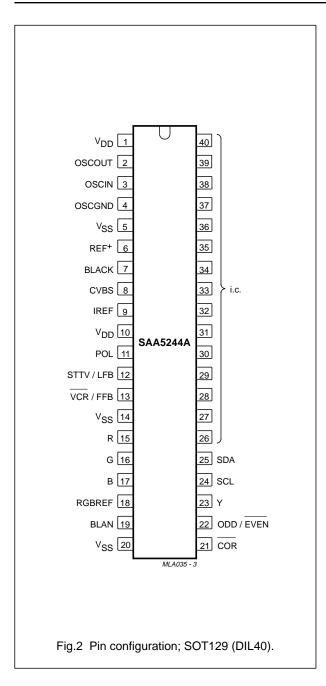

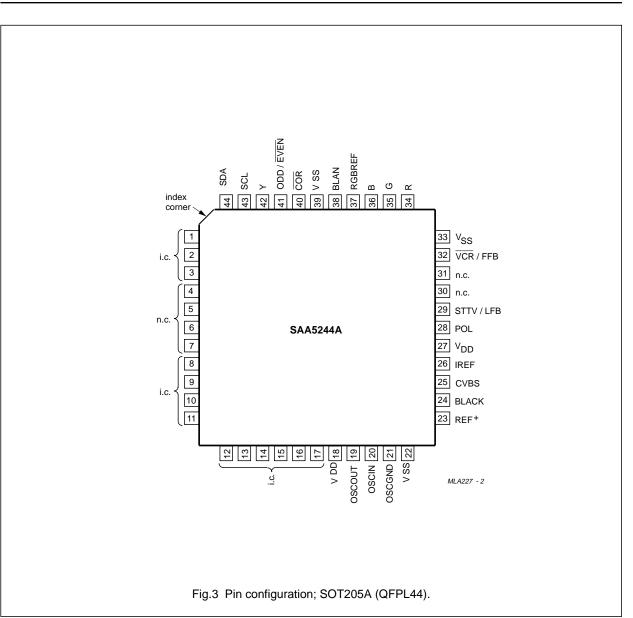

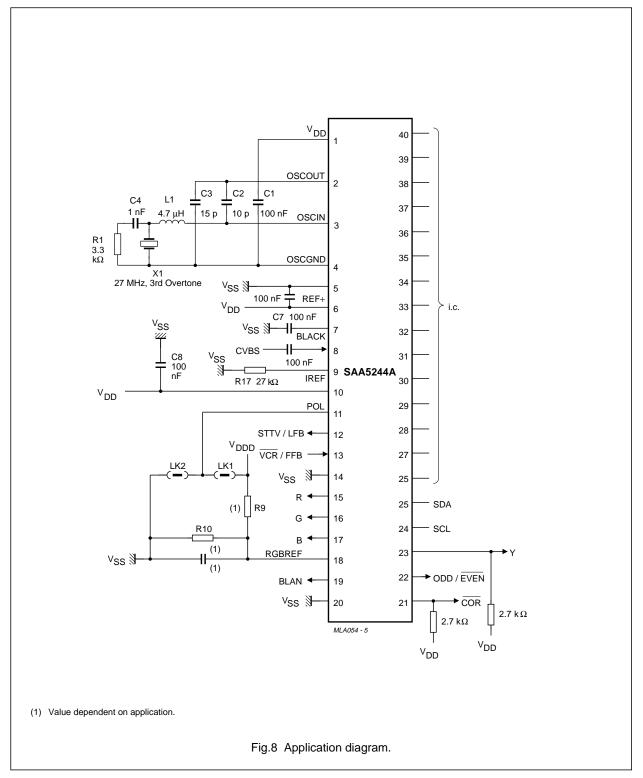

### PINNING

| SYMBOL          | SOT129   | SOT205A           | DESCRIPTION                                                                                                                                                         |

|-----------------|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | 1        | 18                | +5 V supply                                                                                                                                                         |

| OSCOUT          | 2        | 19                | 27 MHz crystal oscillator output                                                                                                                                    |

| OSCIN           | 3        | 20                | 27 MHz crystal oscillator input                                                                                                                                     |

| OSCGND          | 4        | 21                | 0 V crystal oscillator ground                                                                                                                                       |

| V <sub>SS</sub> | 5        | 22                | 0 V ground                                                                                                                                                          |

| REF-            | -        | -                 | negative reference voltage for the ADC. The pin should be connected to 0 V                                                                                          |

| REF+            | 6        | 23                | positive reference voltage for the ADC. The pin should be connected to +5 V                                                                                         |

| BLACK           | 7        | 24                | video black level storage pin, connected to ground via a 100 nF capacitor                                                                                           |

| CVBS            | 8        | 25                | composite video input pin. A positive-going 1 V (peak-to-peak) input is required, connected via a 100 nF capacitor                                                  |

| IREF            | 9        | 26                | reference current input pin, connected to ground via a 27 k $\Omega$ resistor                                                                                       |

| V <sub>DD</sub> | 10       | 27                | +5 V supply                                                                                                                                                         |

| POL             | 11       | 28                | STTV/LFB/FFB polarity selection pin                                                                                                                                 |

| STTV/LFB        | 12       | 29                | sync to TV output pin/line flyback input pin. Function controlled by an internal register bit (scan sync mode)                                                      |

| VCR/FFB         | 13       | 32                | PLL time constant switch/field flyback input pin. Function controlled by an internal register bit (scan sync mode)                                                  |

| V <sub>SS</sub> | 14       | 33                | 0 V ground                                                                                                                                                          |

| R               | 15       | 34                | dot rate character output of the RED colour information                                                                                                             |

| G               | 16       | 35                | dot rate character output of the GREEN colour information                                                                                                           |

| В               | 17       | 36                | dot rate character output of the BLUE colour information                                                                                                            |

| RGBREF          | 18       | 37                | input DC voltage to define the output high level on the RGB pins                                                                                                    |

| BLAN            | 19       | 38                | dot rate fast blanking output                                                                                                                                       |

| V <sub>SS</sub> | 20       | 39                | 0 V ground                                                                                                                                                          |

| COR             | 21       | 40                | programmable output to provide contrast reduction of the TV picture for mixed text and picture displays or when viewing newsflash/subtitle pages; open drain output |

| ODD/EVEN        | 22       | 41                | 25 Hz output synchronized with the CVBS input's field sync pulses to produce a non-interlaced display by adjustment of the vertical deflection currents             |

| Y               | 23       | 42                | dot rate character output of teletext foreground colour information open drain output                                                                               |

| SCL             | 24       | 43                | serial clock input for the I <sup>2</sup> C-bus. It can still be driven during power-down of the device                                                             |

| SDA             | 25       | 44                | serial data port for the I <sup>2</sup> C-bus; open drain output. It can still be driven during power-down of the device                                            |

| n.c.            | -        | 4 to 7<br>30, 31  | not connected                                                                                                                                                       |

| i.c.            | 26 to 40 | 1 to 3<br>8 to 17 | internally connected. Must be left open-circuit in application                                                                                                      |

### SAA5244A

## Integrated VIP and teletext decoder (IVT1.1)

### SAA5244A

#### LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL            | PARAMETER                                           | MIN.  | MAX.                 | UNIT |

|-------------------|-----------------------------------------------------|-------|----------------------|------|

| V <sub>DD</sub>   | supply voltage (all supplies)                       | -0.3  | 6.5                  | V    |

| VI                | input voltage (any input)                           | -0.3  | V <sub>DD</sub> +0.5 | V    |

| Vo                | output voltage (any output)                         | -0.3  | V <sub>DD</sub> +0.5 | V    |

| I <sub>O</sub>    | output current (each output)                        | -     | ±10                  | mA   |

| I <sub>IOK</sub>  | DC input or output diode current                    | -     | ±20                  | mA   |

| T <sub>amb</sub>  | operating ambient temperature range                 | -20   | 70                   | °C   |

| T <sub>stg</sub>  | storage temperature range                           | -55   | 125                  | °C   |

| V <sub>stat</sub> | electrostatic handling<br>human body model (note 1) | -2000 | 2000                 | v    |

#### Note

The human body model ESD simulation is equivalent to discharging a 100 pF capacitor through a 1.5 kΩ resistor; this produces a single discharge transient. Reference Philips Semiconductors test method UZW-B0/FQ-A302 (compatible with MIL-STD method 3015.7).

#### Failure Rate

The failure rate at  $T_{amb} = 55 \text{ °C}$  will be a maximum of 1000 FITS (1 FIT = 1 x 10<sup>-9</sup> failures per hour).

### SAA5244A

### CHARACTERISTICS

$V_{DD}$  = 5 V  $\pm$  10%;  $T_{amb}\,$  = –20 to +70 °C, unless otherwise specified

| SYMBOL                | PARAMETER                                                                                                 | CONDITIONS              | MIN. | TYP. | MAX.                 | UNIT |

|-----------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|------|------|----------------------|------|

| Supply                |                                                                                                           |                         | •    |      |                      | -    |

| V <sub>DD</sub>       | supply voltage range (V <sub>DD</sub> -V <sub>SS</sub> )                                                  |                         | 4.5  | 5    | 5.5                  | V    |

| I <sub>DD</sub>       | total supply current                                                                                      |                         | -    | 74   | 148                  | mA   |

| Inputs                |                                                                                                           |                         |      |      |                      |      |

| CVBS                  |                                                                                                           |                         |      |      |                      |      |

| V <sub>syn</sub>      | sync amplitude                                                                                            |                         | 0.1  | 0.3  | 0.6                  | V    |

| t <sub>syn</sub>      | delay from CVBS to TCS<br>output from STTV buffer<br>(nominal video, average of<br>leading/trailing edge) |                         | -150 | 0    | 150                  | ns   |

| t <sub>syd</sub>      | change in sync delay between<br>all black and all white video<br>input at nominal levels                  |                         | 0    | -    | 25                   | ns   |

| V <sub>vid(p-p)</sub> | video input amplitude<br>(peak-to-peak)                                                                   |                         | 0.7  | 1    | 1.4                  | V    |

|                       | display PLL catching range                                                                                |                         | ±7   | -    | -                    | %    |

| Z <sub>src</sub>      | source impedance                                                                                          |                         | -    | -    | 250                  | Ω    |

| CI                    | input capacitance                                                                                         |                         | -    | -    | 10                   | pF   |

| IREF                  |                                                                                                           |                         |      |      |                      |      |

| R <sub>g</sub>        | resistor to ground                                                                                        |                         | -    | 27   | -                    | kΩ   |

| POL                   |                                                                                                           | ·                       | ·    | ·    |                      |      |

| V <sub>IL</sub>       | input voltage LOW                                                                                         |                         | -0.3 | -    | 0.8                  | V    |

| VIH                   | input voltage HIGH                                                                                        |                         | 2.0  | -    | V <sub>DD</sub> +0.5 | V    |

| ILI                   | input leakage current                                                                                     | $V_{I} = 0$ to $V_{DD}$ | -10  | -    | 10                   | μA   |

| CI                    | input capacitance                                                                                         |                         | -    | -    | 10                   | pF   |

| LFB                   |                                                                                                           |                         |      |      |                      |      |

| V <sub>IL</sub>       | input voltage LOW                                                                                         |                         | -0.3 | -    | 0.8                  | V    |

| VIH                   | input voltage HIGH                                                                                        |                         | 2.0  | -    | V <sub>DD</sub> +0.5 | V    |

| ILI                   | input leakage current                                                                                     | $V_{I} = 0$ to $V_{DD}$ | -10  | -    | 10                   | μA   |

| I                     | input current                                                                                             | note 1                  | -1   | -    | 1                    | mA   |

| t <sub>LFB</sub>      | delay between LFB front edge and input video line sync                                                    |                         | -    | 250  | -                    | ns   |

| VCR/FFB               |                                                                                                           |                         |      |      |                      |      |

| V <sub>IL</sub>       | input voltage LOW                                                                                         |                         | -0.3 | -    | 0.8                  | V    |

| V <sub>IH</sub>       | input voltage HIGH                                                                                        |                         | 2.0  | -    | V <sub>DD</sub> +.5  | V    |

| ILI                   | input leakage current                                                                                     | $V_{I} = 0$ to $V_{DD}$ | -10  | -    | 10                   | μA   |

| l <sub>l</sub>        | input current                                                                                             | note 1                  | -1   | -    | 1                    | mA   |

### SAA5244A

| SYMBOL            | PARAMETER                   | CONDITIONS              | MIN. | TYP. | MAX.                 | UNIT |

|-------------------|-----------------------------|-------------------------|------|------|----------------------|------|

| Inputs            |                             |                         | •    | •    |                      |      |

| RGBREF (N         | IOTE 2)                     |                         |      |      |                      |      |

| VI                | input voltage               |                         | -0.3 | -    | V <sub>DD</sub> +0.5 | V    |

| ILI               | input leakage current       | $V_{I} = 0$ to $V_{DD}$ | -10  | -    | 10                   | μA   |

| I <sub>DC</sub>   | DC current                  |                         | -    | -    | 10                   | mA   |

| SCL               |                             |                         |      | 1    | - 1                  |      |

| V <sub>IL</sub>   | input voltage LOW           |                         | -0.3 | _    | 1.5                  | V    |

| V <sub>IH</sub>   | input voltage HIGH          |                         | 3.0  | _    | V <sub>DD</sub> +0.5 | V    |

| ILI               | input leakage current       | $V_{I} = 0$ to $V_{DD}$ | -10  | -    | 10                   | μA   |

| f <sub>SCL</sub>  | clock frequency             |                         | 0    | -    | 100                  | kHz  |

| t <sub>r</sub>    | input rise time             | 10% to 90%              | -    | -    | 2                    | μs   |

| t <sub>f</sub>    | input fall time             | 90% to 10%              | -    | -    | 2                    | μs   |

| CI                | input capacitance           |                         | -    | -    | 10                   | pF   |

| Inputs/outp       | outs                        |                         | •    | ·    |                      |      |

| CRYSTAL OS        | CILLATOR (OSCIN; OSCOUT)    |                         |      |      |                      |      |

| f <sub>XTAL</sub> | crystal frequency           |                         | _    | 27   | _                    | MHz  |

| G <sub>v</sub>    | small signal voltage gain   |                         | 3.5  | -    | -                    | _    |

| G <sub>m</sub>    | mutual conductance          | f = 100 kHz             | 1.5  | -    | -                    | mA/V |

| Cl                | input capacitance           |                         | -    | -    | 10                   | pF   |

| C <sub>FB</sub>   | feedback capacitance        |                         | -    | -    | 5                    | pF   |

| BLACK             |                             |                         |      |      |                      | ·    |

| C <sub>blk</sub>  | storage capacitor to ground |                         | -    | 100  | -                    | nF   |

| ILI               | input leakage current       | $V_{I} = 0$ to $V_{DD}$ | -10  | -    | 10                   | μA   |

| SDA               |                             | ŀ                       | •    |      |                      | •    |

| V <sub>IL</sub>   | input voltage LOW           |                         | -0.3 | -    | 1.5                  | V    |

| VIH               | input voltage HIGH          |                         | 3.0  | _    | V <sub>DD</sub> +0.5 | V    |

| ILI               | input leakage current       | $V_{I} = 0$ to $V_{DD}$ | -10  | -    | 10                   | μA   |

| CI                | input capacitance           |                         | -    | -    | 10                   | pF   |

| t <sub>r</sub>    | input rise time             | 10% to 90%              | -    | -    | 2                    | μs   |

| t <sub>f</sub>    | input fall time             | 90% to 10%              | -    | -    | 2                    | μs   |

| V <sub>OL</sub>   | output voltage LOW          | I <sub>OL</sub> = 3 mA  | 0    | -    | 0.5                  | V    |

| t <sub>f</sub>    | output fall time            | 3 to 1 V                | -    | -    | 200                  | ns   |

| CL                | load capacitance            |                         | _    | -    | 400                  | pF   |

### SAA5244A

| SYMBOL           | PARAMETER                                               | CONDITIONS                                                                                             | MIN.                 | TYP.   | MAX.              | UNIT |

|------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------|--------|-------------------|------|

| Outputs          |                                                         |                                                                                                        | -                    | -      | 4                 | -1   |

| STTV             |                                                         |                                                                                                        |                      |        |                   |      |

| G <sub>stt</sub> | gain of STTV relative to video input                    |                                                                                                        | 0.9                  | 1.0    | 1.1               |      |

| V <sub>tcs</sub> | TCS amplitude                                           |                                                                                                        | 0.2                  | 0.3    | 0.45              | V    |

| V <sub>DCs</sub> | DC shift between TCS output<br>and nominal video output |                                                                                                        | -                    | -      | 0.15              | V    |

| lo               | output drive current                                    |                                                                                                        | -                    | _      | 3.0               | mA   |

| CL               | load capacitance                                        |                                                                                                        | -                    | -      | 100               | pF   |

| R, G AND B       |                                                         |                                                                                                        |                      |        | •                 |      |

| V <sub>OL</sub>  | output voltage LOW                                      | I <sub>OL</sub> = 2 mA                                                                                 | 0                    | -      | 0.2               | V    |

| V <sub>OH</sub>  | output voltage HIGH                                     | $\begin{array}{l} I_{OH} = -1.6 \text{ mA}; \\ \text{RGBREF} \leq \\ V_{DD} - 2 \text{ V} \end{array}$ | RGBREF<br>-0.25 V    | RGBREF | RGBREF<br>+0.25 V | V    |

| Z <sub>o</sub>   | output impedance                                        |                                                                                                        | -                    | -      | 200               | Ω    |

| CL               | load capacitance                                        |                                                                                                        | -                    | -      | 50                | pF   |

| I <sub>DC</sub>  | DC current                                              |                                                                                                        | -                    | -      | -3.3              | mA   |

| t <sub>r</sub>   | output rise time                                        | 10% to 90%                                                                                             | -                    | -      | 20                | ns   |

| t <sub>f</sub>   | output fall time                                        | 90% to 10%                                                                                             | -                    | -      | 20                | ns   |

| BLAN             |                                                         |                                                                                                        |                      |        |                   |      |

| V <sub>OL</sub>  | output voltage LOW                                      | I <sub>OL</sub> = 1.6 mA                                                                               | 0                    | -      | 0.4               | V    |

| V <sub>OH</sub>  | output voltage HIGH                                     | I <sub>OH</sub> = -0.2 mA;<br>V <sub>DD</sub> = 4.5 V                                                  | 1.1                  | -      | -                 | V    |

| V <sub>OH</sub>  | output voltage HIGH                                     | I <sub>OH</sub> = 0 mA;<br>V <sub>DD</sub> = 5.5 V                                                     | -                    | -      | 2.8               | V    |

| V <sub>OH</sub>  | allowed voltage at pin                                  | with external pull-up                                                                                  | -                    | -      | V <sub>DD</sub>   | V    |

| CL               | load capacitance                                        |                                                                                                        | -                    | -      | 50                | pF   |

| t <sub>r</sub>   | output rise time                                        | 10% to 90%                                                                                             | -                    | -      | 20                | ns   |

| t <sub>f</sub>   | output fall time                                        | 90% to 10%                                                                                             | -                    | _      | 20                | ns   |

| ODD/EVEN         |                                                         |                                                                                                        |                      |        |                   | -    |

| V <sub>OL</sub>  | output voltage LOW                                      | I <sub>OL</sub> = 1.6 mA                                                                               | 0                    | -      | 0.4               | V    |

| V <sub>OH</sub>  | output voltage HIGH                                     | I <sub>OH</sub> = -1.6 mA                                                                              | V <sub>DD</sub> -0.4 | -      | V <sub>DD</sub>   | V    |

| CL               | load capacitance                                        |                                                                                                        | -                    | -      | 120               | pF   |

| t <sub>r</sub>   | output rise time                                        | 0.6 to 2.2 V                                                                                           | -                    | -      | 50                | ns   |

| t <sub>f</sub>   | output fall time                                        | 2.2 to 0.6 V                                                                                           | -                    | -      | 50                | ns   |

### SAA5244A

| SYMBOL               | PARAMETER                                                         | CONDITIONS                                                                                           | MIN. | TYP.       | MAX.            | UNIT |

|----------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|------------|-----------------|------|

| Outputs              |                                                                   |                                                                                                      |      | - <b>I</b> |                 |      |

| COR AND Y            | (OPEN DRAIN)                                                      |                                                                                                      |      |            |                 |      |

| V <sub>OH</sub>      | pull-up voltage at pin                                            |                                                                                                      | -    | -          | V <sub>DD</sub> | V    |

| V <sub>OL</sub>      | output voltage LOW                                                | I <sub>OL</sub> = 5 mA                                                                               | 0    | -          | 1.0             | V    |

| CL                   | load capacitance                                                  |                                                                                                      | -    | -          | 25              | pF   |

| t <sub>f</sub>       | output fall time                                                  | load resistor of 1.2 k $\Omega$ to V <sub>DD</sub> ; measured between V <sub>DD</sub> –0.5 and 1.5 V | -    | -          | 50              | ns   |

| I <sub>LO</sub>      | output leakage current                                            | $V_{I} = 0$ to $V_{DD}$                                                                              | -10  | -          | 10              | μA   |

| Τ <sub>SK</sub>      | skew delay between display<br>outputs R, G, B, COR, Y and<br>BLAN |                                                                                                      | -    | -          | 20              | ns   |

| Timing               |                                                                   |                                                                                                      |      | ·          |                 |      |

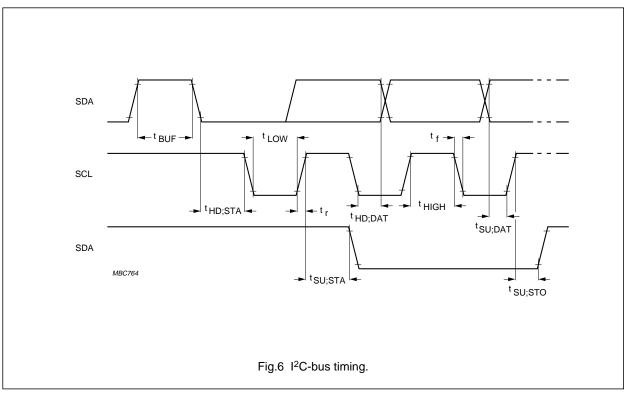

| I <sup>2</sup> C-BUS |                                                                   |                                                                                                      |      |            |                 |      |

| t <sub>LOW</sub>     | clock LOW period                                                  |                                                                                                      | 4    | -          | -               | μs   |

| t <sub>HIGH</sub>    | clock HIGH period                                                 |                                                                                                      | 4    | -          | -               | μs   |

| t <sub>SU;DAT</sub>  | data set-up time                                                  |                                                                                                      | 250  | -          | -               | ns   |

| t <sub>HD;DAT</sub>  | data hold time                                                    |                                                                                                      | 170  | -          | -               | ns   |

| t <sub>SU;STO</sub>  | set-up time from clock HIGH to STOP                               |                                                                                                      | 4    | -          | -               | μs   |

| t <sub>BUF</sub>     | START set-up time following a STOP                                |                                                                                                      | 4    | -          | -               | μs   |

| t <sub>HD;STA</sub>  | START hold time                                                   |                                                                                                      | 4    | -          | -               | μs   |

| t <sub>SU;STA</sub>  | START set-up time following<br>clock LOW-to-HIGH transition       |                                                                                                      | 4    | -          | -               | μs   |

#### Notes to the characteristics

- 1. This current is the maximum allowed into the inputs when line and field flyback signals are connected to these inputs. Series current limiting resistors must be used to limit the input currents to  $\pm 1$  mA.

- 2. RGBREF is the positive supply for the RGB output pins and it must be able to source the I<sub>OH</sub> current from the R, G and B pins. The leakage specification on RGBREF only applies when there is no current load on the RGB pins.

# Integrated VIP and teletext decoder (IVT1.1)

## Integrated VIP and teletext decoder (IVT1.1)

#### **APPLICATION INFORMATION**

SAA5244A

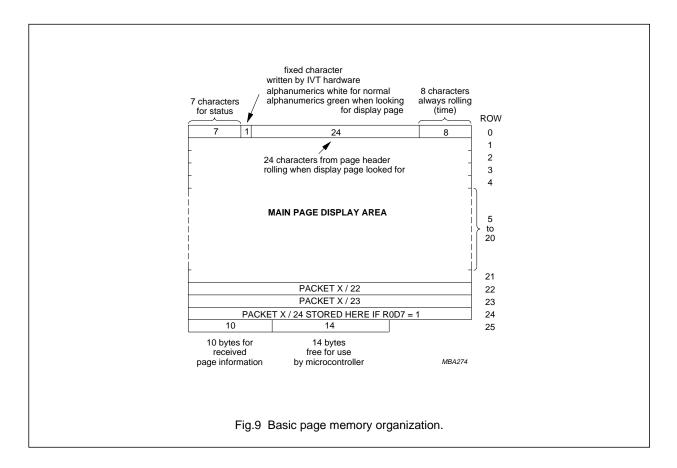

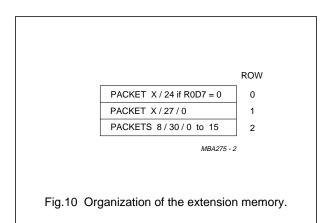

#### SAA5244A page memory organization

The organization of the page memory is shown in Fig.9. The device provides an additional row as compared with first generation decoders; this brings the display format up to 40 characters by 25 rows. Rows 0 to 23 form the teletext page; row 24 is available for software generated status messages and FLOF/FASTEXT prompt information.

#### Row 0:

Row 0 is for the page header. The first seven columns (0 to 6) are free for status messages. The eighth is an alphanumeric white or green control character, written automatically by SAA5244A to give a green rolling header when a page is being looked for. The last eight characters are for rolling time.

#### Row 25:

The first 10 bytes of row 25 contain control data relating to the received page as shown in Table 1. The remaining 14 bytes are free for use by the microcomputer.

## Integrated VIP and teletext decoder (IVT1.1)

#### D0 PU0 PT0 MU0 MT0 HU0 HT0 C7 C11 MAG0 0 D1 PU1 PT1 0 MU1 MT1 HU1 HT1 C8 C12 MAG1 D2 PU2 PT2 MU2 MT2 HU2 C5 C9 C13 MAG2 0 PU3 C10 D3 PT3 MU3 C4 HU3 C6 C14 0 0 D4 HAM.ER HAM.ER HAM.ER HAM.ER HAM.ER HAM.ER HAM.ER HAM.ER FOUND 0 D5 0 0 PBLF 0 0 0 0 0 0 0 0 0 0 0 D6 0 0 0 0 0 0 D7 0 0 0 0 0 0 0 0 0 0 Column 0 1 2 3 4 5 6 7 8 9

#### Table 1 Row 25 received control data format

Where:

| Page number   |                                     |

|---------------|-------------------------------------|

| MAG           | magazine                            |

| PU            | page units                          |

| PT            | page tens                           |

| PBLF          | page being looked for               |

| FOUND         | LOW for page has been found         |

| HAM.ER        | Hamming error in corresponding byte |

| Page sub-code |                                     |

| MU            | minutes units                       |

| MT            | minutes tens                        |

| HU            | hours units                         |

| HT            | hours tens                          |

| C4-C14        | transmitted control bits.           |

### SAA5244A

#### Register maps

SAA5244A mode registers R0 to R11 are shown in Table 2. R0 to R10 are WRITE only; R11 is READ/WRITE. Register map (R3), for page requests, is shown in detail in Table 3.

#### REGISTER D7 D4 D3 D2 D1 D0 D6 D5 FREE AUTO DISABLE DISABLE R11/R11B Adv. 0 X24 \_ POS **RUN PLL** ODD/ HDR ODD/ control SELECT EVEN ROLL EVEN Mode 1 VCS TO ACQ DEW/ TCS T1 Τ0 **ON/OFF** FULL SCS ON FIELD Page 2 TΒ START START START \_ \_ \_ request COLUMN COLUMN COLUMN address SC2 SC1 SC0 Page 3 PRD4 PRD3 PRD2 PRD1 PRD0 \_ \_ \_ request data 5 BKGND COR COR TEXT PON PON Display BKGND TEXT control OUT IN OUT IN OUT IN OUT IN (normal) TEXT Display 6 BKGND BKGND COR COR TEXT PON PON control OUT IN OUT IN OUT IN OUT IN (newsflash /subtitle) Display 7 STATUS CURSOR REVEAL BOTTOM DOUBLE BOX BOX BOX mode TOP ON HALF HEIGHT 24 1-23 ON 0 \_ Cursor 9 SUPPL. CLEAR A0 R4 R3 R2 R1 R0 row BLAST MEM. Cursor 10 SUPPL. SUPPL. C5 C4 C3 C2 C1 C0 **ROW 24** ROW 0 column D6 Cursor 11 \_ D5 D4 D3 D2 D1 D0 data VCS Device 11B 625/525 ROM ROM ROM ROM ROM TEXT status SYNC VER R4 VER R3 VER R2 VER R1 VER R0 SIGNAL SIGNAL QUALITY QUALITY

#### Table 2 Register map

#### Notes to Table 2

- 1. '- ' indicates these bits are inactive and must be written to logic 0 for future compatibility.

- 2. All bits in registers R0 to R10 are cleared to logic 0 on power-up except bits D0 to D1 of registers R1, R5 and R6 which are set to logic 1.

- 3. All memory is cleared to 'space' (00100000) on power-up, except row 0 column 7 chapter 0, which is 'alpha' white (00000111) as the acquisition circuit is enabled but the page is on hold.

- 4. TB must be set to logic 0 for normal operation.

- 5. The I<sup>2</sup>C slave address is 0010001

## Integrated VIP and teletext decoder (IVT1.1)

#### **REGISTER DESCRIPTION**

#### **R0 ADVANCED CONTROL - auto increments to Register 1** R11/R11B Selects reading of R11 or R11B SELECT DISABLE Forces ODD/EVEN output LOW when logic 1 ODD/EVEN DISABLE HDR Disables green rolling header and time ROLL AUTO ODD/EVEN When set forces ODD/EVEN low if any TV picture displayed, if DISABLE ODD/EVEN = 0 FREE RUN PLL Will force the PLL to free run in all conditions X24 POS Automatic display of FASTEXT prompt row when logic 1 R1 MODE - auto increments to Register 2 T0, T1 Interlace/non-interlace 312/313 line control (see Table 4) TCS ON Text composite sync or direct sync select DEW/FULL FIELD Field-flyback or full channel mode ACQ ON/OFF Acquisition circuits turned off when logic 1 VCS TO SCS When logic 1 enables display of messages with 60 Hz input signal **R2 PAGE REQUEST ADDRESS - auto increments to Register 3** COL SC0 - SC2 Point to start column for page request data (see Table 3) ΤВ Must be logic 0 for normal operation R3 PAGE REQUEST DATA - does not auto increment (see Table 3)

#### **R5 NORMAL DISPLAY CONTROL - auto increments to Register 6**

#### R6 NEWSFLASH/SUBTITLE DISPLAY CONTROL - auto increments to Register 7

| PON                  | Picture on                                                                   |

|----------------------|------------------------------------------------------------------------------|

| TEXT                 | Text on                                                                      |

| COR                  | Contrast reduction on                                                        |

| BKGND                | Background colour on                                                         |

| These functions have | IN and OUT referring to inside and outside the boxing function respectively. |

| R7 DISPLAY MODE      | - does not auto increment                                                    |

| BOX ON 0             | Boxing function allowed on Row 0                                             |

| BOX ON 1-23          | Boxing function allowed on Row 1-23                                          |

| BOX ON 24            | Boxing function allowed on Row 24                                            |

| DOUBLE HEIGHT        | To display double height text                                                |

| BOTTOM HALF          | To select bottom half of page when DOUBLE HEIGHT = 1                         |

| REVEAL ON            | To reveal concealed text                                                     |

| CURSOR ON            | To display cursor                                                            |

| STATUS TOP           | Row 25 displayed above or below the main text                                |

### SAA5244A

| <b>R9 CURSOR ROW</b>   | - auto increments to Register 10                                                                                                                                 |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0 to R4               | Active row for data written to or read from memory via the I <sup>2</sup> C-bus                                                                                  |

| A0                     | Selects display memory page (when = 0) or extension packet memory (when = 1)                                                                                     |

| CLEAR MEM.             | When set to 1, clears the display memory.<br>This bit is automatically reset                                                                                     |

| SUPPL. BLAST           | When set to 1, column 4b and 5b (of Table 6) are mapped into 4 and 5 respectively, replacing blast-through alphanumerics in graphics mode                        |

| R10 CURSOR COL         | UMN - auto increments to Register 11 or 11B                                                                                                                      |

| C0 to C5               | Active column for data written to or read from memory via the I <sup>2</sup> C-bus                                                                               |

| SUPPL. ROW 0           | When set to 1, column 4b and 5b (of Table 6) are mapped into columns 6 and 7 respectively, just for row 0 columns 0 to 7                                         |

| SUPPL. ROW 24          | When set to 1, column 4b and 5b (of Table 6) are mapped into columns 6 and 7 respectively just for row 24                                                        |

| R11 CURSOR DAT         | A - does not auto increment                                                                                                                                      |

| D0 to D6               | Data read from/written to memory via I <sup>2</sup> C, at location pointed to by R9 and R10.<br>This location automatically increments each time R11 is accessed |

| R11B DEVICE STA        | TUS - does not auto increment                                                                                                                                    |

| VCS SIGNAL<br>QUALITY  | Indicates that the video signal quality is good and PLL is phase locked to input video when = 1                                                                  |

| TEXT SIGNAL<br>QUALITY | If a good teletext signal is being received when = 1                                                                                                             |

| ROM VER R0 to<br>R4    | Indicated language/ROM variant. For Western European = 01000                                                                                                     |

|                        |                                                                                                                                                                  |

625/525 SYNC If the input video is a 525 line signal when = 1

### SAA5244A

| START<br>COLUMN | PRD4          | PRD3 | PRD2 | PRD1 | PRD0 |

|-----------------|---------------|------|------|------|------|

| 0               | Do care       |      |      |      |      |

|                 | Magazine      | HOLD | MAG2 | MAG1 | MAG0 |

| 1               | Do care       |      |      |      |      |

|                 | Page tens     | PT3  | PT2  | PT1  | PT0  |

| 2               | Do care       |      |      |      |      |

|                 | Page units    | PU3  | PU2  | PU1  | PU0  |

| 3               | Do care       |      |      |      |      |

|                 | Hours tens    | X    | X    | HT1  | НТ0  |

| 4               | Do care       |      |      |      |      |

|                 | Hours units   | HU3  | HU2  | HU1  | HU0  |

| 5               | Do care       |      |      |      |      |

|                 | Minutes tens  | x    | MT2  | MT1  | мто  |

| 6               | Do care       |      |      |      |      |

|                 | Minutes units | MU3  | MU2  | MU1  | MUO  |

#### Table 3 Register map for page requests (R3)

#### Notes to Table 3

- 1. Abbreviations are as for Table 1 except for DO CARE bits.

- 2. When the DO CARE bit is set to logic 1 this means the corresponding digit is to be taken into account for page requests. If the DO CARE bit is set to logic 0 the digit is ignored. This allows, for example, 'normal' or 'timed page' selection.

- 3. If HOLD is set LOW, the page is held and not updated.

- 4. Columns auto-increment on successive I<sup>2</sup>C-bus transmission bytes.

| Table 4 | Interlace/non-interlace | 312/313 line | control (T0 and T1) |

|---------|-------------------------|--------------|---------------------|

|---------|-------------------------|--------------|---------------------|

| T1 | ТО | RESULT                                |

|----|----|---------------------------------------|

| 0  | 0  | interlaced 312.5/312.5 lines          |

| 0  | 1  | non-interlaced 312/313 lines (note 1) |

| 1  | 0  | non-interlaced 312/312 lines (note 1) |

| 1  | 1  | scan-locked                           |

#### Note to Table 4

1. Reverts to interlaced mode if a newsflash or subtitle is being displayed.

## Integrated VIP and teletext decoder (IVT1.1)

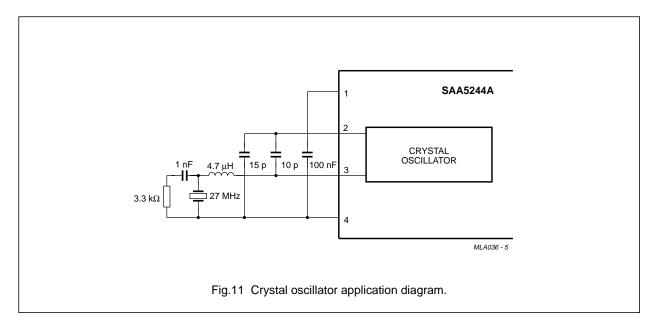

### Table 5 Crystal characteristics

| SYMBOL           | PARAMETER            | MIN. | TYP. | MAX. | UNIT                 |

|------------------|----------------------|------|------|------|----------------------|

| Crystal (27 MHz, | 3rd overtone)        | ·    |      |      |                      |

| C1               | series capacitance   | -    | 1.7  | -    | pF                   |

| C0               | parallel capacitance | -    | 5.2  | -    | pF                   |

| CL               | load capacitance     | -    | 20   | -    | pF                   |

| Rr               | resonant resistance  | -    | -    | 50   | Ω                    |

| R1               | series resistance    | -    | 20   | -    | Ω                    |

| Ха               | ageing               | -    | -    | ±5   | 10 <sup>-6</sup> /yr |

| Xj               | adjustment tolerance | -    | -    | ±25  | 10 <sup>-6</sup>     |

| Xd               | drift                | -    | -    | ±25  | 10 <sup>-6</sup>     |

#### **CLOCK SYSTEMS**

#### **Crystal oscillator**

The crystal is a conventional 2-pin design operating at 27 MHz. It is capable of oscillating with both fundamental and third overtone mode crystals. External components should be used to suppress the fundamental output of the third overtone, as shown in Fig.11. The crystal characteristics are given in Table 5.

#### Product specification

SAA5244A

## Integrated VIP and teletext decoder (IVT1.1)

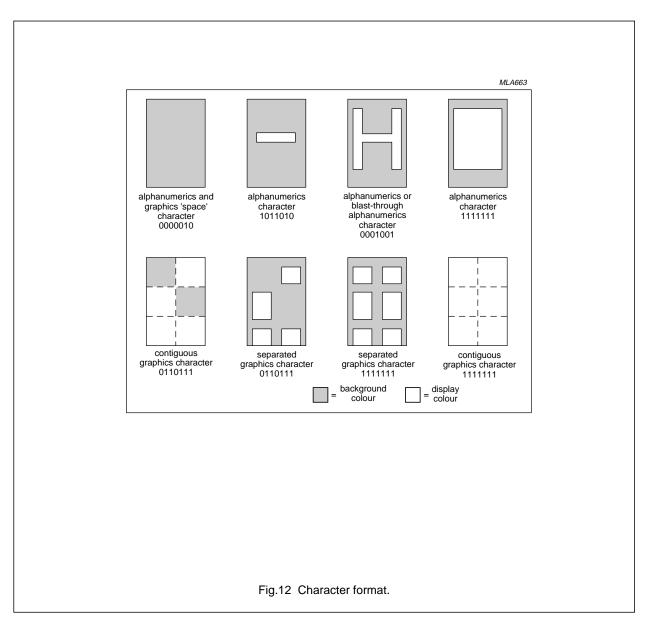

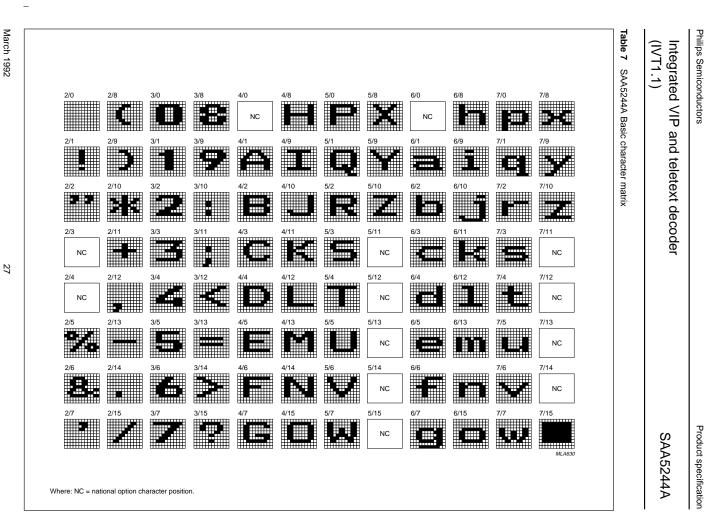

#### Character sets

The WST specification allows the selection of national character sets via the page header transmission bits, C12 to C14. The basic 96 character sets differ only in 13

national option characters as indicated in Table 8 with reference to their table position in the basic character matrix illustrated in Table 7. The SAA5244A automatically decodes transmission bits C12 to C14. Table 6 illustrates the character matrices.

#### b7 1 1 0 0 0 0 0 1 1 b<sub>6</sub> AVAILABLE AS NATIONAL OPTIONS ONLY 0 0 0 0 T S 1 1 1 b<sub>5</sub> 0 0 0 0 0 1 1 1 1 b4 b3 b2 b1 olumn 5b <sup>+</sup> 0 1 2 3 4 4b <sup>-</sup> 5 6 6a 3a 7 7a ŧ. Ť. \* \* 2a alpha -numerics black S ø É é à P graphics black 0 Υ. (a р 0 0 0 0 0 alpha -numerics red é Α ù 1 ₽ QQ è graphics red ļ 0 0 0 1 1 а q alpha -numerics 2 14 à â ä 77 B R graphics green b 1 0 0 0 2 areen é alpha -numerics yellow graphics yellow £ С " 5 » # £ # 3 C S 0 0 1 1 3 alpha -numerics blue \$ \$ ï 4 graphics blue \$ Т Ο d t X D 0 1 0 0 4 alpha -numerics magenta graphics magenta % 5 U E e u 0 1 0 1 5 alpha -numerics Φ ¢ 8. F ۷ f 6 graphics cyan 0 1 1 0 6 cyan alpha -numerics 7 G ٧F WPS graphics white g W 0 1 1 1 7 white Ô 8 ł ö ò conceal display C Н Х Ť h 1 0 0 0 8 flash х å + Ι 3, è û 9 Υ ➔ ī contiguous graphics ) У 1 0 0 1 9 steady Œ ÷ ü ì \* Ζ J separated 1 1 Ç Z 1 0 1 0 10 end box graphics Ð К Ä D) Ā ø k ÷ + . e 1 0 1 1 11 start box ESC Ð ê 12 2 1 Ö Ö black back -< Ç 1 1 0 0 12 normal hight Õ 2 ground new back -ground Å Ü -> -> 1 1 0 1 ٨v m 13 double height m u î Λ ſ hold graphics Ü 1 1 1 0 14 SO n # release graphics # ? Π 1 1 1 1 15 SI O MBA266 - 1

#### Table 6 SAA5244P/A character data input decoding

#### Notes to Table 6 - For character version number (01000) see Register 11B

- 1. \* These control characters are reserved for compatibility with other data codes.

- 2. \*\* These control characters are presumed before each row begins.

- 3. + Columns 4b and 5b can only be accessed when supplementary character bits are set (see Registers 9 and 10).

- 4. Control characters shown in columns 0 and 1 are normally displayed as spaces.

- 5. Characters may be referred to by column and row, For example 2/5 refers to %.

March 1992

#### Product specification

SAA5244A

### SAA5244A

- 6. Black represents displayed colour. White represents background.

- 7. Character rectangle shown as follows:

- 8. The SAA5244A national option characters are illustrated in Table 8.

- 9. Characters 4b/11, 4b/12, 5b/10, 5b/11 and 5b/12 are special characters for combining with character 4b/10.

- 10. National option characters will be developed according to the setting of control bits C12 to C14. These will be mapped into the basic code table into positions shown in Table 8.

- 11. Columns 4b and 5b are mapped into 4 and 5 respectively (replacing blast-through alphanumerics in the graphics mode) when enabled by R9 bit D7 set to 1.

- 12. Columns 4b and 5b are mapped into columns 6 and 7 respectively when enabled by R10 bit D6 (row 0 columns 0 to 7) and R10 bit D7 (row 24) set to 1.

- 13. Columns 2a, 3a, 6a and 7a are displayed in graphics mode.

March 1992

Downloaded from Elcodis.com electronic components distributor

### SAA5244A

|          | PHCB <sup>(1)</sup> |     |     |     | CHARACTER POSITION (COLUMN / ROW) |     |      |      |      |      |        |     |      |      |      |      |

|----------|---------------------|-----|-----|-----|-----------------------------------|-----|------|------|------|------|--------|-----|------|------|------|------|

| LANGUAGE | C12                 | C13 | C14 | 2/3 | 2/4                               | 4/0 | 5/11 | 5/12 | 5/13 | 5/14 | 5 / 15 | 6/0 | 7/11 | 7/12 | 7/13 | 7/14 |

| ENGLISH  | 0                   | 0   | 0   | £   | \$                                | 0   | +    | 12   | +    | ↑    | #      |     | 14   |      | 3,   | -    |

| GERMAN   | 0                   | 0   | 1   | #   | \$                                | S   | Ä    | Ö    | Ü    | ^    |        | •   | ä    | ö    | ü    | ß    |

| SWEDISH  | 0                   | 1   | 0   | #   | X                                 | É   | Ä    | Ö    | Å    | Ü    |        | é   | ä    | ö    | å    | ü    |

| ITALIAN  | 0                   | 1   | 1   | £   | \$                                | é   | •    | ç    | Ŧ    | ↑    | #      | ù   | à    | ò    | è    | ì    |

| FRENCH   | 1                   | 0   | 0   | é   | ï                                 | à   | ë    | ê    | ù    | î    | #      | è   | â    | Ô    | ů    | ç    |

#### Table 8 SAA5244A national option character set

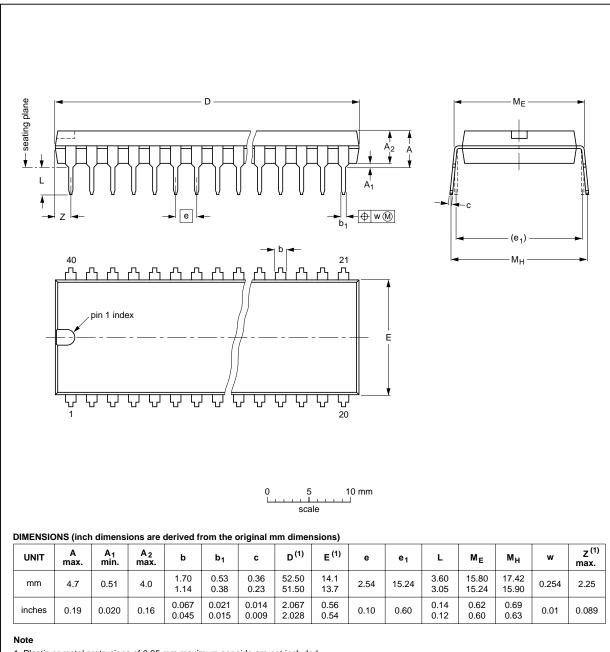

SOT129-1

## Integrated VIP and teletext decoder (IVT1.1)

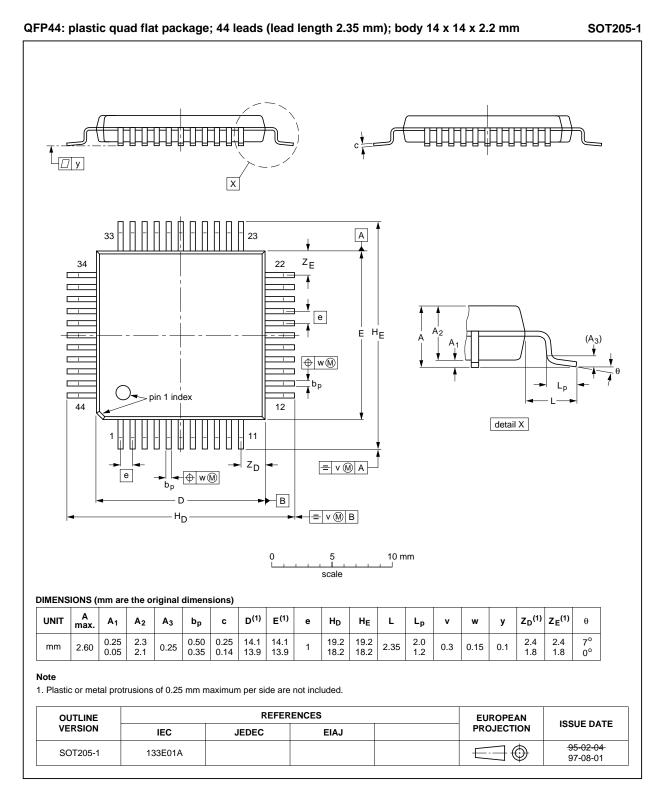

#### PACKAGE OUTLINES

#### DIP40: plastic dual in-line package; 40 leads (600 mil)

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |        | REFER    | ENCES | EUROPEAN   | ISSUE DATE                      |  |

|----------|--------|----------|-------|------------|---------------------------------|--|

| VERSION  | IEC    | JEDEC    | EIAJ  | PROJECTION | ISSUE DATE                      |  |

| SOT129-1 | 051G08 | MO-015AJ |       |            | <del>92-11-17</del><br>95-01-14 |  |

### SAA5244A

#### Product specification

### Integrated VIP and teletext decoder (IVT1.1)

### SOLDERING

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

#### DIP

#### SOLDERING BY DIPPING OR BY WAVE

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature ( $T_{stg max}$ ). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### REPAIRING SOLDERED JOINTS

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

#### QFP

#### **REFLOW SOLDERING**

### Reflow soldering techniques are suitable for all QFP packages.

The choice of heating method may be influenced by larger plastic QFP packages (44 leads, or more). If infrared or vapour phase heating is used and the large packages are not absolutely dry (less than 0.1% moisture content by weight), vaporization of the small amount of moisture in them can cause cracking of the plastic body. For more information, refer to the Drypack chapter in our *"Quality Reference Handbook"* (order code 9397 750 00192).

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary from 50 to 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheat for 45 minutes at 45 °C.

#### WAVE SOLDERING

Wave soldering is **not** recommended for QFP packages. This is because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices.

### If wave soldering cannot be avoided, the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The footprint must be at an angle of 45° to the board direction and must incorporate solder thieves downstream and at the side corners.

#### Even with these conditions, do not consider wave soldering the following packages: QFP52 (SOT379-1), QFP100 (SOT317-1), QFP100 (SOT317-2), QFP100 (SOT382-1) or QFP160 (SOT322-1).

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured. Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### **REPAIRING SOLDERED JOINTS**

Fix the component by first soldering two diagonallyopposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

March 1992

### SAA5244A

### SAA5244A

#### DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.       |  |  |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |  |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                |  |  |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |  |  |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                       |  |  |  |  |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |  |  |  |  |

| Where application information is given, it is advisory and does not form part of the specification.                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |  |  |  |  |

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

#### PURCHASE OF PHILIPS I<sup>2</sup>C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.