# HIGH SPEED 16K x 8 CMOS EPROM

### **KEY FEATURES**

- Very Fast Access Time

- 35 ns

- Low Power Consumption

- EPI Processing

- Latch-up Immunity Up to 200 mA

- Standard EPROM Pinout

- DIP and Surface Mount Packaging Available

### GENERAL DESCRIPTION

The WS57C128FB is a High Performance 128K UV Erasable Electrically Programmable Read Only Memory. It is manufactured with an advanced CMOS technology which enables it to operate at Bipolar speeds while consuming only 90 mA.

Two major features of the WS57C128FB are its Low Power and High Speed. These features make it an ideal solution for applications which require fast access times, low power, and non-volatility. Typical applications include systems which do not utilize mass storage devices and/or are board space limited.

The WS57C128FB is configured in the standard EPROM pinout which provides an easy upgrade path for systems which are currently using standard EPROMs. The EPROMs are available in both 600 Mil DIP packages, and both J-leaded and leadless surface mount packages.

### **MODE SELECTION**

| PINS<br>MODE       | PGM      | CE              | ŌĒ              | V <sub>PP</sub> | v <sub>cc</sub> | OUTPUTS          |

|--------------------|----------|-----------------|-----------------|-----------------|-----------------|------------------|

| Read               | Х        | $V_{IL}$        | V <sub>IL</sub> | Vсс             | Vcc             | D <sub>OUT</sub> |

| Output<br>Disable  | Х        | X               | ٧ <sub>IH</sub> | Vсс             | Vcc             | High Z           |

| Standby            | Х        | ٧ <sub>IH</sub> | Х               | Vсс             | VCC             | High Z           |

| Program            | $V_{IL}$ | $\vee_{IL}$     | $V_{IH}$        | $V_{PP}$        | VCC             | D <sub>IN</sub>  |

| Program<br>Verify  | VIH      | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>PP</sub> | Vcc             | DOUT             |

| Program<br>Inhibit | Х        | V <sub>IH</sub> | Х               | V <sub>PP</sub> | VCC             | High Z           |

$<sup>\</sup>rm X$  can be  $\rm V_{IL}$  or  $\rm V_{IH}.$

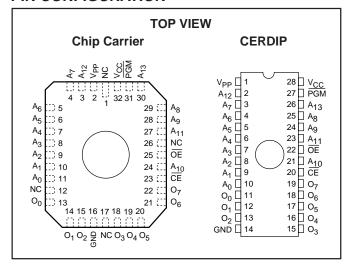

### PIN CONFIGURATION

### PRODUCT SELECTION GUIDE

| PARAMETER                 | WS57C128FB-35 | WS57C128FB-45 | WS57C128FB-55 | WS57C128FB-70 |

|---------------------------|---------------|---------------|---------------|---------------|

| Address Access Time (Max) | 35 ns         | 45 ns         | 55 ns         | 70 ns         |

| Chip Select Time (Max)    | 35 ns         | 45 ns         | 55 ns         | 70 ns         |

| Output Enable Time (Max)  | 20 ns         | 25 ns         | 25 ns         | 25 ns         |

## ABSOLUTE MAXIMUM RATINGS\*

| Storage Temperature                    | 65° to + 150°C |

|----------------------------------------|----------------|

| Voltage on any Pin with                |                |

| Respect to Ground                      | 0.6V to +7V    |

| V <sub>PP</sub> with Respect to Ground | 0.6V to + 13V  |

| ESD Protection                         | >2000V         |

### **OPERATING RANGE**

| RANGE      | TEMPERATURE     | V <sub>CC</sub> |  |  |

|------------|-----------------|-----------------|--|--|

| Commercial | 0°C to +70°C    | +5V ± 10%       |  |  |

| Industrial | -40°C to +85°C  | +5V ± 10%       |  |  |

| Military   | −55°C to +125°C | +5V ± 10%       |  |  |

## \*NOTICE:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

# $\label{eq:decomposition} \textit{DC READ CHARACTERISTICS} \quad \text{Over Operating Range with V}_{PP} = \text{V}_{CC}$

| SYMBOL           | PARAMETER                              | TEST CONDITI                     | ONS        | MIN                  | MAX                   | UNITS |

|------------------|----------------------------------------|----------------------------------|------------|----------------------|-----------------------|-------|

| $V_{IL}$         | Input Low Voltage                      | (Note 5)                         |            | -0.1                 | 0.8                   | V     |

| V <sub>IH</sub>  | Input High Voltage                     | (Note 5)                         |            | 2.0                  | V <sub>CC</sub> + 0.3 | V     |

| V <sub>OL</sub>  | Output Low Voltage                     | I <sub>OL</sub> = 16 mA          |            |                      | 0.4                   | V     |

| V <sub>OH</sub>  | Output High Voltage                    | $I_{OH} = -4 \text{ mA}$         |            | 2.4                  |                       | V     |

| I <sub>SB1</sub> | V <sub>CC</sub> Standby Current (CMOS) | (Notes 1 and 3)                  |            |                      | 500                   | μΑ    |

| I <sub>SB2</sub> | V <sub>CC</sub> Standby Current (TTL)  | (Notes 2 and 3)                  |            |                      | 15                    | mA    |

|                  |                                        | (Notes 1 and 4)                  | Comm'l     |                      | 30                    | mA    |

| I <sub>CC1</sub> | V <sub>CC</sub> Active Current (CMOS)  | Outputs Not Loaded               | Industrial |                      | 40                    | mA    |

|                  |                                        | Odipato Not Lodded               | Military   |                      | 40                    | mA    |

|                  |                                        | (Notes 2 and 4)                  | Comm'l     |                      | 50                    | mA    |

| I <sub>CC2</sub> | V <sub>CC</sub> Active Current (TTL)   | Outputs Not Loaded               | Industrial |                      | 60                    | mA    |

|                  |                                        | Odipato Not Lodded               | Military   |                      | 60                    | mA    |

| I <sub>PP</sub>  | V <sub>PP</sub> Supply Current         | $V_{PP} = V_{CC}$                |            |                      | 100                   | μΑ    |

| $V_{PP}$         | V <sub>PP</sub> Read Voltage           |                                  |            | V <sub>CC</sub> -0.4 | V <sub>CC</sub>       | V     |

| I <sub>LI</sub>  | Input Leakage Current                  | $V_{IN} = 5.5V$ or Gnd           |            | -10                  | 10                    | μΑ    |

| I <sub>LO</sub>  | Output Leakage Current                 | $V_{OUT} = 5.5 \text{ V or Gnd}$ |            | -10                  | 10                    | μA    |

NOTES:

- 1. CMOS inputs: GND  $\pm$  0.3V or  $V_{CC}$   $\pm$  0.3V.

- 2. TTL inputs:  $V_{IL} \le 0.8V$ ,  $V_{IH} \ge 2.0V$ .

- 3. Add 1 mA/MHz for A.C. power component.

- 4. Add 4 mA/MHz for A.C. power component.

- These are absolute voltages with respect to device ground pin and include all overshoots due to system and/or tester noise.Do not attempt to test these values without suitable equipment.

# **AC READ CHARACTERISTICS** Over Operating Range with $V_{PP} = V_{CC}$

| PARAMETER                         | SYMBOL           | 57C128 | 8FB-35 | 57C128 | BFB-45 | 57C128 | BFB-55 | 57C12 | 8FB-70 | UNITS |

|-----------------------------------|------------------|--------|--------|--------|--------|--------|--------|-------|--------|-------|

| TARAMETER                         | OTHER DE         | MIN    | MAX    | MIN    | MAX    | MIN    | MAX    | MIN   | MAX    | O.u.  |

| Address to Output Delay           | t <sub>ACC</sub> |        | 35     |        | 45     |        | 55     |       | 70     |       |

| CE to Output Delay                | t <sub>CE</sub>  |        | 35     |        | 45     |        | 55     |       | 70     |       |

| OE to Output Delay                | t <sub>OE</sub>  |        | 20     |        | 25     |        | 25     |       | 25     | ns    |

| Output Disable to<br>Output Float | t <sub>DF</sub>  |        | 20     |        | 25     |        | 25     |       | 25     |       |

| Address to Output Hold            | t <sub>OH</sub>  | 0      |        | 0      |        | 0      |        | 0     |        |       |

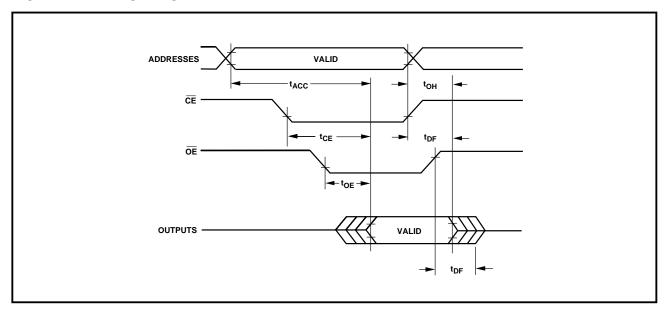

### AC READ TIMING DIAGRAM

## CAPACITANCE(6) T<sub>A</sub> = 25°C, f = 1 MHz

| SYMBOL           | PARAMETER                   | CONDITIONS            | TYP <sup>(7)</sup> | MAX | UNITS |

|------------------|-----------------------------|-----------------------|--------------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance           | $V_{IN} = 0V$         | 4                  | 6   | pF    |

| C <sub>OUT</sub> | Output Capacitance          | V <sub>OUT</sub> = 0V | 8                  | 12  | pF    |

| C <sub>VPP</sub> | V <sub>PP</sub> Capacitance | V <sub>PP</sub> = 0 V | 18                 | 25  | pF    |

NOTES: 6. This parameter is only sampled and is not 100% tested.

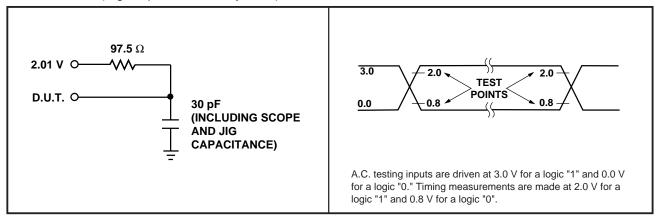

## TEST LOAD (High Impedance Test Systems)

### A.C. TESTING INPUT/OUTPUT WAVEFORM

NOTE: 8. Provide adequate decoupling capacitance as close as possible to this device to achieve the published A.C. and D.C. parameters.

A 0.1 microfarad capacitor in parallel with a 0.01 microfarad capacitor connected between V<sub>CC</sub> and ground is recommended.

Inadequate decoupling may result in access time degradation or other transient performance failures.

<sup>7.</sup> Typical values are for  $T_A = 25$ °C and nominal supply voltages.

## **PROGRAMMING INFORMATION**

**DC CHARACTERISTICS**  $(T_A = 25 \pm 5^{\circ}C, V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}, V_{PP} = 12.75 \pm 0.25 \text{ V})$

| SYMBOLS         | PARAMETER                                                                                         | MIN | MAX | UNITS |

|-----------------|---------------------------------------------------------------------------------------------------|-----|-----|-------|

| lu              | Input Leakage Current<br>(V <sub>IN</sub> = V <sub>CC</sub> or Gnd)                               | -10 | 10  | μΑ    |

| lpp             | $V_{PP}$ Supply Current During<br>Programming Pulse ( $\overline{CE} = \overline{PGM} = V_{IL}$ ) |     | 60  | mA    |

| I <sub>cc</sub> | V <sub>CC</sub> Supply Current                                                                    |     | 30  | mA    |

| V <sub>OL</sub> | Output Low Voltage During Verify (I <sub>OL</sub> = 16 mA)                                        |     | 0.4 | V     |

| Voн             | Output High Voltage During Verify $(I_{OH} = -4 \text{ mA})$                                      | 2.4 |     | V     |

- NOTE:

9. V<sub>CC</sub> must be applied either coincidentally or before V<sub>PP</sub> and removed either coincidentally or after V<sub>PP</sub>.

10. V<sub>PP</sub> must not be greater than 13 volts including overshoot. During  $\overline{CE} = \overline{PGM} = V_{IL}$ , V<sub>PP</sub> must not be switched from 5 volts to 12.5 volts or vice-versa.

- 11. During power up the  $\overline{PGM}$  pin must be brought high ( $\geq V_{IH}$ ) either coincident with or before power is applied to  $V_{PP}$ .

# **AC CHARACTERISTICS** $(T_A = 25 \pm 5^{\circ}C, V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}, V_{PP} = 12.75 \pm 0.25 \text{ V})$

| SYMBOLS          | PARAMETER                          | MIN | TYP | MAX | UNITS |

|------------------|------------------------------------|-----|-----|-----|-------|

| t <sub>AS</sub>  | Address Setup Time                 | 2   |     |     | μs    |

| t <sub>CES</sub> | Chip Enable Setup Time             | 2   |     |     | μs    |

| t <sub>OES</sub> | Output Enable Setup Time           | 2   |     |     | μs    |

| tos              | Data Setup Time                    | 2   |     |     | μs    |

| t <sub>AH</sub>  | Address Hold Time                  | 0   |     |     | μs    |

| t <sub>OH</sub>  | Data Hold Time                     | 2   |     |     | μs    |

| t <sub>DF</sub>  | Chip Disable to Output Float Delay | 0   |     | 130 | ns    |

| t <sub>OE</sub>  | Data Valid From Output Enable      |     |     | 130 | ns    |

| t <sub>VS</sub>  | V <sub>PP</sub> Setup Time         | 2   |     |     | μs    |

| t <sub>PW</sub>  | PGM Pulse Width                    | 100 |     | 200 | μs    |

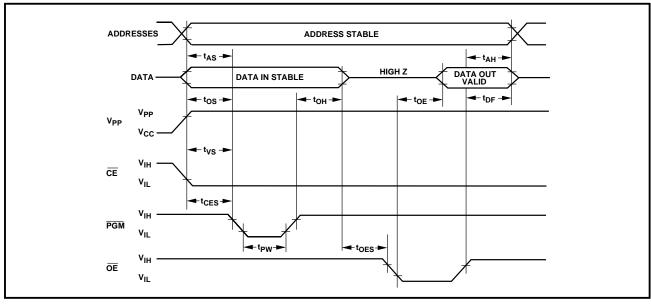

### PROGRAMMING WAVEFORM

## **ORDERING INFORMATION**

| PART NUMBER      | SPEED<br>(ns) | PACKAGE<br>TYPE     | PACKAGE<br>DRAWING | OPERATING<br>TEMPERATURE<br>RANGE | WSI<br>MANUFACTURING<br>PROCEDURE |

|------------------|---------------|---------------------|--------------------|-----------------------------------|-----------------------------------|

| WS57C128FB-35D   | 35            | 28 Pin CERDIP, 0.6" | D2                 | Comm'l                            | Standard                          |

| WS57C128FB-45D   | 45            | 28 Pin CERDIP, 0.6" | D2                 | Comm'l                            | Standard                          |

| WS57C128FB-45DMB | 45            | 28 Pin CERDIP, 0.6" | D2                 | Military                          | MIL-STD-883C                      |

| WS57C128FB-45J   | 45            | 32 Pin PLDCC        | J4                 | Comm'l                            | Standard                          |

| WS57C128FB-45L   | 45            | 32 Pin CLDCC        | L3                 | Comm'l                            | Standard                          |

| WS57C128FB-55CMB | 55            | 32 Pad CLLCC        | C2                 | Military                          | MIL-STD-883C                      |

| WS57C128FB-55D   | 55            | 28 Pin CERDIP, 0.6" | D2                 | Comm'l                            | Standard                          |

| WS57C128FB-55DMB | 55            | 28 Pin CERDIP, 0.6" | D2                 | Military                          | MIL-STD-883C                      |

| WS57C128FB-70D   | 70            | 28 Pin CERDIP, 0.6" | D2                 | Comm'l                            | Standard                          |

| WS57C128FB-70DM  | 70            | 28 Pin CERDIP, 0.6" | D2                 | Military                          | Standard                          |

| WS57C128FB-70DMB | 70            | 28 Pin CERDIP, 0.6" | D2                 | Military                          | MIL-STD-883C                      |

NOTE: 12. The actual part marking will not include the initials "WS."

# PROGRAMMING/ALGORITHMS/ERASURE/PROGRAMMERS

REFER TO PAGE 5-1

The WS57C128FB is programmed using Algorithm D shown on page 5-9.