# 512Mb B-die DDR2 SDRAM Specification Version 0.91

September 2003

### **Contents**

### 1. Key Feature

## 2. Package Pinout/Mechnical Dimension & Addressing

- 2.1 Package Pintout & Mechnical Dimension

- 2.2 Input/Output Function Description

- 2.3 Addressing

### 3. Command Truth Table

- 3.1 Command truth table

- 3.2 Clock Enable (CKE) Truth Table for Synchronous Transitions

- 3.3 DM Truth Table

### 4. Absolute Maximum Rating

# 5. AC & DC Operating Conditions & Specifications

### 512Mb B-die DDR2 SDRAM

# **Revision History**

### Version 0.9 (Aug. 2003)

- Initial Release

### Version 0.91 (Sep. 2003)

- Corrected from M to B in Part No Information(K4T51##3Q"M"-### -> K4T51##3Q"B"-###)

- Removed D4 speed bin(400 4-4-4)

- Added operation temperature condition

Changed setup/hold time values(tlS/tDS, tlH/tDH)

- Added notes for setup/hold time(tIS/tDS, tIH/tDH)

- Changed in/output capacitance values

- Added tREFI values by  $\rm T_{CASE}~(85^{\circ}C/95^{\circ}C)$

### **Part Number Information**

| Organization | DDR2-667 5-5-5  | DDR2-533 4-4-4  | DDR2-400 3-3-3  |

|--------------|-----------------|-----------------|-----------------|

| 128Mx4       | K4T51043QB-GCE6 | K4T51043QB-GCD5 | K4T51043QB-GCCC |

| 12010134     | K4T51043QB-GLE6 | K4T51043QB-GLD5 | K4T51043QB-GLCC |

| 64Mx8        | K4T51083QB-GCE6 | K4T51083QB-GCD5 | K4T51083QB-GCCC |

| 04101X0      | K4T51083QB-GLE6 | K4T51083QB-GLD5 | K4T51083QB-GLCC |

| 32Mx16       | K4T51163QB-GCE6 | K4T51163QB-GCD5 | K4T51163QB-GCCC |

| 32IVIX 16    | K4T51163QB-GLE6 | K4T51163QB-GLD5 | K4T51163QB-GLCC |

#### Note:

<sup>1.</sup> Speed bin is in order of CL-tRCD-tRP

- 1. SAMSUNG Memory: K

- 2. DRAM: 4

- 3. Small Classification

T: DDR2 SDRAM

### 4. Density & Refresh

51:512M 8K/64ms

### 5. Organization

04 : x4 08 : x8 16 : x16

### 6. Bank

3:4 Bank

### 7. Interface (VDD & VDDQ)

Q: SSTL-18(1.8V, 1.8V)

### 8. Version

M: 1st Generation

A: 2nd Generation

B: 3rd Generation

C: 4th Generation

D: 5th Generation

E: 6th Generation

### 9. Package

G:BGA

### 10. Temperature & Power

C: (Commercial, Normal)

L: (Commercial, Low)

### 11. Speed

CC: DDR2-400 3-3-3 D5: DDR2-533 4-4-4 E6: DDR2-667 5-5-5

### 1.Key Features

| Speed       | <b>DDR2-667</b><br>5 - 5- 5 | DDR2-533<br>4 - 4 - 4 | DDR2-400<br>3- 3- 3 | Units |

|-------------|-----------------------------|-----------------------|---------------------|-------|

| CAS Latency | 5                           | 4                     | 3                   | tCK   |

| tRCD(min)   | 15                          | 15                    | 15                  | ns    |

| tRP(min)    | 15                          | 15                    | 15                  | ns    |

| tRC(min)    | 55                          | 55                    | 55                  | ns    |

- JEDEC standard 1.8V ± 0.1V Power Supply

- $VDDQ = 1.8V \pm 0.1V$

- 200 MHz  $f_{CK}$  for 400Mb/sec/pin, 267MHz  $f_{CK}$  for 533Mb/sec/pin, 333MHz  $f_{CK}$  for 667Mb/sec/pin

- 4 Bank

- Posted CAS

- Programmable CAS Latency: 3, 4, 5

- Programmable Additive Latency: 0, 1, 2, 3 and 4

- Write Latency(WL) = Read Latency(RL) -1

- Burst Length: 4, 8(Interleave/nibble sequential)

- Programmable Sequential / Interleave Burst Mode

- Bi-directional Differential Data-Strobe (Single-ended data-strobe is an optional feature)

- Off-Chip Driver(OCD) Impedance Adjustment

- · On Die Termination

- Average Refesh Period 7.8us at lower then  $T_{CASE}$  85°C, 3.9us at 85°C <  $T_{CASE} \le 95$  °C

- Package: 60ball FBGA 128Mx4/64Mx8 , 84ball FBGA 32Mx16

### Description

The 512Mb DDR2 SDRAM chip is organized as either 32Mbit x 4 I/O x 4 banks or 16Mbit x 8 I/O x 4banks or 8Mbit x 16I/O x 4 banks device. This synchronous device achieve high speed double-data-rate transfer rates of up to 667Mb/sec/pin (DDR2-667) for general applications.

The chip is designed to comply with the following key DDR2 SDRAM features: (1) posted CAS with additive latency, (2) write latency = read latency -1, (3) Off-Chip Driver(OCD) impedance adjustment, (4) On Die Termination.

All of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the cross point of differential clocks (CK rising and  $\overline{CK}$  falling). All I/Os are synchronized with a pair of bidirectional strobes (DQS and  $\overline{DQS}$ ) in a source synchronous fashion. A fourteen bit address bus is used to convey row, column, and bank address information in a  $\overline{RAS/CAS}$  multiplexing style. For example, 512Mb(x4) device receive 14/11/2 addressing.

The 512Mb DDR2 devices operate with a single 1.8V  $\pm$  0.1V power supply and 1.8V  $\pm$  0.1V VDDQ.

The 512Mb DDR2 devices are available in 60ball FBGAs(x4/8) and in 84ball FBGAs(x16).

**Note:** The functionality described and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.

## 2. Package Pinout/Mechnical Dimension & Addressing

### 2.1 Package Pinout

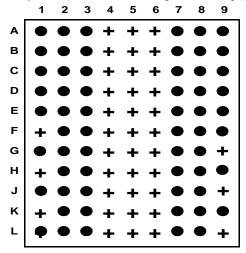

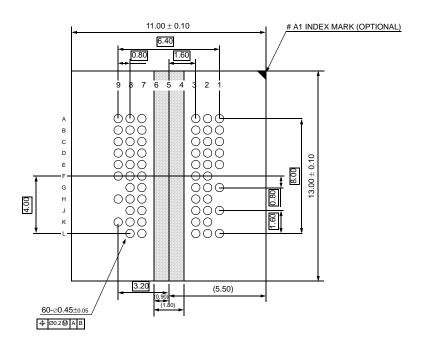

### x4 package pinout (Top View): 60ball FBGA Package

| 1    | 2    | 3    |   | 7 8   | 9    |      |

|------|------|------|---|-------|------|------|

| VDD  | NC   | VSS  | Α | VSSQ  | DQS  | VDDQ |

| NC   | VSSQ | DM   | В | DQS   | VSSQ | NC   |

| VDDQ | DQ1  | VDDQ | С | VDDQ  | DQ0  | VDDQ |

| NC   | VSSQ | DQ3  | D | DQ2   | VSSQ | NC   |

| VDDL | VREF | VSS  | E | VSSDL | CK   | VDD  |

|      | CKE  | WE   | F | RAS   | CK   | ODT  |

| NC   | BA0  | BA1  | G | CAS   | CS   |      |

|      | A10  | A1   | н | A2    | A0   | VDD  |

| VSS  | А3   | A5   | J | A6    | A4   |      |

|      | A7   | A9   | ĸ | A11   | A8   | VSS  |

| VDD  | A12  | NC   | L | NC    | A13  |      |

#### Notes:

B1, B9, D1, D9 = NC for x4 organization.

Pins B3 has identical capacitance as pins B7.

VDDL and VSSDL are power and ground for the DLL. It is recommended that they are isolated on the device from VDD, VDDQ, VSS, and VSSQ.

### **Ball Locations (x4)**

• : Populated Ball

+ : Depopulated Ball

Top View (See the balls through the Package)

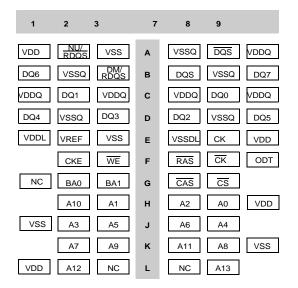

### x8 package pinout (Top View): 60ball FBGA Package

#### Notes:

- 1. Pins B3 and A2 have identical capacitance as pins B7 and A8.

- For a read, when enabled, strobe pair RDQS & RDQS are identical in function and timing to strobe pair DQS & DQS and input masking function is disabled.

- 3. The function of DM or RDQS/RDQS are enabled by EMRS command.

- VDDL and VSSDL are power and ground for the DLL. It is recommended that they are isolated on the device from VDD, VDDQ, VSS, and VSSQ.

### **Ball Locations (x8)**

: Populated Ball

+ : Depopulated Ball

Top View (See the balls through the Package)

1 2 3 4 5 6 7 8 9

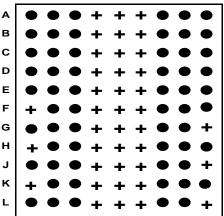

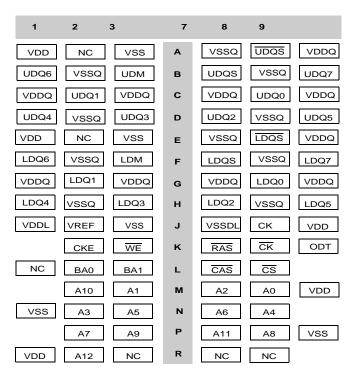

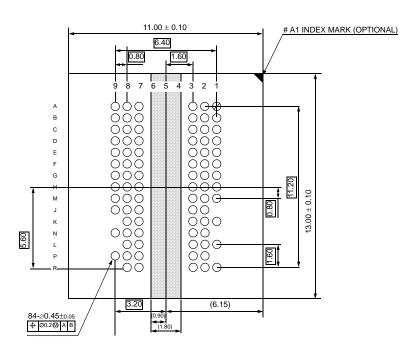

### x16 package pinout (Top View): 84ball FBGA Package

### Notes:

VDDL and VSSDL are power and ground for the DLL. It is recommended that they are isolated on the device from VDD, VDDQ, VSS, and VSSQ.

### **Ball Locations (x16)**

: Populated Ball+ : Depopulated Ball

### **Top View**

(See the balls through the Package)

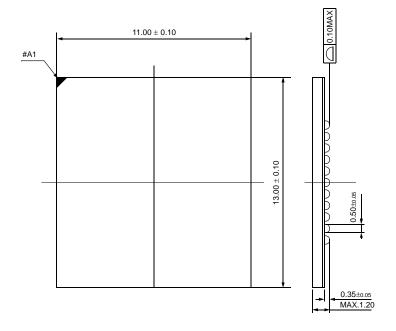

### FBGA Package Dimension(x4/x8)

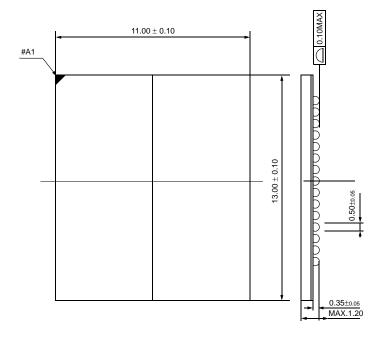

### FBGA Package Dimension(x16)

### 2.2 Input/Output Functional Description

| Symbol                                                           | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK                                                           | Input        | Clock: CK and CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK. Output (read) data is referenced to the crossings of CK and CK (both directions of crossing).                                                                                                                                                                                                                                                                                                                                                                      |

| CKE                                                              | Input        | Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power-Down and Self Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and exit, and for self refresh entry. CKE is asynchronous for self refresh exit. CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK, ODT and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during self refresh.                            |

| <u>cs</u>                                                        | Input        | Chip Select: All commands are masked when $\overline{\mathbb{CS}}$ is registered HIGH. $\overline{\mathbb{CS}}$ provides for external Rank selection on systems with multiple Ranks. $\overline{\mathbb{CS}}$ is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                    |

| ODT                                                              | Input        | On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When enabled, ODT is only applied to each DQ, DQS, DQS, RDQS, RDQS, and DM signal for x4x8 configurations. For x16 configuration ODT is applied to each DQ, UDQS/UDQS, LDQS/LDQS, UDM, and LDM signal. The ODT pin will be ignored if the Extended Mode Register (EMRS) is programmed to disable ODT.                                                                                                                                                                                                                               |

| RAS, CAS, WE                                                     | Input        | Command Inputs: RAS, CAS and WE (along with CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DM                                                               | Input        | <b>Input Data Mask:</b> DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For x8 device, the function of DM or RDQS/RDQS is enabled by EMRS command.                                                                                                                                                                                                                                                                    |

| BA0 - BA1                                                        | Input        | Bank Address Inputs: BA0 and BA1 for 256 and 512Mb, BA0 - BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS or EMRS cycle.                                                                                                                                                                                                                                                                                                                                                               |

| A0 - A13                                                         | Input        | Address Inputs: Provided the row address for Active commands and the column address and Auto Precharge bit for Read/Write commands to select one location out of the memory array in the respective bank. A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op-code during Mode Register Set commands.                                                                                                                                     |

| DQ                                                               | Input/Output | Data Input/ Output: Bi-directional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQS, (DQS)<br>(LDQS), (LDQS)<br>(UDQS), (UDQS)<br>(RDQS), (RDQS) | Input/Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For the x16, LDQS corresponds to the data on DQ0-DQ7; UDQS corresponds to the data on DQ8-DQ15. For the x8, an RDQS option using DM pin can be enabled via the EMRS(1) to simplify read timing. The data strobes DQS, LDQS, UDQS, and RDQS may be used in single ended mode or paired with optional complementary signals DQS, LDQS, UDQS, and RDQS to provide differential pair signaling to the system during both reads and writes. An EMRS(1) control bit enables or disables all complementary data strobe signals. |

| NC                                                               |              | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $V_{DDQ}$                                                        | Supply       | DQ Power Supply: 1.8V +/- 0.1V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SSQ</sub>                                                 | Supply       | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>DDL</sub>                                                 | Supply       | DLL Power Supply: 1.8V +/- 0.1V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SSDL</sub>                                                | Supply       | DLL Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub>                                                  | Supply       | Power Supply: 1.8V +/- 0.1V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub>                                                  | Supply       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>REF</sub>                                                 | Supply       | Reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

In this data sheet, "differential DQS signals" refers to any of the following with A10 = 0 of EMRS(1)

x4 DQS/DQS

x8 DQS/DQS

x8 DQS/DQS, if EMRS(1)[A11] = 0

x8 DQS/DQS, BDQS/RDQS, if EMRS(1)[A11] = 1

x16 LDQS/LDQS and UDQS/UDQS

"single-ended DQS signals" refers to any of the following with A10 = 1 of EMRS(1)

x4 DQS

x8 DQS if EMRS(1) [A11] = 0

x8 DQS, RDQS, if EMRS(1) [A11] = 1

x16 LDQS and UDQS

### 2.3 512Mb Addressing

| Configuration  | 128Mb x4            | 64Mb x 8            | 32Mb x16            |

|----------------|---------------------|---------------------|---------------------|

| # of Bank      | 4                   | 4                   | 4                   |

| Bank Address   | BA0,BA1             | BA0,BA1             | BA0,BA1             |

| Auto precharge | A <sub>10</sub> /AP | A <sub>10</sub> /AP | A <sub>10</sub> /AP |

| Row Address    | A0 ~ A13            | A0 ~ A13            | A0 ~ A12            |

| Column Address | A0 ~ A9,A11         | Ao ~ A9             | Ao ~ A9             |

<sup>\*</sup> Reference information: The following tables are address mapping information for other densities.

### 256Mb

| Configuration  | 64Mb x4             | 32Mb x 8            | 16Mb x16            |

|----------------|---------------------|---------------------|---------------------|

| # of Bank      | 4                   | 4                   | 4                   |

| Bank Address   | BA0,BA1             | BA0,BA1             | BA0,BA1             |

| Auto precharge | A <sub>10</sub> /AP | A <sub>10</sub> /AP | A <sub>10</sub> /AP |

| Row Address    | A0 ~ A12            | A0 ~ A12            | A0 ~ A12            |

| Column Address | A0 ~ A9,A11         | Ao ~ A9             | Ao ~ As             |

### 1Gb

| Configuration  | 256Mb x4            | 128Mb x 8           | 64Mb x16            |

|----------------|---------------------|---------------------|---------------------|

| # of Bank      | 8                   | 8                   | 8                   |

| Bank Address   | BA0 ~ BA2           | BA0 ~ BA2           | BA0 ~ BA2           |

| Auto precharge | A <sub>10</sub> /AP | A <sub>10</sub> /AP | A <sub>10</sub> /AP |

| Row Address    | A0 ~ A13            | A0 ~ A13            | A0 ~ A12            |

| Column Address | A0 ~ A9,A11         | A0 ~ A9             | A0 ~ A9             |

### 2Gb

| Configuration  | 512Mb x4            | 256Mb x 8           | 128Mb x16           |

|----------------|---------------------|---------------------|---------------------|

| # of Bank      | 8                   | 8                   | 8                   |

| Bank Address   | BA0 ~ BA2           | BA0 ~ BA2           | BA0 ~ BA2           |

| Auto precharge | A <sub>10</sub> /AP | A <sub>10</sub> /AP | A <sub>10</sub> /AP |

| Row Address    | A0 ~ A14            | A0 ~ A14            | A0 ~ A13            |

| Column Address | A0 ~ A9,A11         | Ao ~ A9             | Ao ~ A9             |

### 4Gb

| Configuration            | 1 Gb x4             | 512Mb x 8           | 256Mb x16           |

|--------------------------|---------------------|---------------------|---------------------|

| # of Bank                | 8                   | 8                   | 8                   |

| Bank Address             | BA0 ~ BA2           | BA0 ~ BA2           | BA0 ~ BA2           |

| Auto precharge           | A <sub>10</sub> /AP | A <sub>10</sub> /AP | A <sub>10</sub> /AP |

| Row Address              | tbd                 | tbd                 | tbd                 |

| Column Address/page size | tbd                 | tbd                 | tbd                 |

### 3. Command Truth Table.

### 3.1 Command truth table.

|                              | Cł                | KE               |    |     | CAS |    |            |               | BA0   |         |        |  |  |

|------------------------------|-------------------|------------------|----|-----|-----|----|------------|---------------|-------|---------|--------|--|--|

| Function                     | Previous<br>Cycle | Current<br>Cycle | CS | RAS |     | WE | BA1<br>BA2 | A15-A11       | A10   | A9 - A0 | Notes  |  |  |

| (Extended) Mode Register Set | Н                 | Н                | L  | L   | L   | L  | ВА         | C             | P Cod | de      | 1,2    |  |  |

| Refresh (REF)                | Н                 | H                | L  | L   | L   | Н  | Х          | Х             | Х     | Х       | 1      |  |  |

| Self Refresh Entry           | Н                 | L                | L  | L   | L   | Н  | Х          | Х             | Х     | Х       | 1      |  |  |

| Oalf Dafaaala Erit           |                   |                  | Н  | Х   | Х   | Х  | ×          | V             | V     | v       | 4.7    |  |  |

| Self Refresh Exit            | L                 | Н                | L  | Н   | Н   | Н  | X          | Х             | Х     | Х       | 1,7    |  |  |

| Single Bank Precharge        | Н                 | Н                | L  | L   | Н   | L  | ВА         | Х             | L     | Х       | 1,2    |  |  |

| Precharge all Banks          | Н                 | Н                | L  | L   | Н   | L  | Х          | Х             | Н     | Х       | 1      |  |  |

| Bank Activate                | Н                 | Н                | L  | L   | Н   | Н  | ВА         | Row Address 1 |       | 1,2     |        |  |  |

| Write                        | Н                 | Н                | L  | Н   | L   | L  | ВА         | Column        | L     | Column  | 1,2,3, |  |  |

| Write with Auto Precharge    | Н                 | H                | L  | Н   | L   | L  | ВА         | Column        | Н     | Column  | 1,2,3, |  |  |

| Read                         | Н                 | Н                | L  | Н   | L   | Н  | ВА         | Column        | L     | Column  | 1,2,3  |  |  |

| Read with Auto-Precharge     | Н                 | Н                | L  | Н   | L   | Н  | ВА         | Column        | Н     | Column  | 1,2,3  |  |  |

| No Operation                 | Н                 | Х                | L  | Н   | Н   | Н  | Х          | Х             | Х     | Х       | 1      |  |  |

| Device Deselect              | Н                 | Х                | Н  | Х   | Х   | Х  | Х          | Х             | Х     | Х       | 1      |  |  |

| Dawar Dawa Entry             |                   |                  | Н  | Х   | Х   | Х  | V V        | Х             | V     | V       | 4.4    |  |  |

| Power Down Entry             | Н                 | L                | L  | Н   | Н   | Н  | Х          | X             | Х     | Х       | 1,4    |  |  |

| 2 5 5 %                      |                   |                  | Н  | Х   | Х   | Х  |            | V             |       | .,      |        |  |  |

| Power Down Exit              | L                 | Н                | L  | Н   | Н   | Н  | Х          | Х             | Х     | Х       | 1,4    |  |  |

- 1. All DDR2 SDRAM commands are defined by states of  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$  ,  $\overline{\text{WE}}$  and CKE at the rising edge of the clock.

- 2. Bank addresses BA0, BA1, BA2 (BA) determine which bank is to be operated upon. For (E)MRS BA selects an (Extended) Mode Register.

- 3. Burst reads or writes at BL=4 cannot be terminated or interrupted. See sections "Reads interrupted by a Read" and "Writes interrupted by a Write" in section 2.2.4 for details.

- 4. The Power Down Mode does not perform any refresh operations. The duration of Power Down is therefore limited by the refresh requirements outlined in section 2.2.7.

- 5. The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh. See section 2.2.2.4.

- 6. "X" means "H or L (but a defined logic level)".

- 7. Self refresh exit is asynchronous.

### 3.2 Clock Enable (CKE) Truth Table for Synchronous Transitions

|                            | Cł                                   | (E                                | Command (N) <sup>3</sup> |                            |                |

|----------------------------|--------------------------------------|-----------------------------------|--------------------------|----------------------------|----------------|

| Current State <sup>2</sup> | Previous Cycle <sup>1</sup><br>(N-1) | Current Cycle <sup>1</sup><br>(N) | RAS, CAS, WE, CS         | Action (N) <sup>3</sup>    | Notes          |

| Power Down                 | L                                    | L                                 | х                        | Maintain Power-Down        | 11, 13, 15     |

| 1 ower bown                | L                                    | Н                                 | DESELECT or NOP          | Power Down Exit            | 4, 8, 11,13    |

| Self Refresh               | L                                    | L                                 | Х                        | Maintain Self Refresh      | 11, 15         |

| Sell Kellesii              | L                                    | Н                                 | DESELECT or NOP          | Self Refresh Exit          | 4, 5,9         |

| Bank(s) Active             | Н                                    | L                                 | DESELECT or NOP          | Active Power Down Entry    | 4,8,10,11,13   |

| All Banks Idle             | Н                                    | L                                 | DESELECT or NOP          | Precharge Power Down Entry | 4, 8, 10,11,13 |

| All Dallks lule            | Н                                    | L                                 | REFRESH                  | Self Refresh Entry         | 6, 9, 11,13    |

|                            | Н                                    | Н                                 | Refer to the Co          | 7                          |                |

#### Notes

- 1. CKE (N) is the logic state of CKE at clock edge N; CKE (N-1) was the state of CKE at the previous clock edge.

- 2. Current state is the state of the DDR SDRAM immediately prior to clock edge N.

- 3. COMMAND (N) is the command registered at clock edge N, and ACTION (N) is a result of COMMAND (N).

- 4. All states and sequences not shown are illegal or reserved unless explicitly described elsewhere in this document.

- On Self Refresh Exit DESELECT or NOP commands must be issued on every clock edge occurring during the t<sub>XSNR</sub> period.

Read commands may be issued only after t<sub>XSRD</sub> (200 clocks) is satisfied.

- 6. Self Refresh mode can only be entered from the All Banks Idle state.

- 7. Must be a legal command as defined in the Command Truth Table.

- 8. Valid commands for Power Down Entry and Exit are NOP and DESELECT only.

- 9. Valid commands for Self Refresh Exit are NOP and DESELECT only.

- 10. Power Down and Self Refresh can not be entered while Read or Write operations, (Extended) Mode Register Set operations or Precharge operations are in progress. See section 2.2.9 "Power Down" and 3.2.8 "Self Refresh Command" for a detailed list of restrictions.

- 11. Minimum CKE high time is three clocks.; minimum CKE low time is three clocks.

- 12. The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh. See section 2.2.2.4.

- 13. The Power Down does not perform any refresh operations. The duration of Power Down Mode is therefore limited by the refresh requirements outlined in section 2.2.7.

- 14.  $\stackrel{\cdot}{\mathsf{CKE}}$  must be maintained high while the SDRAM is in OCD calibration mode .

- 15. "X" means "don't care (including floating around VREF)" in Self Refresh and Power Down. However ODT must be driven high or low in Power Down if the ODT function is enabled (Bit A2 or A6 set to "1" in EMRS(1)).

### 3.3 DM Truth Table

| Name (Functional)                                                        | DM | DQs   | Note |  |  |  |

|--------------------------------------------------------------------------|----|-------|------|--|--|--|

| Write enable                                                             | -  | Valid | 1    |  |  |  |

| Write inhibit H X 1                                                      |    |       |      |  |  |  |

| Used to mask write data, provided coincident with the corresponding data |    |       |      |  |  |  |

### 4. Absolute Maximum DC Ratings

| Symbol                            | Parameter                           | Rating          | Units | Notes |

|-----------------------------------|-------------------------------------|-----------------|-------|-------|

| VDD                               | Voltage on VDD pin relative to Vss  | - 1.0 V ~ 2.3 V | V     | 1     |

| VDDQ                              | Voltage on VDDQ pin relative to Vss | - 0.5 V ~ 2.3 V | V     | 1     |

| VDDL                              | Voltage on VDDL pin relative to Vss | - 0.5 V ~ 2.3 V | V     | 1     |

| V <sub>IN,</sub> V <sub>OUT</sub> | Voltage on any pin relative to Vss  | - 0.5 V ~ 2.3 V | V     | 1     |

| $T_{\mathtt{STG}}$                | Storage Temperature                 | -55 to +100     | °C    | 1     |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# 5. AC & DC Operating Conditions Recommended DC Operating Conditions (SSTL - 1.8)

| Symbol | Danasatas                 | Rating    |           |           | 11.5  |       |

|--------|---------------------------|-----------|-----------|-----------|-------|-------|

|        | Parameter                 | Min.      | Тур.      | Max.      | Units | Notes |

| VDD    | Supply Voltage            | 1.7       | 1.8       | 1.9       | V     |       |

| VDDL   | Supply Voltage for DLL    | 1.7       | 1.8       | 1.9       | V     | 4     |

| VDDQ   | Supply Voltage for Output | 1.7       | 1.8       | 1.9       | V     | 4     |

| VREF   | Input Reference Voltage   | 0.49*VDDQ | 0.50*VDDQ | 0.51*VDDQ | mV    | 1.2   |

| VTT    | Termination Voltage       | VREF-0.04 | VREF      | VREF+0.04 | V     | 3     |

There is no specific device VDD supply voltage requirement for SSTL-1.8 compliance. However under all conditions VDDQ must be less than or equal to VDD.

<sup>2.</sup> Storage Temperature is the case surface temperature on the center/top side of the DRAM.

<sup>1.</sup> The value of VREF may be selected by the user to provide optimum noise margin in the system. Typically the value of VREF is expected to be about 0.5 x VDDQ of the transmitting device and VREF is expected to track variations in VDDQ.

<sup>2.</sup> Peak to peak ac noise on VREF may not exceed +/-2% VREF (dc).

<sup>3.</sup> VTT of transmitting device must track VREF of receiving device.

<sup>4.</sup> VDDQ tracks with VDD, VDDL tracks with VDD. AC parameters are measured with VDD, VDDQ and VDDDL tied together.

### **Operating Temperature Condition**

| SYMBOL | PARAMETER             | RATING  | UNITS | NOTES |

|--------|-----------------------|---------|-------|-------|

| TOPER  | Operating Temperature | 0 to 95 | °C    | 1, 2  |

#### Note:

- 1. Operating Temperature is the case surface temperature on the center/top side of the DRAM.

- 2. The operation temperature range are the temperature where all DRAM specification will be supported.

### Input DC Logic Level

| Symbol               | Parameter           | Min.         | Max.         | Units | Notes |

|----------------------|---------------------|--------------|--------------|-------|-------|

| V <sub>IH</sub> (dc) | dc input logic high | VREF + 0.125 | VDDQ + 0.3   | ٧     |       |

| V <sub>IL</sub> (dc) | dc input logic low  | - 0.3        | VREF - 0.125 | V     |       |

### Input AC Logic Level

| Symbol               | Parameter           | Min.         | Max.         | Units | Notes |

|----------------------|---------------------|--------------|--------------|-------|-------|

| V <sub>IH</sub> (ac) | ac input logic high | VREF + 0.250 | -            | V     |       |

| V <sub>⊩</sub> (ac)  | ac input logic low  | =            | VREF - 0.250 | V     |       |

### **AC Input Test Conditions**

| Symbol                  | Condition                               | Value                  | Units | Notes |

|-------------------------|-----------------------------------------|------------------------|-------|-------|

| $V_{REF}$               | Input reference voltage                 | 0.5 * V <sub>DDQ</sub> | V     | 1     |

| V <sub>SWING(MAX)</sub> | Input signal maximum peak to peak swing | 1.0                    | V     | 1     |

| SLEW                    | Input signal minimum slew rate          | 1.0                    | V/ns  | 2, 3  |

#### Note

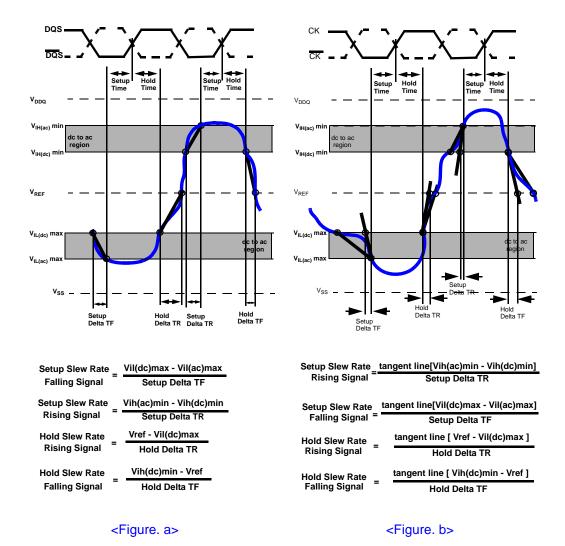

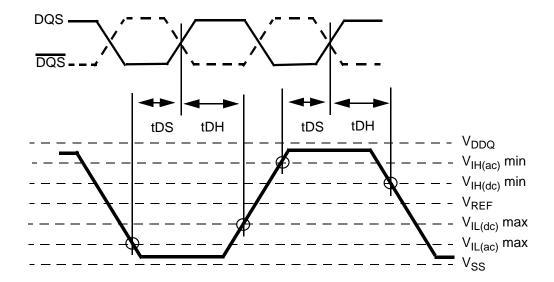

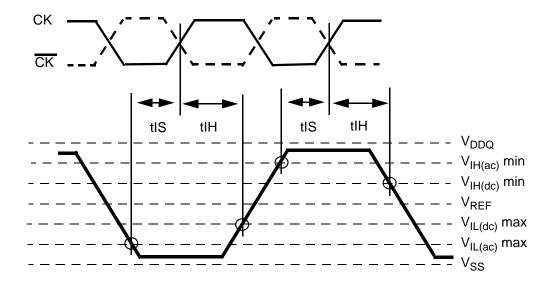

- 1. Setup (tIS & tDS) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of Vih(dc)min. Setup (tIS & tDS) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of Vil(dc)max and the first crossing of Vil(ac)max. If the actual signal is always earlier than the nominal slew rate line between shaded 'dc to ac region', use nominal slew rate for derating value (see Fig a.) If the actual signal is later than the nominal slew rate line anywhere between shaded 'dc to ac region', the slew rate of a tangent line to the actual signal from the ac level to dc level is used for derating value (see Fig b.)

- 2. Hold (tIH & tDH) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of Vil(dc)max and the first crossing of Vref. Hold (tIH & tDH) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of Vih(dc)min and the first crossing of Vref. If the actual signal is always later than the nominal slew rate line between shaded 'dc to Vref region', use nominal slew rate for derating value (see Fig a.) If the actual signal is earlier than the nominal slew rate line anywhere between shaded 'dc to Vref region', the slew rate of a tangent line to the actual signal from the dc level to Vref level is used for derating value (see Fig b.)Input waveform timing is referenced to the input signal crossing through the V<sub>REF</sub> level applied to the device under test.

### Differential input AC logic Level

| Symbol               | Parameter                           | Min.               | Max.               | Units | Notes |

|----------------------|-------------------------------------|--------------------|--------------------|-------|-------|

| V <sub>ID</sub> (ac) | ac differential input voltage       | 0.5                | VDDQ + 0.6         | V     | 1     |

| V <sub>IX</sub> (ac) | ac differential cross point voltage | 0.5 * VDDQ - 0.175 | 0.5 * VDDQ + 0.175 | V     | 2     |

- 1. VIN(DC) specifies the allowable DC execution of each input of differential pair such as CK,  $\overline{CK}$ , DQS,  $\overline{DQS}$ , LDQS,  $\overline{LDQS}$ , UDQS and  $\overline{UDQS}$ .

- 2. VID(DC) specifies the input differential voltage |VTR -VCP | required for switching, where VTR is the true input (such as CK, DQS, LDQS or UDQS) level and VCP is the complementary input (such as CK, DQS, LDQS or UDQS) level. The minimum value is equal to VIH(DC) VIL(DC).

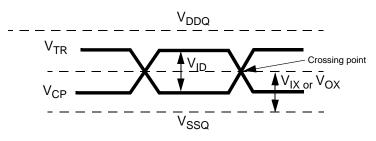

< Differential signal levels >

### Notes:

- 1. VID(AC) specifies the input differential voltage |VTR -VCP | required for switching, where VTR is the true input signal (such as CK, DQS, LDQS or UDQS) and VCP is the complementary input signal (such as  $\overline{CK}$ ,  $\overline{DQS}$ ,  $\overline{LDQS}$  or  $\overline{UDQS}$ ). The minimum value is equal to V IH(AC) V IL(AC).

- 2. The typical value of Vix(AC) is expected to be about 0.5 \* VDDQ of the transmitting device and Vix(AC) is expected to track variations in VDDQ . Vix(AC) indicates the voltage at which differential input signals must cross.

### Differential AC output parameters

|   | Symbol               | Parameter                           | Min.               | Max.               | Units | Notes |

|---|----------------------|-------------------------------------|--------------------|--------------------|-------|-------|

| ĺ | V <sub>OX</sub> (ac) | ac differential cross point voltage | 0.5 * VDDQ - 0.125 | 0.5 * VDDQ + 0.125 | V     | 1     |

#### Notes

1. The typical value of Vox(AC) is expected to be about 0.5 \* V DDQ of the transmitting device and Vox(AC) is expected to track variations in VDDQ . Vox(AC) indicates the voltage at whitch differential output signals must cross.

# Input Signal Overshoot/Undershoot Specification

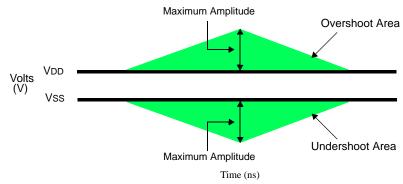

# $\underline{\text{AC Overs}}$ hoot/Undershoot Specification for Address and Control Pins A0-A15, BA0-BA2, $\overline{\text{CS}}$ , $\overline{\text{RAS}}$ , CAS, WE, CKE, ODT

| Parameter                                                          | Specification |           |           |

|--------------------------------------------------------------------|---------------|-----------|-----------|

|                                                                    | DDR2-400      | DDR2-533  | DDR2-667  |

| Maximum peak amplitude allowed for overshoot area (See Figure 1):  | 0.9V          | 0.9V      | 0.9V      |

| Maximum peak amplitude allowed for undershoot area (See Figure 1): | 0.9V          | 0.9V      | 0.9V      |

| Maximum overshoot area above VDD (See Figure1).                    | 0.75 V-ns     | 0.56 V-ns | 0.45 V-ns |

| Maximum undershoot area below VSS (See Figure 1).                  | 0.75 V-ns     | 0.56 V-ns | 0.45 V-ns |

AC Overshoot and Undershoot Definition for Address and Control Pins

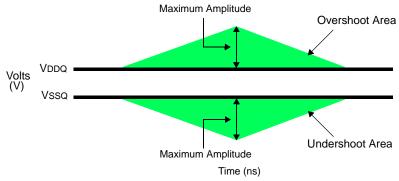

# AC Overshoot/Undershoot Specification for Clock, Data, Strobe, and Mask Pins DQ, DQS, DM, CK, CK

| Parameter                                                          | Specification |           |           |  |

|--------------------------------------------------------------------|---------------|-----------|-----------|--|

|                                                                    | DDR2-400      | DDR2-533  | DDR2-667  |  |

| Maximum peak amplitude allowed for overshoot area (See Figure 2):  | 0.9V          | 0.9V      | 0.9V      |  |

| Maximum peak amplitude allowed for undershoot area (See Figure 2): | 0.9V          | 0.9V      | 0.9V      |  |

| Maximum overshoot area above VDDQ (See Figure 2).                  | 0.38 V-ns     | 0.28 V-ns | 0.23 V-ns |  |

| Maximum undershoot area below VSSQ (See Figure 2).                 | 0.38 V-ns     | 0.28 V-ns | 0.23 V-ns |  |

AC Overshoot and Undershoot Definition for Clock, Data, Strobe, and Mask Pins

Power and ground clamps are implemented on the following input only pins:

- 1. BA0-BA2

- 2. A0-A15

- 3. RAS

- 4. <u>CAS</u> 5. <u>WE</u>

- 6. CS

- 7. ODT

- 8. CKE

### V-I Characteristics for input only pins with clamps

| Voltage across | Minimum Power      | Minimum Ground     |  |  |  |  |

|----------------|--------------------|--------------------|--|--|--|--|

| clamp(V)       | Clamp Current (mA) | Clamp Current (mA) |  |  |  |  |

| 0.0            | 0                  | 0                  |  |  |  |  |

| 0.1            | 0                  | 0                  |  |  |  |  |

| 0.2            | 0                  | 0                  |  |  |  |  |

| 0.3            | 0                  | 0                  |  |  |  |  |

| 0.4            | 0                  | 0                  |  |  |  |  |

| 0.5            | 0                  | 0                  |  |  |  |  |

| 0.6            | 0                  | 0                  |  |  |  |  |

| 0.7            | 0                  | 0                  |  |  |  |  |

| 0.8            | 0.1                | 0.1                |  |  |  |  |

| 0.9            | 1.0                | 1.0                |  |  |  |  |

| 1.0            | 2.5                | 2.5                |  |  |  |  |

| 1.1            | 4.7                | 4.7                |  |  |  |  |

| 1.2            | 6.8                | 6.8                |  |  |  |  |

| 1.3            | 9.1                | 9.1                |  |  |  |  |

| 1.4            | 11.0               | 11.0               |  |  |  |  |

| 1.5            | 13.5               | 13.5               |  |  |  |  |

| 1.6            | 16.0               | 16.0               |  |  |  |  |

| 1.7            | 18.2               | 18.2               |  |  |  |  |

| 1.8            | 21.0               | 21.0               |  |  |  |  |

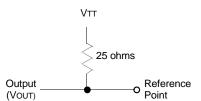

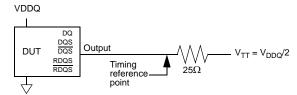

### **Output Buffer Levels**

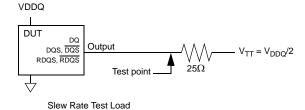

### **Output AC Test Conditions**

| Symbol                                                                            | Parameter                                            | SSTL_18 Class II        | Units | Notes |  |

|-----------------------------------------------------------------------------------|------------------------------------------------------|-------------------------|-------|-------|--|

| V <sub>OH</sub>                                                                   | Minimum Required Output Pull-up under AC Test Load   | V <sub>TT</sub> + 0.603 | V     |       |  |

| V <sub>OL</sub>                                                                   | Maximum Required Output Pull-down under AC Test Load | V <sub>TT</sub> - 0.603 | V     |       |  |

| V <sub>OTR</sub> Output Timing Measurement Reference Level 0.5 * V <sub>DDQ</sub> |                                                      |                         |       | 1     |  |

| The VDDQ of the device under test is referenced.                                  |                                                      |                         |       |       |  |

### **Output DC Current Drive**

| Symbol              | Parameter                        | SSTI_18 Class II | Units | Notes   |

|---------------------|----------------------------------|------------------|-------|---------|

| I <sub>OH(dc)</sub> | Output Minimum Source DC Current | - 13.4           | mA    | 1, 3, 4 |

| I <sub>OL(dc)</sub> | Output Minimum Sink DC Current   | 13.4             | mA    | 2, 3, 4 |

- V<sub>DDQ</sub> = 1.7 V; V<sub>OUT</sub> = 1420 mV. (V<sub>OUT</sub> V<sub>DDQ</sub>)/I<sub>OH</sub> must be less than 21 ohm for values of V<sub>OUT</sub> between V<sub>DDQ</sub> and V<sub>DDQ</sub> 280 mV.

- 2.  $V_{DDQ} = 1.7 \text{ V}$ ;  $V_{OUT} = 280 \text{ mV}$ .  $V_{OUT}/I_{OL}$  must be less than 21 ohm for values of  $V_{OUT}$  between 0 V and 280 mV.

- 3. The dc value of V<sub>REF</sub> applied to the receiving device is set to V<sub>TT</sub>

- 4. The values of I<sub>OH(dc)</sub> and I<sub>OL(dc)</sub> are based on the conditions given in Notes 1 and 2. They are used to test device drive current capability to ensure V<sub>IH</sub> min plus a noise margin and V<sub>IL</sub> max minus a noise margin are delivered to an SSTL\_18 receiver. The actual current values are derived by shifting the desired driver operating point (see Section 3.3) along a 21 ohm load line to define a convenient driver current for measurement.

### **OCD** default characteristics

| Description                                    | Parameter | Min  | Nom | Max  | Unit | Notes |

|------------------------------------------------|-----------|------|-----|------|------|-------|

| Output impedance                               |           | 12.6 | 18  | 23.4 | ohms | 1,2   |

| Output impedance step size for OCD calibration |           | 0    |     | 1.5  | ohms | 6     |

| Pull-up and pull-down mismatch                 |           | 0    |     | 4    | ohms | 1,2,3 |

| Output slew rate                               |           | tbd  |     | tbd  | V/ns | 1,4,5 |

- Note 1: Absolute Specifications (0°C ≤ T<sub>CASE</sub> ≤ +tbd°C; VDD = +1.8V ±0.1V, VDDQ = +1.8V ±0.1V)

- Note 2: Impedance measurement condition for output source dc current: VDDQ = 1.7V; VOUT = 1420mV; (VOUT-VDDQ)/loh must be less than 23.4 ohms for values of VOUT between VDDQ and VDDQ-280mV. Impedance measurement condition for output sink dc current: VDDQ = 1.7V; VOUT = 280mV; VOUT/lol must be less than 23.4 ohms for values of VOUT between 0V and 280mV.

- Note 3: Mismatch is absolute value between pull-up and pull-dn, both are measured at same temperature and voltage.

- Note 4: Slew rate measured from vil(ac) to vih(ac).

- Note 5: The absolute value of the slew rate as measured from DC to DC is equal to or greater than the slew rate as measured from AC to AC. This is guaranteed by design and characterization.

Note 6: This represents the step size when the OCD is near 18 ohms at nominal conditions across all process and represents only the DRAM uncertainty. A 0 ohm value (no calibration) can only be achieved if the OCD impedance is 18 ohms +/- 0.75 ohms under nominal conditions.

Output slew rate load:

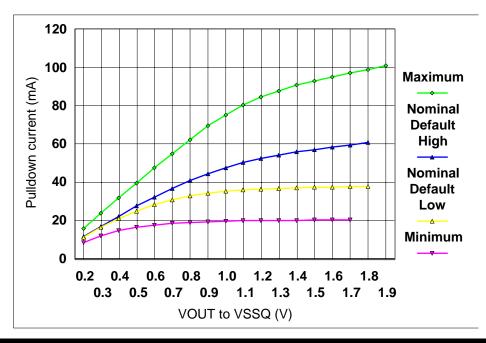

Table 1. Full Strength Default Pulldown Driver Characteristics

|             | Pullo              | Pulldown Current (mA)            |                                   |                     |  |  |  |  |  |

|-------------|--------------------|----------------------------------|-----------------------------------|---------------------|--|--|--|--|--|

| Voltage (V) | Minimum (23.4 Ohms | Nominal Default<br>Low (18 ohms) | Nominal Default<br>High (18 ohms) | Maximum (12.6 Ohms) |  |  |  |  |  |

| 0.2         | 8.5                | 11.3                             | 11.8                              | 15.9                |  |  |  |  |  |

| 0.3         | 12.1               | 16.5                             | 16.8                              | 23.8                |  |  |  |  |  |

| 0.4         | 14.7               | 21.2                             | 22.1                              | 31.8                |  |  |  |  |  |

| 0.5         | 16.4               | 25.0                             | 27.6                              | 39.7                |  |  |  |  |  |

| 0.6         | 17.8               | 28.3                             | 32.4                              | 47.7                |  |  |  |  |  |

| 0.7         | 18.6               | 30.9                             | 36.9                              | 55.0                |  |  |  |  |  |

| 0.8         | 19.0               | 33.0                             | 40.9                              | 62.3                |  |  |  |  |  |

| 0.9         | 19.3               | 34.5                             | 44.6                              | 69.4                |  |  |  |  |  |

| 1.0         | 19.7               | 35.5                             | 47.7                              | 75.3                |  |  |  |  |  |

| 1.1         | 19.9               | 36.1                             | 50.4                              | 80.5                |  |  |  |  |  |

| 1.2         | 20.0               | 36.6                             | 52.6                              | 84.6                |  |  |  |  |  |

| 1.3         | 20.1               | 36.9                             | 54.2                              | 87.7                |  |  |  |  |  |

| 1.4         | 20.2               | 37.1                             | 55.9                              | 90.8                |  |  |  |  |  |

| 1.5         | 20.3               | 37.4                             | 57.1                              | 92.9                |  |  |  |  |  |

| 1.6         | 20.4               | 37.6                             | 58.4                              | 94.9                |  |  |  |  |  |

| 1.7         | 20.6               | 37.7                             | 59.6                              | 97.0                |  |  |  |  |  |

| 1.8         |                    | 37.9                             | 60.9                              | 99.1                |  |  |  |  |  |

| 1.9         |                    |                                  |                                   | 101.1               |  |  |  |  |  |

Figure 1. DDR2 Default Pulldown Characteristics for Full Strength Driver

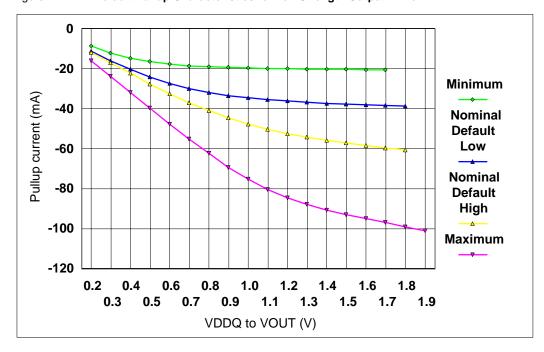

Table 2. Full Strength Default Pullup Driver Characteristics

|             |                    | Pullup Current (mA)              |                                   |                     |  |  |  |  |  |  |

|-------------|--------------------|----------------------------------|-----------------------------------|---------------------|--|--|--|--|--|--|

| Voltage (V) | Minimum (23.4 Ohms | Nominal Default<br>Low (18 ohms) | Nominal Default<br>High (18 ohms) | Maximum (12.6 Ohms) |  |  |  |  |  |  |

| 0.2         | -8.5               | -11.1                            | -11.8                             | -15.9               |  |  |  |  |  |  |

| 0.3         | -12.1              | -16.0                            | -17.0                             | -23.8               |  |  |  |  |  |  |

| 0.4         | -14.7              | -20.3                            | -22.2                             | -31.8               |  |  |  |  |  |  |

| 0.5         | -16.4              | -24.0                            | -27.5                             | -39.7               |  |  |  |  |  |  |

| 0.6         | -17.8              | -27.2                            | -32.4                             | -47.7               |  |  |  |  |  |  |

| 0.7         | -18.6              | -29.8                            | -36.9                             | -55.0               |  |  |  |  |  |  |

| 0.8         | -19.0              | -31.9                            | -40.8                             | -62.3               |  |  |  |  |  |  |

| 0.9         | -19.3              | -33.4                            | -44.5                             | -69.4               |  |  |  |  |  |  |

| 1.0         | -19.7              | -34.6                            | -47.7                             | -75.3               |  |  |  |  |  |  |

| 1.1         | -19.9              | -35.5                            | -50.4                             | -80.5               |  |  |  |  |  |  |

| 1.2         | -20.0              | -36.2                            | -52.5                             | -84.6               |  |  |  |  |  |  |

| 1.3         | -20.1              | -36.8                            | -54.2                             | -87.7               |  |  |  |  |  |  |

| 1.4         | -20.2              | -37.2                            | -55.9                             | -90.8               |  |  |  |  |  |  |

| 1.5         | -20.3              | -37.7                            | -57.1                             | -92.9               |  |  |  |  |  |  |

| 1.6         | -20.4              | -38.0                            | -58.4                             | -94.9               |  |  |  |  |  |  |

| 1.7         | -20.6              | -38.4                            | -59.6                             | -97.0               |  |  |  |  |  |  |

| 1.8         |                    | -38.6                            | -60.8                             | -99.1               |  |  |  |  |  |  |

| 1.9         |                    |                                  |                                   | -101.1              |  |  |  |  |  |  |

Figure 2. DDR2 Default Pullup Characteristics for Full Strength Output Driver

### DDR2 SDRAM Default Output Driver V-I Characteristics

DDR2 SDRAM output driver characteristics are defined for full strength default operation as selected by the EMRS1 bits A7-A9 = '111'. Figures 1 and 2 show the driver characteristics graphically, and tables 1 and 2 show the same data in tabular format suitable for input into simulation tools. The driver characteristics evaluation conditions are:

Nominal Default 25 °C (T case), VDDQ = 1.8 V, typical process Minimum TBD °C (T case), VDDQ = 1.7 V, slow–slow process Maximum 0 °C (T case), VDDQ = 1.9 V, fast–fast process

### **Default Output Driver Characteristic Curves Notes:**

- 1) The full variation in driver current from minimum to maximum process, temperature, and voltage will lie within the outer bounding lines of the V–I curve of figures 1 and 2.

- 2) It is recommended that the "typical" IBIS V-I curve lie within the inner bounding lines of the V-I curves of figures 1 and 2.

|             | Calibrated Pulldow n Current (mA) |                             |                   |                                |                              |  |  |  |  |  |

|-------------|-----------------------------------|-----------------------------|-------------------|--------------------------------|------------------------------|--|--|--|--|--|

| Voltage (V) | Nominal Minimum<br>(21 ohms)      | Nominal Low (18.75<br>ohms) | Nominal (18 ohms) | Nominal High (17.25 t<br>ohms) | lominal Maximum (15<br>ohms) |  |  |  |  |  |

| 0.2         | 9.5                               | 10.7                        | 11.5              | 11.8                           | 13.3                         |  |  |  |  |  |

| 0.3         | 14.3                              | 16.0                        | 16.6              | 17.4                           | 20.0                         |  |  |  |  |  |

| 0.4         | 18.7                              | 21.0                        | 21.6              | 23.0                           | 27.0                         |  |  |  |  |  |

Table 3. Full Strength Calibrated Pulldown Driver Characteristics

Table 4. Full Strength Calibrated Pullup Driver Characteristics

|   |             | Calibrated Pullup Current (mA) |                             |                   |                              |                              |  |  |  |  |  |

|---|-------------|--------------------------------|-----------------------------|-------------------|------------------------------|------------------------------|--|--|--|--|--|

|   | Voltage (V) | Nominal Minimum<br>(21 ohms)   | Nominal Low (18.75<br>ohms) | Nominal (18 ohms) | Nominal High (17.25<br>ohms) | lominal Maximum (15<br>ohms) |  |  |  |  |  |

| Ì | 0.2         | -9.5                           | -10.7                       | -11.4             | -11.8                        | -13.3                        |  |  |  |  |  |

| Ī | 0.3         | -14.3                          | -16.0                       | -16.5             | -17.4                        | -20.0                        |  |  |  |  |  |

| Į | 0.4         | -18.7                          | -21.0                       | -21.2             | -23.0                        | -27.0                        |  |  |  |  |  |

### DDR2 SDRAM Calibrated Output Driver V-I Characteristics

DDR2 SDRAM output driver characteristics are defined for full strength calibrated operation as selected by the procedure outlined in section 2.2.2.3, Off-Chip Driver (OCD) Impedance Adjustment. Tables 3 and 4 show the data in tabular format suitable for input into simulation tools. The nominal points represent a device at exactly 18 ohms. The nominal low and nominal high values represent the range that can be achieved with a maximum 1.5 ohm step size with no calibration error at the exact nominal conditions only (i.e. perfect calibration procedure, 1.5 ohm maximum step size guaranteed by specification). Real system calibration error needs to be added to these values. It must be understood that these V-I curves as represented here or in supplier IBIS models need to be adjusted to a wider range as a result of any system calibration error. Since this is a system specific phenomena, it cannot be quantified here. The values in the calibrated tables represent just the DRAM portion of uncertainty while looking at one DQ only. If the cali

### 512Mb B-die DDR2 SDRAM

bration procedure is used, it is possible to cause the device to operate outside the bounds of the default device characteristics tables and figures. In such a situation, the timing parameters in the specification cannot be guaranteed. It is solely up to the system application to ensure that the device is calibrated between the minimum and maximum default values at all times. If this can't be guaranteed by the system calibration procedure, re-calibration policy, and uncertainty with DQ to DQ variation, then it is recommended that only the default values be used. The nominal maximum and minimum values represent the change in impedance from nominal low and high as a result of voltage and temperature change from the nominal condition to the maximum and minimum conditions. If calibrated at an extreme condition, the amount of variation could be as much as from the nominal minimum to the nominal maximum or vice versa. The driver characteristics evaluation conditions are:

Nominal 25 °C (T case), VDDQ = 1.8 V, typical process Nominal Low and Nominal High 25 °C (T case), VDDQ = 1.8 V, any process Nominal Minimum TBD °C (T case), VDDQ = 1.7 V, any process Nominal Maximum 0 °C (T case), VDDQ = 1.9 V, any process

# **IDD Specification Parameters and Test Conditions**

(IDD values are for full operating range of Voltage and Temperature, Notes 1 - 5)

| Sym-<br>bol | Proposed Conditions                                                                                                                                                                                                                                                                  |                                   | DDR2-<br>667<br>(CL=5) | DDR2-<br>533<br>(CL=4) | DDR2-<br>400<br>(CL=3) | Units | Notes |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------|------------------------|------------------------|-------|-------|

| IDD0        | Operating one bank active-precharge c  tCK = tCK(IDD), tRC = tRC(IDD), tRAS =  CKE is HIGH, CS\ is HIGH between valid  Address bus inputs are SWITCHING;  Data bus inputs are SWITCHING                                                                                              | tRASmin(IDD);                     | TBD                    | TBD                    | TBD                    | mA    |       |

| IDD1        | Operating one bank active-read-precharge current; IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRC = tRC (IDD), tRAS = tRASmin(IDD), tRCD = tRCD(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data pattern is same as IDD4W |                                   |                        | TBD                    | TBD                    | mA    |       |

| IDD2P       | Precharge power-down current; All banks idle; tCK = tCK(IDD); CKE is LOW; Other control and address bus inputs are STABLE; Data bus inputs are FLOATING                                                                                                                              |                                   |                        | TBD                    | TBD                    | mA    |       |

| IDD2Q       | Precharge quiet standby current; All banks idle;  tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are STABLE; Data bus inputs are FLOATING                                                                                                            |                                   |                        | TBD                    | TBD                    | mA    |       |

| IDD2N       | Precharge standby current; All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING                                                                                                               |                                   |                        | TBD                    | TBD                    | mA    |       |

| IDD3P       | Active power-down current; All banks open; tCK = tCK(IDD); CKE is LOW; Other control and address bus inputs are                                                                                                                                                                      | Fast PDN<br>Exit MRS(12)<br>= 0mA | TBD                    | TBD                    | TBD                    | mA    |       |

|             | Other control and address bus inputs are STABLE; Data bus inputs are FLOATING                                                                                                                                                                                                        | Slow PDN<br>Exit MRS(12)<br>= 1mA | TBD                    | TBD                    | TBD                    | mA    |       |

| IDD3N       | Active standby current; All banks open;  tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING                                                     |                                   | TBD                    | TBD                    | TBD                    | mA    |       |

### 512Mb B-die DDR2 SDRAM

| IDD4W | Operating burst write current; All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data bus inputs are SWITCHING                                                                                                                                                                                    |        |     | TBD | TBD | mA |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|----|--|

| IDD4R | Operating burst read current; All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0;  ¹CK = ¹CK(IDD), ¹RAS = ¹RASmax(IDD), ¹RP = ¹RP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data pattern is same as IDD4W                                                                                                                                                                         |        |     | TBD | TBD | mA |  |

| IDD5B | Burst auto refresh current;  tCK = tCK(IDD);  Refresh command at every tRFC(IDD) interval;  CKE is HIGH, CS\ is HIGH between valid commands;  Other control and address bus inputs are SWITCHING;  Data bus inputs are SWITCHING                                                                                                                                                                                                                               |        | TBD | TBD | TBD | mA |  |

| IDD6  | Self refresh current;<br>CK and CK\ at 0V;<br>CKE ≤ 0.2V;                                                                                                                                                                                                                                                                                                                                                                                                      | Normal | TBD | TBD | TBD | mA |  |

|       | Other control and address bus inputs are FLOATING; Data bus inputs are FLOATING Low Power                                                                                                                                                                                                                                                                                                                                                                      |        | TBD | TBD | TBD | mA |  |

| IDD7  | Operating bank interleave read current; All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = \(^1RCD(IDD) - 1 + ^1CK(IDD);\) \(^1CK = ^1CK(IDD), \(^1RC = ^1RC(IDD), \(^1RRD = ^1RRD(IDD), \) \(^1RCD = 1 + ^1CK(IDD);\) \(^1CKE is HIGH, CS\) is HIGH between valid commands; \(^1Address bus inputs are STABLE during DESELECTs;\) \(^1Data pattern is same as IDD4R;\) \(^1RCD - Refer to the following page for detailed timing conditions) |        | TBD | TBD | TBD | mA |  |

- **Note:**1. IDD specifications are tested after the device is properly initialized

- 2. Input slew rate is specified by AC Parametric Test Condition

- 3. IDD parameters are specified with ODT disabled.

- 4. Data bus consists of DQ, DM, DQS, DQS\, RDQS\, RDQS\, LDQS\, LDQS\, UDQS, and UDQS\. IDD values must be met with all combinations of EMRS bits 10 and 11.

- 5. Definitions for IDD

LOW is defined as Vin ≤ VILAC(max)

HIGH is defined as Vin ≥ VIHAC(min)

STABLE is defined as inputs stable at a HIGH or LOW level FLOATING is defined as inputs at VREF = VDDQ/2

SWITCHING is defined as:

inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and control

inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including masks or strobes.

### For purposes of IDD testing, the following parameters are to be utilized

|                             | DDR2-667 | DDR2-533 | DDR2-400 |       |

|-----------------------------|----------|----------|----------|-------|

| Parameter                   | 5-5-5    | 4-4-4    | 3-3-3    | Units |

| CL(IDD)                     | 5        | 4        | 3        | tCK   |

| tRCD(IDD)                   | 15       | 15       | 15       | ns    |

| tRC(IDD)                    | 55       | 55       | 55       | ns    |

| tRRD(IDD)-x4/x8             | 7.5      | 7.5      | 7.5      | ns    |

| <sup>t</sup> RRD(IDD)-x16   | 10       | 10       | 10       | ns    |

| tCK(IDD)                    | 3        | 3.75     | 5        | ns    |

| <sup>t</sup> RASmin(IDD)    | 40       | 40       | 40       | ns    |

| <sup>t</sup> RP(IDD)        | 15       | 15       | 15       | ns    |

| <sup>t</sup> RFC(IDD)-512Mb | 105      | 105      | 105      | ns    |

#### Detailed IDD7

The detailed timings are shown below for IDD7. Changes will be required if timing parameter changes are made to the specification. Legend: A = Active; RA = Read with Autoprecharge; D = Deselect

### IDD7: Operating Current: All Bank Interleave Read operation

All banks are being interleaved at minimum  ${}^{t}RC(IDD)$  without violating  ${}^{t}RRD(IDD)$  using a burst length of 4. Control and address bus inputs are STABLE during DESELECTs. IOUT = 0mA

### Timing Patterns for 4 bank devices x4/ x8/ x16

-DDR2-400 3/3/3 A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D D D D

-DDR2-533 4/4/4 A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D D D

-DDR2-667 5/5/5 A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D

### Input/Output capacitance

| Parameter                                              | Symbol | DDR2-400<br>DDR2-533 |      | DDR2-667 |      |       |

|--------------------------------------------------------|--------|----------------------|------|----------|------|-------|

|                                                        |        | Min                  | Max  | Min      | Max  | Units |

| Input capacitance, CK and $\overline{\text{CK}}$       | сск    | 1.0                  | 2.0  | 1.0      | 2.0  | pF    |

| Input capacitance delta, CK and $\overline{\text{CK}}$ | CDCK   | х                    | 0.25 | х        | 0.25 | pF    |

| Input capacitance, all other input-only pins           | CI     | 1.0                  | 2.0  | 1.0      | 2.0  | pF    |

| Input capacitance delta, all other input-only pins     | CDI    | х                    | 0.25 | х        | 0.25 | pF    |

| Input/output capacitance, DQ, DM, DQS, DQS             | CIO    | 2.5                  | 4.0  | 2.5      | 3.5  | pF    |

| Input/output capacitance delta, DQ, DM, DQS, DQS       | CDIO   | х                    | 0.5  | х        | 0.5  | pF    |

## Electrical Characteristics & AC Timing for DDR2-667/533/400

$(0~^{\circ}\text{C} \leq \text{T}_{\text{CASE}} \leq 95~^{\circ}\text{C};~\text{V}_{\text{DDQ}} = 1.8\text{V} \pm 0.1\text{V};~\text{V}_{\text{DD}} = 1.8\text{V} \pm 0.1\text{V})$

### **Refresh Parameters by Device Density**

| Parameter                              | Symbol |                                                                          | 256Mb | 512Mb | 1Gb   | 2Gb | 4Gb | Units |

|----------------------------------------|--------|--------------------------------------------------------------------------|-------|-------|-------|-----|-----|-------|

| Refresh to active/Refresh command time | tRFC   |                                                                          | 75    | 105   | 127.5 | 195 | tbd | ns    |

| Average periodic refresh interval      | tREFI  | $0  ^{\circ}\text{C} \le \text{T}_{\text{CASE}} \le 85 ^{\circ}\text{C}$ | 7.8   | 7.8   | 7.8   | 7.8 | 7.8 | μS    |

|                                        |        | 85 °C < T <sub>CASE</sub> ≤ 95°C                                         | 3.9   | 3.9   | 3.9   | 3.9 | 3.9 | μs    |

### Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin

| Speed                 | DDR2-667(E6) |       | DDR2-533(D5) |           | DDR2-400(CC) |           | Units |

|-----------------------|--------------|-------|--------------|-----------|--------------|-----------|-------|

| Bin (CL - tRCD - tRP) | 5 - 5- 5     |       | 4 - 4        | 4 - 4 - 4 |              | 3 - 3 - 3 |       |

| Parameter             | min          | max   | min          | max       | min          | max       |       |

| tCK, CL=3             | 5            | 8     | 5            | 8         | 5            | 8         | ns    |

| tCK, CL=4             | 3.75         | 8     | 3.75         | 8         | 5            | 8         | ns    |

| tCK, CL=5             | 3            | 8     | -            | -         | -            | -         | ns    |

| tRCD                  | 15           |       | 15           |           | 15           |           | ns    |

| tRP                   | 15           |       | 15           |           | 15           |           | ns    |

| tRC                   | 55           |       | 55           |           | 55           |           | ns    |

| tRAS                  | 40           | 70000 | 40           | 70000     | 40           | 70000     | ns    |

### **Timing Parameters by Speed Grade**

(Refer to notes for informations related to this table at the bottom)

| Parameter | Symbol | DDR2-667 |     | DDR2-533 |     | DDR2-400 |     | Units | Notes |

|-----------|--------|----------|-----|----------|-----|----------|-----|-------|-------|

|           |        | min      | max | min      | max | min      | max |       |       |

### 512Mb B-die DDR2 SDRAM

|                                                    | 1      | 1                |              | 1                | ı            | ı                | 1            | 1   |              |