#### **TENTATIVE** TOSHIBA MULTI-CHIP INTEGRATED CIRCUIT SILICON GATE CMOS

# SRAM AND FLASH MEMORY MIXED MULTI-CHIP PACKAGE DESCRIPTION

The TH50VSF3680/3681AASB is a mixed multi-chip package containing a 8,388,608-bit Full CMOS SRAM and a 67.108.864-bit flash memory. The CIOS and CIOF inputs can be used to select the optimal memory configuration. The power supply. FLASH MEMORY a Simultaneous Read/Write operation so that data can be read during a Write or Erase operation. The TH50VSF3680/3681AASB can range from 2.7 V to 3.3 V. The TH50VSF3680/3681AASB is available in a 69-pin BGA package, making it suitable for a variety of design applications.

#### **FEATURES**

Power supply voltage  $V_{CCs} = 2.7 \text{ V} \sim 3.3 \text{ V}$  $V_{CCf} = 2.7 \text{ V} \sim 3.3 \text{ V}$

Data retention supply voltage  $V_{CCs} = 1.5 \text{ V} \sim 3.3 \text{ V}$

Current consumption

Operating: 45 mA maximum (CMOS level) Standby: 10 µA maximum (SRAM CMOS level)

Standby: 10 μA maximum (FLASH) Block erase architecture for flash memory

$8 \times 8$  Kbytes  $63 \times 64$  Kbytes

Organization

| CIOF     | CIOS            | Flash Memory               | SRAM                      |

|----------|-----------------|----------------------------|---------------------------|

| $V_{CC}$ | $V_{CC}$        | 4,194,304 words of 16 bits | 524,288 words of 16 bits  |

| VCC      | V <sub>SS</sub> | 4,194,304 words of 16 bits | 1,048,576 words of 8 bits |

| VSS      | V <sub>SS</sub> | 8,388,608 words of 8 bits  | 1,048,576 words of 8 bits |

- · Function mode control for flash memory Compatible with JEDEC-standard commands

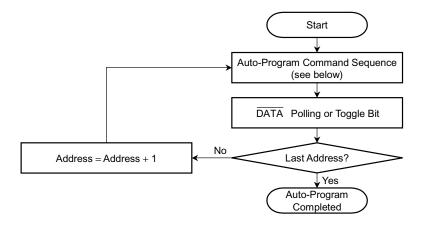

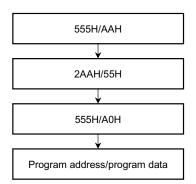

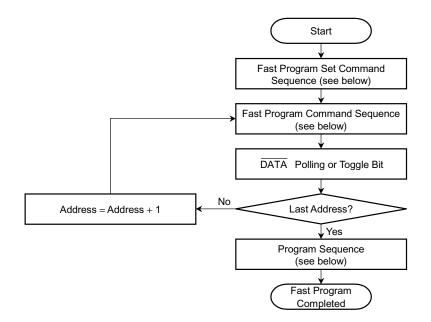

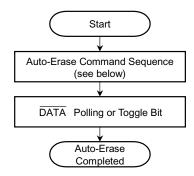

- Flash memory functions Simultaneous Read/Write operations Auto-Program

Auto Chip Erase, Auto Block Erase Auto Multiple-Block Erase Program Suspend/Resume

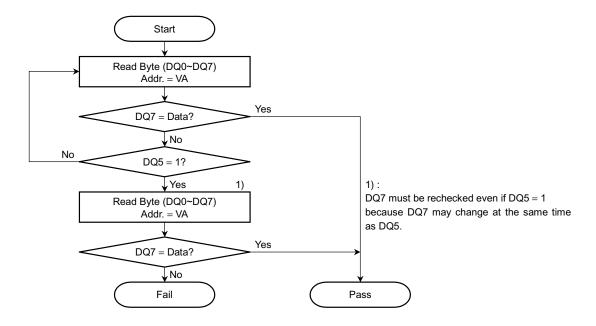

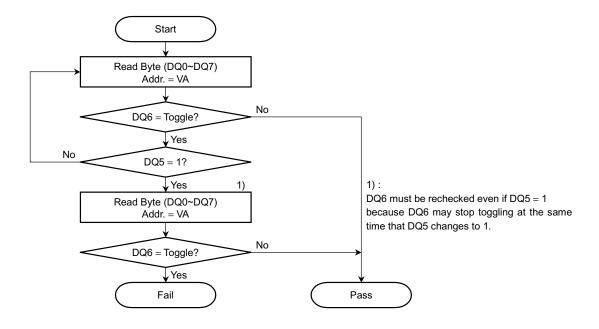

Block-Erase Suspend/Resume Data Polling/Toggle Bit function

Block Protection/Boot Block Protection Automatic Sleep, Hidden ROM Area Supports Common Flash Memory Interface (CFI) Byte/Word Mode

Erase and Program cycle for flash memory 10<sup>5</sup> cycles (typical)

Boot block architecture for flash memory TH50VSF3680AASB: Top boot block TH50VSF3681AASB: Bottom boot block

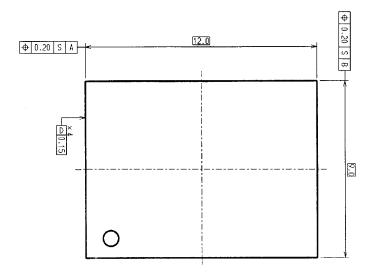

P-FBGA69-1209-0.80A3: 0.31 g (typ.)

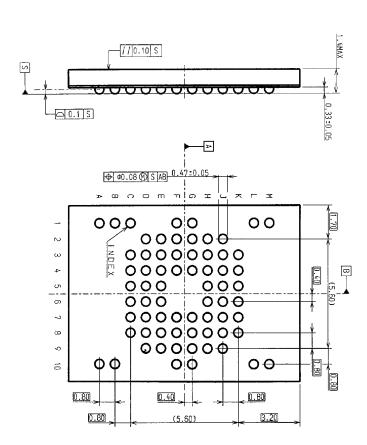

## PIN ASSIGNMENT (TOP VIEW)

Case: CIOF =  $V_{CC}$ , CIOS =  $V_{CC}$  (×16, ×16)

| 1  | 2           | 3               | 4    | 5                                 | 6                | 7    | 8    | 9               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----|-------------|-----------------|------|-----------------------------------|------------------|------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |             |                 |      |                                   |                  |      |      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NC |             |                 |      |                                   |                  |      |      |                 | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NC |             |                 |      |                                   |                  |      |      |                 | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NC |             | A7              | LΒ   | $\overline{\text{WP}}/\text{ACC}$ | WE               | A8   | A11  |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | А3          | A6              | ŪB   | RESET                             | CE2S             | A19  | A12  | A15             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | A2          | A5              | A18  | RY/BY                             | A20              | A9   | A13  | A21             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NC | A1          | A4              | A17  |                                   |                  | A10  | A14  | NC              | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NC | A0          | $V_{\text{SS}}$ | DQ1  |                                   |                  | DQ6  | DU   | A16             | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | CEF         | ŌĒ              | DQ9  | DQ3                               | DQ4              | DQ13 | DQ15 | CIOF            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | CE1S        | DQ0             | DQ10 | $V_{CCf}$                         | $V_{\text{CCs}}$ | DQ12 | DQ7  | $V_{\text{SS}}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |             | DQ8             | DQ2  | DQ11                              | CIOS             | DQ5  | DQ14 |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NC |             |                 |      |                                   |                  |      |      |                 | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NC |             |                 |      |                                   |                  |      |      |                 | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | NC NC NC NC | NC              | NC   | NC                                | NC               | NC   | NC   | NC              | NC         A7         LB         WP/ACC         WE         A8         A11           NC         A3         A6         UB         RESET         CE2S         A19         A12         A15           A2         A5         A18         RY/BY         A20         A9         A13         A21           NC         A1         A4         A17          A10         A14         NC           NC         A0         VSS         DQ1          DQ6         DU         A16           CEF         OE         DQ9         DQ3         DQ4         DQ13         DQ15         CIOF           CEIS         DQ0         DQ10         VCCf         VCCs         DQ12         DQ14         VSS           NC          DQ8         DQ2         DQ11         CIOS         DQ5         DQ14         VSS |

### **PIN NAMES**

| - |                  |                                          |

|---|------------------|------------------------------------------|

|   | A0~A22           | Address Inputs                           |

|   | A12S             | A12 Input for SRAM                       |

|   | A12F             | A12 Input for Flash Memory               |

|   | SA               | A19 Input for SRAM                       |

|   | DQ0~DQ15         | Data Inputs/Outputs                      |

|   | CE1S, CE2S       | Chip Enable Inputs for SRAM              |

|   | CEF              | Chip Enable Input for Flash Memory       |

|   | ŌĒ               | Output Enable Input                      |

|   | WE               | Write Enable Input                       |

|   | LB, UB           | Data Byte Control Input                  |

|   | RY/BY            | Ready/Busy Output                        |

|   | RESET            | Hardware Reset Input                     |

|   | WP/ACC           | Write Protect/Program Acceleration Input |

|   | CIOS             | Word Enable Input for SRAM               |

|   | CIOF             | Word Enable Input for Flash Memory       |

|   | V <sub>CCs</sub> | Power Supply for SRAM                    |

|   | V <sub>CCf</sub> | Power Supply for Flash Memory            |

|   | V <sub>SS</sub>  | Ground                                   |

|   | NC               | Not Connected                            |

|   | DU               | Don't Use                                |

|   |                  |                                          |

• TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are

requipment, office equipment, measuring equipment, industrial robotics, doffiestic applications, etc.). These ToSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

## **PIN ASSIGNMENT (TOP VIEW)**

• Case: CIOF = V<sub>CC</sub>, CIOS = V<sub>SS</sub> (×16, ×8)

|   | 1  | 2    | 3               | 4    | 5      | 6         | 7    | 8    | 9        | 10 |

|---|----|------|-----------------|------|--------|-----------|------|------|----------|----|

|   |    |      |                 |      |        |           |      |      |          |    |

| Α | NC |      |                 |      |        |           |      |      |          | NC |

| В | NC |      |                 |      |        |           |      |      |          | NC |

| С | NC |      | A7              | DU   | WP/ACC | WE        | A8   | A11  |          |    |

| D |    | А3   | A6              | DU   | RESET  | CE2S      | A19  | A12  | A15      |    |

| Е |    | A2   | A5              | A18  | RY/BY  | A20       | A9   | A13  | A21      |    |

| F | NC | A1   | A4              | A17  |        |           | A10  | A14  | NC       | NC |

| G | NC | A0   | $V_{\text{SS}}$ | DQ1  |        |           | DQ6  | SA   | A16      | NC |

| Н |    | CEF  | ŌĒ              | DQ9  | DQ3    | DQ4       | DQ13 | DQ15 | CIOF     |    |

| J |    | CE1S | DQ0             | DQ10 | Vccf   | $V_{CCs}$ | DQ12 | DQ7  | $V_{SS}$ |    |

| K |    |      | DQ8             | DQ2  | DQ11   | CIOS      | DQ5  | DQ14 |          |    |

| L | NC |      |                 |      |        |           |      |      |          | NC |

| М | NC |      |                 |      |        |           |      |      |          | NC |

Case: CIOF =  $V_{SS}$ , CIOS =  $V_{SS}$  (×8, ×8)

|   | 1  | 2    | 3               | 4   | 5                  | 6                | 7   | 8    | 9               | 10 |

|---|----|------|-----------------|-----|--------------------|------------------|-----|------|-----------------|----|

|   |    |      |                 |     |                    |                  |     |      |                 |    |

| Α | NC |      |                 |     |                    |                  |     |      |                 | NC |

| В | NC |      |                 |     |                    |                  |     |      |                 | NC |

| С | NC |      | A7              | DU  | WP/ACC             | WE               | A8  | A11  |                 |    |

| D |    | А3   | A6              | DU  | RESET              | CE2S             | A20 | A13  | A16             |    |

| Е |    | A2   | A5              | A19 | $RY/\overline{BY}$ | A21              | A9  | A14  | A22             |    |

| F | NC | A1   | A4              | A18 |                    |                  | A10 | A15  | NC              | NC |

| G | NC | A0   | $V_{\text{SS}}$ | DQ1 |                    |                  | DQ6 | A12S | A17             | NC |

| Н |    | CEF  | ŌĒ              | DU  | DQ3                | DQ4              | DU  | A12F | CIOF            |    |

| J |    | CE1S | DQ0             | DU  | $V_{CCf}$          | $V_{\text{CCs}}$ | DU  | DQ7  | $V_{\text{SS}}$ |    |

| K |    |      | DU              | DQ2 | DU                 | CIOS             | DQ5 | DU   |                 |    |

| L | NC |      |                 |     |                    |                  |     |      |                 | NC |

| М | NC |      |                 |     |                    |                  |     |      |                 | NC |

Note: A12F and A12S should be wired and used as A12 pin.

000707EBA2

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or other rights. others.

The information contained herein is subject to change without notice.

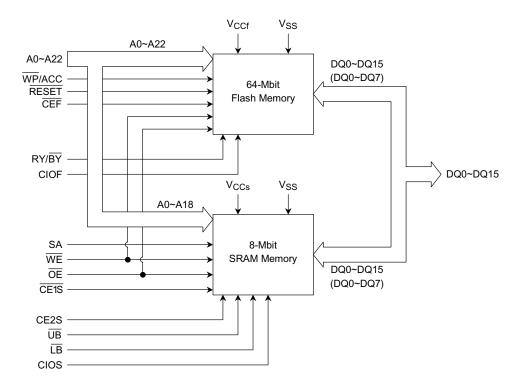

# **BLOCK DIAGRAM**

### **MODE SELECTION**

| OPERATION MODE                    | CEF | CE1S | CE2S | ŌĒ | WE | RESET | ŪB | LΒ | WP/ACC | DQ0~DQ7          | DQ8~DQ15         |

|-----------------------------------|-----|------|------|----|----|-------|----|----|--------|------------------|------------------|

| Flash Read                        | L   | Н    | Х    | L  | Н  | Н     | Х  | Х  | Х      | D <sub>OUT</sub> | D <sub>OUT</sub> |

| i iasii iteau                     | L   | Х    | L    | Ш  | Н  | Н     | Х  | Х  | Х      | D <sub>OUT</sub> | D <sub>OUT</sub> |

|                                   | Н   | L    | Н    | L  | Н  | Н     | L  | L  | Х      | D <sub>OUT</sub> | D <sub>OUT</sub> |

| SRAM Read                         | Н   | L    | Н    | Ы  | Н  | Н     | Н  | L  | Х      | D <sub>OUT</sub> | Hi-Z             |

|                                   | Н   | L    | Н    | L  | Н  | Н     | L  | Н  | Х      | Hi-Z             | D <sub>OUT</sub> |

| Flash Write                       | L   | Н    | Х    | Н  | L  | Н     | Х  | Х  | Х      | D <sub>IN</sub>  | D <sub>IN</sub>  |

| riasii wiile                      | L   | Х    | L    | Н  | L  | Н     | Х  | Х  | Х      | D <sub>IN</sub>  | D <sub>IN</sub>  |

|                                   | Н   | L    | Н    | Χ  | L  | Н     | L  | L  | Х      | D <sub>IN</sub>  | D <sub>IN</sub>  |

| SRAM Write                        | Н   | L    | Н    | Χ  | L  | Н     | Н  | L  | Х      | D <sub>IN</sub>  | Hi-Z             |

|                                   | Н   | L    | Н    | Х  | L  | Н     | L  | Н  | Х      | Hi-Z             | D <sub>IN</sub>  |

| Flash Output Disable              | Х   | Н    | Х    | Н  | Н  | Х     | Х  | Х  | Х      | Hi-Z             | Hi-Z             |

| riasii Output Disable             | Х   | Х    | L    | Н  | Н  | Х     | Х  | Х  | Х      | Hi-Z             | Hi-Z             |

| SRAM Output Disable               | Н   | Х    | Х    | Н  | Н  | Х     | Х  | Х  | Х      | Hi-Z             | Hi-Z             |

| SKAM Output Disable               | Н   | Х    | Х    | Х  | Х  | Х     | Н  | Н  | Х      | Hi-Z             | Hi-Z             |

| Flash Standby                     | Н   | Х    | Х    | Х  | Х  | Н     | Х  | Х  | Х      | S                | S                |

| Flash Hardware<br>Reset / Standby | х   | х    | х    | Х  | Х  | L     | Х  | Х  | х      | S                | S                |

| SRAM Standby                      | Х   | Н    | Х    | Х  | Х  | Х     | Х  | Х  | Х      | F                | F                |

| SKAIVI STAITUDY                   | Х   | Х    | L    | Х  | Х  | Х     | Х  | Х  | Х      | F                | F                |

Notes:  $L = V_{IL}$ ;  $H = V_{IH}$ ;  $X = V_{IH}$  or  $V_{IL}$

F: Depends on flash memory operation mode. S: Depends on SRAM operation mode.

When CIOS =  $V_{CC}$  and CIOF =  $V_{CC}$ , Word Mode is selected for both SRAM and flash memory.

Does not apply when  $\overline{\text{CEF}} = \overline{\text{CE1S}} = \text{V}_{\text{IL}}$  and  $\text{CE2S} = \text{V}_{\text{IH}}$  at the same time.

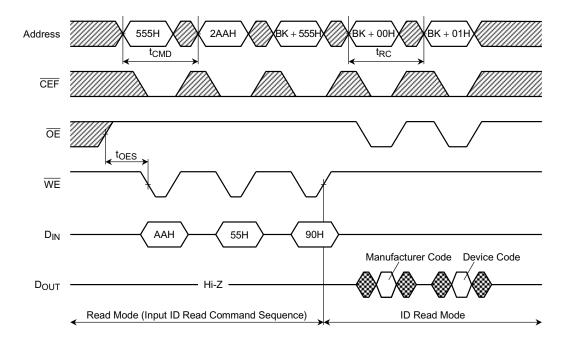

# **ID CODE TABLE**

|                    | TYPE            | A21~A12           | A6 | A1 | A0 | CODE (HEX) <sup>(1)</sup> |

|--------------------|-----------------|-------------------|----|----|----|---------------------------|

| Manufacturer Co    | de              | *                 | L  | L  | L  | 0098H                     |

| Device Code        | TH50VSF3680AASB | *                 | L  | L  | Н  | 0093H                     |

| Device Code        | TH50VSF3681AASB | *                 | L  | L  | Н  | 0095H                     |

| Verify Block Prote | ect             | BA <sup>(2)</sup> | L  | Н  | L  | Data <sup>(3)</sup>       |

Note:  $* = V_{IH}$  or  $V_{IL}$

$L = V_{IL} \quad H = V_{IH}$

(1) DQ8~DQ15 are Hi-Z in Byte mode

(2) BA: Block address(3) 0001H: Protected block0000H: Unprotected block

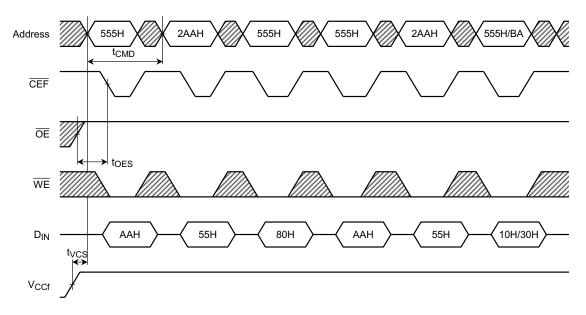

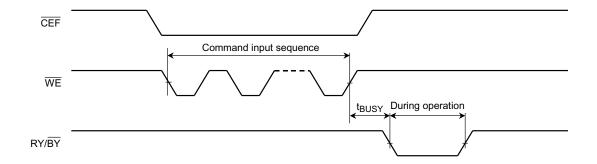

### **COMMAND SEQUENCES**

| COMMAN          |       | BUS<br>WRITE    | FIRST<br>WRITE      |         |                    | ND BUS<br>CYCLE     | THIRD<br>WRITE (            |      |                    | TH BUS<br>CYCLE     |       | BUS<br>CYCLE | SIXTH<br>WRITE    | I BUS<br>CYCLE |

|-----------------|-------|-----------------|---------------------|---------|--------------------|---------------------|-----------------------------|------|--------------------|---------------------|-------|--------------|-------------------|----------------|

| SEQUENC         | Ε     | CYCLES<br>REQ'D | Addr.               | Data    | Addr.              | Data                | Addr.                       | Data | Addr.              | Data                | Addr. | Data         | Addr.             | Data           |

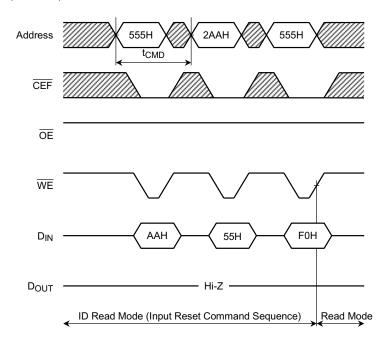

| Read/Reset      |       | 1               | XXXH                | F0H     |                    |                     |                             |      |                    |                     |       |              |                   |                |

| Read/Reset      | Word  | 3               | 555H                | ААН     | 2AAH               | 55H                 | 555H                        | F0H  | RA <sup>(1)</sup>  | RD <sup>(2)</sup>   |       |              |                   |                |

| Reau/Reset      | Byte  | 3               | AAAH                | AAH     | 555H               | 3311                | AAAH                        | FUH  | K                  | ND                  |       |              |                   |                |

| ID Read         | Word  | 3               | 555H                | AAH     | 2AAH               | 55H                 | BK <sup>(3)</sup> +<br>555H | 90H  | IA <sup>(4)</sup>  | ID <sup>(5)</sup>   |       |              |                   |                |

| ID Neau         | Byte  | 3               | AAAH                | AAII    | 555H               | 3311                | BK <sup>(3)</sup> +<br>AAAH | 3011 | ζ.                 | ID.                 |       |              |                   |                |

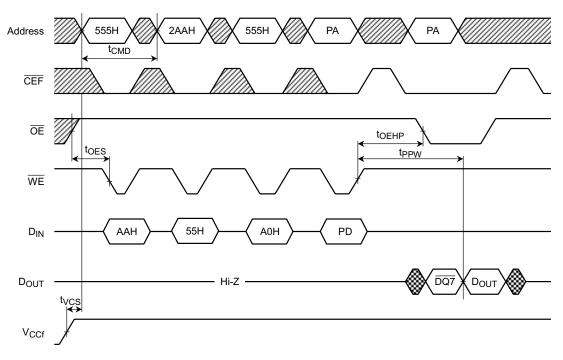

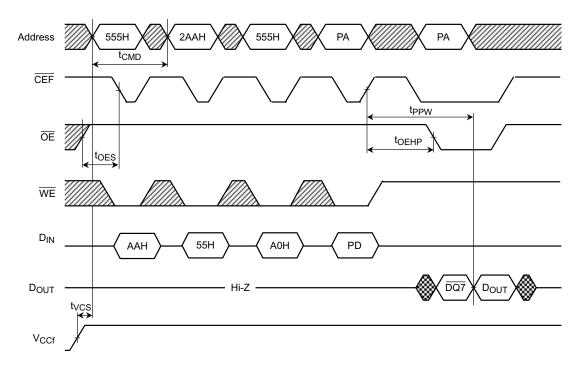

| Auto-Program    | Word  | 4               | 555H                | AAH     | 2AAH               | 55H                 | 555H                        | A0H  | PA <sup>(6)</sup>  | PD <sup>(7)</sup>   |       |              |                   |                |

| Auto-Program    | Byte  | 4               | AAAH                | ААП     | 555H               | חטט                 | AAAH                        | АОП  | PA                 | PU                  |       |              |                   |                |

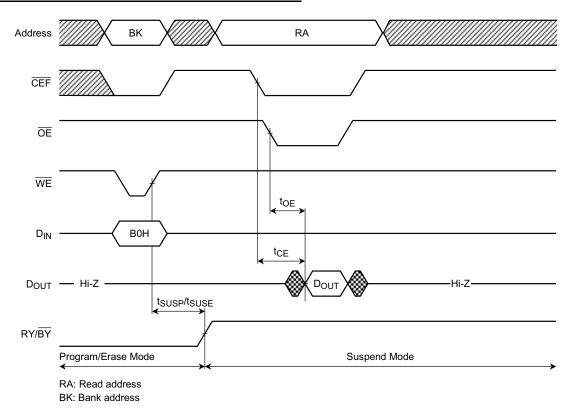

| Program Suspe   | nd    | 1               | вк <sup>(3)</sup>   | ВОН     |                    |                     |                             |      |                    |                     |       |              |                   |                |

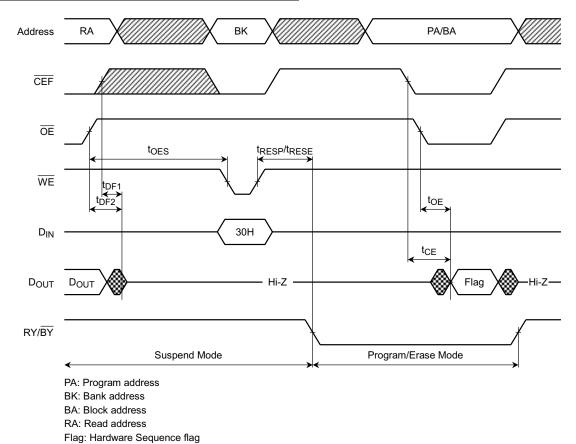

| Program Resum   | ne    | 1               | вк <sup>(3)</sup>   | 30H     |                    |                     |                             |      |                    |                     |       |              |                   |                |

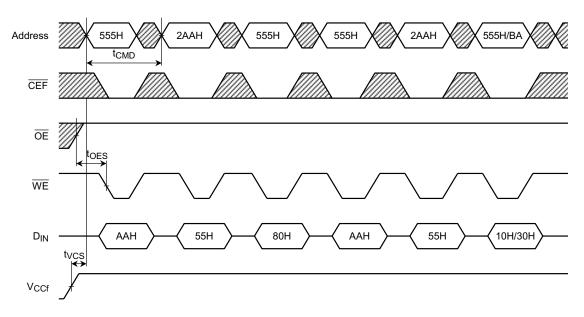

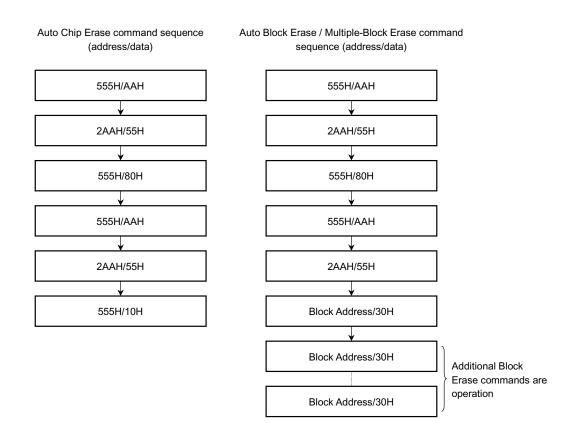

| Auto Chip       | Word  | 6               | 555H                | ААН     | 2AAH               | 55H                 | 555H                        | 80H  | 555H               | AAH                 | 2AAH  | 55H          | 555H              | 10H            |

| Erase           | Byte  | ь               | AAAH                | AAH     | 555H               | 55H                 | AAAH                        | 80H  | AAAH               | AAH                 | 555H  | 55H          | AAAH              | 10H            |

| Auto Block      | Word  | 6               | 555H                | AAH     | 2AAH               | 55H                 | 555H                        | 80H  | 555H               | AAH                 | 2AAH  | 55H          | BA <sup>(8)</sup> | 30H            |

| Erase           | Byte  | О               | AAAH                | ААН     | 555H               | DDH                 | AAAH                        | 8011 | AAAH               | ААН                 | 555H  | ээн          | ВА                | 30H            |

| Block Erase Sus | spend | 1               | вк <sup>(3)</sup>   | вон     |                    |                     |                             |      |                    |                     |       |              |                   |                |

| Block Erase Re  | sume  | 1               | вк <sup>(3)</sup>   | 30H     |                    |                     |                             |      |                    |                     |       |              |                   |                |

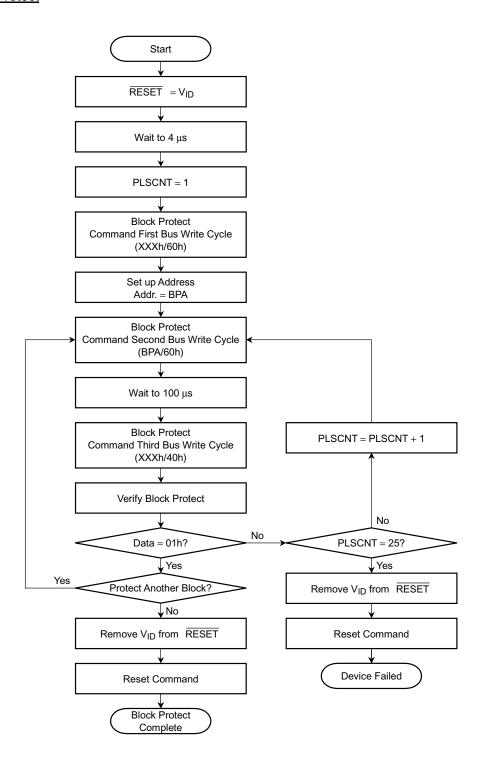

| Block Protect   |       | 4               | XXXH                | 60H     | BPA <sup>(9)</sup> | 60H                 | XXXH                        | 40H  | BPA <sup>(9)</sup> | BPD <sup>(10)</sup> |       |              |                   |                |

| Verify Block    | Word  |                 | 555H                |         | 2AAH               | 5511                | BK <sup>(3)</sup> + 555H    | 0011 | BPA <sup>(9)</sup> | BPD <sup>(10)</sup> |       |              |                   |                |

| Protect         | Byte  | 3               | АААН                | AAH     | 555H               | 55H                 | BK <sup>(3)</sup> +<br>AAAH | 90H  | BPA                | BPD                 |       |              |                   |                |

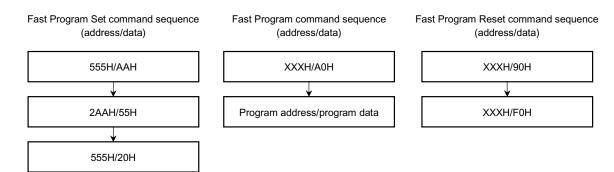

| Fast Program    | Word  | 3               | 555H                | AAH     | 2AAH               | 55H                 | 555H                        | 20H  |                    |                     |       |              |                   |                |

| Set             | Byte  | 3               | AAAH                | AAH     | 555H               |                     | AAAH                        | 20H  |                    |                     |       |              |                   |                |

| Fast Program    |       | 2               | XXXH                | A0H     | PA <sup>(6)</sup>  | PD <sup>(7)</sup>   |                             |      |                    |                     |       |              |                   |                |

| Fast Program R  | eset  | 2               | XXXH                | 90H     | XXXH               | F0H <sup>(13)</sup> |                             |      |                    |                     |       |              |                   |                |

| Hidden ROM      | Word  | 3               | 555H                |         | 2AAH               | 5511                | 555H                        | 0011 |                    |                     |       |              |                   |                |

| Mode Entry      | Byte  | 3               | AAAH                | AAH     | 555H               | 55H                 | AAAH                        | 88H  |                    |                     |       |              |                   |                |

| Hidden ROM      | Word  | 4               | 555H                |         | 2AAH               | 5511                | 555H                        | 4011 | PA <sup>(6)</sup>  | PD <sup>(7)</sup>   |       |              |                   |                |

| Program         | Byte  | 4               | AAAH                | AAH     | 555H               | 55H                 | AAAH                        | A0H  | PA                 | PD                  |       |              |                   |                |

| Hidden ROM      | Word  | 6               | 555H                | AAH     | 2AAH               | 55H                 | 555H                        | 80H  | 555H               | AAH                 | 2AAH  | 55H          | BA <sup>(8)</sup> | 30H            |

| Erase           | Byte  | σ               | AAAH                | AAH     | 555H               | DOFI                | AAAH                        | BUH  | AAAH               | ААП                 | 555H  | DOH          | BA                | 3011           |

| Hidden ROM      | Word  | 4               | 555H                | A A I I | 2AAH               | EE!!                | 555H                        | 0011 | VVVII              | 0011                |       |              |                   |                |

| Mode Exit       | Byte  | 4               | AAAH                | AAH     | 555H               | 55H                 | AAAH                        | 90H  | XXXH               | 00H                 |       |              |                   |                |

|                 | Word  |                 | BK <sup>(3)</sup> + |         |                    |                     |                             |      | _                  |                     |       |              |                   |                |

| Query           | vvoid | 2               | 55H                 | 98H     | CA <sup>(11)</sup> | CD <sup>(12)</sup>  |                             |      |                    |                     |       |              |                   |                |

| Command         | Byte  | _               | BK <sup>(3)</sup> + |         |                    |                     |                             |      |                    |                     |       |              |                   |                |

|                 |       |                 | AAH                 |         |                    |                     |                             |      |                    |                     |       |              |                   |                |

Note: The system should generate the following address patterns: • Byte mode when V<sub>IL</sub> is inputted to CIOF, and addresses Word Mode: 555H or 2AAH to addresses A10~A0

Byte Mode: AAAH or 555H to addresses A10~A0, A12F DQ8~DQ15 are ignored in Word mode.

- (1) RA: Read Address

- (2) RD: Read Data

- (3) BK: Bank Address = A21~A15

- (4) IA: Bank Address and ID Read Address (A6, A1, A0) (9) BPA: Block Address and ID Read Address (A6, A1, A0) Bank Address = A21~A15 Manufacturer Code = (0, 0, 0) Device Code = (0, 0, 1)

- (5) ID: ID Data

- 0098H Manufacturer Code

- 0093H Device Code (TH50VSF3680AASB)

- 0095H Device Code (TH50VSF3681AASB)

- 0001H Protected Block

- are A22~A0

- Write mode when VIH is inputted to CIOF, and addresses are A21~A0

- Valid addresses are A10~A0 when a command is entered.

- (6) PA: Program Address

- (7) PD: Program Data

- (8) BA: Block Address = A21~A12

- Block Address = A21~A12 ID Read Address = (0, 1, 0)

- (10) BPD: Verify Data

- (11) CA: CFI Address

- (12) CD: CFI Data

- (13) F0H: 00H is valid too

# **BLOCK ERASE ADDRESS TABLES**

# (1) TH50VSF3680AASB (top boot block)

|           |            |     |     |      | BLO | OCK A | DDRE | ESS |     |     |     | ADDRES          | S RANGE         |

|-----------|------------|-----|-----|------|-----|-------|------|-----|-----|-----|-----|-----------------|-----------------|

| BANK<br># | BLOCK<br># |     |     | BANK | ADD | RESS  |      |     |     |     |     | ABBREO          | 01011000        |

|           |            | A21 | A20 | A19  | A18 | A17   | A16  | A15 | A14 | A13 | A12 | BYTE MODE       | WORD MODE       |

|           | BA0        | L   | L   | L    | L   | L     | L    | L   | *   | *   | *   | 000000H~00FFFFH | 000000H~007FFFH |

|           | BA1        | L   | L   | L    | L   | L     | L    | Н   | *   | *   | *   | 010000H~01FFFFH | 008000H~00FFFFH |

|           | BA2        | L   | L   | L    | L   | L     | Н    | L   | *   | *   | *   | 020000H~02FFFFH | 010000H~017FFFH |

| BK0       | BA3        | L   | L   | L    | L   | L     | Н    | Н   | *   | *   | *   | 030000H~03FFFFH | 018000H~01FFFFH |

| BKU       | BA4        | L   | L   | L    | L   | Н     | L    | L   | *   | *   | *   | 040000H~04FFFFH | 020000H~027FFFH |

|           | BA5        | L   | L   | L    | L   | Н     | L    | Н   | *   | *   | *   | 050000H~05FFFFH | 028000H~02FFFFH |

|           | BA6        | L   | L   | L    | L   | Н     | Н    | L   | *   | *   | *   | 060000H~06FFFFH | 030000H~037FFFH |

|           | BA7        | L   | L   | L    | L   | Н     | Н    | Н   | *   | *   | *   | 070000H~07FFFFH | 038000H~03FFFFH |

|           | BA8        | L   | L   | L    | Н   | L     | L    | L   | *   | *   | *   | 080000H~08FFFFH | 040000H~047FFFH |

|           | BA9        | L   | L   | L    | Η   | L     | L    | Н   | *   | *   | *   | 090000H~09FFFFH | 048000H~04FFFFH |

|           | BA10       | L   | L   | L    | Н   | L     | Н    | L   | *   | *   | *   | 0A0000H~0AFFFFH | 050000H~057FFFH |

| BK1       | BA11       | L   | L   | L    | Η   | L     | Η    | Н   | *   | *   | *   | 0B0000H~0BFFFFH | 058000H~05FFFFH |

| BKI       | BA12       | L   | L   | Ш    | Ι   | Ι     | L    | L   | *   | *   | *   | 0C0000H~0CFFFFH | 060000H~067FFFH |

|           | BA13       | L   | L   | L    | Η   | Ι     | L    | Н   | *   | *   | *   | 0D0000H~0DFFFFH | 068000H~06FFFFH |

|           | BA14       | L   | L   | Ш    | Ι   | Ι     | Ι    | L   | *   | *   | *   | 0E0000H~0EFFFH  | 070000H~077FFFH |

|           | BA15       | L   | L   | L    | Ι   | Η     | Ι    | Н   | *   | *   | *   | 0F0000H~0FFFFH  | 078000H~07FFFFH |

|           | BA16       | L   | L   | Ι    | Ы   | ┙     | L    | L   | *   | *   | *   | 100000H~10FFFFH | 080000H~087FFFH |

|           | BA17       | L   | L   | Н    | L   | L     | L    | Н   | *   | *   | *   | 110000H~11FFFFH | 088000H~08FFFFH |

|           | BA18       | L   | L   | Н    | L   | L     | Н    | L   | *   | *   | *   | 120000H~12FFFFH | 090000H~097FFFH |

| BK2       | BA19       | L   | L   | Н    | L   | L     | Н    | Н   | *   | *   | *   | 130000H~13FFFFH | 098000H~09FFFFH |

| DIVZ      | BA20       | L   | L   | Н    | L   | Н     | L    | L   | *   | *   | *   | 140000H~14FFFFH | 0A0000H~0A7FFFH |

|           | BA21       | L   | L   | Τ    | L   | Ι     | L    | Н   | *   | *   | *   | 150000H~15FFFFH | 0A8000H~0AFFFFH |

|           | BA22       | L   | L   | Н    | L   | Η     | Н    | L   | *   | *   | *   | 160000H~16FFFFH | 0B0000H~0B7FFFH |

|           | BA23       | L   | L   | Н    | L   | Н     | Н    | Н   | *   | *   | *   | 170000H~17FFFFH | 0B8000H~0BFFFFH |

|           | BA24       | L   | L   | Η    | Η   | L     | L    | L   | *   | *   | *   | 180000H~18FFFFH | 0C0000H~0C7FFFH |

|           | BA25       | L   | L   | Н    | Н   | L     | L    | Н   | *   | *   | *   | 190000H~19FFFFH | 0C8000H~0CFFFFH |

|           | BA26       | L   | L   | Η    | Η   | L     | Η    | L   | *   | *   | *   | 1A0000H~1AFFFFH | 0D0000H~0D7FFFH |

| BK3       | BA27       | L   | L   | Н    | Н   | L     | Н    | Н   | *   | *   | *   | 1B0000H~1BFFFFH | 0D8000H~0DFFFFH |

| DIG       | BA28       | L   | L   | Η    | Η   | Η     | L    | L   | *   | *   | *   | 1C0000H~1CFFFFH | 0E0000H~0E7FFFH |

|           | BA29       | L   | L   | Н    | Н   | Н     | L    | Н   | *   | *   | *   | 1D0000H~1DFFFFH | 0E8000H~0EFFFFH |

|           | BA30       | L   | L   | Η    | Η   | Η     | Η    | L   | *   | *   | *   | 1E0000H~1EFFFFH | 0F0000H~0F7FFFH |

|           | BA31       | L   | L   | Н    | Н   | Н     | Н    | Н   | *   | *   | *   | 1F0000H~1FFFFFH | 0F8000H~0FFFFFH |

| DANK      | DI OOK     |     |     |      | BLO | OCK A | DDRE | ESS | 1   |     |     | ADDRES          | S RANGE         |

|-----------|------------|-----|-----|------|-----|-------|------|-----|-----|-----|-----|-----------------|-----------------|

| BANK<br># | BLOCK<br># |     | ı   | BANK | ADD | RESS  |      | ı   |     |     | ı   |                 |                 |

|           |            | A21 | A20 | A19  | A18 | A17   | A16  | A15 | A14 | A13 | A12 | BYTE MODE       | WORD MODE       |

|           | BA32       | L   | Н   | L    | L   | L     | L    | L   | *   | *   | *   | 200000H~20FFFFH | 100000H~107FFFH |

|           | BA33       | L   | Н   | L    | L   | L     | L    | Н   | *   | *   | *   | 210000H~21FFFFH | 108000H~10FFFFH |

|           | BA34       | L   | Н   | L    | L   | L     | Н    | L   | *   | *   | *   | 220000H~22FFFFH | 110000H~117FFFH |

| BK4       | BA35       | L   | Н   | L    | L   | L     | Н    | Н   | *   | *   | *   | 230000H~23FFFFH | 118000H~11FFFFH |

| Bitt      | BA36       | L   | Н   | L    | L   | Н     | L    | L   | *   | *   | *   | 240000H~24FFFFH | 120000H~127FFFH |

|           | BA37       | L   | Н   | L    | L   | Н     | L    | Н   | *   | *   | *   | 250000H~25FFFFH | 128000H~12FFFFH |

|           | BA38       | L   | Н   | L    | L   | Ι     | Ι    | L   | *   | *   | *   | 260000H~26FFFFH | 130000H~137FFFH |

|           | BA39       | L   | Н   | L    | L   | Η     | Η    | Н   | *   | *   | *   | 270000H~27FFFFH | 138000H~13FFFFH |

|           | BA40       | L   | Н   | L    | Ι   | L     | L    | L   | *   | *   | *   | 280000H~28FFFFH | 140000H~147FFFH |

|           | BA41       | L   | Н   | Ш    | Ι   | Ы     | L    | Н   | *   | *   | *   | 290000H~29FFFFH | 148000H~14FFFFH |

|           | BA42       | L   | Н   | L    | Ι   | Ы     | Ι    | L   | *   | *   | *   | 2A0000H~2AFFFH  | 150000H~157FFFH |

| BK5       | BA43       | L   | Н   | Ш    | Ι   | Ы     | Ι    | Н   | *   | *   | *   | 2B0000H~2BFFFFH | 158000H~15FFFFH |

| BKS       | BA44       | L   | Н   | L    | Н   | Н     | L    | L   | *   | *   | *   | 2C0000H~2CFFFFH | 160000H~167FFFH |

|           | BA45       | L   | Н   | L    | Н   | Н     | L    | Н   | *   | *   | *   | 2D0000H~2DFFFFH | 168000H~16FFFFH |

|           | BA46       | L   | Н   | L    | Η   | Η     | Η    | L   | *   | *   | *   | 2E0000H~2EFFFFH | 170000H~177FFFH |

|           | BA47       | L   | Н   | L    | Н   | Н     | Н    | Н   | *   | *   | *   | 2F0000H~2FFFFFH | 178000H~17FFFFH |

|           | BA48       | L   | Н   | Н    | L   | L     | L    | L   | *   | *   | *   | 300000H~30FFFFH | 180000H~187FFFH |

|           | BA49       | L   | Н   | Н    | L   | L     | L    | Н   | *   | *   | *   | 310000H~31FFFFH | 188000H~18FFFFH |

|           | BA50       | L   | Н   | Н    | L   | L     | Н    | L   | *   | *   | *   | 320000H~32FFFFH | 190000H~197FFFH |

| BK6       | BA51       | L   | Н   | Н    | L   | L     | Н    | Н   | *   | *   | *   | 330000H~33FFFFH | 198000H~19FFFFH |

| DNO       | BA52       | L   | Н   | Н    | L   | Н     | L    | L   | *   | *   | *   | 340000H~34FFFFH | 1A0000H~1A7FFFH |

|           | BA53       | L   | Н   | Н    | L   | Н     | L    | Н   | *   | *   | *   | 350000H~35FFFFH | 1A8000H~1AFFFFH |

|           | BA54       | L   | Н   | Н    | L   | Н     | Н    | L   | *   | *   | *   | 360000H~36FFFFH | 1B0000H~1B7FFFH |

|           | BA55       | L   | Н   | Н    | L   | Н     | Н    | Н   | *   | *   | *   | 370000H~37FFFFH | 1B8000H~1BFFFFH |

|           | BA56       | L   | Н   | Н    | Н   | L     | L    | L   | *   | *   | *   | 380000H~38FFFFH | 1C0000H~1C7FFFH |

|           | BA57       | L   | Н   | Η    | Η   | L     | L    | Н   | *   | *   | *   | 390000H~39FFFFH | 1C8000H~1CFFFFH |

|           | BA58       | L   | Н   | Н    | Н   | L     | Н    | L   | *   | *   | *   | 3A0000H~3AFFFFH | 1D0000H~1D7FFFH |

| DI/7      | BA59       | L   | Н   | Η    | Η   | L     | Η    | Н   | *   | *   | *   | 3B0000H~3BFFFFH | 1D8000H~1DFFFFH |

| BK7       | BA60       | L   | Н   | Н    | Н   | Н     | L    | L   | *   | *   | *   | 3C0000H~3CFFFFH | 1E0000H~1E7FFFH |

|           | BA61       | L   | Н   | Η    | Η   | Η     | L    | Н   | *   | *   | *   | 3D0000H~3DFFFFH | 1E8000H~1EFFFFH |

|           | BA62       | L   | Н   | Н    | Н   | Н     | Н    | L   | *   | *   | *   | 3E0000H~3EFFFFH | 1F0000H~1F7FFFH |

|           | BA63       | L   | Н   | Н    | Н   | Н     | Н    | Н   | *   | *   | *   | 3F0000H~3FFFFH  | 1F8000H~1FFFFFH |

| 5 4 4 11 6 | DI GOL     |     |     |      | BLO | OCK A | DDRE | ESS |     |     |     | ADDRES          | S RANGE         |

|------------|------------|-----|-----|------|-----|-------|------|-----|-----|-----|-----|-----------------|-----------------|

| BANK<br>#  | BLOCK<br># |     |     | BANK | ADD | RESS  |      |     |     |     |     | 7.551.25        |                 |

|            |            | A21 | A20 | A19  | A18 | A17   | A16  | A15 | A14 | A13 | A12 | BYTE MODE       | WORD MODE       |

|            | BA64       | Н   | L   | L    | L   | L     | L    | L   | *   | *   | *   | 400000H~40FFFFH | 200000H~207FFFH |

|            | BA65       | Н   | L   | L    | L   | L     | L    | Н   | *   | *   | *   | 410000H~41FFFFH | 208000H~20FFFFH |

|            | BA66       | Н   | L   | L    | L   | L     | Н    | L   | *   | *   | *   | 420000H~42FFFFH | 210000H~217FFFH |

| BK8        | BA67       | Н   | L   | L    | L   | L     | Н    | Н   | *   | *   | *   | 430000H~43FFFFH | 218000H~21FFFFH |

| БКо        | BA68       | Н   | L   | L    | L   | Ι     | L    | L   | *   | *   | *   | 440000H~44FFFFH | 220000H~227FFFH |

|            | BA69       | Н   | L   | L    | L   | Η     | L    | Н   | *   | *   | *   | 450000H~45FFFFH | 228000H~22FFFFH |

|            | BA70       | Н   | L   | Ы    | L   | Ι     | Ι    | L   | *   | *   | *   | 460000H~46FFFFH | 230000H~237FFFH |

|            | BA71       | Н   | L   | L    | L   | Η     | Η    | Н   | *   | *   | *   | 470000H~47FFFFH | 238000H~23FFFFH |

|            | BA72       | Н   | L   | L    | Ι   | L     | L    | L   | *   | *   | *   | 480000H~48FFFFH | 240000H~247FFFH |

|            | BA73       | Н   | L   | L    | Η   | L     | L    | Н   | *   | *   | *   | 490000H~49FFFFH | 248000H~24FFFFH |

|            | BA74       | Н   | L   | L    | Ι   | L     | Ι    | L   | *   | *   | *   | 4A0000H~4AFFFFH | 250000H~257FFFH |

| BK9        | BA75       | Н   | L   | Ы    | Ι   | Ы     | Ι    | Н   | *   | *   | *   | 4B0000H~4BFFFFH | 258000H~25FFFFH |

| BK9        | BA76       | Η   | L   | L    | Н   | Н     | L    | L   | *   | *   | *   | 4C0000H~4CFFFFH | 260000H~267FFFH |

|            | BA77       | Н   | L   | L    | Н   | Н     | L    | Н   | *   | *   | *   | 4D0000H~4DFFFFH | 268000H~26FFFFH |

|            | BA78       | Н   | L   | L    | Η   | Η     | Η    | L   | *   | *   | *   | 4E0000H~4EFFFFH | 270000H~277FFFH |

|            | BA79       | Н   | L   | L    | Н   | Н     | Н    | Н   | *   | *   | *   | 4F0000H~4FFFFFH | 278000H~27FFFFH |

|            | BA80       | Н   | L   | Η    | L   | L     | L    | L   | *   | *   | *   | 500000H~50FFFFH | 280000H~287FFFH |

|            | BA81       | Н   | L   | Н    | L   | L     | L    | Н   | *   | *   | *   | 510000H~51FFFFH | 288000H~28FFFFH |

|            | BA82       | Н   | L   | Н    | L   | L     | Н    | L   | *   | *   | *   | 520000H~52FFFFH | 290000H~297FFFH |

| BK10       | BA83       | Н   | L   | Н    | L   | L     | Н    | Н   | *   | *   | *   | 530000H~53FFFFH | 298000H~29FFFFH |

| BK10       | BA84       | Η   | L   | Н    | L   | Н     | L    | L   | *   | *   | *   | 540000H~54FFFFH | 2A0000H~2A7FFFH |

|            | BA85       | Н   | L   | Н    | L   | Н     | L    | Н   | *   | *   | *   | 550000H~55FFFFH | 2A8000H~2AFFFFH |

|            | BA86       | Н   | L   | Н    | L   | Н     | Н    | L   | *   | *   | *   | 560000H~56FFFFH | 2B0000H~2B7FFFH |

|            | BA87       | Н   | L   | Η    | L   | Η     | Η    | Н   | *   | *   | *   | 570000H~57FFFFH | 2B8000H~2BFFFFH |

|            | BA88       | Н   | L   | Н    | Н   | L     | L    | L   | *   | *   | *   | 580000H~58FFFFH | 2C0000H~2C7FFFH |

|            | BA89       | Н   | L   | Н    | Н   | L     | L    | Н   | *   | *   | *   | 590000H~59FFFFH | 2C8000H~2CFFFFH |

|            | BA90       | Н   | L   | Н    | Н   | L     | Н    | L   | *   | *   | *   | 5A0000H~5AFFFFH | 2D0000H~2D7FFFH |

| DV11       | BA91       | Н   | L   | Н    | Н   | L     | Н    | Н   | *   | *   | *   | 5B0000H~5BFFFFH | 2D8000H~2DFFFFH |

| BK11       | BA92       | Н   | L   | Н    | Н   | Н     | L    | L   | *   | *   | *   | 5C0000H~5CFFFFH | 2E0000H~2E7FFFH |

|            | BA93       | Н   | L   | Η    | Η   | Η     | L    | Н   | *   | *   | *   | 5D0000H~5DFFFFH | 2E8000H~2EFFFFH |

|            | BA94       | Н   | L   | Н    | Н   | Н     | Н    | L   | *   | *   | *   | 5E0000H~5EFFFFH | 2F0000H~2F7FFFH |

|            | BA95       | Н   | L   | Н    | Н   | Н     | Н    | Н   | *   | *   | *   | 5F0000H~5FFFFFH | 2F8000H~2FFFFFH |

| DANK      | DI OOK     |     |     |      | BLO | OCK A | DDRE | ESS |     |     |     | ADDRES          | S RANGE         |

|-----------|------------|-----|-----|------|-----|-------|------|-----|-----|-----|-----|-----------------|-----------------|

| BANK<br># | BLOCK<br># |     |     | BANK | ADD | RESS  |      | ı   |     |     | ı   | -               |                 |

|           |            | A21 | A20 | A19  | A18 | A17   | A16  | A15 | A14 | A13 | A12 | BYTE MODE       | WORD MODE       |

|           | BA96       | Н   | Ι   | L    | L   | Ы     | Ы    | L   | *   | *   | *   | 600000H~60FFFH  | 300000H~307FFFH |

|           | BA97       | Н   | Н   | L    | L   | L     | L    | Н   | *   | *   | *   | 610000H~61FFFFH | 308000H~30FFFFH |

|           | BA98       | Н   | Ι   | L    | L   | Ы     | Ι    | L   | *   | *   | *   | 620000H~62FFFFH | 310000H~317FFFH |

| BK12      | BA99       | Н   | I   | Г    | L   | L     | Н    | Н   | *   | *   | *   | 630000H~63FFFFH | 318000H~31FFFFH |

| BK12      | BA100      | Н   | Н   | L    | L   | Η     | L    | L   | *   | *   | *   | 640000H~64FFFH  | 320000H~327FFFH |

|           | BA101      | Н   | Ι   | Г    | L   | Н     | L    | Н   | *   | *   | *   | 650000H~65FFFFH | 328000H~32FFFFH |

|           | BA102      | Н   | Н   | L    | L   | Н     | Н    | L   | *   | *   | *   | 660000H~66FFFFH | 330000H~337FFFH |

|           | BA103      | Н   | Н   | L    | L   | Н     | Н    | Н   | *   | *   | *   | 670000H~67FFFH  | 338000H~33FFFFH |

|           | BA104      | Н   | Н   | L    | Н   | L     | L    | L   | *   | *   | *   | 680000H~68FFFFH | 340000H~347FFFH |

|           | BA105      | Н   | Н   | L    | Н   | L     | L    | Н   | *   | *   | *   | 690000H~69FFFH  | 348000H~34FFFFH |

|           | BA106      | Н   | Н   | L    | Н   | L     | Н    | L   | *   | *   | *   | 6A0000H~6AFFFFH | 350000H~357FFFH |

| DICAO     | BA107      | Н   | Н   | L    | Н   | L     | Н    | Н   | *   | *   | *   | 6B0000H~6BFFFFH | 358000H~35FFFFH |

| BK13      | BA108      | Н   | Н   | L    | Н   | Н     | L    | L   | *   | *   | *   | 6C0000H~6CFFFFH | 360000H~367FFFH |

|           | BA109      | Н   | Н   | L    | Н   | Н     | L    | Н   | *   | *   | *   | 6D0000H~6DFFFFH | 368000H~36FFFFH |

|           | BA110      | Н   | Н   | L    | Н   | Н     | Н    | L   | *   | *   | *   | 6E0000H~6EFFFFH | 370000H~377FFFH |

|           | BA111      | Н   | Н   | L    | Н   | Н     | Н    | Н   | *   | *   | *   | 6F0000H~6FFFFH  | 378000H~37FFFFH |

|           | BA112      | Н   | Н   | Н    | L   | L     | L    | L   | *   | *   | *   | 700000H~70FFFFH | 380000H~387FFFH |

|           | BA113      | Н   | Н   | Н    | L   | L     | L    | Н   | *   | *   | *   | 710000H~71FFFFH | 388000H~38FFFFH |

|           | BA114      | Н   | Н   | Н    | L   | L     | Н    | L   | *   | *   | *   | 720000H~72FFFFH | 390000H~397FFFH |

| DIZAA     | BA115      | Н   | Н   | Н    | L   | L     | Н    | Н   | *   | *   | *   | 730000H~73FFFFH | 398000H~39FFFFH |

| BK14      | BA116      | Н   | Н   | Н    | L   | Н     | L    | L   | *   | *   | *   | 740000H~74FFFH  | 3A0000H~3A7FFFH |

|           | BA117      | Н   | Н   | Н    | L   | Н     | L    | Н   | *   | *   | *   | 770000H~75FFFFH | 3A8000H~3AFFFFH |

|           | BA118      | Н   | Н   | Н    | L   | Н     | Н    | L   | *   | *   | *   | 760000H~76FFFH  | 3B0000H~3B7FFFH |

|           | BA119      | Н   | Н   | Н    | L   | Н     | Н    | Н   | *   | *   | *   | 770000H~77FFFFH | 3B8000H~3BFFFFH |

|           | BA120      | Н   | Н   | Н    | Н   | L     | L    | L   | *   | *   | *   | 780000H~78FFFFH | 3C0000H~3C7FFFH |

|           | BA121      | Н   | Н   | Н    | Н   | L     | L    | Н   | *   | *   | *   | 790000H~79FFFFH | 3C8000H~3CFFFFH |

|           | BA122      | Н   | Н   | Н    | Н   | L     | Н    | L   | *   | *   | *   | 7A0000H~7AFFFFH | 3D0000H~3D7FFFH |

| BK15      | BA123      | Н   | Н   | Н    | Н   | L     | Н    | Н   | *   | *   | *   | 7B0000H~7BFFFFH | 3D8000H~3DFFFFH |

|           | BA124      | Н   | Н   | Н    | Н   | Н     | L    | L   | *   | *   | *   | 7C0000H~7CFFFFH | 3E0000H~3E7FFFH |

|           | BA125      | Н   | Н   | Н    | Н   | Н     | L    | Н   | *   | *   | *   | 7D0000H~7DFFFFH | 3E8000H~3EFFFFH |

|           | BA126      | Н   | Н   | Н    | Н   | Н     | Н    | L   | *   | *   | *   | 7E0000H~7EFFFFH | 3F0000H~3F7FFFH |

# **TOSHIBA**

| BANK BLOCK |            |     |     | BLO  | OCK A | DDRE | ESS |     |     |     | ADDRES | S RANGE         |                 |

|------------|------------|-----|-----|------|-------|------|-----|-----|-----|-----|--------|-----------------|-----------------|

| BANK<br>#  | BLOCK<br># |     |     | BANK | ( ADD | RESS |     |     |     |     |        | ADDRES          | S RANGE         |

|            |            | A21 | A20 | A19  | A18   | A17  | A16 | A15 | A14 | A13 | A12    | BYTE MODE       | WORD MODE       |

|            | BA127      | Н   | Н   | Н    | Н     | Н    | Н   | Н   | L   | L   | L      | 7F0000H~7F1FFFH | 3F8000H~3F8FFFH |

|            | BA128      | Τ   | Н   | Н    | Н     | Н    | Н   | Н   | L   | L   | Н      | 7F2000H~7F3FFFH | 3F9000H~3F9FFFH |

|            | BA129      | Н   | Н   | Н    | Н     | Н    | Н   | Н   | L   | Н   | L      | 7F4000H~7F5FFFH | 3FA000H~3FAFFFH |

| BK16       | BA130      | Ι   | Н   | Н    | Н     | Н    | Н   | Н   | L   | Н   | Н      | 7F6000H~7F7FFFH | 3FB000H~3FBFFFH |

| BK 10      | BA131      | Н   | Н   | Н    | Н     | Н    | Н   | Н   | Η   | L   | L      | 7F8000H~7F9FFFH | 3FC000H~3FCFFFH |

|            | BA132      | Н   | Н   | Н    | Н     | Н    | Н   | Н   | Н   | L   | Н      | 7FA000H~7FBFFFH | 3FD000H~3FDFFFH |

|            | BA133      | Н   | Н   | Н    | Н     | Н    | Н   | Н   | Н   | Н   | L      | 7FC000H~7FDFFFH | 3FE000H~3FEFFFH |

| BA134      |            | Н   | Н   | Н    | Н     | Н    | Н   | Н   | Н   | Н   | Н      | 7FE000H~7FFFFFH | 3FF000H~3FFFFFH |

# (2) TH50VSF3681AASB (bottom boot block)

| BANK | BLOCK |     |     |      |     | OCK A |     | SS  | Ī   |     |     | ADDRES          | S RANGE         |

|------|-------|-----|-----|------|-----|-------|-----|-----|-----|-----|-----|-----------------|-----------------|

| #    | #     |     | I   | BANK | ADD | RESS  |     |     |     |     | I   |                 | Г               |

|      |       | A21 | A20 | A19  | A18 | A17   | A16 | A15 | A14 | A13 | A12 | BYTE MODE       | WORD MODE       |

|      | BA0   | L   | L   | L    | L   | L     | L   | L   | L   | L   | L   | 000000H~001FFFH | 000000H~000FFFH |

|      | BA1   | L   | L   | L    | L   | L     | L   | L   | L   | L   | Н   | 002000H~003FFFH | 001000H~001FFFH |

|      | BA2   | L   | L   | L    | L   | L     | L   | L   | L   | Н   | L   | 004000H~005FFFH | 002000H~002FFFH |

| BK0  | BA3   | L   | L   | L    | L   | L     | L   | L   | L   | Н   | Н   | 006000H~007FFFH | 003000H~003FFFH |

| Bito | BA4   | L   | L   | L    | L   | L     | L   | L   | Н   | L   | L   | 008000H~009FFFH | 004000H~004FFFH |

|      | BA5   | L   | L   | L    | L   | L     | L   | L   | Н   | L   | Н   | 00A000H~00BFFFH | 005000H~005FFFH |

|      | BA6   | L   | L   | L    | L   | L     | L   | L   | Н   | Н   | L   | 00C000H~00DFFFH | 006000H~006FFFH |

|      | BA7   | L   | L   | L    | L   | L     | L   | L   | Н   | Н   | Н   | 00E000H~00FFFFH | 007000H~007FFFH |

|      | BA8   | L   | L   | L    | L   | L     | L   | Н   | *   | *   | *   | 010000H~01FFFFH | 008000H~00FFFFH |

|      | BA9   | L   | L   | Ш    | Ш   | Ы     | Ι   | Ш   | *   | *   | *   | 020000H~02FFFFH | 010000H~017FFFH |

|      | BA10  | L   | L   | L    | L   | Ы     | Ι   | Ι   | *   | *   | *   | 030000H~03FFFFH | 018000H~01FFFFH |

| BK1  | BA11  | L   | L   | Г    | L   | Н     | L   | L   | *   | *   | *   | 040000H~04FFFFH | 020000H~027FFFH |

|      | BA12  | L   | L   | L    | L   | Н     | L   | Н   | *   | *   | *   | 050000H~05FFFFH | 028000H~02FFFFH |

|      | BA13  | L   | L   | L    | L   | Н     | Н   | L   | *   | *   | *   | 060000H~06FFFH  | 030000H~037FFFH |

|      | BA14  | L   | L   | L    | L   | Н     | Н   | Н   | *   | *   | *   | 070000H~07FFFH  | 038000H~03FFFFH |

|      | BA15  | L   | L   | L    | Н   | L     | L   | L   | *   | *   | *   | 080000H~08FFFFH | 040000H~047FFFH |

|      | BA16  | L   | L   | L    | Н   | L     | L   | Н   | *   | *   | *   | 090000H~09FFFH  | 048000H~04FFFH  |

|      | BA17  | L   | L   | L    | Н   | L     | Н   | L   | *   | *   | *   | 0A0000H~0AFFFH  | 050000H~057FFFH |

| DICO | BA18  | L   | L   | L    | Н   | L     | Н   | Н   | *   | *   | *   | 0B0000H~0BFFFFH | 058000H~05FFFFH |

| BK2  | BA19  | L   | L   | L    | Н   | Н     | L   | L   | *   | *   | *   | 0C0000H~0CFFFFH | 060000H~067FFFH |

|      | BA20  | L   | L   | L    | Н   | Н     | L   | Н   | *   | *   | *   | 0D0000H~0DFFFFH | 068000H~06FFFFH |

|      | BA21  | L   | L   | L    | Н   | Н     | Н   | L   | *   | *   | *   | 0E0000H~0EFFFFH | 070000H~077FFFH |

|      | BA22  | L   | L   | L    | Н   | Н     | Н   | Н   | *   | *   | *   | 0F0000H~0FFFFH  | 078000H~07FFFH  |

|      | BA23  | L   | L   | Н    | L   | L     | L   | L   | *   | *   | *   | 100000H~10FFFFH | 080000H~087FFFH |

|      | BA24  | L   | L   | Н    | L   | L     | L   | Н   | *   | *   | *   | 110000H~11FFFFH | 088000H~08FFFFH |

|      | BA25  | L   | L   | Н    | L   | L     | Н   | L   | *   | *   | *   | 120000H~12FFFFH | 090000H~097FFFH |

|      | BA26  | L   | L   | Н    | L   | L     | Н   | Н   | *   | *   | *   | 130000H~13FFFFH | 098000H~09FFFFH |

| BK3  | BA27  | L   | L   | Н    | L   | Н     | L   | L   | *   | *   | *   | 140000H~14FFFFH | 0A0000H~0A7FFFH |

|      | BA28  | L   | L   | Н    | L   | Н     | L   | Н   | *   | *   | *   | 150000H~15FFFFH | 0A8000H~0AFFFFH |

|      | BA29  | L   | L   | Н    | L   | Н     | Н   | L   | *   | *   | *   | 160000H~16FFFFH | 0B0000H~0B7FFFH |

|      | BA30  | L   | L   | Н    | L   | Н     | Н   | Н   | *   | *   | *   | 170000H~17FFFFH | 0B8000H~0BFFFFH |

| DANK      | BLOCK |     |     |      | BLO | OCK A | DDRE | ESS |     |     |     | ADDRES          | S RANGE         |

|-----------|-------|-----|-----|------|-----|-------|------|-----|-----|-----|-----|-----------------|-----------------|

| BANK<br># | #     |     |     | BANK | ADD | RESS  | 1    |     |     | 1   |     |                 |                 |

|           |       | A21 | A20 | A19  | A18 | A17   | A16  | A15 | A14 | A13 | A12 | BYTE MODE       | WORD MODE       |

|           | BA31  | L   | L   | Н    | Н   | L     | L    | L   | *   | *   | *   | 180000H~18FFFFH | 0C0000H~0C7FFFH |

|           | BA32  | L   | L   | Н    | Н   | L     | L    | Н   | *   | *   | *   | 190000H~19FFFFH | 0C8000H~0CFFFFH |

|           | BA33  | L   | L   | Н    | Н   | L     | Н    | L   | *   | *   | *   | 1A0000H~1AFFFFH | 0D0000H~0D7FFFH |

| BK4       | BA34  | L   | L   | Н    | Н   | L     | Н    | Н   | *   | *   | *   | 1B0000H~1BFFFFH | 0D8000H~0DFFFFH |

| Bitt      | BA35  | L   | L   | Н    | Н   | Н     | L    | L   | *   | *   | *   | 1C0000H~1CFFFFH | 0E0000H~0E7FFH  |

|           | BA36  | L   | L   | Н    | Η   | Η     | L    | Н   | *   | *   | *   | 1D0000H~1DFFFFH | 0E8000H~0EFFFFH |

|           | BA37  | L   | L   | Η    | Ι   | Ι     | Ι    | L   | *   | *   | *   | 1E0000H~1EFFFFH | 0F0000H~0F7FFH  |

|           | BA38  | L   | L   | Н    | Η   | Η     | Η    | Н   | *   | *   | *   | 1F0000H~1FFFFFH | 0F8000H~0FFFFFH |

|           | BA39  | L   | Н   | L    | L   | L     | L    | L   | *   | *   | *   | 200000H~20FFFFH | 100000H~107FFFH |

|           | BA40  | L   | Н   | Ш    | Ы   | Ы     | ┙    | Н   | *   | *   | *   | 210000H~21FFFFH | 108000H~10FFFFH |

|           | BA41  | L   | Н   | L    | L   | L     | Ι    | L   | *   | *   | *   | 220000H~22FFFFH | 110000H~117FFFH |

| BK5       | BA42  | L   | Н   | L    | L   | L     | Η    | Н   | *   | *   | *   | 230000H~23FFFFH | 118000H~11FFFFH |

| BKS       | BA43  | L   | Н   | Г    | L   | Н     | L    | L   | *   | *   | *   | 240000H~24FFFFH | 120000H~127FFFH |

|           | BA44  | L   | Н   | L    | L   | Η     | L    | Н   | *   | *   | *   | 250000H~25FFFFH | 128000H~12FFFFH |

|           | BA45  | L   | Н   | L    | L   | Ι     | Ι    | L   | *   | *   | *   | 260000H~26FFFFH | 130000H~137FFFH |

|           | BA46  | L   | Н   | Ш    | Ы   | Ι     | Ι    | Н   | *   | *   | *   | 270000H~27FFFFH | 138000H~13FFFFH |

|           | BA47  | L   | Н   | L    | Ι   | Ы     | Ы    | L   | *   | *   | *   | 280000H~28FFFFH | 140000H~147FFFH |

|           | BA48  | L   | Н   | Ш    | Ι   | Ы     | ┙    | Н   | *   | *   | *   | 290000H~29FFFFH | 148000H~14FFFFH |

|           | BA49  | L   | Н   | Г    | Н   | L     | Н    | L   | *   | *   | *   | 2A0000H~2AFFFH  | 150000H~157FFFH |

| BK6       | BA50  | L   | Н   | L    | Η   | L     | Η    | Н   | *   | *   | *   | 2B0000H~2BFFFFH | 158000H~15FFFFH |

| BRO       | BA51  | L   | Н   | Г    | Н   | Н     | L    | L   | *   | *   | *   | 2C0000H~2CFFFFH | 160000H~167FFFH |

|           | BA52  | L   | Н   | L    | Η   | Η     | L    | Н   | *   | *   | *   | 2D0000H~2DFFFFH | 168000H~16FFFFH |

|           | BA53  | L   | Н   | Г    | Н   | Н     | Н    | L   | *   | *   | *   | 2E0000H~2EFFFFH | 170000H~177FFFH |

|           | BA54  | L   | Н   | L    | Η   | Η     | Η    | Н   | *   | *   | *   | 2F0000H~2FFFFH  | 178000H~17FFFFH |

|           | BA55  | L   | Н   | Ι    | L   | L     | L    | L   | *   | *   | *   | 300000H~30FFFFH | 180000H~187FFFH |

|           | BA56  | L   | Н   | Н    | L   | L     | L    | Н   | *   | *   | *   | 310000H~31FFFFH | 188000H~18FFFFH |

|           | BA57  | L   | Н   | Н    | L   | L     | Н    | L   | *   | *   | *   | 320000H~32FFFFH | 190000H~197FFFH |

| BK7       | BA58  | L   | Н   | Н    | L   | L     | Н    | Н   | *   | *   | *   | 330000H~33FFFFH | 198000H~19FFFFH |

| DIV!      | BA59  | L   | Н   | Н    | L   | Н     | L    | L   | *   | *   | *   | 340000H~34FFFFH | 1A0000H~1A7FFFH |

|           | BA60  | L   | Н   | Н    | L   | Н     | L    | Н   | *   | *   | *   | 350000H~35FFFFH | 1A8000H~1AFFFFH |

|           | BA61  | L   | Н   | Н    | L   | Н     | Н    | L   | *   | *   | *   | 360000H~36FFFFH | 1B0000H~1B7FFFH |

|           | BA62  | L   | Н   | Н    | L   | Н     | Н    | Н   | *   | *   | *   | 370000H~37FFFFH | 1B8000H~1BFFFFH |

| DANIK     | DI OOK     |     |     |      | BLO | OCK A | DDRE | ESS |     |     |     | ADDRES          | S RANGE         |

|-----------|------------|-----|-----|------|-----|-------|------|-----|-----|-----|-----|-----------------|-----------------|

| BANK<br># | BLOCK<br># |     | ı   | BANK | ADD | RESS  |      | ı   |     |     | ı   |                 |                 |

|           |            | A21 | A20 | A19  | A18 | A17   | A16  | A15 | A14 | A13 | A12 | BYTE MODE       | WORD MODE       |

|           | BA63       | L   | Н   | Н    | Н   | L     | L    | L   | *   | *   | *   | 380000H~38FFFFH | 1C0000H~1C7FFFH |

|           | BA64       | L   | Н   | Н    | Н   | L     | L    | Н   | *   | *   | *   | 390000H~39FFFFH | 1C8000H~1CFFFFH |

|           | BA65       | L   | Н   | Н    | Н   | L     | Н    | L   | *   | *   | *   | 3A0000H~3AFFFFH | 1D0000H~1D7FFFH |

| BK8       | BA66       | L   | Н   | Н    | Н   | L     | Н    | Н   | *   | *   | *   | 3B0000H~3BFFFFH | 1D8000H~1DFFFFH |

| Bito      | BA67       | L   | Н   | Н    | Н   | Н     | L    | L   | *   | *   | *   | 3C0000H~3CFFFFH | 1E0000H~1E7FFFH |

|           | BA68       | L   | Н   | Н    | Н   | Н     | L    | Н   | *   | *   | *   | 3D0000H~3DFFFFH | 1E8000H~1EFFFFH |

|           | BA69       | L   | Н   | Η    | Ι   | Н     | Ι    | L   | *   | *   | *   | 3E0000H~3EFFFFH | 1F0000H~1F7FFFH |

|           | BA70       | L   | Н   | Н    | Η   | Н     | Η    | Н   | *   | *   | *   | 3F0000H~3FFFFFH | 1F8000H~1FFFFFH |

|           | BA71       | Н   | L   | L    | L   | L     | L    | L   | *   | *   | *   | 400000H~40FFFFH | 200000H~207FFFH |

|           | BA72       | Н   | L   | Ш    | Ы   | L     | ┙    | Н   | *   | *   | *   | 410000H~41FFFFH | 208000H~20FFFFH |

|           | BA73       | Н   | L   | L    | L   | L     | Ι    | L   | *   | *   | *   | 420000H~42FFFFH | 210000H~217FFFH |

| BK9       | BA74       | Н   | L   | Г    | L   | L     | Н    | Н   | *   | *   | *   | 430000H~43FFFFH | 218000H~21FFFFH |

| DK9       | BA75       | Н   | L   | L    | L   | Н     | L    | L   | *   | *   | *   | 440000H~44FFFFH | 220000H~227FFFH |

|           | BA76       | Н   | L   | L    | L   | Н     | L    | Н   | *   | *   | *   | 450000H~45FFFFH | 228000H~22FFFFH |

|           | BA77       | Н   | L   | L    | L   | Н     | Н    | L   | *   | *   | *   | 460000H~46FFFFH | 230000H~237FFFH |

|           | BA78       | Н   | L   | L    | L   | Н     | Н    | Н   | *   | *   | *   | 470000H~47FFFFH | 238000H~23FFFFH |

|           | BA79       | Н   | L   | L    | Н   | L     | L    | L   | *   | *   | *   | 480000H~48FFFFH | 240000H~247FFFH |

|           | BA80       | Н   | L   | L    | Н   | L     | L    | Н   | *   | *   | *   | 490000H~49FFFFH | 248000H~24FFFFH |

|           | BA81       | Н   | L   | L    | Н   | L     | Н    | L   | *   | *   | *   | 4A0000H~4AFFFFH | 250000H~257FFFH |

| DIC10     | BA82       | Н   | L   | L    | Н   | L     | Н    | Н   | *   | *   | *   | 4B0000H~4BFFFFH | 258000H~25FFFFH |

| BK10      | BA83       | Н   | L   | L    | Н   | Н     | L    | L   | *   | *   | *   | 4C0000H~4CFFFFH | 260000H~267FFFH |

|           | BA84       | Н   | L   | L    | Н   | Н     | L    | Н   | *   | *   | *   | 4D0000H~4DFFFFH | 268000H~26FFFFH |

|           | BA85       | Н   | L   | L    | Н   | Н     | Н    | L   | *   | *   | *   | 4E0000H~4EFFFFH | 270000H~277FFFH |

|           | BA86       | Н   | L   | L    | Н   | Н     | Н    | Н   | *   | *   | *   | 4F0000H~4FFFFH  | 278000H~27FFFFH |

|           | BA87       | Н   | L   | Н    | L   | L     | L    | L   | *   | *   | *   | 500000H~50FFFFH | 280000H~287FFFH |

|           | BA88       | Н   | L   | Н    | L   | L     | L    | Н   | *   | *   | *   | 510000H~51FFFFH | 288000H~28FFFFH |

|           | BA89       | Н   | L   | Н    | L   | L     | Н    | L   | *   | *   | *   | 520000H~52FFFFH | 290000H~297FFFH |

| DICAL     | BA90       | Н   | L   | Н    | L   | L     | Н    | Н   | *   | *   | *   | 530000H~53FFFFH | 298000H~29FFFFH |

| BK11      | BA91       | Н   | L   | Н    | L   | Н     | L    | L   | *   | *   | *   | 540000H~54FFFFH | 2A0000H~2A7FFFH |

|           | BA92       | Н   | L   | Н    | L   | Н     | L    | Н   | *   | *   | *   | 550000H~55FFFFH | 2A8000H~2AFFFFH |

|           | BA93       | Н   | L   | Н    | L   | Н     | Н    | L   | *   | *   | *   | 560000H~56FFFFH | 2B0000H~2B7FFFH |

|           | BA94       | Н   | L   | Н    | L   | Н     | Н    | Н   | *   | *   | *   | 570000H~57FFFFH | 2B8000H~2BFFFFH |

| DANK      | DI OOK     |     |     |      | BLO | OCK A | DDRE | ESS | 1   |     |     | ADDRES          | S RANGE         |

|-----------|------------|-----|-----|------|-----|-------|------|-----|-----|-----|-----|-----------------|-----------------|

| BANK<br># | BLOCK<br># |     | ı   | BANK | ADD | RESS  |      | ı   |     |     | ı   |                 |                 |

|           |            | A21 | A20 | A19  | A18 | A17   | A16  | A15 | A14 | A13 | A12 | BYTE MODE       | WORD MODE       |

|           | BA95       | Н   | L   | Н    | Н   | L     | L    | L   | *   | *   | *   | 580000H~58FFFFH | 2C0000H~2C7FFFH |

|           | BA96       | Н   | L   | Н    | Н   | L     | L    | Н   | *   | *   | *   | 590000H~59FFFH  | 2C8000H~2CFFFFH |

|           | BA97       | Н   | L   | Н    | Н   | L     | Н    | L   | *   | *   | *   | 5A0000H~5AFFFFH | 2D0000H~2D7FFFH |

| BK12      | BA98       | Н   | L   | Н    | Н   | L     | Н    | Н   | *   | *   | *   | 5B0000H~5BFFFFH | 2D8000H~2DFFFFH |

| DICIZ     | BA99       | Н   | L   | Н    | Н   | Н     | L    | L   | *   | *   | *   | 5C0000H~5CFFFFH | 2E0000H~2E7FFH  |

|           | BA100      | Н   | L   | Н    | Н   | Н     | L    | Н   | *   | *   | *   | 5D0000H~5DFFFFH | 2E8000H~2EFFFFH |

|           | BA101      | Н   | L   | Η    | Ι   | Н     | Ι    | L   | *   | *   | *   | 5E0000H~5EFFFFH | 2F0000H~2F7FFFH |

|           | BA102      | Н   | L   | Н    | Η   | Н     | Η    | Н   | *   | *   | *   | 5F0000H~5FFFFFH | 2F8000H~2FFFFFH |

|           | BA103      | Н   | Н   | L    | L   | L     | L    | L   | *   | *   | *   | 600000H~60FFFH  | 300000H~307FFFH |

|           | BA104      | Н   | Н   | L    | L   | L     | L    | Н   | *   | *   | *   | 610000H~61FFFFH | 308000H~30FFFFH |

|           | BA105      | Н   | Н   | L    | L   | L     | Ι    | L   | *   | *   | *   | 620000H~62FFFFH | 310000H~317FFFH |

| BK13      | BA106      | Н   | Н   | L    | L   | L     | Η    | Н   | *   | *   | *   | 630000H~63FFFFH | 318000H~31FFFFH |

| BK 13     | BA107      | Н   | Н   | L    | L   | Н     | L    | L   | *   | *   | *   | 640000H~64FFFH  | 320000H~327FFFH |

|           | BA108      | Н   | Н   | L    | L   | Н     | Ы    | Н   | *   | *   | *   | 650000H~65FFFFH | 328000H~32FFFFH |

|           | BA109      | Н   | Н   | L    | L   | Н     | Ι    | L   | *   | *   | *   | 660000H~66FFFFH | 330000H~337FFFH |

|           | BA110      | Н   | Н   | Г    | L   | Н     | Н    | Н   | *   | *   | *   | 670000H~67FFFH  | 338000H~33FFFFH |

|           | BA111      | Н   | Н   | L    | Η   | L     | L    | L   | *   | *   | *   | 680000H~68FFFFH | 340000H~347FFFH |

|           | BA112      | Н   | Н   | Г    | Н   | L     | L    | Н   | *   | *   | *   | 690000H~69FFFFH | 348000H~34FFFFH |

|           | BA113      | Н   | Н   | L    | Н   | L     | Н    | L   | *   | *   | *   | 6A0000H~6AFFFFH | 350000H~357FFFH |

| BK14      | BA114      | Н   | Н   | L    | Н   | L     | Н    | Н   | *   | *   | *   | 6B0000H~6BFFFFH | 358000H~35FFFFH |

| DK 14     | BA115      | Н   | Н   | L    | Н   | Н     | L    | L   | *   | *   | *   | 6C0000H~6CFFFFH | 360000H~367FFFH |

|           | BA116      | Н   | Н   | L    | Н   | Н     | L    | Н   | *   | *   | *   | 6D0000H~6DFFFFH | 368000H~36FFFFH |

|           | BA117      | Н   | Н   | L    | Н   | Н     | Н    | L   | *   | *   | *   | 6E0000H~6EFFFFH | 370000H~377FFFH |

|           | BA118      | Н   | Н   | L    | Н   | Н     | Н    | Н   | *   | *   | *   | 6F0000H~6FFFFH  | 378000H~37FFFFH |

|           | BA119      | Н   | Н   | Н    | L   | L     | L    | L   | *   | *   | *   | 700000H~70FFFFH | 380000H~387FFFH |

|           | BA120      | Н   | Н   | Н    | L   | L     | L    | Н   | *   | *   | *   | 710000H~71FFFFH | 388000H~38FFFFH |

|           | BA121      | Н   | Н   | Н    | L   | L     | Н    | L   | *   | *   | *   | 720000H~72FFFFH | 390000H~397FFFH |

| DV15      | BA122      | Н   | Н   | Η    | L   | L     | Η    | Н   | *   | *   | *   | 730000H~73FFFFH | 398000H~39FFFFH |

| BK15      | BA123      | Н   | Н   | Н    | L   | Н     | L    | L   | *   | *   | *   | 740000H~74FFFFH | 3A0000H~3A7FFFH |

|           | BA124      | Н   | Н   | Η    | L   | Н     | L    | Н   | *   | *   | *   | 750000H~75FFFFH | 3A8000H~3AFFFFH |

|           | BA125      | Н   | Н   | Н    | L   | Н     | Н    | L   | *   | *   | *   | 760000H~76FFFFH | 3B0000H~3B7FFFH |

|           | BA126      | Н   | Н   | Н    | L   | Н     | Н    | Н   | *   | *   | *   | 770000H~77FFFFH | 3B8000H~3BFFFFH |

# **TOSHIBA**

| BANK BLOCK |            |     |     | BLO  | OCK A | DDRE | ESS |     |     |     | ADDRES | S RANGE         |                 |

|------------|------------|-----|-----|------|-------|------|-----|-----|-----|-----|--------|-----------------|-----------------|

| BANK<br>#  | BLOCK<br># |     |     | BANK | ( ADD | RESS |     |     |     |     |        | ADDRES          | S RANGE         |

|            |            | A21 | A20 | A19  | A18   | A17  | A16 | A15 | A14 | A13 | A12    | BYTE MODE       | WORD MODE       |

|            | BA127      | Н   | Н   | Н    | Н     | L    | L   | L   | *   | *   | *      | 780000H~78FFFFH | 3C0000H~3C7FFFH |

|            | BA128      | Η   | Τ   | Н    | Н     | L    | L   | Н   | *   | *   | *      | 790000H~79FFFFH | 3C8000H~3CFFFFH |

|            | BA129      | Н   | Н   | Н    | Н     | L    | Н   | L   | *   | *   | *      | 7A0000H~7AFFFFH | 3D0000H~3D7FFFH |