### Features

- Single-chip 2.5GHz WiMAX Transceiver

- Fully Differential Design

- Low-IF/Zero-IF Transceiver Architecture; Requires No External Filters

- Self Calibration Mode for RX / TX Filters

- Support Channel Bandwidths of 3.5, 5.0, 7.0, 8.75, and 10MHz

- Modulation up to 64QAM

- Ultra-fast Fractional-N Synthesizer

- Sensitivity < -74dBm at 64-QAM, CR=3/4, 7MHz BW Typical

- Phase Noise Synthesizer: 0.8° (-37dBc)

- Low Supply Voltage: 3.0 V

- TX Output PRF: 0 dBm, -34 dB EVM

- RX/TX Operating Current: 270/360mA Typical

- 56-lead QFN Package

- Low External Component Count

- · Integrated Self IQ Calibration (no external components or control)

- HFDD Support

### Applications

- 2.5GHz Band Wireless Communication Devices

- IEEE<sup>®</sup> 802.16-2004 Radios

- Supports OFDM up to 64QAM

### Description

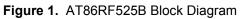

Atmel<sup>®</sup>'s AT86RF525B is a fully integrated, low cost RF 2.5GHz Low-IF/Zero-IF conversion transceiver for WiMAX applications. It combines excellent RF performance, small size, and low current consumption. The AT86RF525B chip is fabricated on the advanced SiGe BiCMOS process AT46000. The transceiver combines LNA, PA driver, RX/TX mixer, RX/TX filters, VCO, Synthesizer, RX Gain control, and TX Power control, all fully digitally controlled. Only a minimum number of external components are required.

2.5GHz WiMAX Transceiver

## AT86RF525B

## Preliminary

5189A-WiMAX-9/07

### **Quick Reference Data**

Table 1. Quick Reference Data

| Symbol             | Parameter                             | Conditions                                                | Min | Тур        | Max        | Unit       |

|--------------------|---------------------------------------|-----------------------------------------------------------|-----|------------|------------|------------|

| F <sub>RF</sub>    | Input Center Frequency                |                                                           | 2.3 |            | 2.7        | GHz        |

| DFRS               | Frequency Resolution                  |                                                           |     |            | 19.6       | Hz         |

| V <sub>DD</sub>    | Supply Voltage                        | Applied to VDD pins                                       | 3.0 | 3.3        | 3.6        | V          |

| IDDRX              | Supply Current                        | Receive mode                                              |     | 270        |            | mA         |

| I <sub>DDTX</sub>  | Supply Current                        | Transmit mode, 0dBm                                       |     | 360        |            | mA         |

| I <sub>DDSYN</sub> | Supply Current                        | Synthesizer Mode                                          |     | 135        |            | mA         |

| I <sub>DDSTB</sub> | Supply Current                        | Stand By Mode,<br>CLK driver activated<br>Clock Load 20pF |     | 2, 5       |            | mA         |

| SENS               | Sensitivity QPSK<br>Sensitivity 64QAM | BW=3.5MHz, CR=½, S/N=9.4dB<br>BW=7MHz, CR=¾, S/N=24.4dB   |     | -92<br>-74 | -88<br>-70 | dBm        |

| P <sub>RF</sub>    | TX Output Power                       | FRF= 2.5 GHz, 64QAM, EVM=-<br>34dB, incl. Balun           |     | 0          |            | dBm        |

| PN                 | Integrated Phase Noise of Synthesizer | Integrated over Frequency Range<br>50kHz 1MHz             |     | 0.8        |            | deg<br>rms |

| T <sub>AMB</sub>   | Operating Ambient<br>Temperature      |                                                           | -30 | 27         | +70        | °C         |

Note: All voltages are referred to GND. VDD=3.0V TAMB=27°C, unless otherwise noted.

### **Electrical Characteristics**

Table 2.

Receiver Characteristics (Note 1)

| Symbol                    | Parameter                             | Min                                                                    | Тур     | Мах  | Unit       |                       |

|---------------------------|---------------------------------------|------------------------------------------------------------------------|---------|------|------------|-----------------------|

|                           | •                                     | System                                                                 |         |      |            |                       |

| F <sub>RF</sub>           | Input Center Frequency                |                                                                        | 2.3     |      | 2.7        | GHz                   |

| Z <sub>IN</sub>           | Differential Impedance at LNA Input   | Includes a matching inductor and two series capacitors                 |         | 100  |            | $\Omega$ diff.        |

| SENS                      | Sensitivity QPSK<br>Sensitivity 64QAM | BW=3.5MHz, CR=½, S/N=9.4dB<br>BW=7MHz, CR=¾, S/N=24.4dB                |         |      | -88<br>-70 | dBm                   |

| P <sub>IN,MAX</sub>       | Maximum Input Power                   | BW=7MHz, EVM=24.4dB                                                    | -20     |      |            | dBm                   |

| $NF_{SSB}$                | Noise Figure Single Side Band         | high gain mode, includes balun<br>w/o Frontend loss                    |         | 5    | 6          | dB                    |

| G <sub>RX,STEP</sub>      | RX Chain: Gain Steps                  |                                                                        |         | 0.76 |            | dB                    |

| G <sub>RX,RANG</sub><br>E | RX Chain: Gain Range                  |                                                                        |         | 95.5 |            | dB                    |

| t <sub>RX/TX</sub>        | RX to TX Switching Time               | TDD Mode<br>HFDD Mode                                                  |         |      | 5<br>50    | μs                    |

| Symbol                    | Parameter                             | Conditions                                                             | Min     | Тур  | Max        | Unit                  |

| ACR±1                     | Adjacent Ch. Rejection                | 16QAM 3/4<br>64QAM 3/4                                                 |         |      | -11<br>-4  | dB                    |

| ACR±2                     | Nonadjacent Ch.<br>Rejection          | 16QAM 3/4<br>64QAM 3/4                                                 |         |      | -30<br>-23 | dB                    |

|                           | Baseban                               | d filters, DC cancellation, RSSI, IC                                   | outputs |      |            |                       |

| R <sub>OUT</sub>          | Output load resistance                | Pin to GND                                                             | 1       |      |            | MΩ                    |

| C <sub>OUT</sub>          | Output load capacitance               | Pin to GND                                                             |         | 20   | 50         | pF                    |

| V <sub>OMAX</sub>         | Maximum Output Voltage                | Differential                                                           | 1       |      |            | V                     |

| V <sub>OUT</sub>          | I or Q output Voltage                 | Differential at the load specified<br>Output buffer gain offset = +6dB |         | 1    |            | V <sub>p</sub> , diff |

| G <sub>B,OFFSTE</sub><br>P | l, Q output buffer:<br>Gain Offset Steps |                                                |     | 0.76                      |       | dB   |

|----------------------------|------------------------------------------|------------------------------------------------|-----|---------------------------|-------|------|

| G <sub>B,RANGE</sub>       | I, Q output buffer:<br>Gain Range        |                                                | -9  |                           | +2.25 | dB   |

| BW <sub>3dB</sub>          | 3-dB Bandwidth of Filter                 | 1.875MHz<br>2.7MHz<br>3.75MHz<br>5MHz<br>Note2 |     | 3.5<br>5.0<br>7.0<br>8.75 |       | MHz  |

| IMRR                       | Image Rejection Ratio                    | Note 2                                         |     | -42                       | -36   | dB   |

| CMD                        | Common Mode IQ Voltage                   |                                                | 1.2 | 1.25                      | 1.35  | V DC |

### Table 3. Transmitter Characteristics (Note 1)

| Symbol                | Parameter                                 | Conditions                                                               | Min | Тур                       | Max     | Unit          |

|-----------------------|-------------------------------------------|--------------------------------------------------------------------------|-----|---------------------------|---------|---------------|

|                       | 1                                         | System                                                                   |     |                           |         |               |

| F <sub>RF</sub>       | Output Center Frequency                   |                                                                          | 2.3 |                           | 2.7     | GHz           |

| Z <sub>OUT</sub>      | Differential Impedance at Driver Output   |                                                                          |     | 100                       |         | $\Omega$ diff |

| P <sub>OUT</sub>      | TX Output Power                           | For 64QAM modulated signals                                              |     | 0                         |         | dBm           |

| t <sub>TX/RX</sub>    | TX to RX Switching Time                   | TDD Mode<br>HFDD Mode                                                    |     |                           | 5<br>50 | μs            |

| G <sub>PA,RANGE</sub> | TX Chain Gain Control<br>Range            |                                                                          | 50  | 71.9                      |         | dB            |

| G <sub>LSB,STEP</sub> | TX Chain Gain Control<br>LSB<br>Step Size |                                                                          |     | 0.76                      |         | dB            |

| BW <sub>3dB</sub>     | 3-dB Bandwidth of Filter                  | 1.875MHz<br>2.7MHz<br>3.75MHz<br>5MHz<br>Note2                           |     | 3.5<br>5.0<br>7.0<br>8.75 |         | MHz           |

| L <sub>Carr</sub>     | Carrier Leakage                           | Referred to sub carrier level of<br>64QAM modulated signals<br>Note 2, 3 |     | -20                       | -12     | dBc           |

| IMRR                  | Image Rejection Ratio                     | Referred to sub carrier level of<br>64QAM modulated signals<br>Note 2, 3 |     | -49                       | -45     | dBr           |

| Symbol                | Parameter                                 | Conditions                                                               | Min | Тур                       | Max     | Unit          |

|                       |                                           | System                                                                   |     |                           |         |               |

| EVM                   | Error Vector Magnitude                    | 64QAM ¾, 0dBm Output Power                                               |     | -34                       |         | dB            |

| Z <sub>IN</sub>       | IQ Input Impedance                        | Differential                                                             |     | 10                        |         | kΩ diff       |

| V <sub>IN</sub>       | IQ Input Voltage                          | Peak, Differential                                                       |     | 1                         |         | Vp,diff       |

| V <sub>IN,DC</sub>    | DC Input Voltage                          |                                                                          |     | 1.25                      |         | V             |

Notes: 1. VDD=3.0V, TAMB =27°C, FRF=3.55 GHz, specific application circuit TBD, unless otherwise noted.

2. Internally adjusted by build-in self-calibration.

# AT86RF525B [Preliminary] ،

4

### **Functional Description**

The AT86RF525B is based on the IEEE 802.16-2004 standard. This product will provide transmit, receive, and frequency synthesis functions using the OFDM modulation schemes, as defined in the above specifications.

The AT86RF525B consists of a frequency-agile RF transceiver intended for use in 2.5GHz licensed bands at data rates up to 26Mbps.

Configuration and control registers and a bi-directional data communications interface are available to communicate with existing baseband devices from different vendors. The AT86RF525B addresses the requirements of base station (BS) as well as subscriber stations (SS) equipment. The device will operate down to 3.0V.

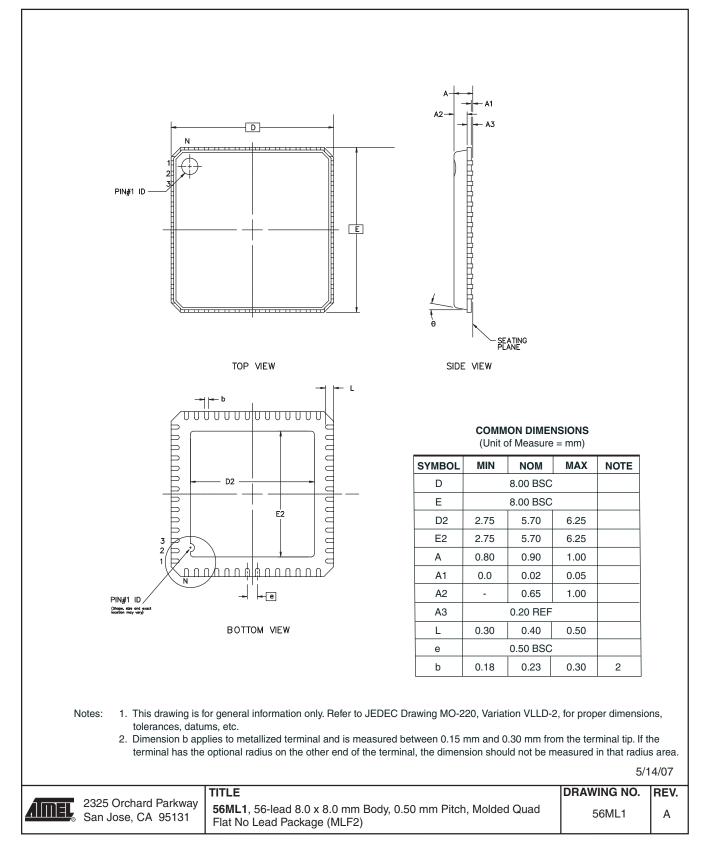

The AT86RF525B is fabricated in Atmel's AT46000 advanced SiGe BiCMOS process technology and is assembled in a 8mm x 8mm 56-lead QFN package.

### **RX** Path

The differential low noise amplifier (DLNA) makes use of a differential bipolar stage with resistive emitter linearization. For digital gain control operation the DLNA supports the four gain modes 0, 6, 12, and 18dB. The linearity improves as the gain is reduced.

The differential inphase quadrature phase mixer (IQMIX) utilizes a differential bipolar stage with emitter degeneration for the best linearity performance. A complex driving LO source is chosen for optimal LO leakage cancellation. The IQMIX has 4, 10, 16, and 22dB of switchable gain.

The receive poly phase filter (RXPPF) is designed as a frequency shifted leapfrog structure. The filter provides three different bandwidths at three different center frequencies. The bandwidth of this filter is tuned by a built-in self-test (BIST). The PPF filter cap values are automatically adjusted upon power-up. The cap tuning values can be recalled via SPI. Image rejection is also calibrated upon request via SPI.

There are also three digitally controlled gain amplifiers (DGA1-3) available to provide the necessary amplification for the receive signal. Each stage supports the four gain modes 0, 6, 12, and 18dB respectively. An additional fine gain stage DGB enables gain tuning of approximately  $\pm$ 6dB in 0.76 dB steps. An output buffer with gain offset matches the voltage swing of the radio to the respective Baseband input stage.

The gain control is complete digital and affects LNA, MIX, and the three DGAs by using the same granularity for each stage. The BB/MAC provides the gain vector at a separated serial interface.

Fast TX/RX switching is possible via TX/RX switch input pins controlled by BB/MAC.

The low-IF conversion receiver does not have to amplify DC signals, but the gain setting process produces different offsets in gain stages. An offset correction takes place after each gain step in the receiver to prevent signal saturation. Every stage has an individual offset correction circuit to maintain the correct overall dynamic range. The DC feedback (DCFB) works as an output offset compensation network, which depends on actual gain setting.

The internal gain control operation is optimized for fixed target amplitude. To adapt to different application requirements, the IQ Output Buffer DGB has a programmable gain offset from – 1.5dB to 6dB in increments of 0.76dB. This allows the nominal output voltage to be set between 180mVp and 650mVp. The gain is controllable via the register setting. The IQOB is able to drive

a capacitive load on all four-output ports (RXI1, RXI2, RXQ1, RXQ2). The CMD pin is available to provide the common mode voltage of the Digital Output Buffer (DGB).

#### TX Path

The transmit low pass filter (TXLP) is band limited to meet the emission regulation for OFDM signals. THe dat signals to the four input ports (TX11, TX12, TXQ1, TXQ2) driving the TXLP should be digital but with defined levels.

The complex filtered BB signal is up converted with IQ low-IF up converter (IQUC). A complex driving LO source is used to minimize LO leakage. The output currents of the two mixer stages are added together. The resulting signal drives the power amplifier control block (PAC).

The PAC is a Gilbert cell based current domain amplifier with the gain controlled by DC voltage across the mixer core. In that way linear to logarithmic (dB) gain control is achieved.

The BB/MAC provides the gain setting vector at a separated serial interface.

#### Synthesizer

The Voltage Controlled Oscillator (VCO) operates at two times the Local Oscillator (LO) frequency. The VCO output feeds a specialized divide-by-two module. The divider provides the required times one LO frequency with both in-phase and quadrature components for use in the IQ Mixer (IQMIX) and the IQ UpConverter (IQUC). The use of the divider at two times the LO also reduces load pull on the LO frequency each time the integrated Power Amplifier (PA) is enabled.

The VCO core is a differential double-grounded bipolar stage with the load for the VCO tank circuit made up of inductive and capacitive components in parallel. No external tuning devices are required. A fully differential inductor is contained on-chip. The capacitive portion of the frequency determining circuitry is made up of a binary weighted capacitor array and an analog voltage controlled varactor. The radio makes use of a Hybrid Phase Lock Loop (PLL) architecture. The coarse tuning is accomplished with the combination of Digital PLL/Binary capacitance array and the fine tuning is accomplished using the more conventional analog portion of the PLL. This use of coarse and fine tuning together reduces the analog VCO gain requirement. The reduction of tuning tolerance issues and noise are a direct effect of this type of PLL. Additionally, the characteristic impedance of the loop filter can be increased to reduce the charge pump current which helps in the integration of the active loop filter on-chip. This PLL also contains both integral and proportional charge pumps whose currents may be changed via register settings. This allows the loop parameters to be optimized for tuning speed and noise reduction.

The fractional-N synthesizer in this radio utilizes a unique Phase Interpolation Divider (PID) rather than the more conventional modulus divider architecture. The PID allows for very good frequency resolution and fast tuning speed. It also has the speed and power advantages of an asynchronous divider and is fully programmable within a restricted frequency range.

LSB

LSB

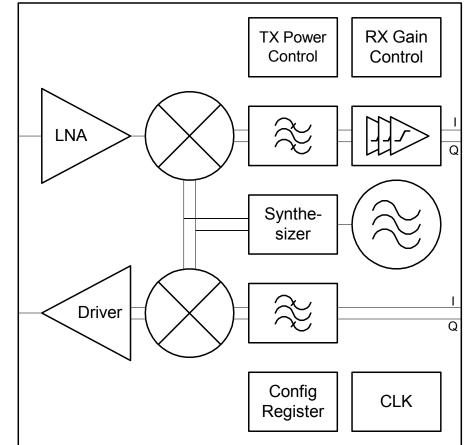

### **SPI Interface**

Serial peripheral interface SPI controls the transceiver. This 4-wire bus contains the ports SDE, SCL, SDI and SDO. The SPI has an 8-bit organization. Each transmission starts with a command byte with the following structure:

| MS | ЗB |      |      |      |      |      |      | LSB  |

|----|----|------|------|------|------|------|------|------|

| С  | MD | ADR6 | ADR5 | ADR4 | ADR3 | ADR2 | ADR1 | ADR0 |

The command bit CMD is set to "1" for WRITE operation and "0" for READ operation.

The transmission is continued with the data bytes. The number of data bytes depends on the register. The MSB of each data byte is send first.

For an 8 bit register:

MSB

| DATA |

|------|------|------|------|------|------|------|------|

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | Ο    |

| '    | 0    | 5    | Ŧ    | 5    | 2    | 1    | 0    |

For 16 bit register:

MSB

| DATA1<br>5 | DATA1<br>4 | DATA1<br>3 | DATA1<br>2 | DATA11 | DATA1<br>0 | DATA9 | DATA8 |

|------------|------------|------------|------------|--------|------------|-------|-------|

|            |            |            |            |        |            |       |       |

| DATA7      | DATA6      | DATA5      | DATA4      | DATA3  | DATA2      | DATA1 | DATA0 |

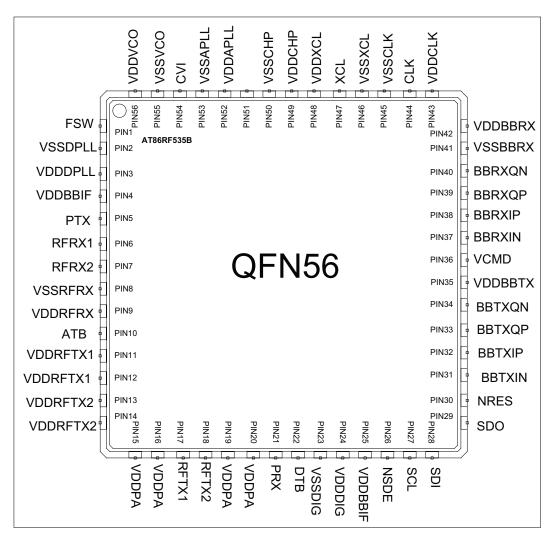

## Pin Description and Package Drawing

### Table 4. Pin Description

| Pin      | Pin No. | Description                                                                                                                                                                         |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FSW      | 1       | PLL Frequency Switch for HFDD Mode<br>Digital CMOS input levels                                                                                                                     |

| VSSDPLL  | 2       | Ground Supply of Digital PLL Modules                                                                                                                                                |

| VDDDPLL  | 3       | Voltage Supply of Digital PLL Modules                                                                                                                                               |

| VDDBBIF  | 4       | Supply Voltage of Digital Base Band Interface Pads                                                                                                                                  |

| PTX      | 5       | Power Switch Transmit Path<br>High active, digital CMOS input levels                                                                                                                |

| RFRX1    | 6       | RF Receive Input 1<br>Low noise amplifier input. The $50\Omega$ matching is in part by the bond/package inductance and an external<br>component (tbd).                              |

| RFRX2    | 7       | RF Receive Input 2<br>Complementary signal to RFRX1                                                                                                                                 |

| VSSRFRX  | 8       | Ground Supply of Radio Frequency Receive Circuit Modules                                                                                                                            |

| VDDRFRX  | 9       | Voltage Supply of Radio Frequency Receive Circuit Modules                                                                                                                           |

| ATB      | 10      | Analog Test Bus Analog IO<br>Analog output/input signal for testing purposes, connection configurable over SPI                                                                      |

| VDDRFTX1 | 11      | Voltage Supply of Radio Frequency Transmit Circuit Modules                                                                                                                          |

| VDDRFTX1 | 12      | Voltage Supply of Radio Frequency Transmit Circuit Module                                                                                                                           |

| VDDRFTX2 | 13      | Voltage Supply of Radio Frequency Transmit Circuit Modules                                                                                                                          |

| VDDRFTX2 | 14      | Voltage Supply of Radio Frequency Transmit Circuit Modules                                                                                                                          |

| VDDPA    | 15      | Voltage Supply of Power Amplifier Driving Module                                                                                                                                    |

| VDDPA    | 16      | Voltage Supply of Power Amplifier Driving Module                                                                                                                                    |

| RFTX1    | 17      | RF Transmit Output 1<br>P1dB up to +15dBm @ 50 $\Omega$ differential 3.5GHz. The 50 $\Omega$ matching is in part by the bond/package<br>inductance and an external component (tbd). |

| RFTX2    | 18      | RF Transmit Output 2<br>Complementary signal to RFTX1                                                                                                                               |

| VDDPA    | 19      | Voltage Supply of Power Amplifier Driving Module                                                                                                                                    |

| VDDPA    | 20      | Voltage Supply of Power Amplifier Driving Module                                                                                                                                    |

| PRX      | 21      | Power Switch of Receive Path<br>High active, digital CMOS input levels                                                                                                              |

| DTB      | 22      | Digital Test Bus Input/Output Digital<br>DTB input/output signal for testing purposes, connection and direction is configurable over SPI.                                           |

| VSSDIG   | 23      | Ground Supply SPI Interface Pads and of Digital Circuit Modules                                                                                                                     |

| VDDDIG   | 24      | Voltage Supply of Digital Circuit Modules                                                                                                                                           |

| VDDBBIF  | 25      | Voltage Supply of Digital Base Band Interface Pads                                                                                                                                  |

# AT86RF525B [Preliminary]

### Table 4. Pin Description

| Pin     | Pin No. | Description                                                                                                                                                                                                                                                                                                        |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NSDE    | 26      | SPI Enable Digital Input<br>The rising edge of SCL and a low SDE indicate the start of a data transmission to the SPI slave                                                                                                                                                                                        |

| SCL     | 27      | SPI Clock Digital Input<br>At every rising edge the SDI data is latched into the internal SPI register. SDO data change also on the<br>rising edge.                                                                                                                                                                |

| SDI     | 28      | SPI Data Digital Input<br>Serial SPI data input stream is started with SDE and contain first an address byte. Read in is MSB first.<br>The MSB of the address byte is the R/W control bit. After the address byte there follows a number of data<br>bytes. The actual number of data bytes depends on the address. |

| SDO     | 29      | SPI Data Digital Output                                                                                                                                                                                                                                                                                            |

| NRES    | 30      | Power On Reset<br>Low active, open drain output with internal 10k? pull up resistor                                                                                                                                                                                                                                |

| BBTXIN  | 31      | Base Band Transmit Input I Negative<br>Complementary signal to BBTXIP                                                                                                                                                                                                                                              |

| BBTXIP  | 32      | Base Band Transmit Input I Positive<br>Base band transmit input signal In Phase                                                                                                                                                                                                                                    |

| BBTXQP  | 33      | Base Band Transmit Input Q Positive<br>Complementary signal to BBTXQN                                                                                                                                                                                                                                              |

| BBTXQN  | 34      | Base Band Transmit Input Q Negative<br>Base band transmit input signal Quad Phase                                                                                                                                                                                                                                  |

| VDDBBTX | 35      | Voltage Supply of BB TX circuit modules                                                                                                                                                                                                                                                                            |

| VCMD    | 36      | Common Mode Voltage Bias Output<br>RX Elements DC output voltage 1.0V, only active if PRX=High                                                                                                                                                                                                                     |

| BBRXIN  | 37      | Base Band Receive Output I Negative<br>In Phase output negative. The base band-processed signal is level voltage programmable to adapt to<br>different base band ADCs. The capacitive load should be less than 10pF asymmetric                                                                                     |

| BBRXIP  | 38      | Base Band Receive Output I Positive<br>Complementary signal to BBRXIN                                                                                                                                                                                                                                              |

| BBRXQP  | 39      | Base Band Receive Output Q Positive<br>Quad Phase output positive. The base band-processed signal is level voltage programmable to adapt to<br>different base band ADCs. The capacitive load should be less than 10pF asymmetric.                                                                                  |

| BBRXQN  | 40      | Base Band Receive Output Q Negative<br>Complementary signal to BBRXQP                                                                                                                                                                                                                                              |

| VSSBBRX | 41      | Voltage Supply of BB Receive circuit modules                                                                                                                                                                                                                                                                       |

| VDDBBRX | 42      | Voltage Supply of BB Receive circuit modules                                                                                                                                                                                                                                                                       |

| VDDCLK  | 43      | Ground Supply of CMOS Clock Output Driver                                                                                                                                                                                                                                                                          |

| CLK     | 44      | 40MHz CMOS Clock Digital Output Driver                                                                                                                                                                                                                                                                             |

| VSSCLK  | 45      | Ground Supply of CMOS Clock Output Driver                                                                                                                                                                                                                                                                          |

| VSSXCL  | 46      | Ground Supply of Crystal Clock Input Buffer                                                                                                                                                                                                                                                                        |

| XCL     | 47      | Crystal Clock Input Buffer                                                                                                                                                                                                                                                                                         |

| VDDXCL  | 48      | Voltage Supply of Crystal Clock Input Buffer                                                                                                                                                                                                                                                                       |

5189A-WiMAX-9/07

### Table 4. Pin Description

| Pin     | Pin No. | Description                                                        |

|---------|---------|--------------------------------------------------------------------|

| VDDCHP  | 49      | Voltage Supply of Phase Frequency Detector and Charge Pump Modules |

| VSSCHP  | 50      | Ground Supply of Phase Frequency Detector and Charge Pump Modules  |

|         | 51      |                                                                    |

| VDDAPLL | 52      | Voltage Supply of PLL Analog Divider Modules                       |

| VSSAPLL | 53      | Ground Supply of PLL Analog Divider Modules                        |

| CVI     | 54      | VCO Control Voltage IO (Testpin)                                   |

| VSSVCO  | 55      | Ground Supply of Synthesizer modules VCO and APLF                  |

| VDDVCO  | 56      | Voltage Supply of Synthesizer modules VCO and APLF                 |

Note: Additional ground supplies are generated by down bonds to exposed paddle

#### Figure 3. Pin Information

### Package Drawing - 56MLI

## **Revision History**

| Doc. Rev. | Date   | Comments                  |

|-----------|--------|---------------------------|

| 5189A     | 9/2007 | Initial document release. |

#### Headquarters

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com Technical Support Wimax@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2007 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.