## Am79C850

## SUPERNET® 3

#### DISTINCTIVE CHARACTERISTICS

- Compliant with the ANSI X3T9.5/ISO 9314 specification

- 100 Mbps data rate

- Timed token-passing protocol

- Ring topology

- Complete memory management

- Supports 256K bytes of local frame buffer memory

- Supports buffer memory bandwidths of 200 Mbps and 400 Mbps

- Tag-Mode: minimum latency/highest performance buffer memory management, ideal for adapter card designs

- ANSI-compliant TP-PMD Stream Cipher Scrambling/Descrambling

- Full duplex operation: 200 Mbps continuous data rate

- Supports both fiber optic and copper twistedpair media

- Diagnostic features

- Built in Self Test (BIST) in Address Filter,

Physical Layer Controller with Scrambler

- Hardware Physical Connection Management support

- Low power consumption—reduction of more than 25% from SUPERNET 2 solution

## **FUNCTIONAL OVERVIEW**

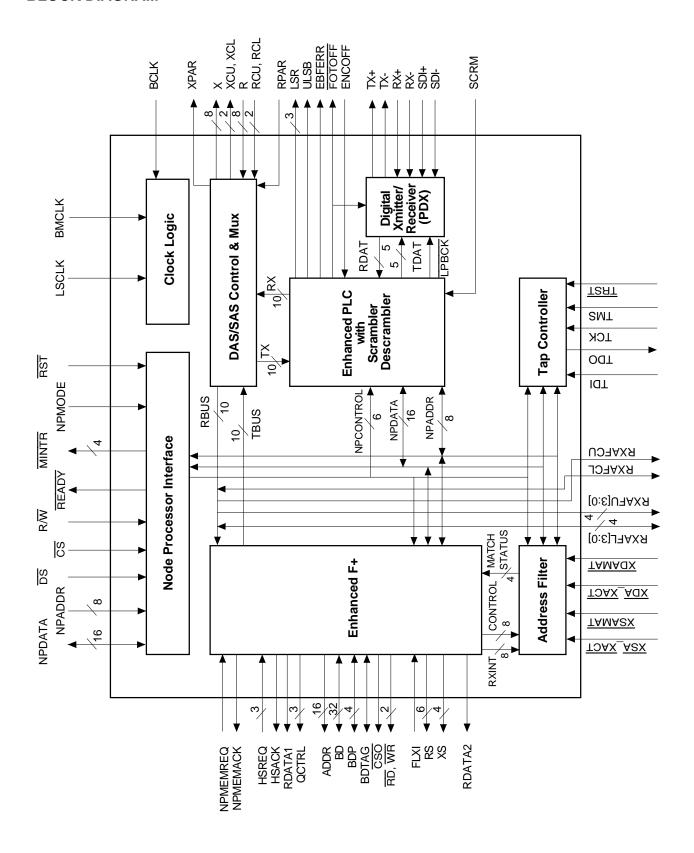

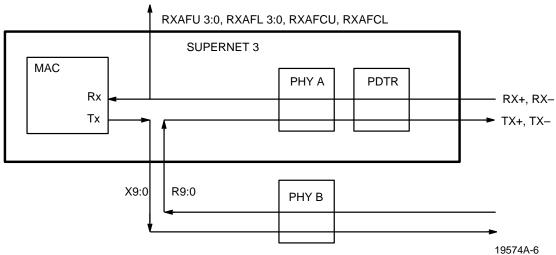

SUPERNET 3 is a 208-pin CMOS integration of FDDI MAC, PHY, Address Filter, and clock generation and recovery functions. It is the third generation FDDI offering from AMD which integrates the SUPERNET 2 family of chips into a single-chip solution. Refer to the SUPERNET 2 data book (PID 15502C) for basic feature descriptions.

The SUPERNET 3 is backward compatible to the SUPERNET 2 Tag Mode of operation in which the SUPERNET 3 buffer memory interface logic maintains the buffer memory as multiple FIFOs.

The SUPERNET 3 provides DMA channels, arbitrates access to the network buffer memory, and controls the data path between the buffer memory and the medium. The MAC also implements the timed-token protocol and receive/transmit control as specified for the Media Access Control (MAC) sublayer of the ISO standard 9314-2 for FDDI. The Physical Layer functions defined by the ISO 9314-1 are performed by the SUPERNET 3. SUPERNET 3 implements on-chip digital clock recovery and transmit functions for fiber. To support copper media, the PHY-PMD interface is maintained and an external module can be implemented in the same footprint as the fiber optic transceiver to perform the MLT-3 encoding/decoding and equalization. SUPERNET 3 integrates the scrambler and functions for transmissions descrambler copper media.

## **SUPERNET 3 FEATURES UPDATE**

The basic feature description for SUPERNET 3 is provided in the SUPERNET 2 data book. The enhanced features are as listed below:

- This is a CMOS integration of the redesigned FORMAC Plus, an enhanced PLC, a 32-entry address filter (AF, which is based on a Content Addressable Memory, or CAM, core), and a CMOS PDX core for clock and data recovery.

- A 32-entry, extensible and fully maskable AF allows additional individual and group addresses to be supported.

- The physical data transmitter and receiver (PDX) circuits are also embedded on-chip using proprietary digital clock-recovery technology.

- For the purposes of implementing copper PMD, the scrambler/descrambler functions are embedded within the chip.

- The Buffer Memory interface has been modified to support slower SRAM's (35 ns) without affecting backward compatibility with SUPERNET 2.

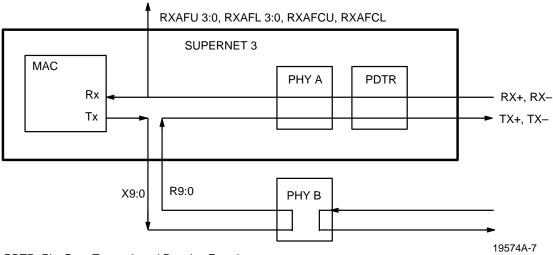

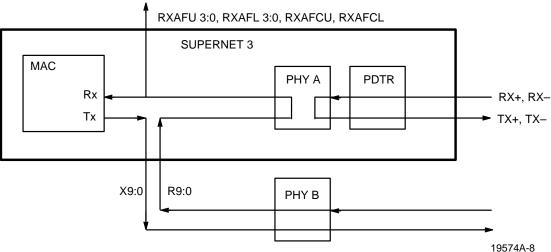

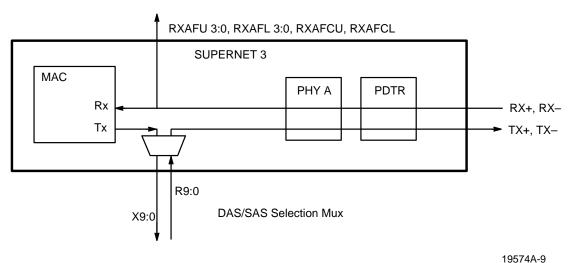

- SUPERNET 3 supports the FDDI single attachment station (SAS) but is capable of supporting a dual attachment station (DAS)

Publication# 19574 Rev. A Amendment /0 Issue Date: April 1995

- configurations with an external physical layer controller.

- SUPERNET 3 has a Test Access Port and Boundary Scan Architecture, IEEE1149.1.

- SUPERNET 3 provides Built-in Self Test (BIST) features for the Address Filter, and PLC-S.

- All registers are readable and writable by the Node Processor. All reserved bits shall be read back as zero except where noted.

- The Receive Status (RS) pins are expanded from 5 to 6 pins to support enhanced status reporting.

- The Transmit Status (XS) pins are expanded from 3 to 4 pins to support enhanced status reporting.

- Enhanced frame reception is possible by splitting the receive queue.

- Modified TAG Mode of operation for easy conversion from NON-TAG SUPERNET 2 to SUPERNET 3.

- All SUPERNET 3 registers will be initialized with a default value on reset.

- The A, C indicator setting has been modified. It is now possible to control the setting of the A, C indicators independent of the mode of operation (online, online special mode, and external loopback mode).

- Maskable 'vectored-interrupts' are provided. It is now possible to detect the event causing the interrupt in the SUPERNET 3 in two cycles by reading the vector register which gives the vector of the status register followed by a read of the appropriate status register.

- An additional mode register (MDREG3) is provided. Setting the bits in this mode register enables the additional SUPERNET 3 features.

## **BLOCK DIAGRAM**

## **Table of Contents**

| Distinctive Characteristics                     | 1  |

|-------------------------------------------------|----|

| Functional Overview                             | 1  |

| SUPERNET 3 Features Update                      | 1  |

| Block Diagram                                   | 3  |

| Connection Diagram                              | 7  |

| Ordering Information                            | 10 |

| Pin Description                                 | 11 |

| SUPERNET 2 Features not Supported               | 19 |

| Miscellaneous Changes from SUPERNET 2           |    |

| Explanation of Enhancements                     |    |

| Status Pins                                     |    |

| Slower Buffer Memory Interface                  |    |

| Clocking                                        |    |

| A, C Indicators                                 |    |

| Transmit Queues                                 |    |

| Non-Tag Mode of Operation No Longer Supported   |    |

| Modified TAG Mode Operation                     |    |

| Transmit Command                                |    |

| TDAT Loopback                                   |    |

| Mode Register 3 (MDREG3)                        |    |

| Address Space                                   |    |

| Interrupts                                      |    |

| Receive Flush/Transmit Inhibit pin FLXI (input) |    |

| Single Frame Receive Mode                       |    |

| Receive Queue Operation                         |    |

| Address Bit Swapping                            |    |

| Auto-Unlocking of Receive Queues                |    |

| Symbol Control                                  |    |

| Dual Attachment Station (DAS) Support           |    |

| Changes and Enhancements to PHY                 |    |

| Testability                                     |    |

| Summary of Changes to Status and Mode Registers |    |

| Status Register 3 (ST3U & ST3L)                 |    |

| Parity Generation and Checking                  |    |

| Node Processor Synchronous Mode Operation       |    |

| Address Filter (AF) Support                     |    |

| Introduction                                    |    |

| Function of the Address Filter                  |    |

| Node Processor Registers                        |    |

| MAC Interface                                   |    |

**SUPERNET 3**

4

## **Table of Contents (continued)**

| Address Filter Test Specification                                              |    |

|--------------------------------------------------------------------------------|----|

| Introduction                                                                   | 62 |

| Test Logic Description                                                         | 62 |

| Writing Entries into the AF                                                    | 65 |

| Finding Entries in the AF                                                      | 65 |

| Invalidating Entries in the AF                                                 | 65 |

| PDX Functional Description                                                     | 66 |

| Introduction                                                                   | 66 |

| Default Timer and Register Values                                              | 67 |

| SUPERNET 3 Registers                                                           | 69 |

| SUPERNET 3 Programmable Registers                                              | 69 |

| SUPERNET 3 Command Registers                                                   |    |

| SUPERNET 3 Command Registers 1                                                 | 75 |

| SUPERNET 3 Command Registers 2                                                 | 75 |

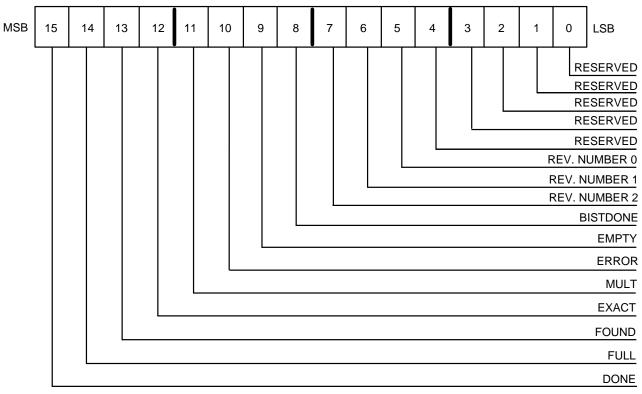

| Revision I.D                                                                   | 76 |

| Absolute Maximum Ratings                                                       | 77 |

| DC CHARACTERISTICS over operating ranges unless otherwise specified            | 77 |

| SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges                     | 79 |

| References                                                                     | 96 |

| PHY Device                                                                     | 96 |

| MAC Device                                                                     | 96 |

| Testability                                                                    | 96 |

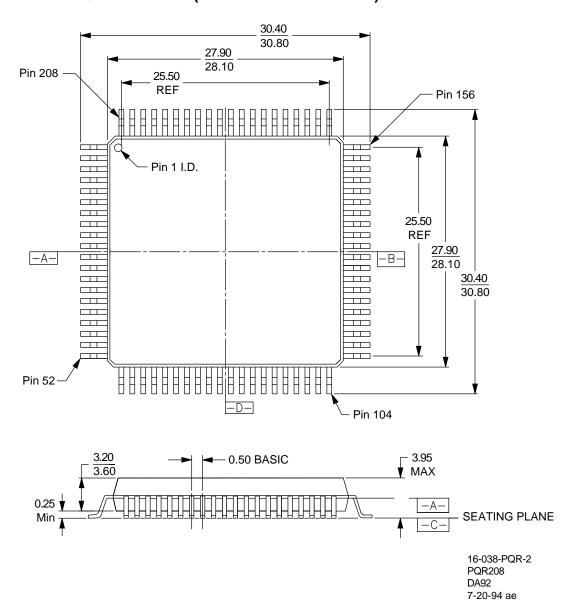

| Physical Dimensions                                                            | 97 |

| PQR208, Trimmed and Formed 208-Pin Plastic Quad Flat Pack (measured in inches) | 97 |

## List of Figures

| Figure 1.  | Memory Receive Queue (Modified TAG Mode)                | 24 |

|------------|---------------------------------------------------------|----|

| Figure 2.  | Register 3 (MDREG3)                                     | 26 |

| Figure 3.  | Frame Selection Register (FRSELREG)                     | 29 |

| Figure 4.  | Delay Register (UNLCKDLY)                               | 31 |

| Figure 5.  | THRU_A Configuration                                    | 32 |

| Figure 6.  | WRAP_A Configuration                                    | 32 |

| Figure 7.  | WRAP_B Configuration                                    | 33 |

| Figure 8.  | WRAP_S or SAS Configuration                             | 33 |

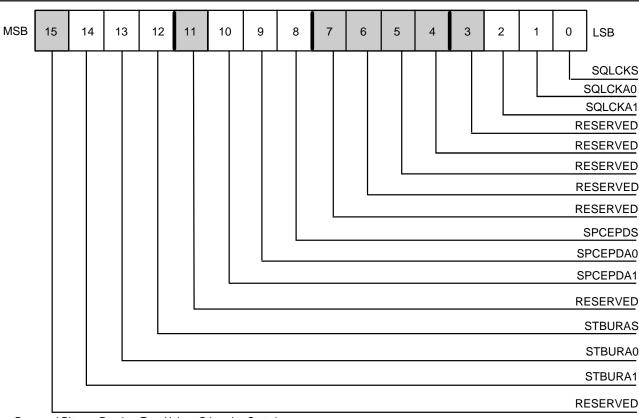

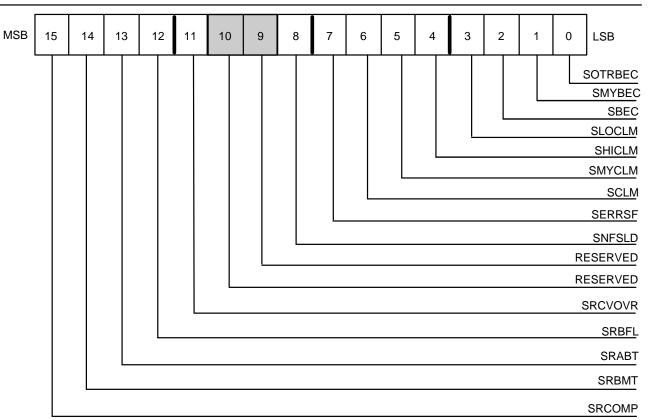

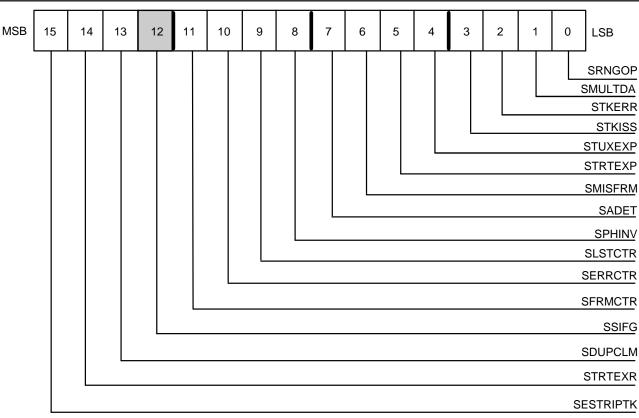

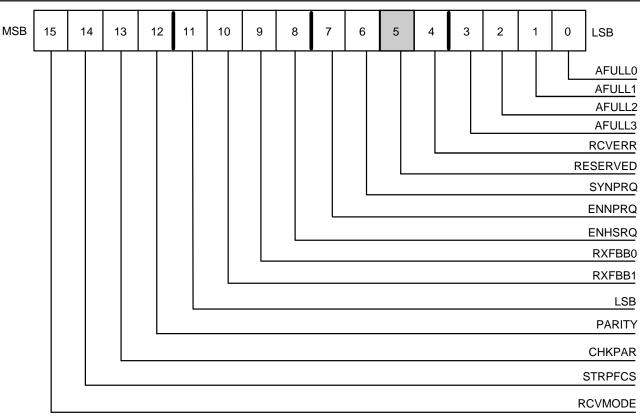

| Figure 9.  | Status Register 1 – Upper 16 Bits (ST1U) (NPADDR = 00h) | 41 |

| Figure 10. | Status Register 1 – Lower 16 Bits (ST1L) (NPADDR = 01h) | 41 |

| Figure 11. | Status Register 2 – Upper 16 Bits (ST2U) (NPADDR = 02h) | 42 |

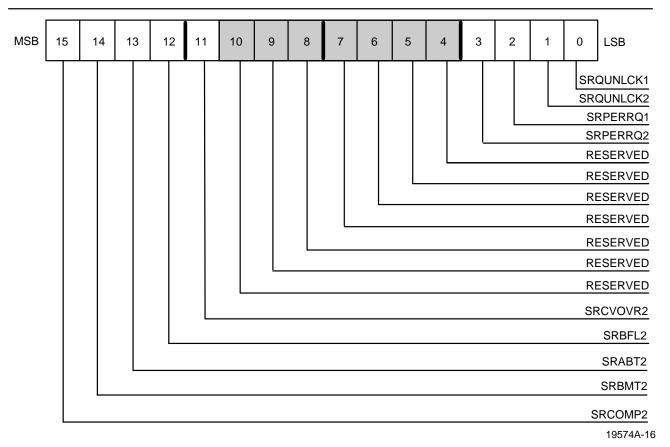

| Figure 12. | Status Register 2 – Lower 16 Bits (ST2L) (NPADDR = 03h) | 42 |

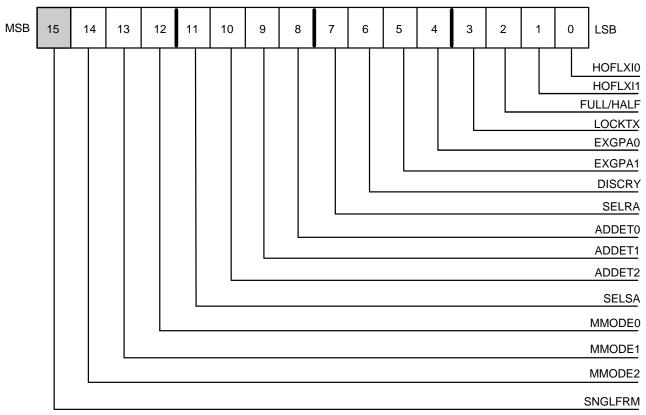

| Figure 13. | Mode Register 1 (MDREG1) (NPADDR = 10h)                 | 43 |

| Figure 14. | Mode Register 2 (MDREG2) (NPADDR = 20h)                 | 43 |

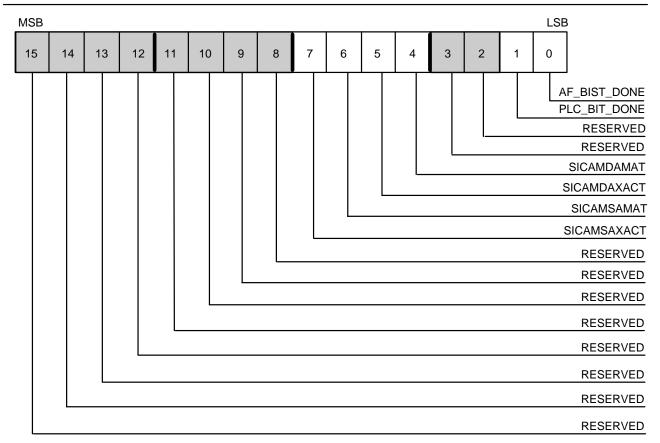

| Figure 15. | Status Register 3 – Upper 16 Bits (ST3U) (NPADDR = 61h) | 44 |

| Figure 16. | Status Register 3 – Lower 16 Bits (ST3L) (NPADDR = 62h) | 45 |

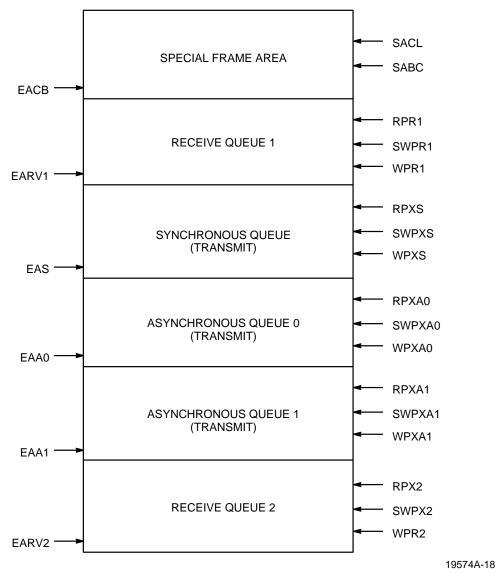

| Figure 17. | Buffer Memory Queue Organization                        | 47 |

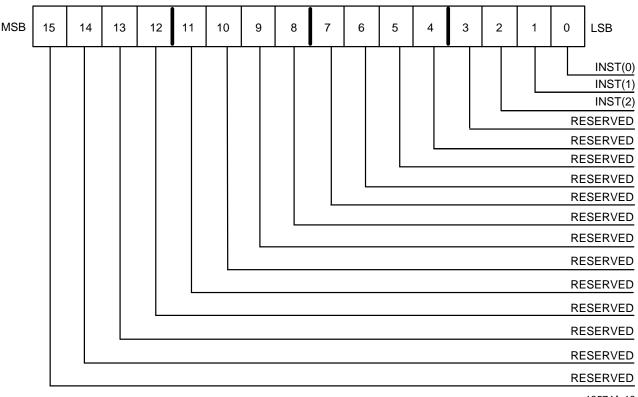

| Figure 18. | Command Register                                        | 50 |

| Figure 19. | Command Register                                        | 52 |

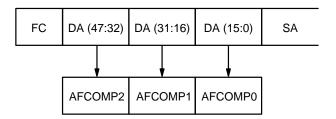

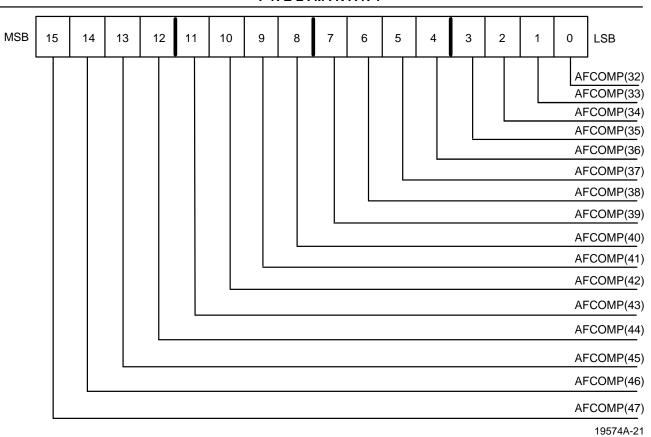

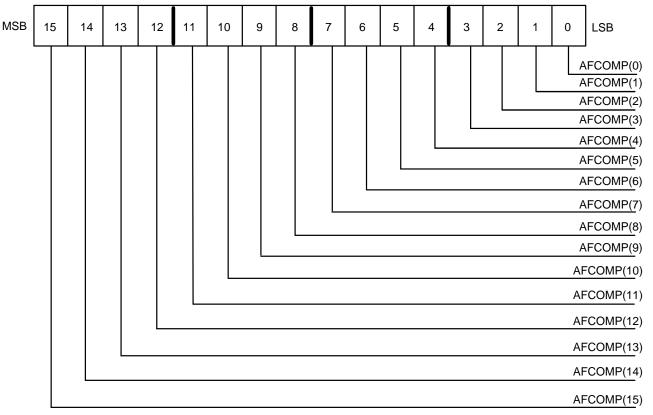

| Figure 20. | Node Processor Comparand Register (AFCOMP2)             | 54 |

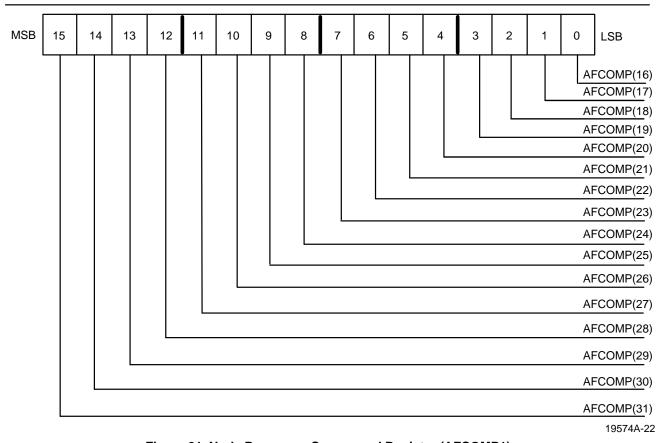

| Figure 21. | Node Processor Comparand Register (AFCOMP1)             | 54 |

| Figure 22. | Node Processor Comparand Register (AFCOMP0)             | 55 |

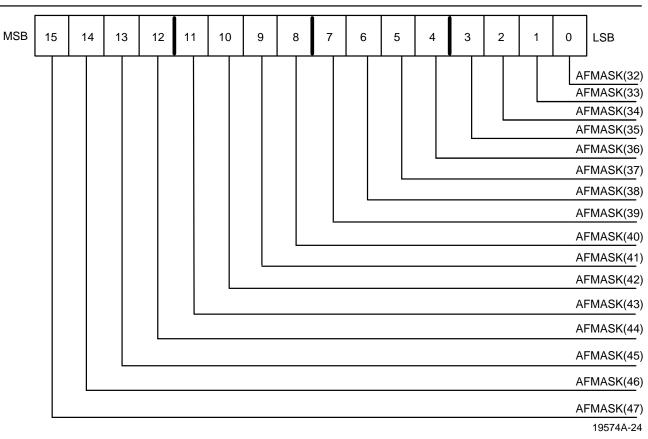

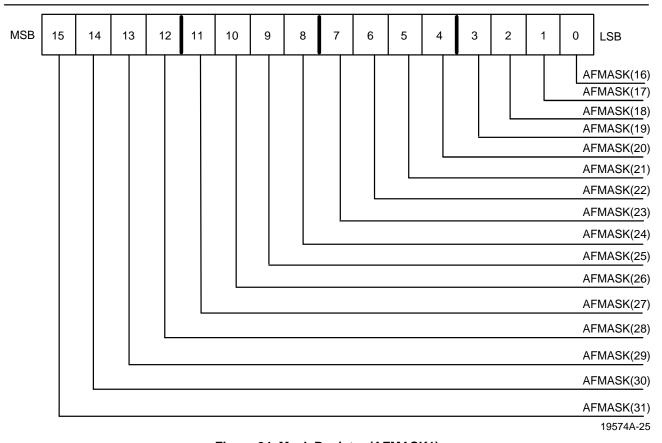

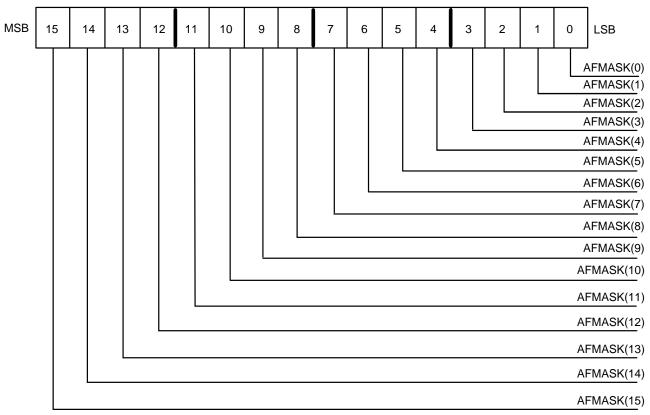

| Figure 23. | Mask Register (AFMASK2)                                 | 56 |

| Figure 24. | Mask Register (AFMASK1)                                 | 56 |

| Figure 25. | Mask Register (AFMASK0)                                 | 57 |

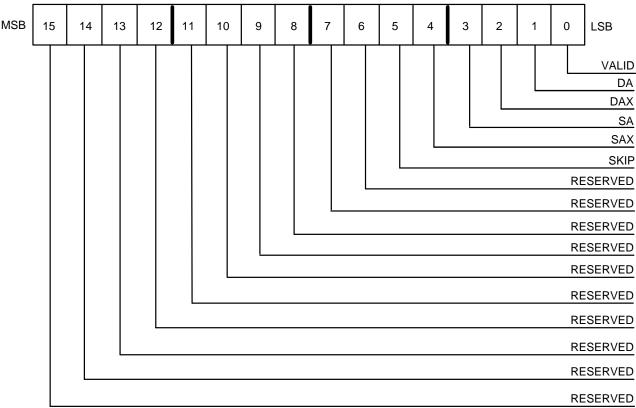

| Figure 26. | Personality Register                                    | 58 |

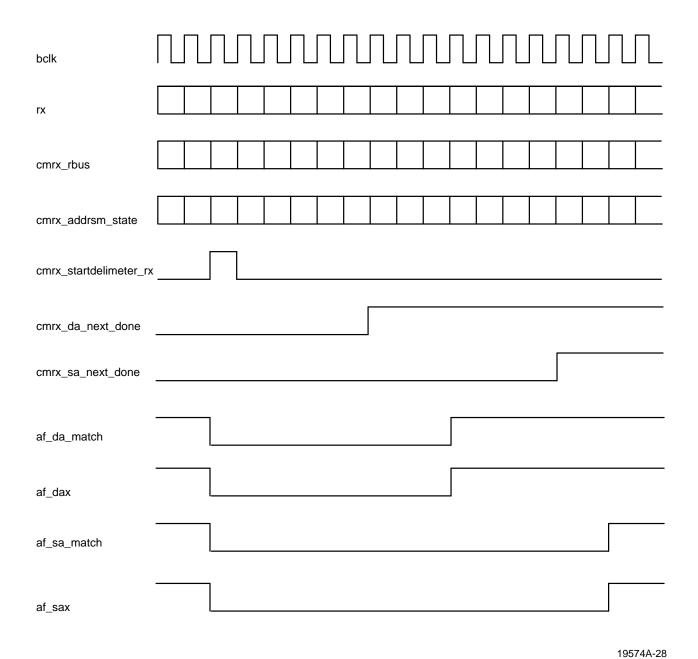

| Figure 27. | AF-MAC Interface Handshake                              | 60 |

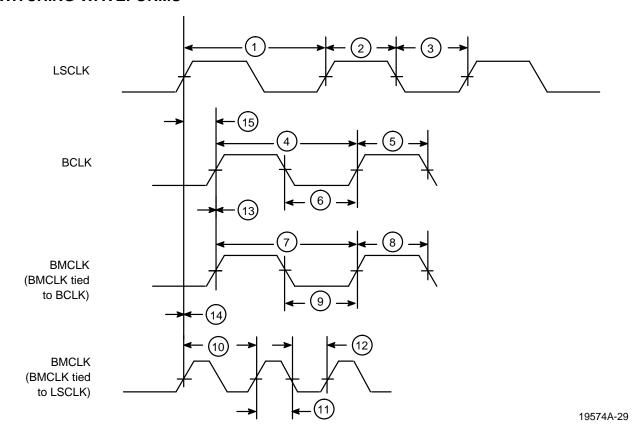

| Figure 28. | Clock Timings                                           | 78 |

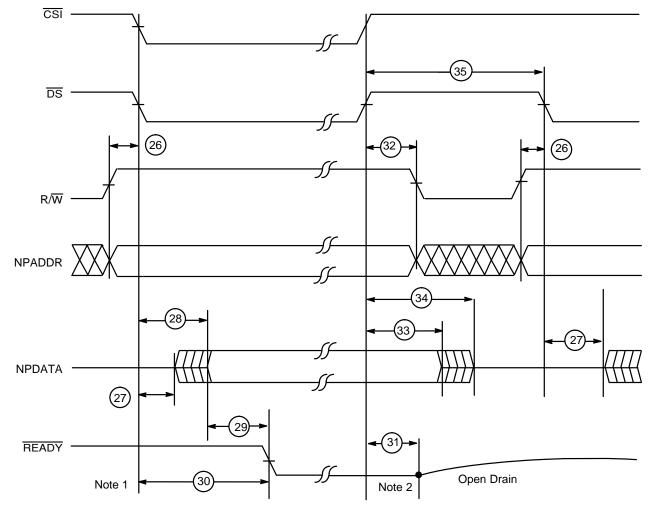

| Figure 29. | NP Asynchronous Read                                    | 80 |

| Figure 30. | NP Asynchronous Write                                   | 81 |

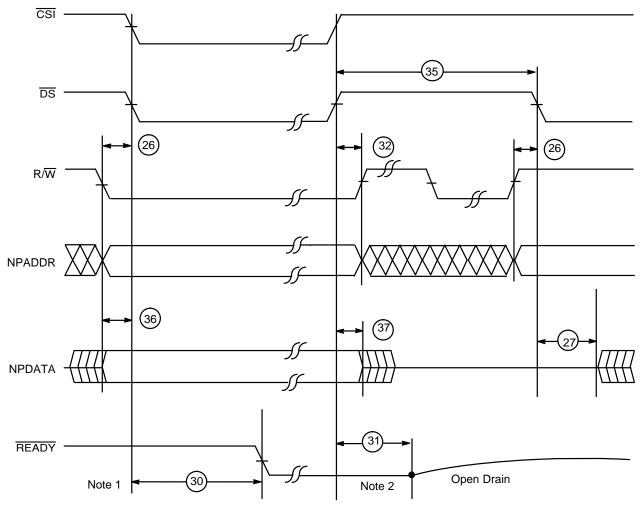

| Figure 31. | NP Synchronous Read and Write Except MDR Accesses       | 82 |

| Figure 32. | NP Synchronous Read and Write MDR Accesses              | 83 |

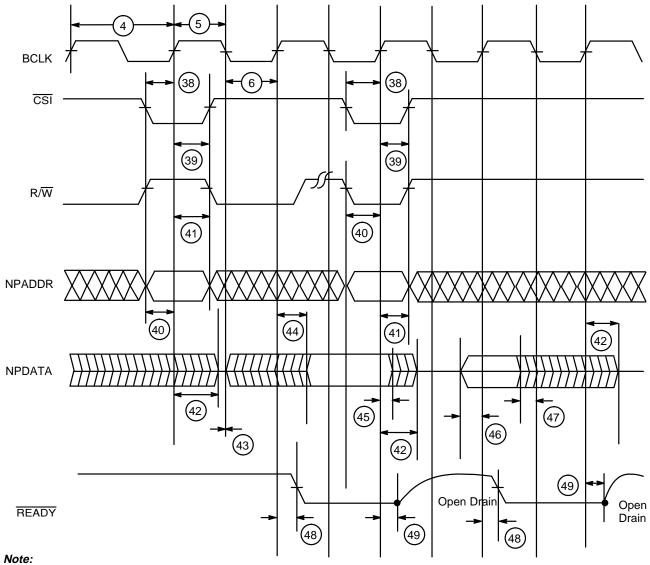

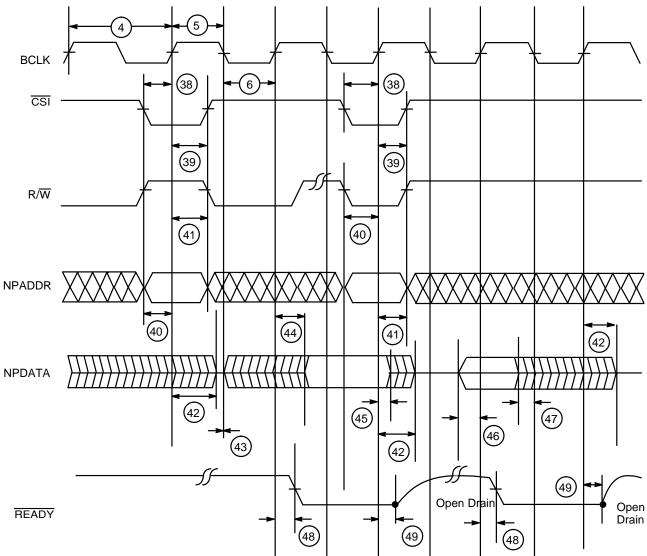

| Figure 33. | Host Interface Signal Timings                           | 84 |

| Figure 34. | NP DMA Signals                                          | 85 |

| Figure 35. | Host Interface Signal Timings                           | 87 |

| Figure 36. | Buffer Memory Read Cycle Timings                        | 88 |

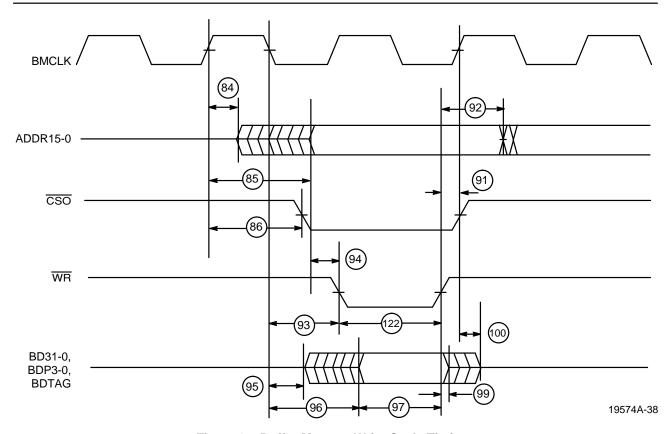

| Figure 37. | Buffer Memory Write Cycle Timings                       | 88 |

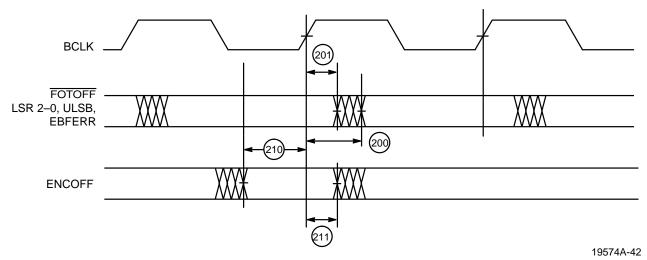

| Figure 38. | PHY Interface Timings                                   | 89 |

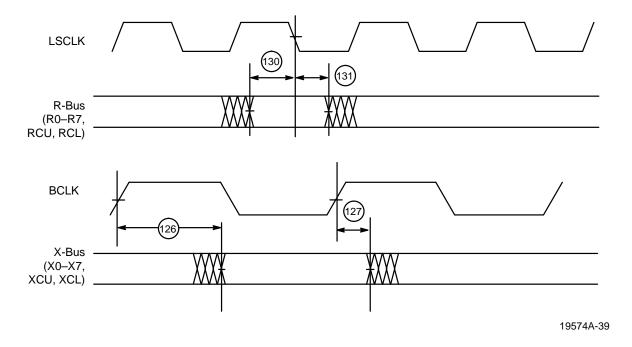

| Figure 39. | MAC Miscellaneous Signal Timings                        | 90 |

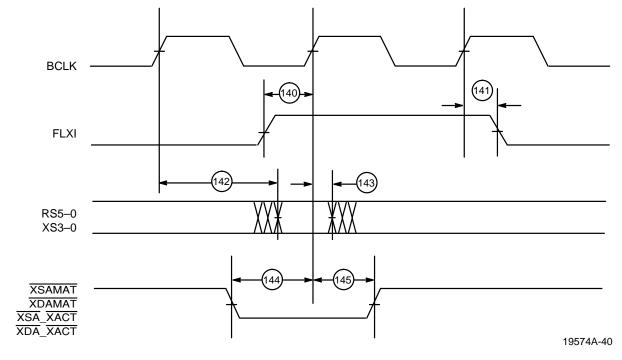

| Figure 40. | External CAM Interface Timings                          | 91 |

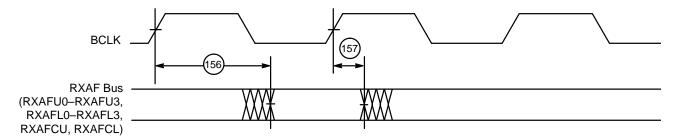

| Figure 41. | PHY Miscellaneous Signal Timings                        | 92 |

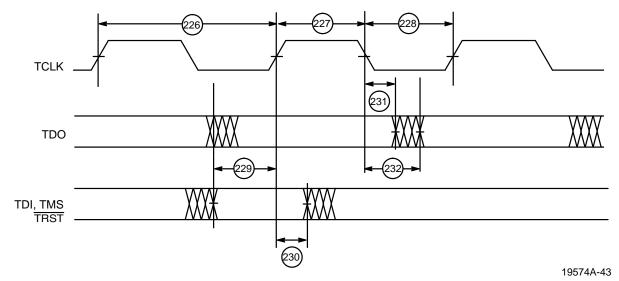

| Figure 42. | TEST Interface Signal Timings                           | 93 |

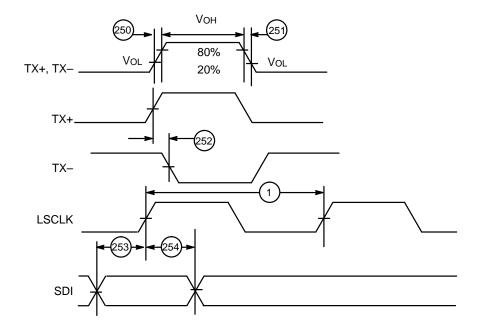

| Figure 43. | PMD Interface Signal Timings                            | 94 |

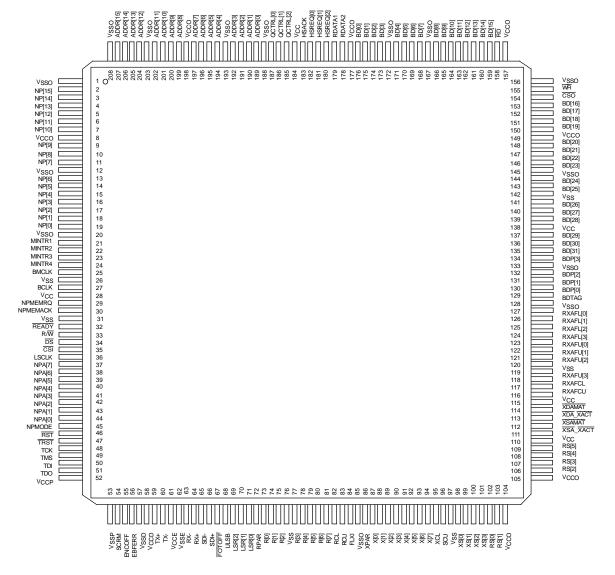

## **CONNECTION DIAGRAM**

208-Pin PQR (Top View)

19574A-1

## **PQFP PIN DESIGNATIONS**

## **Listed by Pin Number**

| Pin # | Description | Pin# | Description | Pin# | Description | Pin# | Description |

|-------|-------------|------|-------------|------|-------------|------|-------------|

| 1     | VSSO        | 35   | CSI         | 69   | LSR[2]      | 103  | RS[1]       |

| 2     | NP[15]      | 36   | LSCLK       | 70   | LSR[1]      | 104  | VCCO        |

| 3     | NP[14]      | 37   | NPA[7]      | 71   | LSR[0]      | 105  | VCCO        |

| 4     | NP[13]      | 38   | NPA[6]      | 72   | RPAR        | 106  | RS[2]       |

| 5     | NP[12]      | 39   | NPA[5]      | 73   | R[0]        | 107  | RS[3]       |

| 6     | NP[11]      | 40   | NPA[4]      | 74   | R[1]        | 108  | RS[4]       |

| 7     | NP[10]      | 41   | NPA[3]      | 75   | R[2]        | 109  | RS[5]       |

| 8     | VCCO        | 42   | NPA[2]      | 76   | VSS         | 110  | VCC         |

| 9     | NP[9]       | 43   | NPA[1]      | 77   | R[3]        | 111  | XSA_XACT    |

| 10    | NP[8]       | 44   | NPA[0]      | 78   | R[4]        | 112  | XSAMAT      |

| 11    | NP[7]       | 45   | NPMODE      | 79   | R[5]        | 113  | XDA_XACT    |

| 12    | VSSO        | 46   | RST         | 80   | R[6]        | 114  | XDAMAT      |

| 13    | NP[6]       | 47   | TRST        | 81   | R[7]        | 115  | VCC         |

| 14    | NP[5]       | 48   | TCK         | 82   | RCL         | 116  | RXAFCU      |

| 15    | NP[4]       | 49   | TMS         | 83   | RCU         | 117  | RXAFCL      |

| 16    | NP[3]       | 50   | TDI         | 84   | FLXI        | 118  | RXAFU[3]    |

| 17    | NP[2]       | 51   | TDO         | 85   | VSSO        | 119  | VSS         |

| 18    | NP[1]       | 52   | VCCP        | 86   | XPAR        | 120  | RXAFU[2]    |

| 19    | NP[0]       | 53   | VSSP        | 87   | X[0]        | 121  | RXAFU[1]    |

| 20    | VSSO        | 54   | SCRM        | 88   | X[1]        | 122  | RXAFU[0]    |

| 21    | MINTR1      | 55   | ENCOFF      | 89   | X[2]        | 123  | RXAFL[3]    |

| 22    | MINTR2      | 56   | EBFERR      | 90   | X[3]        | 124  | RXAFL[2]    |

| 23    | MINTR3      | 57   | VSSD        | 91   | X[4]        | 125  | RXAFL[1]    |

| 24    | MINTR4      | 58   | VCCD        | 92   | X[5]        | 126  | RXAFL[0]    |

| 25    | BMCLK       | 59   | TX+         | 93   | X[6]        | 127  | VSSO        |

| 26    | VSS         | 60   | TX-         | 94   | X[7]        | 128  | BDTAG       |

| 27    | BCLK        | 61   | VCCE        | 95   | XCL         | 129  | BDP[0]      |

| 28    | VCC         | 62   | VSSE        | 96   | XCU         | 130  | BDP[1]      |

| 29    | NPMEMRQ     | 63   | RX-         | 97   | VSS         | 131  | BDP[2]      |

| 30    | NPMEMACK    | 64   | RX+         | 98   | XS[0]       | 132  | VSSO        |

| 31    | VSS         | 65   | SDI-        | 99   | XS[1]       | 133  | BDP[3]      |

| 32    | READY       | 66   | SDI+        | 100  | XS[2]       | 134  | BD[31]      |

| 33    | R/W         | 67   | FOTOFF      | 101  | XS[3]       | 135  | BD[30]      |

| 34    | DS          | 68   | ULSB        | 102  | RS[0]       | 136  | BD[29]      |

## PQFP PIN DESIGNATIONS

## Listed by Pin Number

| Pin # | Description | Pin# | Description     | Pin # | Description | Pin# | Description |

|-------|-------------|------|-----------------|-------|-------------|------|-------------|

| 137   | VCC         | 155  | $\overline{WR}$ | 173   | BD[3]       | 191  | ADDR[2]     |

| 138   | BD[28]      | 156  | VSSO            | 174   | BD[2]       | 192  | ADDR[3]     |

| 139   | BD[27]      | 157  | VCCO            | 175   | BD[1]       | 193  | VSSO        |

| 140   | BD[26]      | 158  | RD              | 176   | BD[0]       | 194  | ADDR[4]     |

| 141   | VSS         | 159  | BD[15]          | 177   | VCCO        | 195  | ADDR[5]     |

| 142   | BD[25]      | 160  | BD[14]          | 178   | RDATA2      | 196  | ADDR[6]     |

| 143   | BD[24]      | 161  | BD[13]          | 179   | RDATA1      | 197  | ADDR[7]     |

| 144   | VSSO        | 162  | BD[12]          | 180   | HSREQ[2]    | 198  | VCCO        |

| 145   | BD[23]      | 163  | BD[11]          | 181   | HSREQ[1]    | 199  | ADDR[8]     |

| 146   | BD[22]      | 164  | BD[10]          | 182   | HSREQ[0]    | 200  | ADDR[9]     |

| 147   | BD[21]      | 165  | BD[9]           | 183   | HSACK       | 201  | ADDR[10]    |

| 148   | BD[20]      | 166  | BD[8]           | 184   | VCC         | 202  | ADDR[11]    |

| 149   | VCCO        | 167  | VSSO            | 185   | QCTRL[2]    | 203  | VSSO        |

| 150   | BD[19]      | 168  | BD[7]           | 186   | QCTRL[1]    | 204  | ADDR[12]    |

| 151   | BD[18]      | 169  | BD[6]           | 187   | QCTRL[0]    | 205  | ADDR[13]    |

| 152   | BD[17]      | 170  | BD[5]           | 188   | VSSO        | 206  | ADDR[14]    |

| 153   | BD[16]      | 171  | BD[4]           | 189   | ADDR[0]     | 207  | ADDR[15]    |

| 154   | CSO         | 172  | VSSO            | 190   | ADDR[1]     | 208  | VSSO        |

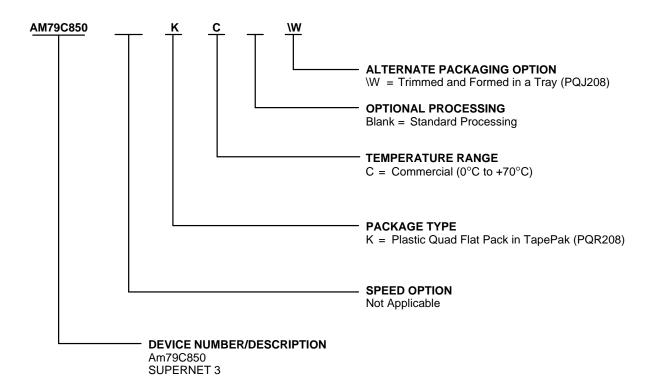

## **ORDERING INFORMATION**

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |          |  |  |  |  |

|--------------------|----------|--|--|--|--|

| AM79C850           | KC, KC\W |  |  |  |  |

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### PIN DESCRIPTION

I/O pins can only be high impedance in Test Access Port (TAP) operation. Refer to TAP Testability section.

## PHY/PMD Interface (46 Pins)

### RX+. RX-

## **Receive Data (PECL Input)**

These pins receive differential NRZI data.

## TX+, TX-

### **Transmit Data (PECL Output)**

These transmit outputs carry differential NRZI data. They can be forced to logical 0 (TX+LOW, TX-HIGH) by asserting the FOTOFF input.

#### **RCU**

### **Receive Control Upper (TTL input)**

RCU is asserted high to indicate that the upper nibble of the R bus (R7–4) is a network control character. When RCU is low, this nibble contains data. RCU is synchronous to BCLK. This pin has internal pull-up.

## **RCL**

## Receive Control Lower (TTL input)

RCL is asserted high to indicate that the lower nibble of the R bus (R3–0) is a network control character. When RCL is low, this nibble contains data. RCL is synchronous to BCLK. This pin has internal pull-up.

## R7-0

## Receive Bus (TTL input)

The R bus is used to receive information from the external physical layer (PHY) device. Bytes clocked from the physical layer (PHY) into the SUPERNET 3 R-bus input are synchronous to the BCLK. These pins have internal pull-up.

#### **RPAR**

#### Receive parity (TTL input)

RPAR is an input signal used to enhance error detection on the external PHY interface R7:0 bus. RPAR is an input signal used to implement even parity checking on R bus. If there is an odd number of 1's on {R7:0, RCU, RCL}, then RPAR should be 1 and if there is an even number of 1's on {R7:0, RCU, RCL} then RPAR should be 0. This pin has internal pull-up.

#### RXAFU3-0

## Receive Bus Tap for External AF (TTL output, high impedance)

The internal MAC Receive bus lines upper nibble are tapped and brought out as the RXAFU 3–0 pins. These pins are used by an external AF to do external SA and/or DA match.

#### RXAFL3-0

## Receive Bus Tap for External AF (TTL output, TTL input, high impedance)

The internal MAC Receive bus lines lower nibble are tapped and brought out as the RXAFL 3–0 pins. These pins are used by an external AF to do external SA and/or DA match.

**Note:** The RXAFL[3:0] input pins are for diagnostic purposes only.

#### RXAFCU

## Control Upper for AF Receive Bus (TTL output, high impedance)

The RXAFCU output signal is used to flag control symbols being presented on the nibble (3:0) of the RXAFU bus. This signal is synchronous to BCLK. If RXAFCU is asserted high, the nibble on the RXAFU bus is interpreted as a network control character. Otherwise, it is interpreted as a data nibble.

#### RXAFCL

## Control Lower for AF Receive Bus (TTL output, TTL input, high impedance)

The RXAFCL output signal is used to flag control symbols being presented on the nibble (3:0) of the RXAFL bus. This signal is synchronous to BCLK. If RXAFCL is asserted high, the nibble on the RXAFL bus is interpreted as a network control character. Otherwise, it is interpreted as a data nibble.

**Note:** The RXAFCL input is for diagnostic purposes only.

#### X7-0

## Transmit Bus (TTL output, high impedance)

This eight-bit output bus is used to send control and data information to the external physical layer (PHY) device to be transmitted over the medium. Information on the X-bus output is synchronous to the BCLK.

#### **XPAR**

### Transmit parity (TTL output, high impedance)

XPAR is an output signal used to enhance error detection on the MAC—external PHY interface X7:0 bus. If there is an odd number of 1's on {X7:0, XCU, XCL}, then XPAR should be 1 and if there is an even number of 1's on {X7:0, XCU, XCL} then XPAR should be 0.

### XCU

## Transmit Control Upper (TTL output, high impedance)

The XCU output signal is used to flag control symbols being presented on the upper nibble of the transmit bus. This signal is synchronous to BCLK. If XCU is asserted

SUPERNET 3 11

high, the upper nibble of the X-bus is interpreted as a network control character. Otherwise, it is interpreted as a data nibble.

#### **XCL**

## Transmit Control Lower (TTL output, high impedance)

The XCL output signal is used to flag control symbols being presented on the lower nibble of the transmit bus. This signal is synchronous to BCLK. If XCL is asserted high, the lower nibble of the X-bus is interpreted as a network control character. Otherwise, it is interpreted as a data nibble.

### **FOTOFF**

## Fiber Optic Transmitter Off (TTL Output, Active Low, high impedance)

The FOTOFF signal, when asserted, causes the optical transmitter to turn off.

## SDI+, SDI-

## Signal Detect (PECL Differential Line Receiver Inputs)

The SDI input signal pair is from the optical or copper transceivers to indicate whether the received optical or electrical signal is above its threshold. The inverted value of this signal is held in the PHY\_STATUS\_A register, and the LSDO interrupt bit in the PHY is set whenever SDI becomes asserted.

#### SCRM

## Scrambler/Descrambler enable (DC Input, Active High)

When this pin is strapped high, the SUPERNET 3 is set to operate with a copper PMD and the scrambler/descrambler is enabled. When the pin is strapped to ground, then the scrambler/descrambler function is disabled in the SUPERNET 3, and the SUPERNET 3 is set to operate with a fiber PMD. This pin is ORed with the bit 0 (CIPHER\_ENABLE) in the PLC\_CNTRL\_C register and the result is indicated in the same bit (bit 0). The PMD selection and scrambler/descrambler (S/D) enabling is as follows:

| SCRM<br>pin | CIPHER_<br>ENABLE<br>bit | Result                   |

|-------------|--------------------------|--------------------------|

| Low         | Reset                    | Fiber PMD. S/D disabled. |

| Low         | Set                      | Copper PMD. S/D enabled. |

| High        | Reset                    | Copper PMD. S/D enabled. |

| High        | Set                      | Copper PMD. S/D enabled. |

#### LSR 2-0

#### Line State Register (TTL Output, high impedance)

The LSR2-0 signals directly output the LINE\_ST field of the PLC\_STATUS\_A register to ring test and monitor equipment.

#### **EBFERR**

## Elasticity Buffer Error (TTL Output, Active High, high impedance)

EBFERR indicates when an overflow or underflow condition occurs in the Elasticity Buffer.

#### **ENCOFF**

## **Encoder Off (TTL Input, Active High)**

ENCOFF signal turns off the 4B/5B encoding and decoding function of the PLC core.

#### ULSB

### **Unknown Line State (TTL Output, high impedance)**

The ULSB signal directly outputs the UNKN\_LINE\_ST bit of the PLC\_STATUS\_A register to ring test and monitor equipment.

## Clock Pins (3 Pins)

### LSCLK

### Local Symbol Clock pin (TTL input)

The LSCLK is a 25 MHz clock. It is used by the PLC core.

#### **BCLK**

## Byte Clock pin (TTL input)

The BCLK is a 12.5 MHz clock. It is used by the PLC and the MAC cores.

#### **BMCLK**

#### **Buffer Memory Clock pin (TTL input)**

The BMCLK is the clock signal that the MAC core uses for generating the signals to the buffer memory. BMCLK is driven with either a 12.5 or 25 MHz clock signal. If 12.5 MHz operation is desired, then this pin can be tied to BCLK pin. If 25 MHz operation is desired, then this pin can be tied to LSCLK pin.

# Node Processor (NP) Interface (35 Pins)

The following paragraphs describe the pins used to interface the SUPERNET 3 with the node processor (NP) or other control devices. The NP interface is used for initializing the SUPERNET 3 as well as for reporting status.

#### CS

## **Chip Select Input (TTL input, active low)**

- Asynchronous when NPMODE = 0

- Synchronous when NPMODE = 1

The Chip Select Input (active low) enables Read and Write operations to the SUPERNET 3. In the asynchronous mode, the data output is enabled while  $\overline{CSI}$  and  $\overline{DS}$  are both low and  $R/\overline{W}$  is high. In the synchronous mode, the data output is enabled while  $\overline{CSI}$  is low and  $R/\overline{W}$  is high.

#### $\overline{DS}$

### Data Strobe/ (TTL input, active low)

- Asynchronous when NPMODE = 0

- Synchronous when NPMODE = 1

The  $\overline{\rm DS}$  input (active low) is used in the handshake between the NP and SUPERNET 3 when the SUPERNET 3 acts as bus slave during register accesses. In the asynchronous mode, this input signal is set by the node processor to transfer data between the NP and the SUPERNET 3. The direction of the data transfer is dictated by the logic level of the  $R/\overline{W}$  line. The NP sets  $\overline{\rm DS}$  low to initiate a data transfer.  $\overline{\rm DS}$  is not used in the synchronous mode. The chip-select input ( $\overline{\rm CSI}$ ) must be low while  $\overline{\rm DS}$  is low in order to start an NP bus transaction.

#### NPADDR7-0

#### NP Address Bus (TTL input)

The NPADDR7–0 input lines allow direct access to SUPERNET 3 internal registers. In addition, these lines are used to place SUPERNET 3 into different operating states.

The NPADDR bus of the SUPERNET 3 performs two control functions. First, the input on NPADDR7–0 acts as an address, selecting the proper internal register for a read or write operation that is controlled by the  $R/\overline{W}$  pin. The data is either read onto or loaded from the 16-bit NP bus. For a discussion of the results of read and load instructions, see the section under Programming the FORMAC Plus in the SUPERNET 2 data book. Second, instructions or commands can be issued to SUPERNET 3 by using the NPADDR bus.

#### NPDATA15-0

## NP Data Bus (TTL input, TTL output, high impedance)

The NP data bus is a 16-bit wide bidirectional data bus used to interface the SUPERNET 3 to the node processor. Data transfer on the NP data bus can be synchronous or asynchronous depending upon the setting of the NPMODE pin. For asynchronous operation, a two-wire handshake is provided through the READY and data-strobe (DS) lines.

## **NPMODE**

### NP Bus Mode (TTL input)

The level on the NPMODE pin defines the type of NP-bus interface with the SUPERNET 3. When NPMODE is strapped high, the NP interface operates synchronously with BCLK. When NPMODE is strapped low, asynchronous interface operation is selected.

#### **READY**

## Ready (TTL output, open drain, active low, high impedance)

In asynchronous mode, the  $\overline{READY}$  output (active low) is used in the handshake between the NP and SUPERNET 3. The SUPERNET 3  $\overline{READY}$  output provides an asynchronous acknowledgment to the NP that data transfer is complete. The SUPERNET 3 asserts  $\overline{READY}$  when it has put the data onto the NP bus during a read cycle, or when it has taken the data from the NP bus during a write cycle.  $\overline{READY}$  is a response to the  $\overline{CSI}$  and  $\overline{DS}$  inputs, and returns high after the  $\overline{CSI}$  or  $\overline{DS}$  signals go high.

In the synchronous mode, the READY line goes active on the BCLK edge when CSI and DS are active. READY goes inactive on the following BCLK edge. In the case of loading/reading of the MDR (memory data register), READY goes active on the BCLK edge after the completion of any pending data transfer from/to buffer memory.

## R/W

### Read/Write Select (TTL input)

The R/ $\overline{W}$  line is used to select the type of access (i.e., read or write) between the SUPERNET 3 and the NP. If R/ $\overline{W}$  is high, data is read from the SUPERNET 3 to the NP. If R/ $\overline{W}$  is low, the data flow is from the NP to the SUPERNET 3.

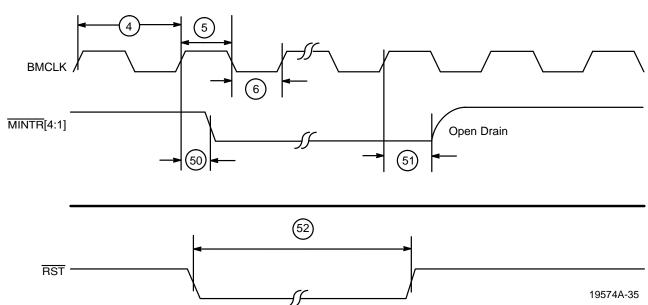

#### MINTR<sub>1</sub>

## Maskable Interrupt 1 (TTL output, open drain, high impedance)

The MINTR1 output (active low) is an attention line to the NP. MINTR1, when active, indicates an interrupt due to one or more unmasked flags in status register 1. In general, the active state of MINTR1 indicates that an unmasked interrupt condition or a transmit condition has occurred. MINTR1 is deactivated once either the lower or upper 16 bits of status register 1 (ST1L or ST1U) are read. Once MINTR1 is asserted, all 32 bits of status register 1 must be read to enable any future interrupt on this pin.

## MINTR2

## Maskable Interrupt 2 (TTL output, open drain, high impedance)

The MINTR2 output (active low) is an attention line to the NP. MINTR2, when active, indicates an interrupt due to one or more unmasked flags in status register 2. In general, the active state of MINTR2 indicates that an unmasked interrupt condition, a receive condition, or a

change in ring status has occurred. MINTR2 is deactivated once either the lower or upper 16 bits of status register 2 (ST2L or ST2U) are read. Once MINTR2 is asserted, all 32 bits of status register 2 must be read in order to enable any future interrupt on this pin.

#### MINTR3

## Maskable Interrupt 3 (TTL output, open drain, high impedance)

The MINTR3 output (active low) is an attention line to the NP. MINTR3, when active, indicates an interrupt due to one or more unmasked flags in status register 3. In general, the active state of MINTR3 indicates that an unmasked interrupt condition, a receive condition in the second receive queue has occurred. MINTR3 is deactivated once either the lower or upper 16 bits of status register 3 (ST3L or ST3U) are read. Once MINTR3 is asserted, all 32 bits of status register 3 must be read in order to enable any future interrupt on this pin.

#### **MINTR4**

## Maskable Interrupt 4 (TTL output, open drain, high impedance)

The MINTR4 output (active low) is an attention line to the NP. MINTR4, when active, indicates an interrupt due to one or more unmasked flags in the PHY interrupt event (INTR\_EVENT) register. In general, the active state of MINTR4 indicates that a change in PCM state machine or timer expiration or counter overflow has occurred. MINTR4 remains active until cleared by reading the INTR\_EVENT register.

When the MENSNGLINT (MDREG 3, bit 10) is set, the SUPERNET 3 generates only one interrupt (MINTR4) and the other interrupt lines (MINTR1, MINTR2, and MINTR3) are not toggled. The SUPERNET 3 operates in a vectored interrupt mode, i.e., a vector register is read to determine which status register is the source of the interrupt.

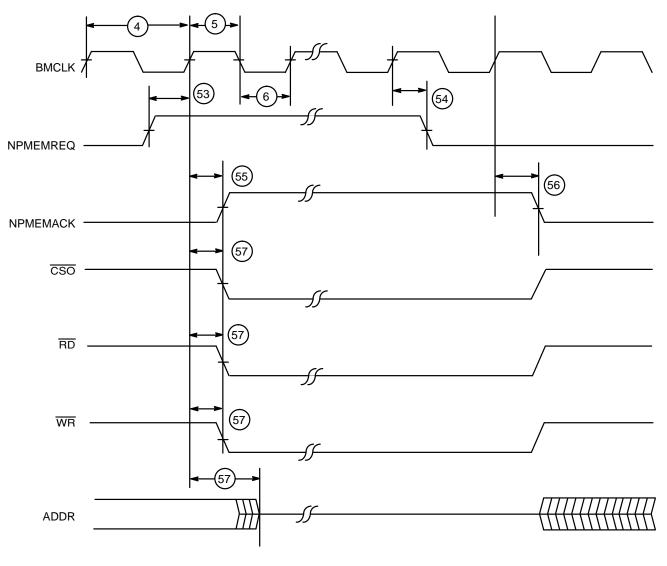

#### **NPMEMRQ**

### **Node Processor Memory Request (TTL input)**

The input signal NPMEMRQ is a request by the node processor to obtain control of buffer memory.

### **NPMEMACK**

## Node Processor Memory Access Acknowledge (TTL output, high impedance)

This signal indicates that an NPMEMRQ has been granted and that the  $\frac{NP}{RD}$ ,  $\frac{NP}{RD}$ ,  $\frac{NP}{RD}$ ,  $\frac{NP}{RD}$ ,  $\frac{NP}{RD}$ ,  $\frac{NP}{RD}$ ,  $\frac{NP}{RD}$ , and BDTAG). If NPMEMACK is forced low while NPMEMRQ is active (due to a higher priority request), the NP must release control of the bus within two BMCLK periods after the NPMEMACK line goes inactive.

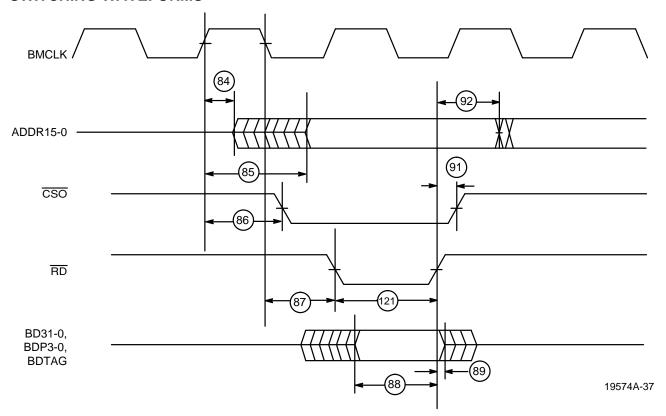

# **SUPERNET 3/Buffer Memory Interface** (56 Pins)

## **ADDR15-0**

## **Buffer Memory Address (TTL output, high impedance)**

The 16-bit ADDR-bus provides the addresses that access the buffer memory. The address selection depends on the result of bus arbitration in the SUPERNET 3. Each memory access lasts for two BMCLK clock cycles and the address is valid for both of these cycles. When buffer memory control has been released to the NP, the ADDR bus is in the high-impedance state.

**Note:** As long as the use of the buffer memory has not been granted to the node processor or host (HSACK and NPMEMACK not active), the SUPERNET 3 may drive the address lines even though no control signals are active.

#### **BD31-0**

## **Buffer Memory Data Bus (TTL input, output, high impedance)**

The 32-bit BD bus interfaces the SUPERNET 3 to the buffer memory or any external logic using this bus. These lines transfer data to and from the buffer memory for the SUPERNET 3. These signals are synchronous to BMCLK.

#### **BDP3-0**

## Buffer Data Parity Bus (TTL input, output, high impedance)

The BDP3–0 bus contains the four byte-parity lines for the BD bus as shown in the following table:

| BD-Bus Lines      | Corresponding<br>Parity Lines |

|-------------------|-------------------------------|

| BD7-0 and tag bit | BDP0                          |

| BD15-8            | BDP1                          |

| BD23-16           | BDP2                          |

| BD31–24           | BDP3                          |

**Note:** BD bus parity can be either even or odd, based on the state of the parity bit (bit 12) in mode register 2 (MDREG2).

#### **BDTAG**

# Buffer Data Tag Indication (TTL input, output, high impedance)

In receive mode, this bit defines whether the information on the BD bus is data (BDTAG = 0) or frame status (BDTAG = 1). In transmit mode, when BDTAG = 1, it indicates that the end of a frame has been reached, as indicated by the presence of a tag bit in both the last long

word and the descriptor word at the end of the frame. In transmit mode, when BDTAG = 0, it indicates that the information on the BD bus is data, i.e., end-of-frame not yet reached.

## **CSO**

## Chip-Select Output (TTL output, high impedance, active low)

The chip-select output (active low) is a select signal for buffer memory read and write operations. This line is in the high-impedance state when buffer memory control is released to the NP.

### $\overline{RD}$

## Buffer Memory Read (TTL output, high impedance, active low)

This output signal (active low) controls the buffer memory during a buffer-memory read accesses. This line is in the high-impedance state when buffer memory control is released to the NP.

### $\overline{\mathsf{WR}}$

## Buffer Memory Write (TTL output, high impedance, active low)

This (active low) output signal, in its active-low state, allows write accesses to buffer memory. This line is in the high-impedance state when buffer memory control is released to the NP.

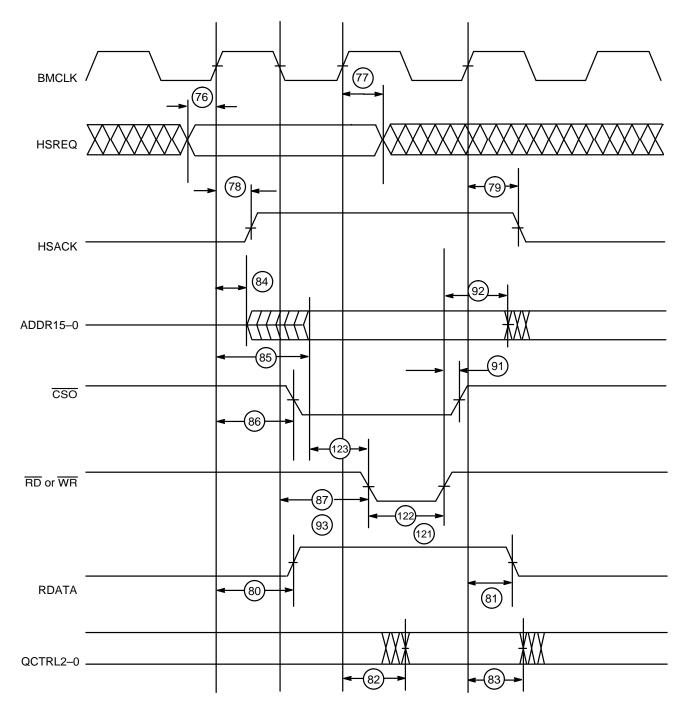

## Host/Buffer Memory Interface (10 Pins)

All these signals are synchronous to BMCLK.

#### **HSACK**

#### Host Acknowledge (TTL output, high impedance)

This signal indicates that the current host read/write request is being granted by SUPERNET 3 and allows read/write accesses of buffer memory by the host.

#### HSREQ2-0

#### **Host Request Bus (TTL input)**

The host request bus specifies to SUPERNET 3 the type of buffer memory access the host requires, as described in the following table.

Special-frame write requests are used to set up claim, beacon, and auto-void frames in the buffer memory (see the discussion under Buffer Memory Operation in SUPERNET 2 data book). These requests make use of the WPXSF register to set up special frames in the special-frame area.

Read request is used to retrieve received frames from buffer memory and store them in the system memory. Write requests are used to set up frames in buffer memory for transmission.

| HSREQ2 | HSREQ1 | HSREQ0 | Type of Request                            |

|--------|--------|--------|--------------------------------------------|

| 0      | 0      | 0      | None.                                      |

| 0      | 0      | 1      | Read Request:<br>Second Receive<br>Queue*  |

| 0      | 1      | 0      | Special Frame<br>Write Request.            |

| 0      | 1      | 1      | Read Request:<br>Receive Queue.            |

| 1      | 0      | 0      | Write Request:<br>Synchronous Queue.       |

| 1      | 0      | 1      | Write Request:<br>Asynchronous<br>Queue 0. |

| 1      | 1      | 0      | Write Request:<br>Asynchronous<br>Queue 1. |

| 1      | 1      | 1      | Write Request<br>Asynchronous<br>Queue 1.  |

**Note:** \* Only if two receive queue operation is selected through MDREG3.

#### QCTRL2-0

## Buffer Queue Control (TTL output, high impedance)

The QCTRL2–0 status output lines are encoded as described in the following table.

| QCTRL2 | QCTRL1 | QCTRL0 | Indicated Status                                                                                                    |

|--------|--------|--------|---------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | 0      | <ul><li>(1) Quiescent.</li><li>(2) Space remains<br/>for more data while<br/>loading a transmit<br/>queue</li></ul> |

| 0      | 0      | 1      | Unloading transmit<br>frame from Synchro-<br>nous Queue                                                             |

| 0      | 1      | 0      | Unloading transmit<br>frame from Asynchro-<br>nous Queue 0                                                          |

| 0      | 1      | 1      | Unloading transmit frame from Asynchronous Queue 1                                                                  |

| 1      | 0      | 0      | Reserved                                                                                                            |

| 1      | 0      | 1      | Current transmit frame<br>Underrun                                                                                  |

| 1      | 1      | 0      | Current transmit queue full.                                                                                        |

| 1      | 1      | 1      | Current transmit queue almost full                                                                                  |

These signals communicate to the host the current condition of the transmit queues. This provides useful information for doing the host interface. The meaning of these states are as follows:

## A. QCTRL[2:0] = 000

The quiescent state exists when SUPERNET 3 is neither transmitting nor receiving. This state is also true while loading a transmit queue (making a write request to a queue) and not yet unloading it, and when there is space in the queue for more data.

## B. QCTRL[2:0] = 001, 010 or 011

These states indicate unloading frame from the Synchronous Queue, Asynchronous Queue 0 or Asynchronous Queue 1, respectively. They are valid as long as the corresponding queue is not yet in the almost full or full state and, at the same time, the SUPERNET 3 is reading out of the queue. The host can transfer more data into the corresponding queue when any of these states is present. These three combinations may appear one BMCLK period later than the time indicated in the timing diagram.

## C. QCTRL[2:0] = 101

This state is present when all of the following three conditions are satisfied:

- 1. The host has issued a write request for this queue

- 2. Transmit FIFO underrun occurs

- Transmit buffer-memory underrun occurs for this queue

## D. QCTRL[2:0] = 110

When the transmit queue being requested is full, this state is presented at the queue control signals. Note that

this state does not exist in SUPERNET 2, it is added in SUPERNET 3.

## E. QCTRL[2:0] = 111

This state means the number of free long words remaining in the transmit queue which the current write request is for has decreased to the almost-full value (AFULL3-0) programmed in mode register 2. This signal condition is asserted for one BMCLK cycle only as in the FORMAC PLUS if the MENAFULL bit in the mode register 3 is not set. If this bit is set, this state will remain for every cycle as long as the queue is in almost full condition and it is not yet full.

**Note:** If AFULL3-0 is set to 000, this state is not presented, even when the transmit FIFO in buffer memory is full.

#### RDATA1

## Receive Data for Receive Queue #1 (TTL output, high impedance)

This signal indicates that received data is present in the buffer memory and is ready to be transferred by the host to system memory. Read requests are not acknowledged when RDATA1 is inactive.

#### RDATA2

## Receive Data for Receive Queue #2 (TTL output, high impedance)

This signal indicates that received data is present in the buffer memory and is ready to be transferred by the host to system memory. Read requests are not acknowledged when RDATA2 is inactive.

# **Special Functions and Control Pins** (16 Pins)

## **FLXI**

#### Flush/Inhibit (TTL input)

The SUPERNET 3 FLXI pin can be programmed to perform either of two functions: it can provide a flush received frame function for the chip or it can provide an unconditional transmit-inhibit function.

If the FLUSH function is selected and the pin is asserted by external logic, then the incoming frame is flushed. The buffer memory pointers are not advanced from where they were before the frame was received. This prevents unwanted frames and fragments from occupying receive buffer space and taking up the buffer memory bus bandwidth.

If the TRANSMIT INHIBIT function is selected and the pin is asserted by external logic, then the SUPERNET 3 completes transmitting the current frame (if transmitting) releases the token and no further transmissions can occur until the pin is deasserted. During the time that the TRANSMIT INHIBIT function is enabled, the network timers and state machines operate normally.

# RS5-0 Receive Status (TTL output, high impedance)

The receive-status (RS4-0) pins indicate the type of frame received, and the condition of the receive state

machine. The RS4–0 status output pins are encoded as illustrated in Table 3 in the SUPERNET 2 data book and the enhancements RS5–0 are described here.

| RS5 | RS4 | RS3 | RS2     | RS1 | RS0 | Indicated Status                                |

|-----|-----|-----|---------|-----|-----|-------------------------------------------------|

| 0   | Х   | Х   | Х       | Х   | Х   | As in SUPERNET 2 FORMAC Plus                    |

| 1   | 0   | 0   | 0       | 0   | 0   | Reserved                                        |

| 1   | 0   | Х   | 0       | 0   | 1   | Starting Delimiter and non-data symbol received |

| 1   | 0   | 0   | 0       | 1   | 0   | OSM mode: Stripping frame                       |

| 1   | 0   | 0   | 0       | 1   | 1   | Reserved                                        |

| 1   | 0   | 0   | 1       | 0   | 0   | Reserved                                        |

| 1   | 0   | 0   | 1       | 0   | 1   | Frame Abort                                     |

| 1   | 0   | 0   | 1       | 1   | 0   | Frame Flush                                     |

| 1   | 0   | 0   | 1       | 1   | 1   | Reserved                                        |

|     |     |     | through |     |     |                                                 |

| 1   | 1   | 1   | 1       | 1   | 1   | Reserved                                        |

#### XS3-0

## Transmit Status (TTL output, high impedance)

The transmit-status (XS3–0) pins indicate the transmit status conditions of the MAC and are valid for one clock cycle. These status signals are not present for repeated or stripped frames. These status output pins are encoded as illustrated in Table 4 (SUPERNET 2 data book) and the enhancements are described here.

| XS3 | XS2 | XS1 | XS0 | Indicated Status                        |

|-----|-----|-----|-----|-----------------------------------------|

| 0   | 0   | 0   | 0   | Quiescent.                              |

| 0   | 0   | 0   | 1   | Transmit Aborted.                       |

| 0   | 0   | 1   | 0   | Token Issued                            |

| 0   | 0   | 1   | 1   | Reserved.                               |

| 0   | 1   | 0   | 0   | Transmitting Syn-<br>chronous Queue.    |

| 0   | 1   | 0   | 1   | Transmitting Asynchronous Queue 0.      |

| 0   | 1   | 1   | 0   | Transmitting Asyn-<br>chronous Queue 1. |

| 0   | 1   | 1   | 1   | Reserved                                |

| 1   | 0   | 0   | 0   | Reserved                                |

| 1   | 0   | 0   | 1   | Initiated Claim.                        |

| 1   | 0   | 1   | 0   | Initiated Beacon.                       |

| 1   | 0   | 1   | 1   | Initiated Void                          |

| 1   | 1   | 0   | 0   | MAC Frame<br>Aborted                    |

| 1   | 1   | 0   | 1   | Void Frame<br>Aborted                   |

#### **XDAMAT**

## External Destination Address Match (TTL input, active low)

This input provides a means for additional destination-address detection external to the SUPERNET 3. This pin should be tied high when external destination-address detection is not used. This input should remain asserted for at least one BCLK cycle, and must be deasserted for at least one BCLK cycle before a subsequent external destination address match is recognized.

The XDAMAT pin which is generated by the external AF is logically ORed with the "af\_da" output signal generated by the internal AF logic. This pin should be tied high when external address detection (such as an external AF) is not used.

## XDA XACT

# External Destination Address Exact Match (TTL input, active low)

This input indicates whether the external address match was exact (low) or inexact (high). This input should remain asserted for at least one BCLK cycle, and must be deasserted for at least one BCLK cycle before a subsequent external source address match is recognized. It must be asserted and deasserted in an identical

fashion to the  $\overline{\text{XDAMAT}}$  pin. This input is used in conjunction with the  $\overline{\text{XDAMAT}}$  pin as follows:

| Match               | Action                                    |

|---------------------|-------------------------------------------|

| XDA_XACT and XDAMAT | A, C indicators set and frame copied*.    |

| XDA_XACT and XDAMAT | Invalid combination.<br>Ignored by MAC.   |

| XDA_XACT and XDAMAT | A, C indicators not set and frame copied. |

| XDA_XACT and XDAMAT | No action.                                |

<sup>\*</sup> Frame is copied if valid frame or if in promiscuous or limited promiscuous mode. In OSM, the A, C indicators are set according to the OSM rules if bits 4, 5 (MEIND0,1) are set.

The XDA\_XACT pin which is generated by the external AF is logically ORed with the "af\_dax" output signal generated by the internal AF logic. This pin is enabled only if the MENXACT bit in the mode register 3 is set. This pin should be tied high when external address detection (such as an external AF) is not used.

#### **XSAMAT**

## External Source Address Match (TTL input, active low)

This input provides a means for additional source-address detection external to the SUPERNET 3. This pin should be tied high when external source-address detection is not used. This input should remain asserted for at least one BCLK cycle, and must be deasserted for at least one BCLK cycle before a subsequent external destination address match is recognized.

The XSAMAT pin which is generated by the external AF is logically ORed with the "af\_sa" output signal generated by the internal AF logic. This pin should be tied high when external address detection (such as an external AF) is not used.

## XSA XACT

## External Source Address Exact Match (TTL input, active low)

This input indicates whether the external source address match was exact (low) or inexact (high). This input should remain asserted for at least one BCLK cycle, and must be deasserted for at least one BCLK cycle before a subsequent external source address match is recognized. It must be asserted and deasserted in an identical fashion to the  $\overline{\text{XSAMAT}}$  pin. This input is used in conjunction with the  $\overline{\text{XSAMAT}}$  pin as follows:

| Match               | Action                                  |

|---------------------|-----------------------------------------|

| XSA_XACT and XSAMAT | Frame stripped.                         |

| XSA_XACT and XSAMAT | Invalid combination.<br>Ignored by MAC. |

| XSA_XACT and XSAMAT | Frame not stripped.                     |

| XSA_XACT and XSAMAT | No action.                              |

The XSA\_XACT pin which is generated by the external AF is logically ORed with the "af\_sax" output signal generated by the internal AF logic. This pin is enabled only if the MENXACT bit in the mode register 3 is set. This pin should be tied high when external address detection (such as an external AF) is not used.

## RST Reset (TTL input)

The RST signal (active low) is an asynchronous input that initializes the internal SUPERNET 3 state machines and registers. Once RST is asserted low, it must remain asserted for at least twenty BCLK cycles. When it is deasserted the SUPERNET 3 is ready to begin normal operation only after 750 LSCLK cycles. The 750 LSCLK cycles are needed for calibration of the PDX core. Assertion and deassertion are asynchronous. A warm reset (assertion of RST after the device is in operation) will cause device outputs to be unpredictable until the device is initialized.

## **Testability Interface (5 Pins)**

#### TCK

#### Test Clock In (TTL input)

TCK provides the clock for the test logic. Any storedstate devices contained in the test logic must retain their state indefinitely if the signal applied to TCK is held high or low.

#### **TMS**

## Test Mode Select In (TTL input, Synchronous to TCK)

The test mode select input directs the operation of the generation of the TAP controller. The state of the TMS signal is sampled on the rising edge of TCK. If for some reason TMS is not driven externally, the TAP controller should behave as if this signal were driven with a logic 1 (internal pull-up).

#### TDI

## Test Data In (TTL input, Synchronous to TCK)

This pin provides for the application of serial instructions and data. The state of this signal is sampled on the rising edge of TCK. If for some reason TDI is not driven externally, the test logic should behave as if a logic 1 were applied to this signal (internal pull-up).

#### **TDO**

## Test Data Output (TTL Output, 3-state, Synchronous to TCK)

This pin provides the serial output for instructions and data from the test logic. No inversion of data is allowed between TDI and TDO during shift operations. The state of TDO changes on the falling edge of TCK. TDO is in the high impedance state except during shifting operations.

#### TRST

### Test Reset (asynchronous TTL input, active low)

This input is provided for asynchronous initialization of the TAP controller. When a logic 0 is applied, the TAP controller must go to the Test-Logic-Reset state. If for some reason TRST is not driven externally, the test logic should behave as if a logic 1 were applied (internal pull-up). This pin can not be used to initialize any system logic.

## **Power and Ground (37 Pins)**

#### **GND**

## **Ground (input)**

There are 23 ground (GND) pins on the SUPERNET 3 chip. They must all be connected to a common external ground reference.

## Vcc

#### +5 V Power (input)

There are 15 pins carrying +5-V power (VCC) on the SUPERNET 3 chip. They must all be connected to a 5 V  $\pm 5\%$  source.

## SUPERNET 2 Features not Supported

The following features are not supported in SUPERNET 3 in any mode.

- SUPERNET 3 supports the Tag Mode of operation for the system-to-buffer-memory and network (MAC)-to-buffer-memory interfaces. Non-Tag mode of operation is no longer supported.

- SUPERNET 3 supports three transmit queues: Synchronous, Async0 and Async1. Async2 is no longer supported.

- The 'Disable Carry' (DISCRY) function is no longer supported. Setting of the DISCRY bit in the mode register 1 (MDREG1: bit 6) allowed segmenting of the TRT, THT, TVX, and TMSYNC registers into 4 and 5 bits each for diagnostic purposes. This is no longer necessary due to the testability enhancements.

- Single-Frame Receive mode is no longer supported.

- Symbol Control is no longer supported in the MAC. This function was used for diagnostics purposes to transmit user-controlled data, control and violation symbols to the PHY.

- The HOLD function and associated logic is eliminated and it is no longer supported.

## Miscellaneous Changes from SUPERNET 2

The 'Current Queue Almost Full' (AFULL) encoding of the QCTRL signals is modified to be asserted for every clock after the AFULL boundary

- is crossed until the queue is full while a Host write request is asserted. Currently, the signal is asserted for one clock only.

- 'XDA\_XACT' and 'XSA\_XACT' input signals are provided for the external CAM (if implemented).

- For increased robustness, all internal tri-state busses will have a driven default state and will not be allowed to float.

- The Node Processor access interface has been streamlined to two modes:

- 1) The FORMAC Plus asynchronous access mechanism for accessing all blocks.

- 2) The PLC two-cycle synchronous access mechanism for accessing all blocks.

- There are four interrupt pins: two generated by the two MAC status registers, one generated by the AF and one generated by the PHY status register.

## **EXPLANATION OF ENHANCEMENTS**

## **Status Pins**

#### XS 3:0

#### **Transmit Status pins (outputs)**

An additional transmit status pin has been added to provide more transmit information. The encoding of the status pins is fully backward compatible with the SUPERNET 2 chipset. The enhanced encoding is enabled by setting the MENXS bit in the mode register 3 (MDREG3). The encoding of the XS pins is as follows:

| XS3 | XS2 | XS1 | XS0 | Indicated Status                       |  |

|-----|-----|-----|-----|----------------------------------------|--|

| 0   | 0   | 0   | 0   | Quiescent                              |  |

| 0   | 0   | 0   | 1   | Transmit Aborted                       |  |

| 0   | 0   | 1   | 0   | Token Issued                           |  |

| 0   | 0   | 1   | 1   | Reserved                               |  |

| 0   | 1   | 0   | 0   | Transmitting Syn-<br>chronous Queue    |  |

| 0   | 1   | 0   | 1   | Transmitting Asyn-<br>chronous Queue 0 |  |

| 0   | 1   | 1   | 0   | Transmitting Asyn-<br>chronous Queue 1 |  |

| 0   | 1   | 1   | 1   | Reserved                               |  |

| 1   | 0   | 0   | 0   | Reserved                               |  |

| 1   | 0   | 0   | 1   | Initiated Claim                        |  |

| 1   | 0   | 1   | 0   | Initiated Beacon                       |  |

| 1   | 0   | 1   | 1   | Initiated Void                         |  |

| 1   | 1   | 0   | 0   | MAC Frame<br>Aborted                   |  |

| 1   | 1   | 0   | 1   | Void Frame<br>Aborted                  |  |

| 1   | 1   | 1   | 0   | Reserved                               |  |

| 1   | 1   | 1   | 1   | Reserved                               |  |

#### **RS 5:0**

## Receive Status pins (outputs)

An additional receive status pin has been added to provide more receive information. The encoding of the status pins is fully backward compatible with the SUPERNET 2 chipset. The enhanced encoding is enabled by setting the MENRS bit in the mode register 3 (MDREG3). The encoding of the RS pins is shown on the following table.

| RS5 | RS4 | RS3 | RS2     | RS1 | RS0 | Indicated Status                                |

|-----|-----|-----|---------|-----|-----|-------------------------------------------------|

| 0   | Х   | Х   | Х       | Х   | Х   | As in SUPERNET 2 FORMAC Plus                    |

| 1   | 0   | 0   | 0       | 0   | 0   | Reserved                                        |

| 1   | 0   | Х   | 0       | 0   | 1   | Starting Delimiter and non-data symbol received |

| 1   | 0   | 0   | 0       | 1   | 0   | OSM mode: Stripping frame                       |

| 1   | 0   | 0   | 0       | 1   | 1   | Reserved                                        |

| 1   | 0   | 0   | 1       | 0   | 0   | Reserved                                        |

| 1   | 0   | 0   | 1       | 0   | 1   | Frame Abort                                     |

| 1   | 0   | 0   | 1       | 1   | 0   | Frame Flush                                     |

| 1   | 0   | 0   | 1       | 1   | 1   | Reserved                                        |

|     |     |     | through |     |     |                                                 |

| 1   | 1   | 1   | 1       | 1   | 1   | Reserved                                        |

### **QCTRL 2:0**

### **Queue Control pins (outputs)**

The encoding of the QCTRL pins is as follows:

| QCTRL2 | QCTRL1 | QCTRL0 | Indicated Status                                               |

|--------|--------|--------|----------------------------------------------------------------|

| 0      | 0      | 0      | (1) Quiescent.                                                 |

|        |        |        | (2) Space remains for more data while loading a transmit queue |

| 0      | 0      | 1      | Unloading transmit frame from Synchronous Queue                |

| 0      | 1      | 0      | Unloading transmit frame from Asynchronous Queue 0             |

| 0      | 1      | 1      | Unloading transmit frame from Asynchronous Queue 1             |

| 1      | 0      | 0      | Reserved                                                       |

| 1      | 0      | 1      | Current transmit frame<br>Underrun                             |

| 1      | 1      | 0      | Current transmit queue full                                    |

| 1      | 1      | 1      | Current transmit queue almost full                             |

## **Slower Buffer Memory Interface**

The buffer memory interface has been modified enabling slower SRAMs (35 ns) to be used as buffer memory. This reduces the system cost. The interface is fully backward compatible with the SUPERNET 2 buffer memory interface.

## Clocking

#### **LSCLK**

#### **Local Symbol Clock pin (input)**

The LSCLK is a 25 MHz clock. It is used by the PLC-S and PDX cores.

#### **BCLK**

#### Byte Clock pin (input)

The BCLK is a 12.5 MHz clock. It is used by the PLC-S and the MAC cores.

#### **BMCLK**

## **Buffer Memory Clock pin (input)**

The BMCLK is the clock signal that the MAC core uses for generating the signals to the buffer memory. BMCLK is driven with either a 12.5 or 25 MHz clock signal. If 12.5 MHz operation is desired, then this pin must be tied to BCLK pin. If 25 MHz operation is desired, then this pin must be tied to LSCLK pin.

#### A, C Indicators

The setting of the A, C indicators has been modified to allow the indicator setting to be selectable in any of the modes: online, online special mode, or external loopback. The A, C indicators can be set as normal, MSC method, or not modified at all. The modified setting of the A, C indicators can be selected by setting the

MEIND0 and MEIND1 bits in the mode register 3 (MDREG3).

| MEIND1 | MEIND0 | Description                                                                                                                              |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | Default SUPERNET 2 behavior                                                                                                              |

| 0      | 1      | Set A, C as in ONLINE mode.<br>This overrides OSM status<br>indicator setting (i.e., if MDREG1<br>bits MMODE2=0, MMODE1=1,<br>MMODE0=0). |

| 1      | 0      | Set A, C as in OSM mode.<br>This overrides the MMODE2–0<br>bits in the MDREG2 for the status<br>indicator setting.                       |

| 1      | 1      | Do not set the A, C indicators in any mode.                                                                                              |

| MEIND[1:0] | OSM | EN_XACT | XDA_XACT | XDA | DA_INT | A_FLAG | C_FLAG | A_BIT | C_BIT |

|------------|-----|---------|----------|-----|--------|--------|--------|-------|-------|

| 00         | 0   | х       | Х        | 0   | 0      | 0      | 0      | NM    | NM    |

| 00         | 0   | х       | х        | х   | 1      | 1      | 1      | 1     | 1     |

| 00         | 0   | х       | х        | 1   | 0      | 1      | 1      | 1     | 1     |

| 00         | 1   | х       | Х        | 0   | 0      | 0      | 0      | NM    | NM    |

| 00         | 1   | х       | х        | х   | 1      | 1      | 1      | 1     | 1     |

| 00         | 1   | х       | х        | 1   | 0      | 0      | 1      | NM    | 1     |

| 01         | х   | 0       | Х        | 0   | 0      | 0      | 0      | NM    | NM    |

| 01         | х   | 0       | х        | х   | 1      | 1      | 1      | 1     | 1     |

| 01         | х   | 0       | Х        | 1   | 0      | 1      | 1      | 1     | 1     |

| 01         | х   | 1       | Х        | 0   | 0      | 0      | 0      | NM    | NM    |

| 01         | х   | 1       | х        | х   | 1      | 1      | 1      | 1     | 1     |

| 01         | х   | 1       | 0        | 1   | 0      | 0      | 1      | NM    | 1     |

| 01         | х   | 1       | 1        | 1   | 0      | 1      | 1      | 1     | 1     |

| 10         | х   | 0       | Х        | 0   | 0      | 0      | 0      | NM    | NM    |

| 10         | х   | 0       | Х        | х   | 1      | 1      | 1      | 1     | 1     |

| 10         | х   | 0       | Х        | 1   | 0      | 0      | 1      | NM    | 1     |

| 10         | х   | 1       | х        | 0   | 0      | 0      | 0      | NM    | NM    |

| 10         | Х   | 1       | Х        | х   | 1      | 1      | 1      | 1     | 1     |

| 10         | Х   | 1       | 0        | 1   | 0      | 0      | 1      | NM    | 1     |

| 10         | Х   | 1       | 1        | 1   | 0      | 1      | 1      | 1     | 1     |

| 11         | Х   | Х       | Х        | х   | Х      | 0      | 0      | NM    | NM    |

where,

MEIND[1:0] Bit 4 and 5 of MDREG3

OSM - Bit 14-12 of MDREG1

EN\_XACT - Bit 2 of MDREG3

XDA\_XACT - Pin 113, is an active low signal. "1" indicates signal is active and "0" indicates signal is inactive

XDA - Pin 114, is an active low signal. "1" indicates signal is active and "0" indicates signal is inactive.

DA\_INT - Internal DA match signal

A\_FLAG - DA Match Flag

C\_FLAG - Frame Copied Flag

A\_BIT - A bit in the End Delimiter

C\_BIT - C bit in the End Delimiter

x - Don't care condition.

NM - Not modified by the MAC

#### **Transmit Queues**

## **ASYNC2 Transmit Queue Not Supported**

The SUPERNET 3 supports SYNCHRONOUS, and two ASYNCHRONOUS priorities. The ASYNC2 queue is no longer supported. This causes the following changes:

- 1. TPRI2 (16-bit priority register for asynchronous queue 2) is no longer implemented.

- 2. EAA2, WPXA2, SWPXA2, RPXA2 registers are no longer implemented.

- 3. The 'Clear Asynchronous Queue 2 Lock' and 'Transmit Asynchronous Queue 2' commands are no longer available in the command registers 1 and 2, respectively. The value 0x18 in command register 1 and 0x08 in command register 2 shall not be decoded to any other instruction. These values are reserved.

- The STEFRMA2, STECFRMA2 and STXABRA2 bits in the upper 16 bits of the status register 1 (ST1U) are reserved and set to zero. Similarly SQLCK2, STXINFLA2, SPCEPDA2, and STBURA2 are reserved and set to zero.

- The QCTRL[2:0] = 100 encoding is now invalid. This

encoding indicated 'Request transfer into

Asynchronous Queue 2' which is no longer

available. The encoding is reserved and shall not be

used to indicate any other QCTRL condition. (See

NOTE)

- 6. The HSREQ[2:0] = 111 is now decoded as "Write Request: Asynchronous Queue 1". In FORMAC+ this request indicated a write request to asynchronous queue 2 which is no longer available.

**Note:** If the encoding HSREQ[2:0] = 111 is used, the SUPERNET 3 would not use the QCTRL[2:0] = 100

encoding to indicate status of Asynchronous Queue, but instead the QCTRL[2:0] = 011 ("Request transfer into Asynchronous Queue 1") encoding would be indicated by SUPERNET 3 and external logic could be added to invert this encoding to be compatible with FORMAC+.

## **AFULL Encoding of QCTRL Signals Modified**

The QCTRL2–0 pins provide the encoded status of the buffer memory transmit queues. The value QCTRL[2:0] = 111, 'Current queue almost full', was asserted for one host write cycle in SUPERNET 2. This signal shall now be generated for every host write cycle until the queue becomes full or the almost full threshold is no longer exceeded.

This new signal assertion is implemented only if the bit MENAFULL is set in mode register 3 (MDREG3)

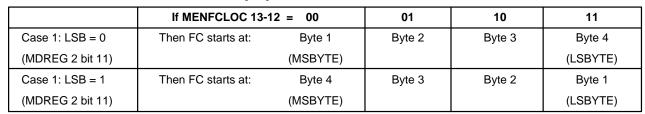

#### **Transmit Frame Format**

In SUPERNET 2 transmit frames must consist of aligned data, i.e. all words in the buffer memory must contain four valid bytes, except that the last data word may consist of less than four bytes. This required that the Frame Control (FC) of the frame be written as the most significant byte of the frame data long word. SUPERNET 3 would support an enhanced feature, where in the Frame Control (FC) could be any byte of the frame data long word. The Destination Address (DA) would follow the FC as the next byte in any mode of operation. This feature is enabled only when the bits MENFCLOC (bit 12 & 13) is set in mode register 3 (MDREG3). Upon reset these bits would be both zero and the Frame Control (FC) has to be written as the most significant byte of the frame data long word. The following table describes the decoding of the MENFCLOC bits in the mode register 3 (MDREG 3):

## Non-Tag Mode of Operation No Longer Supported

The SUPERNET 3 only supports the tag mode of operation for transmit and receive. The non-tag mode of operation is no longer supported. All functionality related to the non-tag mode of operation is removed. This causes the following changes:

- Bits [7:4] in status register 1 upper (ST1U), indicating 'Transmit End of Chain of Frames' (STECFRM-S, A0, A1, A2) are now reserved. They shall be read as zero.

- 2. Bits [7:4] in status register 1 lower (ST1L), indicating 'Transmit Instruction Full' (STXINFL-S, A0, A1, A2) are now reserved. They shall be read as zero.

- In Command register 2, the commands 'Transmit Synchronous Queue' [0x01], 'Transmit Asynchronous Queue 0' [0x02], and 'Transmit Asynchronous Queue 2' [0x08] are now reserved. These values shall not be decoded to any other instruction.

- 4. Bit 15 in mode register 2 (MDREG2) indicating Buffer Memory Mode is now decoded differently. This bit shall be read as one upon reset, indicating TAG mode of operation. If programmed to zero, the modified TAG mode of operation will be enabled. This bit selection applies to both receive queues if MENDRCV bit is set in mode register 3 (MDREG 3).

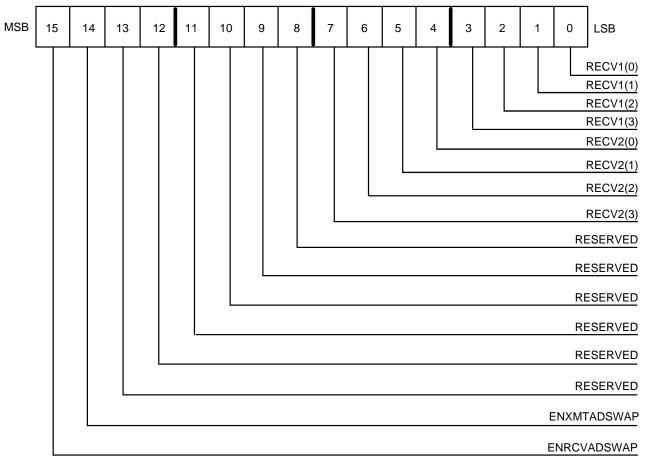

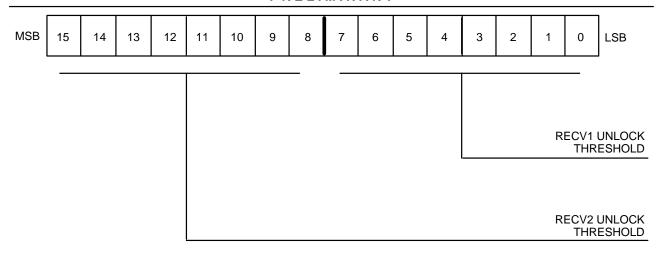

### **Modified TAG Mode Operation**

The SUPERNET 3 will have two modes of host interface to buffer memory. The two modes are distinct and independent ways of accessing the buffer memory depending upon the selection of the TAG mode or modified TAG mode. In TAG mode the SUPERNET 3 provides the local buffer management, i.e the queue pointers are maintained by SUPERNET 3. Modified TAG mode is used when the NON-TAG mode users of FORMAC+ are redesigning for SUPERNET 3. Loading

of transmit frames in modified TAG is identical to TAG mode. The unloading of received frames is different in Modified TAG mode of operation. The format of a receive frame is as shown Figure 1. The first long word in each frame consists of a 16-bit status word and a 16-bit word that gives the length of the frame in bytes. The status/length word is followed by the data words. The location of the first byte in the first long word of data is defined by the byte boundary bits RXFBB1-0 of mode register (MDREG 2). At the end of the frames that make up a receive queue, SUPERNET 3 writes a long word with all bits as a logic 0, which indicates that there is no more data in this queue. The only function of this word is to act as an end delimiter. Note that the MSVALID bit in bit 31 of the status word at the start of the frame is always in the logic 1 state. Also, when another frame follows this queue, it overwrites the end delimiter word with the receive status word of the new frame. After each frame has been written into buffer memory, SUPERNET 3 write the status and frame length at the start of each frame, and places an end-indicator word of all 0's at the end of the gueue. Once a frame is completely received, the status bit SRCOMP in status register 2 (ST2U) is set. If the received frame is aborted, the SUPERNET 3 will write the status word indicating the aborted status (bit 30) and the length field bits will be all zero. If the receive queue has an overflow condition during frame reception, the status register bit indicating SRCVOVR in status register 2 (ST2U bit 11), is set high and the frame is aborted. An overflow also sets the MSRABT bit (bit 30) in the receive frame status word of the incomplete frame. The received frames are unloaded by the host from the buffer memory by using the host request pins (HSREQ). The RDATA signal is always in the 0 state and receive frame threshold (RTHR) is not applicable in modified TAG mode for asserting the RDATA pin. If dual receive queue operation is selected (MENDRCV, bit 11 in MDREG 3) then the receive status information would be indicated in the corresponding status register (ST2U for RECV1 and ST3U for RECV2).

| 31 16         | 16 15                        |  |     | P3 | P2 | P1 | P0 |               |

|---------------|------------------------------|--|-----|----|----|----|----|---------------|

| STATUS WORD 1 | STATUS WORD 1 FRAME 1 LENGTH |  |     |    |    |    |    |               |

| FRAME 1       |                              |  | 0   |    |    |    |    |               |

| STATUS WORD 2 | FRAME 2 LENGTH               |  | 0   |    |    |    |    |               |

| FRAME 2       |                              |  | 0 0 |    |    |    |    |               |

| STATUS WORD 3 | FRAME 3 LENGTH               |  | 1   |    |    |    |    | Aborted Frame |

| STATUS WORD 4 | FRAME 4 LENGTH               |  | 1   |    |    |    |    | Aborted Frame |

| STATUS WORD 5 | FRAME 5 LENGTH               |  | 1   |    |    |    |    |               |

| FRAME 5       |                              |  |     |    |    |    |    |               |

| ALL 2         | ZEROs                        |  | 0   |    |    |    |    |               |

19574A-2

Figure 1. Memory Receive Queue (Modified TAG Mode)

#### **Transmit Command**

The SUPERNET 3 provides a feature to control transmission of frames from ASYNC1 queue in both TAG and Modified TAG modes. This feature can be enabled by programming the MENTRCMD (bit 14) in mode register 3 (MDREG3). This feature, when enabled, would wait for the "Transmit Asynchronous Queue1" command. This feature would be applicable only to ASYNC1 gueue. The SUPERNET 3 has to be in initialize mode to enable the transmit command feature. Once this is enabled the SUPERNET 3 will not transmit from ASYNC1 queue unless a command in given by the Node Processor. To disable this feature, the SUPERNET 3 has to be in initialize or memory active mode. The read pointer (RPXA1), write pointer (WPXA1) and shadow write pointer (SWPXA1) are under the control of the user. The frames to be transmitted could be loaded by the host into the buffer memory either by using the host request pins, or by using NPDMA pins or by using the MARW and MDR registers.

When using the host request pins, the SUPERNET 3 responds to the host request as in any mode, except that the transmit threshold register value would be ignored. IFPC would not monitor the frames being loaded into buffer memory for memory full condition, buffer empty condition etc. After the last data word and descriptor are written to complete the frame, transmit command can be issued to start transmission.

When NPMEMRQ pin is used by the NP the address bus and memory control signal lines are placed in the high-impedance state by the SUPERNET 3. This gives the NP free access to load the buffer memory, however, the frames must conform to the format defined. The NP is also responsible in keeping track of Async 1 pointers (WPXA1, RPXA1, LTDPA1) prior to issuing the transmit command.

When the NP uses the MARW and MDR to load the buffer memory, it first loads the MARW with the starting

address of the frame. Then the MDRU is loaded from the NP, followed by the MDRL. As soon as the second 16-bit data word is loaded, SUPERNET 3 sets an internal request to move the contents of the MDR to the buffer memory. The MARW is incremented after the write operation is completed. The NP could use the set tag command in CMDREG2 to set the tag bit for the MDR write cycle, however, the tag bit command is valid for one NP write operation only.

After the complete frame(s) have been loaded for transmission, the NP has to program the last transmit descriptor pointer (LTDPA1) to be equal to the address of the last descriptor written. Also, the ASYNC1 queue (WPXA1) write pointer needs to be programmed to LTDPA1 + 1. The SUPERNET 3 would assume that the read pointer is at the correct address. The NP should then give an instruction to SUPERNET 3 to transmit the ASYNC1 queue. The SUPERNET 3 would transmit till the read pointer (RPXA1) equals the last transmit descriptor pointer (LTDPA1). The user could load multiple frames before issuing the command. The NP cannot issue more than one transmit command until the SUPERNET 3 indicates the "End of transmit command" status (STECMDA1) in status register 1 - upper (ST1U).

## **TDAT Loopback**

The SUPERNET 3 provides a feature to control the loopback of transmit datapath after the PLC (TDAT) back to the receive data path of the PLC (RDAT). This loopback path is enabled when MDREG3, bit 15 (MENTDLPBK) bit is set to logic "1".

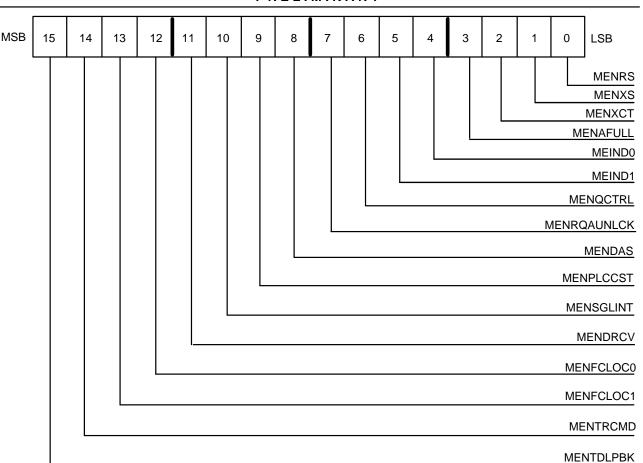

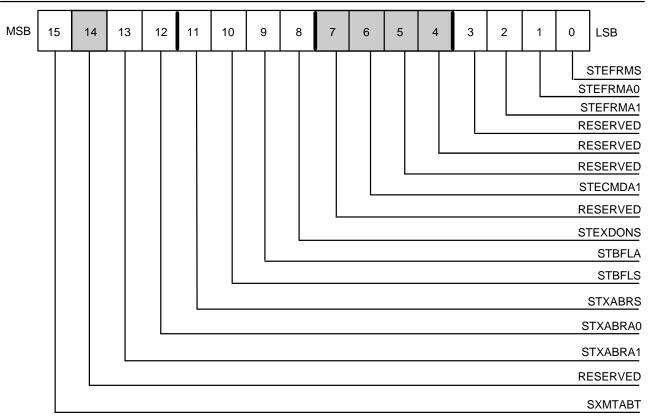

## **Mode Register 3 (MDREG3)**

An additional 16-bit mode register 3 is provided. The new features and modifications are enabled by the setting of the bits in the MDREG3. By default, the register bits are reset to zero. This register can only be written when the SUPERNET 3 is in Initialize or Memory Active modes.

19574A-3