#### Features

- 32,768 channel x 32,768 channel non-blocking digital Time Division Multiplex (TDM) switch at 65.536 Mbps, 32.768 Mbps and 16.384 Mbps or using a combination of rates

- 16,384 channel x 16,384 channel non-blocking digital TDM switch at 8.192 Mbps

- High jitter tolerance with multiple input clock sources and frequencies

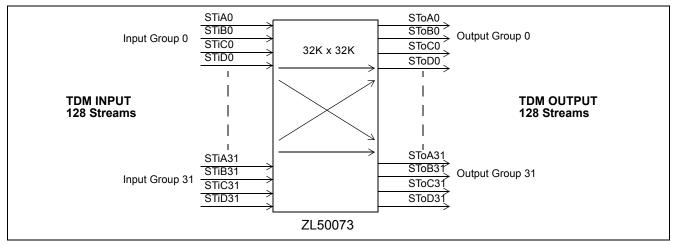

- Up to 128 serial TDM input streams, divided into 32 groups with 4 input streams per group

- Up to 128 serial TDM output streams, divided into 32 groups with 4 output streams per group

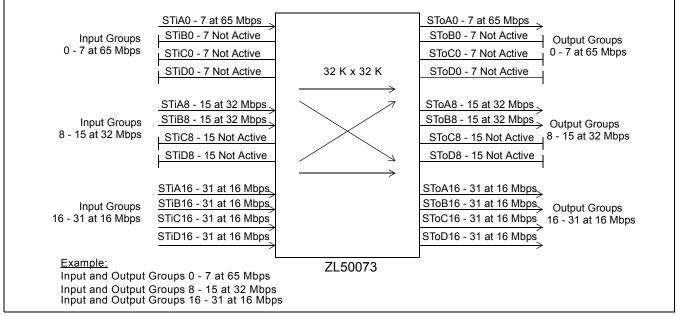

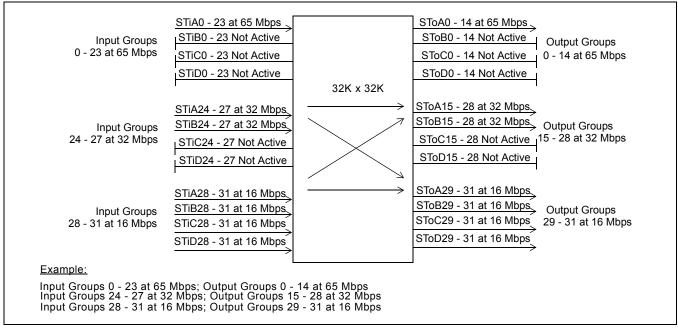

- Per-group input and output data rate conversion selection at 65.536 Mbps, 32.768 Mbps, 16.384 Mbps and 8.192 Mbps. Input and output data group rates can differ

- Per-group input bit delay for flexible sampling point selection

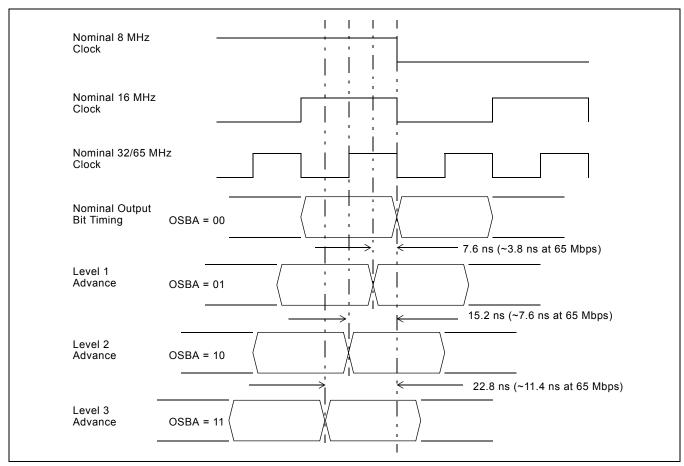

- · Per-group output fractional bit advancement

- Four sets of output timing signals for interfacing additional devices

- Per-channel A-Law/μ-Law Translation

#### January 2006

#### **Ordering Information**

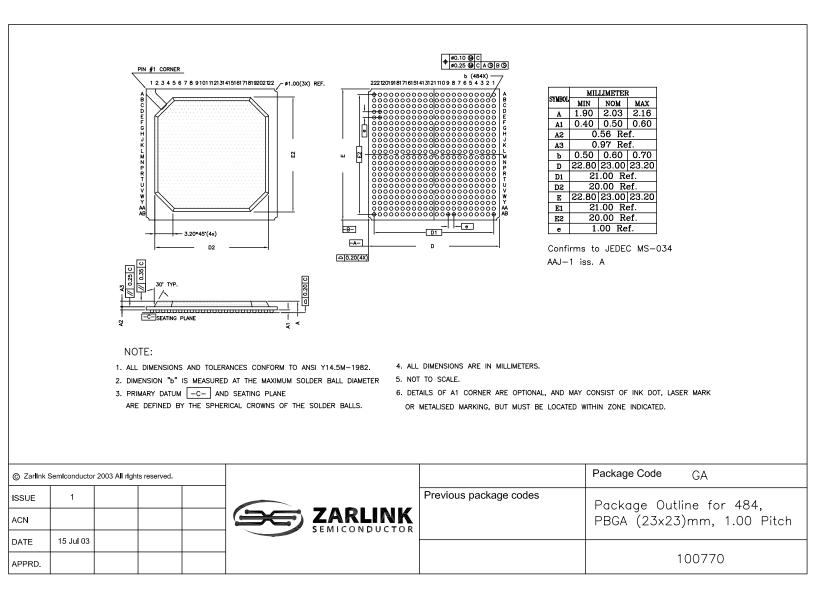

ZL50073GAC 484 Ball PBGA Trays ZL50073GAG2 484 Ball PBGA\*\* Trays \*\*Pb Free Tin/Silver/Copper

#### -40°C to +85°C

- Per-channel constant or variable throughput delay for frame integrity and low latency applications

- · Per-stream Bit Error Rate (BER) test circuits

- Per-channel high impedance output control

- · Per-channel force high output control

- Per-channel message mode

- Control interface compatible with Intel and Motorola Selectable 32 bit and 16 bit nonmultiplexed buses

- Connection Memory block programming

- Supports ST-BUS and GCI-Bus standards for input and output timing

- IEEE 1149.1 (JTAG) test port

- 3.3 V I/O with 5 V tolerant inputs; 1.8 V core voltage

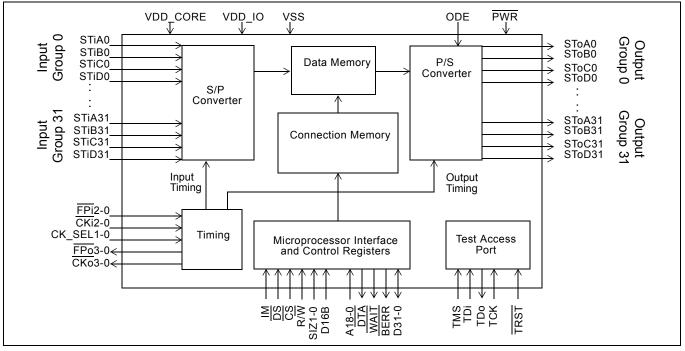

#### Figure 1 - ZL50073 Functional Block Diagram

1 Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Downloaded from Elcodis.com electronic components Gopyright 2004-2006, Zarlink Semiconductor Inc. All Rights Reserved.

# Applications

- Large Switching Platforms

- Central Office Switches

- Wireless Base Stations

- Multi-service Access Platforms

- Media Gateways

## Description

The ZL50073 is a non-blocking Time Division Multiplex (TDM) switch with maximum 32,768 x 32,768 channels. The device can switch 64 kbps and Nx64 kbps TDM channels from any input stream to any output stream. With a number of enhanced features, the ZL50073 is designed for high capacity voice and data switching applications.

The ZL50073 has 128 input and 128 output data streams which can operate at 8.192 Mbps, 16.384 Mbps, 32.768 Mbps or 65.536 Mbps. The large number of inputs and outputs maintains full 32 K x 32 K channel switching capacity at bit rates of 65 Mbps, 32 Mbps and 16 Mbps. Up to 32 input and output data streams may operate at 65 Mbps. Up to 64 input and output data streams may operate at 32 Mbps. Up to 128 input and output data streams may operate at 16 Mbps or 8 Mbps. The data rate can be independently set in groups of 4 input or output streams. In this way it is possible to provide rate conversion from input data channel to output data channel.

The ZL50073 uses a master clock (CKi0) and frame pulse (FPi0) to define the TDM data stream frame boundary and timing. A high speed system clock is derived internally from CKi0 and FPi0. The input and output data streams can independently reference their timings to one of the input clocks or to the internal system clock.

The ZL50073 has a variety of user configurable options designed to provide flexibility when data streams are connected to multiple TDM components or circuits. These include:

- Two additional programmable reference inputs, CKi2 1 and FPi2 1, which can be used to provide alternative sources for input and output stream timing

- Variable input bit delay and output advancement, to accommodate delays and frame offsets of streams connected through different data paths

- Four timing outputs, CKo3 0 and FPo3 0, which can be configured independently to provide a variety of clock and frame pulse options

- Support of both ST-BUS and GCI-Bus formats

The ZL50073 also has a number of value added features for voice and data applications:

- Per-channel variable delay mode for low latency applications and constant delay mode for frame integrity applications

- Per-channel A-Law/µ-Law Conversions for both voice and data

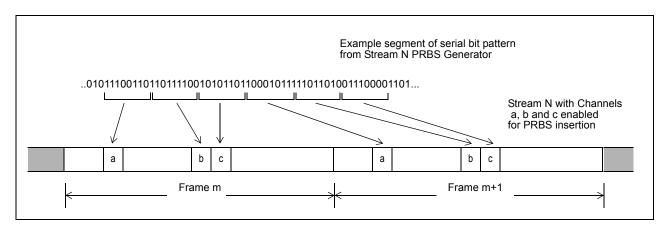

- 128 separate Pseudo-random Bit Sequence (PRBS) test circuits; one per stream. This provides an integrated Bit Error Rate (BER) test capability to facilitate data path integrity checking

The ZL50073 has two major modes of operation: Connection Mode (normal) and Message Mode. In Connection Mode, data bytes received at the TDM inputs are switched to timeslots in the output data streams, with mapping controlled by the Connection Memories. Using Zarlink's Message Mode capability, microprocessor data can be broadcast to the output data streams on a per-channel basis. This feature is useful for transferring control and status information to external circuits or other TDM devices.

A non-multiplexed microprocessor port provides access to the internal Data Memory, Connection Memory and Control Registers used to program ZL50073 options. The port is configurable to interface with either Motorola or Intel-type microprocessors and is selectable to be either 32 bit or 16 bit.

The mandatory requirements of IEEE 1149.1 standard are supported via the dedicated Test Access Port.

# **Table of Contents**

| Features                                                   |     |

|------------------------------------------------------------|-----|

| Applications                                               | . 2 |

| Description                                                | . 2 |

| Change Summary                                             | . 7 |

| 1.0 Functional Description                                 | 14  |

| 1.1 Overview                                               | 14  |

| 1.2 Switch Operation                                       | 15  |

| 1.3 Stream Provisioning                                    | 16  |

| 1.4 Input and Output Rate Selection                        |     |

| 1.4.1 Per Group Rate Selection                             |     |

| 1.5 Rate Conversion                                        |     |

| 2.0 Input Clock (CKi) and Input Frame Pulse (FPi) Timing.  | 18  |

| 3.0 Output Clock (CKo) and Output Frame Pulse (FPo) Timing | 19  |

| 4.0 Output Channel Control                                 |     |

| 5.0 Data Input Delay and Data Output Advancement           |     |

| 5.1 Input Sampling Point Delay Programming.                |     |

| 5.2 Fractional Bit Advancement on Output                   |     |

| 6.0 Message Mode                                           |     |

| 6.1 Data Memory Read                                       |     |

| 6.2 Connection Memory Block Programming                    |     |

| 7.0 Data Delay Through the Switching Paths                 |     |

| 7.1 Constant Delay Mode                                    |     |

| 7.2 Variable Delay Mode                                    |     |

| 8.0 Per-Channel A-Law/m-Law Translation                    |     |

| 9.0 Bit Error Rate Tester                                  |     |

|                                                            |     |

| 10.0 Microprocessor Port                                   |     |

| 10.1 Addressing.                                           |     |

| 10.2 32 bit Bus Operation                                  |     |

| 10.4 Bus Operation                                         |     |

| 10.4.1 Read Cycle.                                         |     |

| 10.4.2 Write Cycle                                         |     |

| 11.0 Power-up and Initialization of the ZL50073            |     |

| 11.1 Device Reset and Initialization                       |     |

| 11.2 Power Supply Sequencing                               |     |

| 11.3 Initialization                                        |     |

| 12.0 IEEE 1149.1 Test Access Port.                         |     |

| 12.1 Test Access Port (TAP).                               |     |

| 12.2 Instruction Register                                  |     |

| 12.3 Test Data Register.                                   |     |

| 12.4 Boundary Scan Description Language (BSDL)             |     |

| 13.0 Memory Map of ZL50073                                 |     |

| 14.0 Detailed Memory and Register Descriptions.            |     |

| 14.1 Connection Memory                                     |     |

| 14.1.1 Connection Memory Bit Functions                     |     |

| 14.1.2 Connection Memory LSB                               |     |

| 14.2 Data Memory                                           |     |

| 14.3 BER Control Memory and Error Counters                 |     |

| 14.3.1 Input BER Enable Control Memory                     |     |

| 14.3.2 BER Counters                                        | 42  |

|                                                            |     |

# **Table of Contents**

| 14.4 Group Control Registers          |  |

|---------------------------------------|--|

| 14.5 Input Clock Control Register     |  |

| 14.6 Output Clock Control Register    |  |

| 14.7 Block Init Register              |  |

| 14.8 Block Init Enable Register       |  |

| 15.0 DC/AC Electrical Characteristics |  |

# List of Figures

| Figure 1 - ZL50073 Functional Block Diagram                                              | 1 |

|------------------------------------------------------------------------------------------|---|

| Figure 2 - 32 K x 32 K Channel Basic Switch Configuration                                | 5 |

| Figure 3 - ZL50073 32 K x 32 K Channel and Stream Provisioning Example at Multiple Rates | 7 |

| Figure 4 - Input and Output Data Rate Conversion Example                                 | 8 |

| Figure 5 - Input Sampling Point Delay Programming                                        | 0 |

| Figure 6 - Output Bit Advancement Timing                                                 |   |

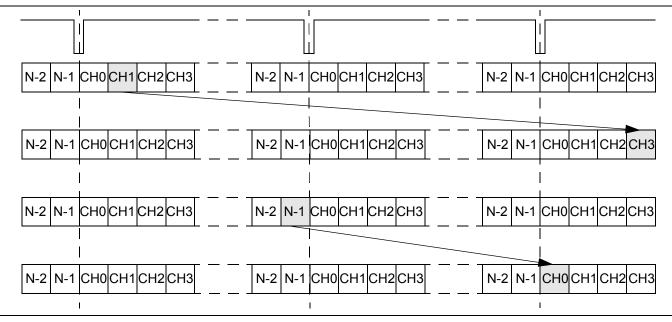

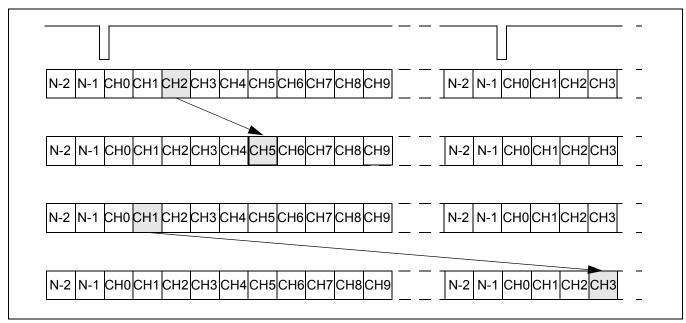

| Figure 7 - Data Throughput Delay for Constant Delay                                      | 3 |

| Figure 8 - Data Throughput Delay for Variable Delay                                      | 3 |

| Figure 9 - Example PRBS Timeslot Insertion                                               | 5 |

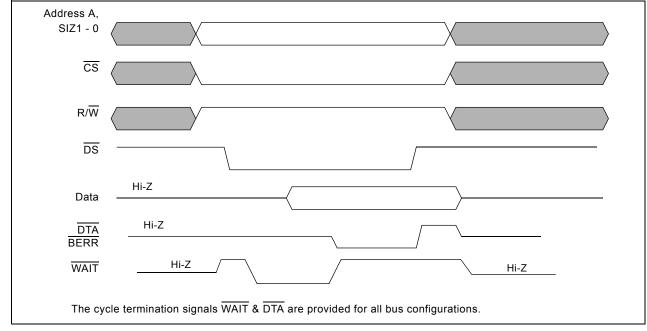

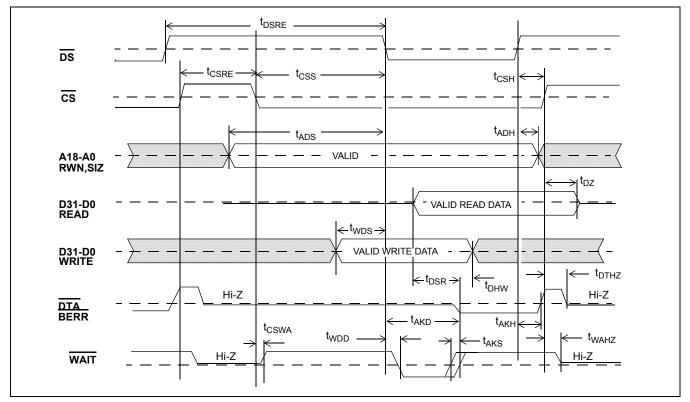

| Figure 10 - Read Cycle Operation                                                         | 9 |

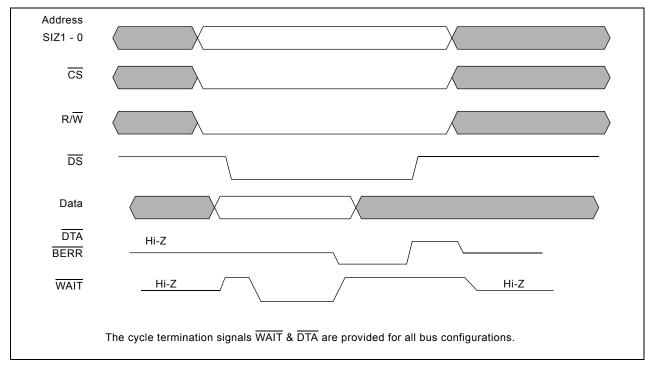

| Figure 11 - Write Cycle Operation                                                        | 0 |

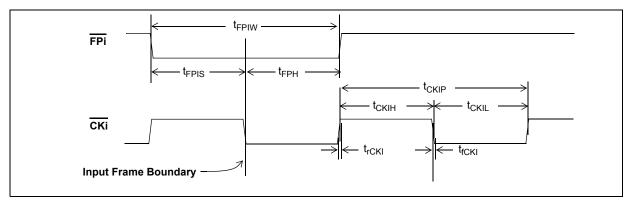

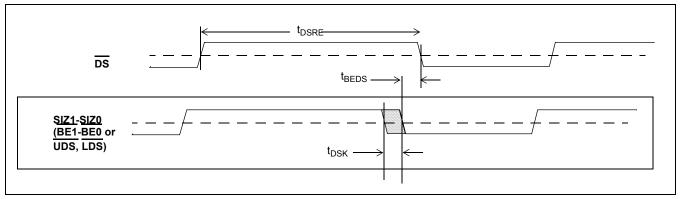

| Figure 12 - Frame Pulse Input and Clock Input                                            | 5 |

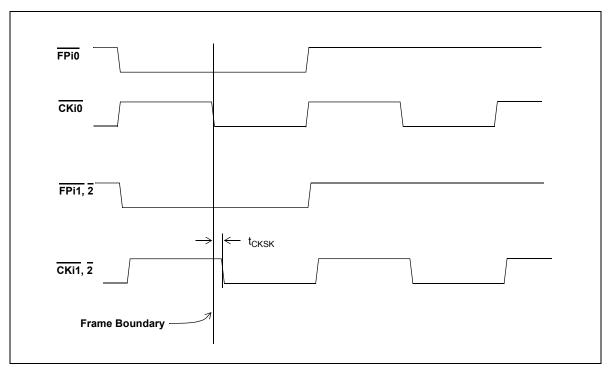

| Figure 13 - Frame Skew Timing Diagram                                                    | 6 |

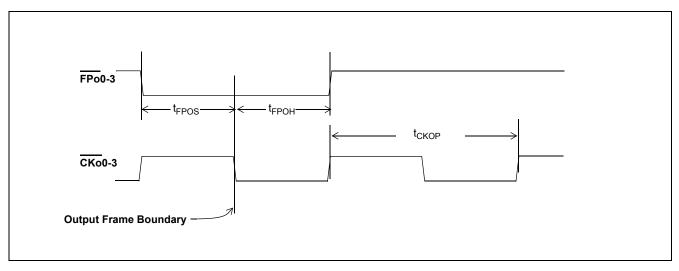

| Figure 14 - ST-Bus Frame Pulse and Clock Output Timing                                   | 8 |

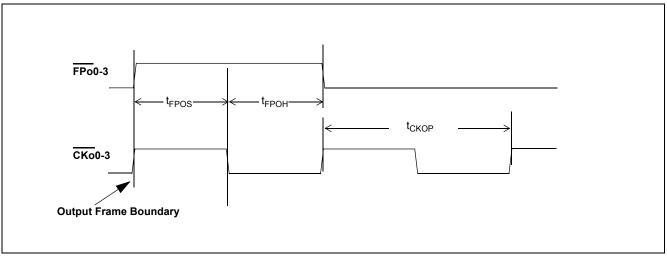

| Figure 15 - GCI Frame Pulse and Clock Output Timing5                                     | 8 |

| Figure 16 - Serial Data Timing to CKi 6                                                  | 0 |

| Figure 17 - Serial Data Timing to CKo 6                                                  | 2 |

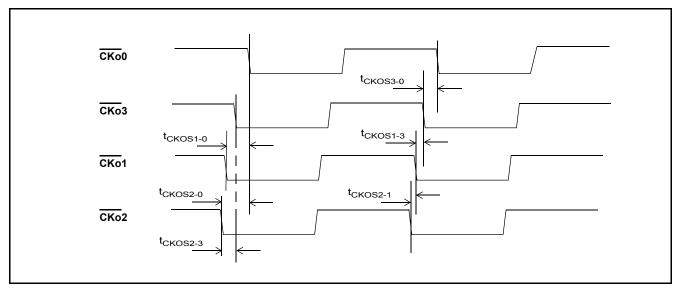

| Figure 18 - CKo to other CKo Skew                                                        | 3 |

| Figure 19 - Microprocessor Bus Interface Timing                                          | 5 |

| Figure 20 - Intel Mode Timing 6                                                          |   |

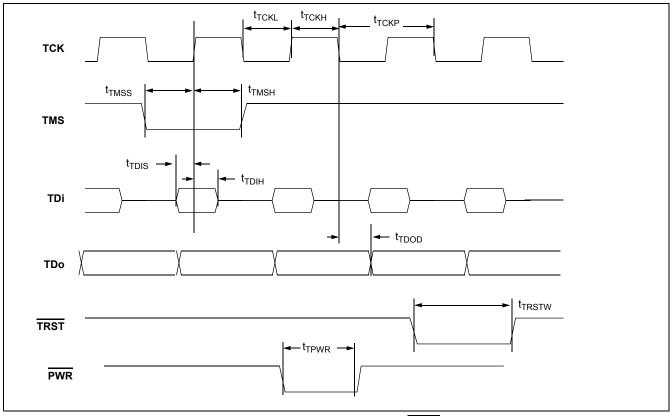

| Figure 21 - IEEE 1149.1 Test Port & PWR Reset Timing                                     | 6 |

# **List of Tables**

| Table 1 - Data Rate and Maximum Switch Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2 - TDM Stream Bit Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16 |

| Table 3 - CKi0 and FPi0 Setting via CK_SEL1 - 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18 |

| Table 4 - Input and Output Voice and Data Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24 |

| Table 5 - Example of Address and Byte Significance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26 |

| Table 6 - 32 Bit Motorola Mode Byte Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26 |

| Table 7 - 32 Bit Motorola Mode Access Transfer Size    Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26 |

| Table 8 - 32 bit Intel Mode Bus Enable Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26 |

| Table 9 - Byte Enable Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27 |

| Table 10 - 16 Bit Mode Word Alignment.    Image: Comparison of the second | 27 |

| Table 11 - 16 Bit Mode Example Byte Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28 |

| Table 12 - Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32 |

| Table 13 - Connection Memory Group Address Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33 |

| Table 14 - Connection Memory Stream Address Offset at Various Output Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34 |

| Table 15 - Connection Memory Timeslot Address Offset Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34 |

| Table 16 - Connection Memory Bits (CMB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35 |

| Table 17 - Connection Memory LSB Group Address Mapping         Connection Memory LSB Group Address Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37 |

| Table 18 - Connection Memory LSB Stream Address Offset at Various Output Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39 |

| Table 19 - Data Memory Group Address Mapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40 |

| Table 20 - Data Memory Stream Address Offset at Various Output Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40 |

| Table 21 - BER Enable Control Memory Group Address Mapping         Image: Control Memory Group Address Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41 |

| Table 22 - BER Enable Control Memory Stream Address Offset at Various Output Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42 |

| Table 23 - BER Counter Group and Stream Address Mapping    Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43 |

| Table 24 - Group Control Register Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43 |

| Table 25 - Group Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44 |

| Table 26 - Input Clock Control Register    Input Clock Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 |

| Table 27 - Output Clock Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48 |

| Table 28 - Block and Power-up Initialization Status Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52 |

# **Change Summary**

The following table captures the changes from the April 2005 issue.

| Page | ltem                                                       | Change                                                    |  |  |  |  |  |  |

|------|------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

| 28   | 10.4.1, "Read Cycle"                                       | Clarified WAIT signal description in Read Cycle.          |  |  |  |  |  |  |

| 29   | Figure 10 "Read Cycle Operation"                           | Corrected WAIT signal tristate timing in Read Cycle.      |  |  |  |  |  |  |

| 29   | 10.4.2, "Write Cycle"                                      | Clarified WAIT signal description in Write Cycle.         |  |  |  |  |  |  |

| 30   | Figure 11 "Write Cycle Operation"                          | Corrected WAIT signal tristate timing in write Cycle.     |  |  |  |  |  |  |

| 43   | Table 23 "BER Counter Group and<br>Stream Address Mapping" | Corrected BER Counter Group and Stream Mapping Addresses. |  |  |  |  |  |  |

The following table captures the changes from the July 2004 issue.

| Page | Item                                                                                                                                                                                                                                                                                                                                                                                                                  | Change                                                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12   | "Pin Description" - CKo0-3                                                                                                                                                                                                                                                                                                                                                                                            | Added special requirement for using output clock at 65.536 MHz.                                                                                                                                        |

| 13   | "Pin Description" - DTA, WAIT                                                                                                                                                                                                                                                                                                                                                                                         | Added more detailed description to the $\overline{\text{DTA}}$ and $\overline{\text{WAIT}}$ pins.                                                                                                      |

| 54   | "AC Electrical Characteristics1 - FPi0-2<br>and CKi0-2 Timing"                                                                                                                                                                                                                                                                                                                                                        | Added t <sub>FPIS</sub> , t <sub>FPIH</sub> (input frame pulse setup and hold) maximum values.                                                                                                         |

| 56   | Figure 13 "Frame Skew Timing Diagram"                                                                                                                                                                                                                                                                                                                                                                                 | Added FPi1,2 frame pulse to Figure "Frame Skew Timing Diagram" to clarify frame boundary skew.                                                                                                         |

| 57   | <ul> <li>(1) "AC Electrical Characteristics1 -<br/>FPO0-3 and CKO0-3 (65.536 MHz)</li> <li>Timing"</li> <li>(2) "AC Electrical Characteristics1 -<br/>FPO0-3 and CKO0-3 (32.768 MHz)</li> <li>Timing"</li> <li>(3) "AC Electrical Characteristics1 -<br/>FPO0-3 and CKO0-3 (16.384 MHz)</li> <li>Timing"</li> <li>(4) "AC Electrical Characteristics1 -<br/>FPO0-3 and CKO0-3 (8.192 MHz)</li> <li>Timing"</li> </ul> | Added CKO0-3 and FPO0-3 setup and hold parameters for all different clock rates.                                                                                                                       |

| 58   | "AC Electrical Characteristics - Output<br>Clock Jitter Generation"                                                                                                                                                                                                                                                                                                                                                   | Added this table to specify $\overline{CKO}0-3$ jitter generation.                                                                                                                                     |

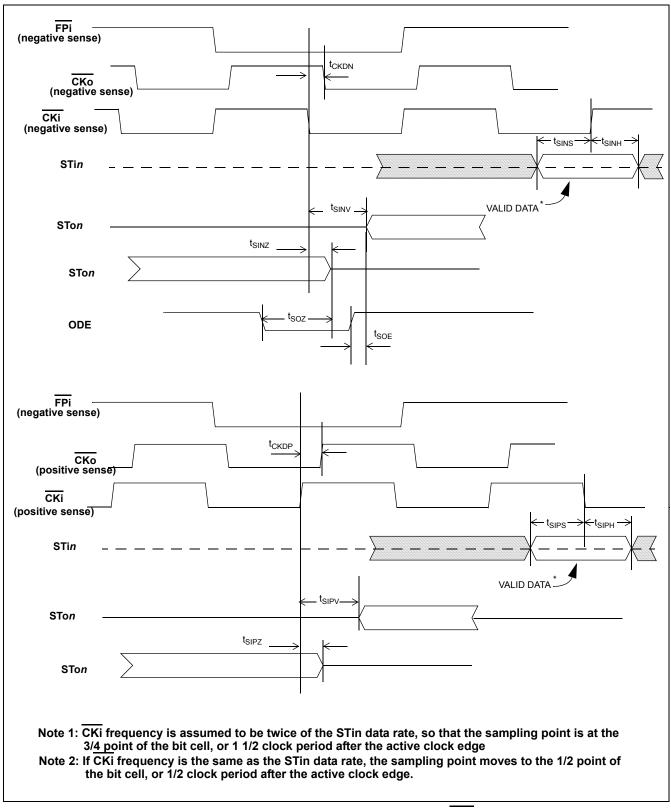

| 59   | "AC Electrical Characteristics1 - Serial<br>Data Timing2 to CKi"                                                                                                                                                                                                                                                                                                                                                      | (1) Values of parameters $t_{SIPS}$ , $t_{SIPH}$ , $t_{SINS}$ , $t_{SINH}$ , $t_{SINV}$ , $t_{SIPZ}$ and $t_{SINZ}$ are revised.<br>(2) Separated parameter $t_{CKD}$ into $t_{CKDP}$ and $t_{CKDN}$ . |

| 60   | Figure 16 "Serial Data Timing to CKi"                                                                                                                                                                                                                                                                                                                                                                                 | Added more detail to figure.                                                                                                                                                                           |

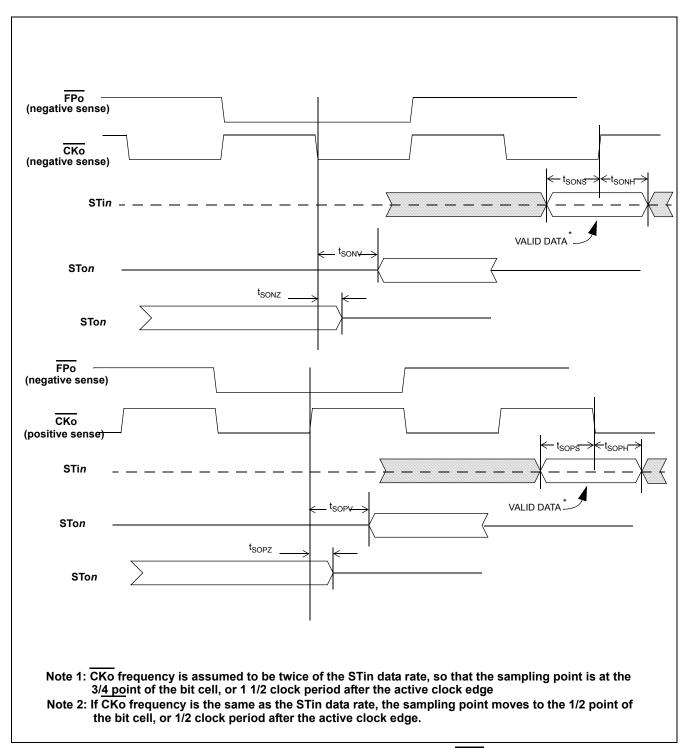

| 61   | "AC Electrical Characteristics - Serial<br>Data Timing1 to CKo2"                                                                                                                                                                                                                                                                                                                                                      | Values of parameters $t_{SOPS}$ , $t_{SOPH}$ , $t_{SONS}$ , $t_{SONH}$ , $t_{SOPV}$ , $t_{SONV}$ , $t_{SOPZ}$ and $t_{SONZ}$ are revised.                                                              |

| 62   | Figure 17 "Serial Data Timing to CKo"                                                                                                                                                                                                                                                                                                                                                                                 | Added more detail to figure.                                                                                                                                                                           |

| 63   | "AC Electrical Characteristics - CKo to<br>Other CKo Skew1"                                                                                                                                                                                                                                                                                                                                                           | Added $\overline{\text{CKO}}$ skew parameters, t <sub>CKOS</sub> .                                                                                                                                     |

| 63   | Figure 18 "CKo to other CKo Skew"                                                                                                                                                                                                                                                                                                                                                                                     | Added figure to show t <sub>CKOS.</sub>                                                                                                                                                                |

#### Pin Diagram - ZL50073 23 mm x 23 mm 484 Ball PBGA (as viewed through top of package)

A1 corner identified by metallized marking.

|    | 1            | 2            | 3            | 4            | 5            | 6                         | 7                       | 8                       | 9                       | 10                        | 11                    | 12                        | 13                      | 14                    | 15                        | 16                      | 17                        | 18           | 19           | 20           | 21           | 22           |