# IEEE 1588-2008 Synchronization PLL

**Data Sheet**

June 2011

A full Design Manual is available to qualified customers. To register, please send an email to TimingandSynch@Zarlink.com.

#### **Features**

- Frequency, Phase and Time Synchronization over IP, MPLS and Ethernet Packet Networks

- Frequency accuracy performance for WCDMA-FDD, GSM, LTE-FDD and femtocell applications, with target performance less than ± 15 ppb.

- Frequency performance for ITU-T G.823 and G.824 synchronization interface, as well as G.8261 PNT EEC, PNT PEC and CES interface specifications.

- Phase Synchronization performance for WCDMA-TDD, Mobile WiMAX, TD-SCDMA and CDMA2000 applications with target performance less than ± 1 μs phase alignment.

- Time Synchronization for UTC-traceability and GPS replacement.

- Meets the SONET/SDH jitter generation requirements up to OC-48/STM-16

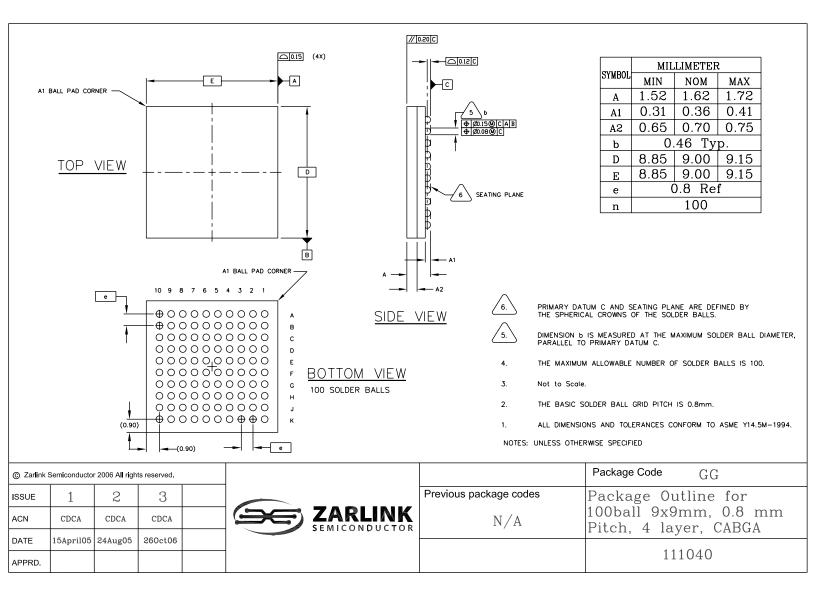

## Ordering Information

ZL30347GGG 100 Pin CABGA Trays

ZL30347GGG2 100 Pin CABGA\* Trays

\*Pb Free Tin/Silver/Copper

-40°C to +85°C

- Programmable output synthesizers (P0, P1) generate telecom clock frequencies from any multiple of 8 kHz up to 100 MHz

- Generates standard SONET/SDH clock rates (e.g., 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, 622.08 MHz) or Ethernet clock rates (e.g., 25 MHz, 50 MHz, 125 MHz, 156.25 MHz, 312.5 MHz) for synchronizing Gigabit Ethernet PHYs

- Client reference switching between multiple Servers

- Client holdover when Server packet connectivity is lost

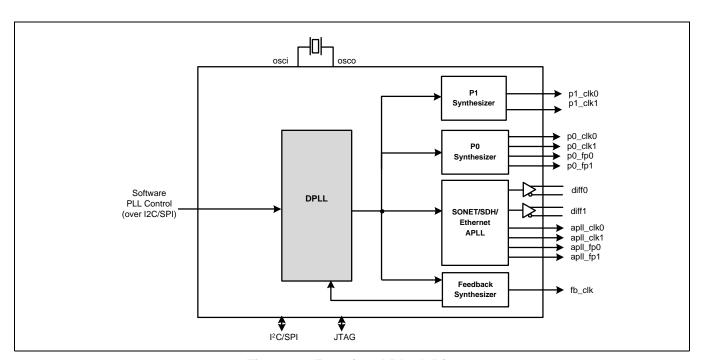

Figure 1 - Functional Block Diagram

ZL30347 Data Sheet

### **Applications**

- Integrated basestation reference clock for air interface for GSM, WCDMA, LTE and WiMAX macro, micro or femtocells

- Mobile Backhaul NID, edge router or access aggregation node

- EPON/GE-PON & GPON OLT

- EPON/GE-PON & GPON ONU/OLT

- DSLAM and RT-DSLAM

#### **Description**

The ZL30347 is a member of a family of footprint-compatible devices offering the full range of features required for timing and synchronization across packet networks. These devices focus on the Clock Recovery, Servo Mechanism and Clock Generation for Synchronization using IEEE-1588. They work seamlessly with Time Stamp solutions from all the major Switch/PHY NPU/CPU vendors.

These are the only commercially available single chip devices to offer both packet timing using IEEE-1588 Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE) capable of driving the physical layer clock with the required very low jitter. The ZL30347 offers a full Stratum 3 DPLL, ideal for Timing Card applications and supports clock recovery over L2 and L3 networks for all wireless applications.

# For more information about all Zarlink products visit our Web Site at

www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's l2C components conveys a license under the Philips I2C Patent rights to use these components in an I2C System, provided that the system conforms to the I2C Standard Specification as defined by Philips.

Zarlink, ZL, the Zarlink Semiconductor logo and the Legerity logo and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Zarlink Semiconductor Inc.

TECHNICAL DOCUMENTATION - NOT FOR RESALE