## ZL30155 Dual Channel Universal Clock Translator

Short Form Data Sheet

### Features

- Two independent clock channels

- Programmable synthesizers generate any clockrate from 1 kHz to 720 MHz

- Two precision synthesizers generate clocks with jitter below 0.7 ps RMS for 10 G PHYs

- Programmable digital PLLs synchronize to any clock rate from 1 kHz to 720 MHz

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

- Digital PLLs filter jitter from 14 Hz, 28 Hz, 56 Hz, 112 Hz, 224 Hz, 448 Hz or 896 Hz

- Automatic hitless reference switching and digital holdover on reference fail

- Four reference inputs configurable as single ended or differential

- · Eight LVPECL outputs and four LVCMOS outputs

#### **Ordering Information**

ZL30155GGG 100 Pin CABGA Trays ZL30155GGG2 100 Pin CABGA\* Trays

CABGA\* Trays

\*Pb Free Tin/Silver/Copper -40°C to +85°C

- Operates from a single crystal resonator or clock oscillator

- Configurable via SPI/I2C interface

## Applications

- 10 Gigabit linecards

- Synchronous Ethernet, 10GBASE-R and 10 GBASE-W

- OTN multiplexers and transponders

- SONET/SDH, Fibre Channel, XAUI

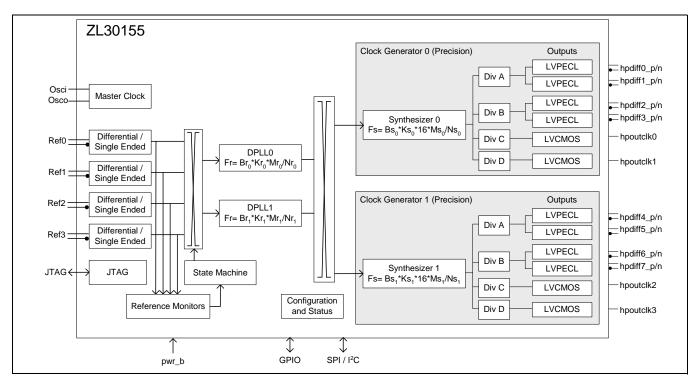

#### Figure 1 - Functional Block Diagram

1

Downloaded from Elcodis.com electronic components dist Sopyright 2010, Zarlink Semiconductor Inc. All Rights Reserved.

April 2010

## Description

The ZL30155 Dual Channel Universal Clock Translator, part of Zarlink's ClockCenter platform of Synchronous Clock devices, delivers industry leading synchronization performance for high-speed complex applications. The highly integrated and programmable solution provides translation from any input reference frequency to any output clock frequency with jitter performance that can directly drive 10G PHY devices.

The ZL30155 integrates 2 independent digital PLLs, accepts 4 input references and generates 12 programmable clock outputs. The highly integrated solution allows designers to replace multiple components with a single chip, simplifying design and reducing component count and power.

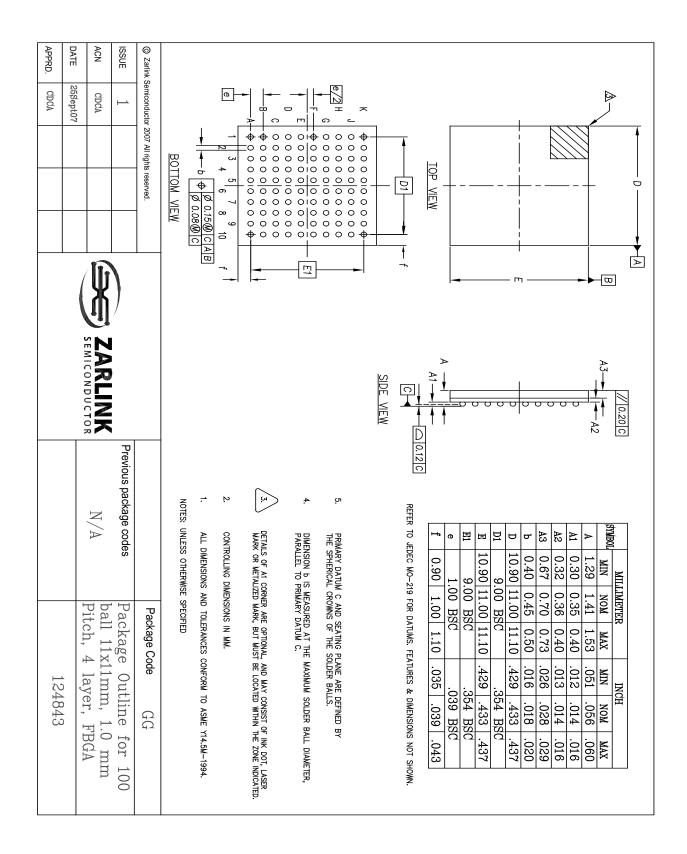

## **Mechanical Drawing**

# For more information about all Zarlink products visit our Web Site at

## www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's l2C components conveys a license under the Philips l2C Patent rights to use these components in an l2C System, provided that the system conforms to the l2C Standard Specification as defined by Philips.

Zarlink, ZL, the Zarlink Semiconductor logo and the Legerity logo and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Zarlink Semiconductor Inc.

TECHNICAL DOCUMENTATION - NOT FOR RESALE