# **MNDSPEED**<sup>®</sup>

### M21353

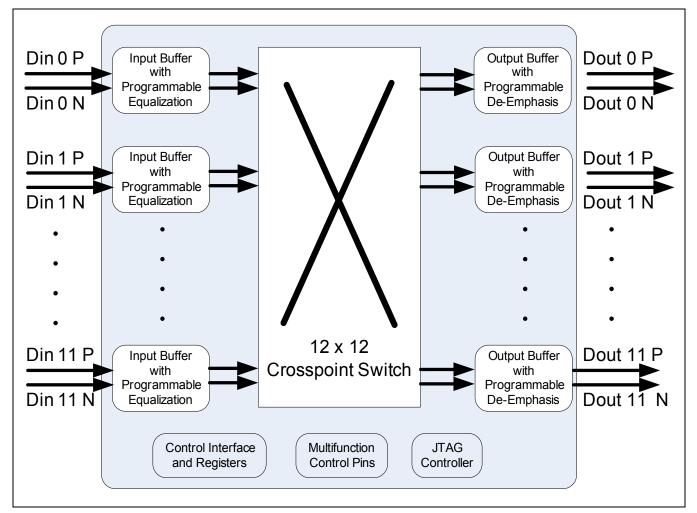

### 4.25 Gbps Twelve-Channel Backplane Equalizer and Driver with 12x12 Crosspoint Switch

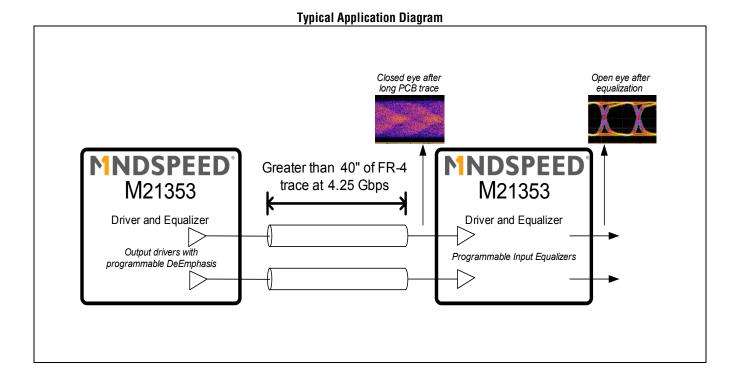

The M21353 is a twelve channel device designed to enable the transmission of multi-gigabit serial data through the most challenging environments. The device features twelve independent, programmable equalizers that equalize data at rates up to 4.25 Gbps. Control of the M21353 is provided through an I<sup>2</sup>C compatible software control interface. The M21353 can also self-configure from an external EEPROM without the need for a host processor. For compatibility with PCI-Express and S-ATA/SAS systems, the M21353 is designed with an electrical idle pass-through function to drive the differential output to the common mode level during OOB signaling. Boundary scan is provided for high-speed input and output pins, and the device is available in a 12x12 mm, 88 pin MLF package.

#### Features

- Programmable Equalization for greater than 40" of FR-4 PCB trace at 4.25 Gbps

- Supports electrical idle signaling for PCIe and OOB signaling for S-ATA/SAS

- Twelve channel programmable equalizer for data rates up to 4.25 Gbps

- Low power dissipation: 110 mW per channel, 1.3 W total power at 1.2V

- Up to 16 dB of input equalization and 6 dB of output deemphasis

- 12x12 mm, 88 pin MLF package

- Extended case temperature range (-20 °C to 85 °C)

- Integrated 12x12 Crosspoint Switch Matrix

#### Applications

| XAUI             | 3.125 Gbps  | _                              | —                            |

|------------------|-------------|--------------------------------|------------------------------|

| S-ATA/SAS        | 1.5 Gbps    | 3.0 Gbps                       | —                            |

| PCIe             | 2.5 Gbps    | _                              | —                            |

| Fibre<br>Channel | 1.0625 Gbps | 2.125 Gbps                     | 4.25 Gbps                    |

| Infiniband       | 2.5 Gbps    | _                              | —                            |

| SDI Video        | 270 Mbps    | 1.485 Gbps<br>1.485/1.001 Gbps | 2.97 Gbps<br>2.97/1.001 Gbps |

### **Ordering Information**

| Part Number                                                                                                                                                                                                                  | Package                      | Operating Case Temperature |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------|--|--|--|

| M21353G-13                                                                                                                                                                                                                   | 12x12 mm, 88 pin MLF package | -20 °C to 85 °C            |  |  |  |

| The M21353 is RoHS compliant. Refer to <b>http://www.mindspeed.com/web/support/environment/index.html</b> for additional information. Mindspeed RoHS compliant devices are backwards compatible with 225 °C reflow profiles. |                              |                            |  |  |  |

### **Revision History**

| Revision | Level    | Date         | Description                                                                                                                                                                   |

|----------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | Released | January 2009 | Updated for production release.                                                                                                                                               |

|          |          |              | The following specifications were modified in Table 1-3 and Table 1-4:                                                                                                        |

|          |          |              | <ul> <li>Power Consumption</li> <li>Input Launch Amplitude</li> <li>Rise/Fall Time</li> <li>Deterministic Jitter</li> <li>Random Jitter</li> <li>Propagation Delay</li> </ul> |

|          |          |              | Values for input equalization and output de-emphasis dynamic range were removed from Table 1-4.                                                                               |

|          |          |              | Channel to Channel skew was added to Table 1-4.                                                                                                                               |

|          |          |              | Figure 2-1 through Figure 2-11 were added.                                                                                                                                    |

|          |          |              | Default value of registers 41h-4Ch were modified to reflect the new default state. (Output buffers powered-down by default in M21453G-13.)                                    |

|          |          |              | Removed description of register address 04h - Register 04h is now a MSPD internal register.                                                                                   |

|          |          |              | Removed support for programmable interrupt pulse widths for xALARM signal in register 00h[3:0].                                                                               |

|          |          |              | Support for SDI video was added, see Section 5.8 for details.                                                                                                                 |

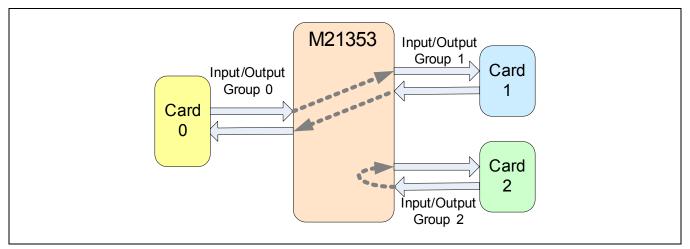

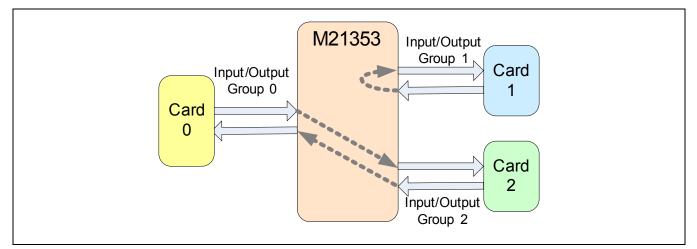

|          |          |              | Additional information on how to configure the crosspoint switch core was added in Section 5.9.                                                                               |

|          |          |              | Added etails on boundary scan support were in Section 5.11.                                                                                                                   |

|          |          |              | Added details on how to compute the correct seed value for the checksum register (address 01h) when using MIC mode in Section 5.13.                                           |

| А        | Advance  | May 2008     | Initial release.                                                                                                                                                              |

| Symbol                | Parameter                                                                                                                                       | Minimum | Maximum | Unit |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------|

| AVDDIO                | Analog I/O power supply voltage                                                                                                                 | —       | 2.1     | V    |

| AVDDCORE/<br>DVDDCORE | Core power supply voltage                                                                                                                       | —       | 1.5     | V    |

| DVDDIO                | Digital I/O power supply voltage                                                                                                                | —       | 3.6     | V    |

| Tst                   | Storage Temperature                                                                                                                             | -65     | 150     | °C   |

| Vesd                  | Electrostatic discharge voltage (HBM)                                                                                                           | —       | 2000    | V    |

| Vesd                  | Electrostatic discharge voltage (CDM)                                                                                                           | —       | 500     | V    |

| ·                     | evice beyond the minimum/maximum limits may cause permanent dama<br>e above table are stress limits only, and do not imply functional operation | 0       |         |      |

**Recommended Operating Conditions** Table 1-2.

| Symbol                | Parameter                        | Minimum | Typical            | Maximum | Unit |

|-----------------------|----------------------------------|---------|--------------------|---------|------|

| AVDDIO                | Analog I/O power supply voltage  | 1.14    | 1.2, 1.8           | 1.89    | V    |

| AVDDCORE/<br>DVDDCORE | Core power supply voltage        | 1.14    | 1.2                | 1.26    | V    |

| DVDDIO                | Digital I/O power supply voltage | 1.14    | 1.2, 1.8, 2.5, 3.3 | 3.47    | V    |

| Tc                    | Operating Case Temperature       | -20     |                    | 85      | °C   |

| Symbol   | Parameter                                        | Note | Minimum | Typical | Maximum | Unit |

|----------|--------------------------------------------------|------|---------|---------|---------|------|

| AIDDIO   | Analog I/O power supply current (AVDDIO = 1.2V)  | 1    | —       | 210     | 240     | mA   |

| AIDDIO   | Analog I/O power supply current (AVDDIO = 1.8V)  | 2    | —       | 390     | 475     | mA   |

| AIDDCORE | Analog core power supply current (AVDDIO = 1.2V) | 1    | —       | 850     | 1000    | mA   |

| AIDDCORE | Analog core power supply current (AVDDIO = 1.8V) | 2    | —       | 925     | 1200    | mA   |

| DIDDIO   | Digital I/O power supply current                 | —    | —       | 2       | —       | mA   |

| DVDDCORE | Digital core power supply current                | —    | —       | 3       | —       | mA   |

| Pdiss    | Total power dissipation (AVDDIO=1.2V)            | 1, 3 | —       | 1.3     | 1.6     | W    |

| Pdiss    | Total power dissipation (AVDDIO=1.8V)            | 2, 3 | —       | 1.8     | 2.4     | W    |

#### Table 1-3. Power Consumption Specifications

1. Valid with nominal (800 mVppd) output swing for all channels.

2. Valid with maximum (1500 mVppd) output swing for all channels.

3. Typical calculated with nominal current and voltage. Maximum calculated with maximum current and 5% over voltage.

Unless noted otherwise, specifications in this section are valid with AVDDIO = 1.8V, 25 °C case temperature, 800 mV differential input data swing, nominal (800 mVppd) output data swing, PRBS  $2^{15} - 1$  test pattern at 4.25 Gbps,  $R_L = 50\Omega$ , short cables and/or traces.

| Symbol          | Parameter                                                                                                    | Note    | Minimum       | Typical | Maximum       | Unit    |

|-----------------|--------------------------------------------------------------------------------------------------------------|---------|---------------|---------|---------------|---------|

| DR              | NRZ Data Rate                                                                                                | —       | 100           | _       | 4250          | Mbps    |

| Vin             | Input differential voltage swing (AC-Coupled), voltage measured at the device input                          | —       | 200           | —       | 2000          | mV      |

| VI              | Input launch amplitude (Voltage used to drive a signal across 40" of FR-4 trace)                             | _       | 500           | _       |               | mVppd   |

| VI              | Input launch amplitude (Voltage used to drive a signal across 40" of FR-4 trace, pathological video pattern) | _       | 700           | _       | _             | mVppd   |

| Rt              | PCML differential input impedance termination                                                                | _       | 80            | 100     | 120           | Ω       |

| Voh             | PCML single ended output logic-high                                                                          | —       | AVDDIO - 0.05 | —       | AVDDIO        | V       |

| Vod             | PCML p-p differential output swing                                                                           | 1,2,3,6 | 350           | _       | 1750          | mV      |

| Tr/Tf           | PCML output rise/fall time (20-80%)                                                                          | 6       | —             | 60      | —             | ps      |

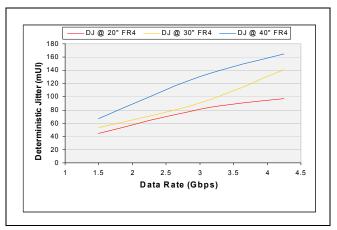

| DJ              | Deterministic output jitter                                                                                  | 4       | —             | 0.1     | 0.2           | UI      |

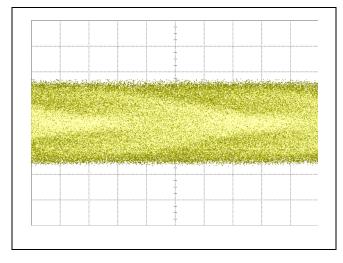

| RJ              | Random output jitter (RMS)                                                                                   | 4       | —             | 6       | 9             | mUI RMS |

| Tprop           | Propagation delay                                                                                            |         | —             | 1       |               | ns      |

| Tskew           | Channel to channel skew                                                                                      |         | _             | 300     | _             | ps      |

| V <sub>IH</sub> | CMOS Input logic high                                                                                        | _       | 0.85 x DVDDIO |         |               | V       |

| V <sub>IF</sub> | CMOS input logic floating state                                                                              | —       | 0.25 x DVDDIO | _       | 0.75 x DVDDIO | V       |

| V <sub>IL</sub> | CMOS input logic low                                                                                         | -       | —             | _       | 0.15 x DVDDIO | V       |

Table 1-4.

Input/Output Electrical Characteristics (1 of 2)

Unit V V

swing

|                 |                                                                                                                                                                             | •             | ,                   |                  |                      |         |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|------------------|----------------------|---------|

| Symbol          | Parameter                                                                                                                                                                   | Note          | Minimum             | Typical          | Maximum              | l       |

| V <sub>OH</sub> | CMOS output logic high                                                                                                                                                      | 5             | 0.85 x DVDDIO       | —                | —                    |         |

| V <sub>OL</sub> | CMOS output logic low                                                                                                                                                       | 5             | —                   | —                | 0.15 x DVDDIO        |         |

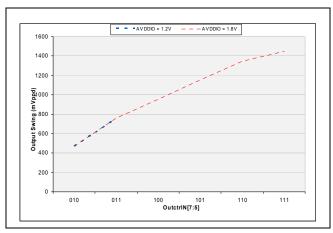

| 2. Output       | O must be 1.8V to achieve higher than 800 mV output sw<br>swing is specified with output de-emphasis disabled.<br>tput swing levels can be selected. Output swing increases | Ū             | ately 200 mV with 6 | each setting. Se | e Figure 2-6 for tyr | bical s |

| levels.         |                                                                                                                                                                             |               |                     | g                |                      |         |

| 4. Additiv      | e output jitter with minimal media length                                                                                                                                   |               |                     |                  |                      |         |

| 5. Two-w        | ire serial interface can drive 500 pF at 100 kHz and 400 kH                                                                                                                 | Hz, 100 pF at | 3.4 MHz.            |                  |                      |         |

Table 1-4.

Input/Output Electrical Characteristics (2 of 2)

Measured using a CID pattern with a minimum CID length of 10 bits.

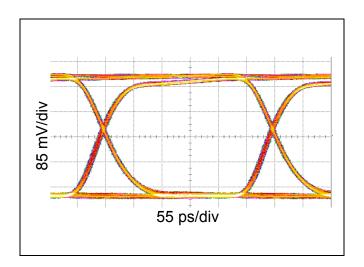

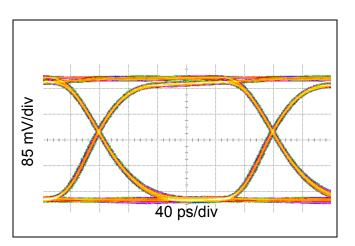

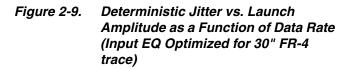

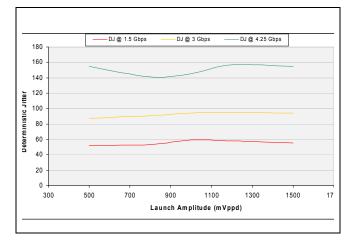

Unless noted otherwise, test conditions in this section are: AVDDIO = 1.8V, 25 °C case temperature, 800 mVppd input data swing, nominal (800 mVppd) output data swing PRBS  $2^{15}$  - 1 test pattern at 4.25 Gbps,  $R_L = 50\Omega$ , short traces and/or cables.

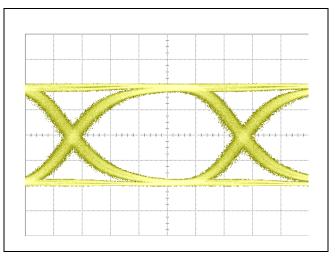

Figure 2-1. Eye Diagram at 3.125 Gbps

Figure 2-2. Eye Diagram at 4.25 Gbps

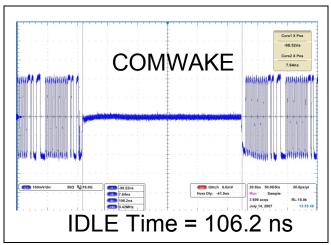

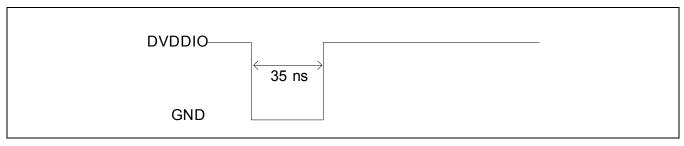

Figure 2-3. Output Waveform With COMWAKE OOB Signal

Figure 2-4. Deterministic Jitter vs. Data Rate as a Function of Trace Length

###

Figure 2-5. Eye Diagram After 40" of FR-4 Trace

*Figure 2-6. Differential Output Swing vs. OutctrIN*[7:5] Setting as a Function of *AVDDIO*

Figure 2-7. Eye Diagram after Equalizing 40" of FR-4 trace at 4.25 Gbps

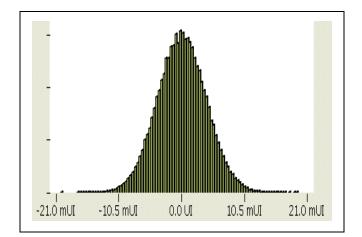

Figure 2-8. Random Jitter Distribution

### MNDSPEED<sup>°</sup>

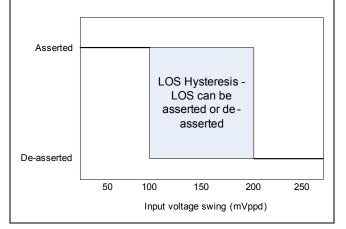

#### Figure 2-11. Typical LOS Assert/De-Assert Behavior

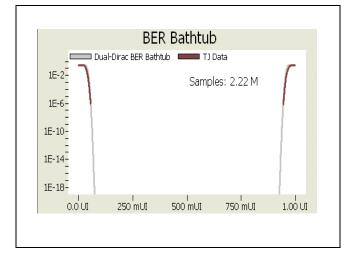

#### Figure 2-10. Bathtub Curve

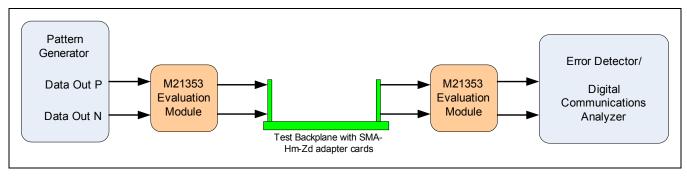

Figure 2-12. Input Equalization Test Setup Test Backplane

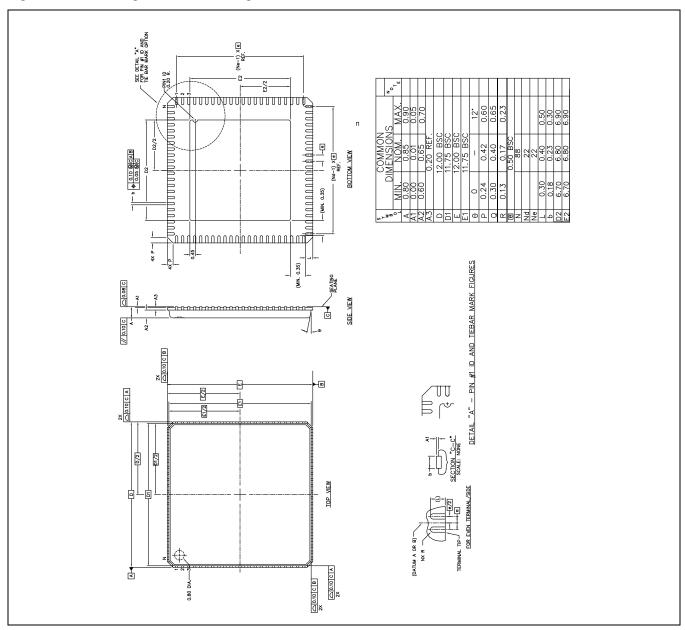

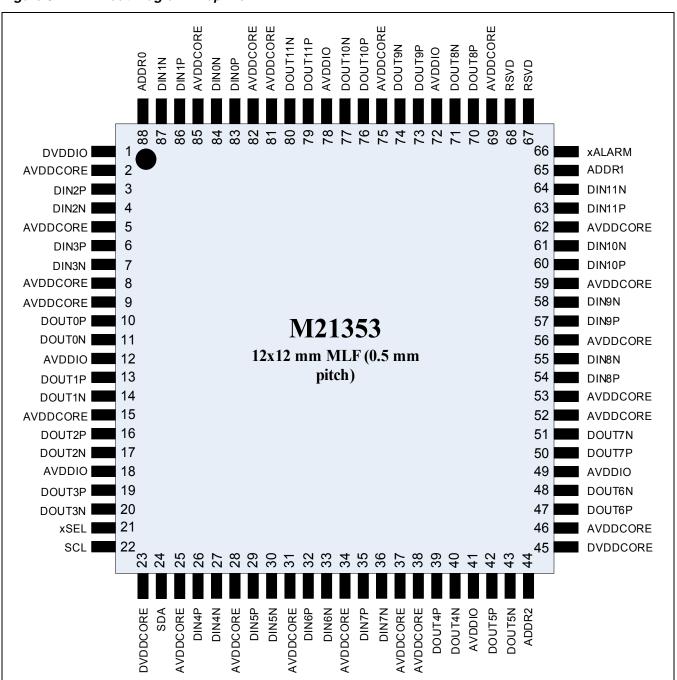

The M21353 is assembled in 12x12 mm, 88 pin MLF packages. The package paddle should be soldered to the ground plane to provide a GND connection and a thermal path for the device.

Figure 3-1. Package Outline Drawing

### Mindspeed Technologies<sup>®</sup>

### **MNDSPEED**°

Figure 3-2. Pinout Diagram - Top View

| Pin Name              | Pin Number(s)                                                                      | Pin Function                             | Pin Type            |

|-----------------------|------------------------------------------------------------------------------------|------------------------------------------|---------------------|

| AVDDIO                | 12,18,41, 49, 72, 78,                                                              | Analog IO Voltage Supply                 | Power               |

| DVDDIO                | 1                                                                                  | Digital IO Voltage Supply                | Power               |

| AVDDCORE              | 2, 5, 8, 9, 15, 25, 28, 31, 34, 37, 38, 46, 52, 53, 56, 59, 62, 69, 75, 81, 82, 85 | Analog Core Voltage Supply               | Power               |

| DVDDCORE              | 23, 45                                                                             | Digital Core Voltage Supply              | Power               |

| GND                   | Exposed pad on bottom of package                                                   | Device ground                            | Ground              |

| XSEL                  | 21                                                                                 | Hardware Strobe Pin                      | Control             |

| SCL                   | 22                                                                                 | 2 wire interface SCL pin                 | Control             |

| SDA                   | 24                                                                                 | 2 wire interface SDA pin                 | Control             |

| ADDR2                 | 44                                                                                 | 2 wire interface address select pin      | Control             |

| ADDR1                 | 65                                                                                 | 2 wire interface address select pin      | Control             |

| ADDR0                 | 88                                                                                 | 2 wire interface address select pin      | Control             |

| xalarm <sup>(1)</sup> | 66                                                                                 | Alarm output pin <sup>(1)</sup>          | Status - Open Drain |

| RSVD                  | 67, 68                                                                             | Do not connect for M21353 <sup>(2)</sup> | Mindspeed Reserved  |

| DINOP                 | 83                                                                                 | Channel 0 Input P                        | High-Speed Input    |

| DINON                 | 84                                                                                 | Channel O Input N                        | High-Speed Input    |

| DIN1P                 | 86                                                                                 | Channel 1 Input P                        | High-Speed Input    |

| DIN1N                 | 87                                                                                 | Channel 1 Input N                        | High-Speed Input    |

| DIN2P                 | 3                                                                                  | Channel 2 Input P                        | High-Speed Input    |

| DIN2N                 | 4                                                                                  | Channel 2 Input N                        | High-Speed Input    |

| DIN3P                 | 6                                                                                  | Channel 3 Input P                        | High-Speed Input    |

| DIN3N                 | 7                                                                                  | Channel 3 Input N                        | High-Speed Input    |

| DIN4P                 | 26                                                                                 | Channel 4 Input P                        | High-Speed Input    |

| DIN4N                 | 27                                                                                 | Channel 4 Input N                        | High-Speed Input    |

| DIN5P                 | 29                                                                                 | Channel 5 Input P                        | High-Speed Input    |

| DIN5N                 | 30                                                                                 | Channel 5 Input N                        | High-Speed Input    |

| DIN6P                 | 32                                                                                 | Channel 6 Input P                        | High-Speed Input    |

| DIN6N                 | 33                                                                                 | Channel 6 Input N                        | High-Speed Input    |

| DIN7P                 | 35                                                                                 | Channel 7 Input P                        | High-Speed Input    |

| DIN7N                 | 36                                                                                 | Channel 7 Input N                        | High-Speed Input    |

| DIN8P                 | 54                                                                                 | Channel 8 Input P                        | High-Speed Input    |

| DIN8N                 | 55                                                                                 | Channel 8 Input N                        | High-Speed Input    |

| DIN9P                 | 57                                                                                 | Channel 9 Input P                        | High-Speed Input    |

| DIN9N                 | 58                                                                                 | Channel 9 Input N                        | High-Speed Input    |

| DIN10P                | 60                                                                                 | Channel 10 Input P                       | High-Speed Input    |

| DIN10N                | 61                                                                                 | Channel 10 Input N                       | High-Speed Input    |

Table 3-1.M21353 Pin Descriptions (1 of 2)

| Pin Name | Pin Number(s) | Pin Function        | Pin Type          |

|----------|---------------|---------------------|-------------------|

| DIN11P   | 63            | Channel 11 Input P  | High-Speed Input  |

| DIN11N   | 64            | Channel 11 Input N  | High-Speed Input  |

| DOUTOP   | 10            | Channel 0 Output P  | High-Speed Output |

| DOUTON   | 11            | Channel 0 Output N  | High-Speed Output |

| DOUT1P   | 13            | Channel 1 Output P  | High-Speed Output |

| DOUT1N   | 14            | Channel 1 Output N  | High-Speed Output |

| DOUT2P   | 16            | Channel 2 Output P  | High-Speed Output |

| DOUT2N   | 17            | Channel 2 Output N  | High-Speed Output |

| DOUT3P   | 19            | Channel 3 Output P  | High-Speed Output |

| DOUT3N   | 20            | Channel 3 Output N  | High-Speed Output |

| DOUT4P   | 39            | Channel 4 Output P  | High-Speed Output |

| DOUT4N   | 40            | Channel 4 Output N  | High-Speed Output |

| DOUT5P   | 42            | Channel 5 Output P  | High-Speed Output |

| DOUT5N   | 43            | Channel 5 Output N  | High-Speed Output |

| DOUT6P   | 47            | Channel 6 Output P  | High-Speed Output |

| DOUT6N   | 48            | Channel 6 Output N  | High-Speed Output |

| DOUT7P   | 50            | Channel 7 Output P  | High-Speed Output |

| DOUT7N   | 51            | Channel 7 Output N  | High-Speed Output |

| DOUT8P   | 70            | Channel 8 Output P  | High-Speed Output |

| DOUT8N   | 71            | Channel 8 Output N  | High-Speed Output |

| DOUT9P   | 73            | Channel 9 Output P  | High-Speed Output |

| DOUT9N   | 74            | Channel 9 Output N  | High-Speed Output |

| DOUT10P  | 76            | Channel 10 Output P | High-Speed Output |

| DOUT10N  | 77            | Channel 10 Output N | High-Speed Output |

| DOUT11P  | 79            | Channel 11 Output P | High-Speed Output |

| DOUT11N  | 80            | Channel 11 Output N | High-Speed Output |

Table 3-1.M21353 Pin Descriptions (2 of 2)

Note:

1. xALARM is an open-drain output, and should be connected to an external pull-up resistor in system designs.

2. These pins are used for the REFCLK connection in the M21363. Mindspeed recommends that system PCBs for the M21353 include a refclk circuit if feasible to allow for the use of the M21363 on the same PCB.

## 4.0 Control Registers Map and Descriptions

### 4.1 Control Registers Map

| Table 4-1. | M21353 Register Summary Table (1 of 4) |

|------------|----------------------------------------|

|            |                                        |

| Address | Register<br>Name                    | D7<br>(MSB)         | D6                          | D5                       | D4                  | D3                     | D2                                 | D1                  | DO                  | Default<br>(Lane/<br>Group<br>mode) | R/W |

|---------|-------------------------------------|---------------------|-----------------------------|--------------------------|---------------------|------------------------|------------------------------------|---------------------|---------------------|-------------------------------------|-----|

| 00h     | Alarm Mode                          |                     | M                           | SPD                      | 1                   | xALARM<br>mode control |                                    |                     |                     |                                     | R/W |

| 01h     | Checksum                            |                     |                             |                          | Seed valu           | e for MIC checksum     |                                    |                     |                     | 55h/55h                             | R/W |

| 02h     | MIC Control                         |                     | MSPD                        |                          |                     | Identit                | fies number of devi                | ces in MIC m        | node                | 00h/00h                             | R/W |

| 03h     | Gen Config                          | Standby             | MSPD                        | Group<br>Switch          | Clear Alarm         | Strobe Mode            | MSPD Set Squelch Level             |                     |                     | 2Bh/2Bh                             | R/W |

| 05h     | Strobe                              | ICL Select          | xSel Mode                   |                          |                     | Software Strobe        |                                    |                     | 00h/00h             | R/W                                 |     |

| 06h     | Polarity Invert                     |                     | M                           | SPD                      |                     | Input 11<br>Polarity   | Input 10 Polarity                  | Input 9<br>Polarity | Input 8<br>Polarity | 00h/00h                             | R/W |

| 07h     | Polarity Invert                     | Input 7<br>Polarity | Input 6<br>Polarity         | Input 5<br>Polarity      | Input 4<br>Polarity | Input 3<br>Polarity    | Input 2 Polarity                   | Input 1<br>Polarity | Input 0<br>Polarity | 00h/00h                             | R/W |

| 08h*    | Active Switch<br>Config             |                     | Configuration for Output 11 |                          |                     |                        | Configuration for (                | Dutput 10           |                     | BAh/00h                             | R/W |

| 09h*    | Active Switch<br>Config             |                     | Configuratio                | n for Output             | 9                   |                        | Configuration for Output 8         |                     |                     | 98h/00h                             | R/W |

| 0Ah*    | Active Switch<br>Config             |                     | Configuratio                | n for Output             | 7                   |                        | Configuration for Output 6         |                     |                     | 32h/00h                             | R/W |

| 0Bh*    | Active Switch<br>Config             |                     | Configuratio                | n for Output             | 5                   |                        | Configuration for Output 4         |                     |                     | 10h/00h                             | R/W |

| 0Ch     | Active Switch<br>Config             |                     | Configuratio                | n for Output             | 3                   | Co                     | Configuration for Output 2/Group 2 |                     |                     | 76h/02h                             | R/W |

| 0Dh     | Active Switch<br>Config             | Con                 | figuration for              | <sup>•</sup> Output 1/Gi | roup 1              | Co                     | Configuration for Output 0/Group 0 |                     |                     | 54h/01h                             | R/W |

| 0Eh*    | Intermediate<br>Switch Config<br>#1 |                     | Configuratior               | n for Output             | 11                  |                        | Configuration for Output 10        |                     |                     | BAh/00h                             | R/W |

| OFh*    | Intermediate<br>Switch Config<br>#1 |                     | Configuratio                | n for Output             | 9                   |                        | Configuration for Output 8         |                     |                     | 98h/00h                             | R/W |

| 10h*    | Intermediate<br>Switch Config<br>#1 |                     | Configuratio                | n for Output             | 7                   |                        | Configuration for                  | Output 6            |                     | 32h/00h                             | R/W |

Mindspeed Technologies<sup>®</sup>

| Address | Register<br>Name                    | D7<br>(MSB)                | D6                                                    | D5            | D4                     | D3                         | D2                                 | D1                    | DO          | Default<br>(Lane/<br>Group<br>mode) | R/W |

|---------|-------------------------------------|----------------------------|-------------------------------------------------------|---------------|------------------------|----------------------------|------------------------------------|-----------------------|-------------|-------------------------------------|-----|

| 11h*    | Intermediate<br>Switch Config<br>#1 |                            | Configuratio                                          | n for Output  | 5                      | Configuration for Output 4 |                                    |                       |             | 10h/00h                             | R/W |

| 12h     | Intermediate<br>Switch Config<br>#1 |                            | Configuratio                                          | n for Output  | 3                      | Co                         | Configuration for Output 2/Group 2 |                       |             | 76h/02h                             | R/W |

| 13h     | Intermediate<br>Switch Config<br>#1 | Cont                       | figuration fo                                         | r Output 1/Gı | roup 1                 | Co                         | Configuration for Output O/Group O |                       |             | 54h/01h                             | R/W |

| 14h*    | Intermediate<br>Switch Config<br>#2 | (                          | Configuratio                                          | n for Output  | 11                     |                            | Configuration for Output 10        |                       |             | 32h/00h                             | R/W |

| 15h*    | Intermediate<br>Switch Config<br>#2 |                            | Configuration for Output 9 Configuration for Output 8 |               |                        |                            |                                    |                       | 10h/00h     | R/W                                 |     |

| 16h*    | Intermediate<br>Switch Config<br>#2 | Configuration for Output 7 |                                                       |               |                        | Configuration for Output 6 |                                    |                       | 76h/00h     | R/W                                 |     |

| 17h*    | Intermediate<br>Switch Config<br>#2 | Configuration for Output 5 |                                                       |               |                        | Configuration for Output 4 |                                    |                       | 54h/00h     | R/W                                 |     |

| 18h     | Intermediate<br>Switch Config<br>#2 |                            | Configuratio                                          | n for Output  | 3                      | Co                         | onfiguration for Output 2/Group 2  |                       |             | BAh/00h                             | R/W |

| 19h     | Intermediate<br>Switch Config<br>#2 | Cont                       | figuration fo                                         | r Output 1/Gı | roup 1                 | Co                         | nfiguration for Outp               | out 0/Group 0         |             | 98h/12h                             | R/W |

| 1Ah*    | Input Config A                      | Input 11 Co                | onfiguration                                          | Input 10 C    | onfiguration           | Input 9 C                  | Configuration                      | Input 8 Co            | nfiguration | FFh/00h                             | R/W |

| 1Bh*    | Input Config A                      | Input 7 Co                 | nfiguration                                           | Input 6 Co    | onfiguration           | Input 5 C                  | Configuration                      | Input 4 Co            | nfiguration | FFh/00h                             | R/W |

| 1Ch     | Input Config A                      | Input 3 Co                 | nfiguration                                           |               | oup 2 Config-<br>ation | Input 1/Grou               | p 1 Configuration                  | Input 0/Gro<br>figura |             | FFh/3Fh                             | R/W |

| 1Dh*    | Input 11<br>Equalization            |                            |                                                       |               |                        | 11 Equalization            |                                    |                       |             | 37h/00h                             | R/W |

| 1Eh*    | Input 10<br>Equalization            |                            |                                                       |               |                        | 10 Equalization            |                                    |                       |             | 37h/00h                             | R/W |

| 1Fh*    | Input 9<br>Equalization             |                            |                                                       |               |                        | t 9 Equalization           |                                    |                       |             | 37h/00h                             | R/W |

| 20h*    | Input 8<br>Equalization             |                            |                                                       |               |                        | t 8 Equalization           |                                    |                       |             | 37h/00h                             | R/W |

| 21h*    | Input 7<br>Equalization             |                            |                                                       |               |                        | t 7 Equalization           |                                    |                       |             | 37h/00h                             | R/W |

| 22h*    | Input 6<br>Equalization             |                            |                                                       |               |                        | t 6 Equalization           |                                    |                       |             | 37h/00h                             | R/W |

| 23h*    | Input 5<br>Equalization             |                            |                                                       |               | Inpu                   | t 5 Equalization           |                                    |                       |             | 37h/00h                             | R/W |

Table 4-1.M21353 Register Summary Table (2 of 4)

| Address | Register<br>Name        | D7<br>(MSB) | D6            | D5                         | D4       | D3                         | D2                      | D1                   | DO                    | Default<br>(Lane/<br>Group<br>mode) | R/W |

|---------|-------------------------|-------------|---------------|----------------------------|----------|----------------------------|-------------------------|----------------------|-----------------------|-------------------------------------|-----|

| 24h*    | Input 4<br>Equalization |             |               |                            | Input    | 4 Equalization             |                         |                      |                       | 37h/00h                             | R/W |

| 25h*    | Input 3<br>Equalization |             |               |                            | Input    | 3 Equalization             |                         |                      |                       | 37h/00h                             | R/W |

| 26h     | Input 2<br>Equalization |             |               |                            | Input/Gr | oup 2 Equalizat            | ion                     |                      |                       | 37h/37h                             | R/W |

| 27h     | Input 1<br>Equalization |             |               |                            | Input/Gr | oup 1 Equalizat            | ion                     |                      |                       | 37h/37h                             | R/W |

| 28h     | Input 0<br>Equalization |             |               |                            | Input/Gr | oup 0 Equalizat            | ion                     |                      |                       | 37h/37h                             | R/W |

| 35h*    | Input 11<br>Config B    | MS          | MSPD          |                            | M        | SPD                        | Input11 Squelch         | MSPD                 | Input11<br>EBI Enable | C0h/00h                             | R/W |

| 36h*    | Input 10<br>Config B    | MS          | MSPD          |                            | M        | SPD                        | Input10 Squelch         | MSPD                 | Input10<br>EBI Enable | C0h/00h                             | R/W |

| 37h*    | Input 9<br>Config B     | MSPD        |               | In9 LOS<br>Enable          | M        | SPD                        | Input9 Squelch          | MSPD                 | Input9 EBI<br>Enable  | C0h/00h                             | R/W |

| 38h*    | Input 8<br>Config B     | MS          | SPD           | In8 LOS<br>Enable          | M        | SPD                        | Input8 Squelch          | MSPD                 | Input8 EBI<br>Enable  | C0h/00h                             | R/W |

| 39h*    | Input 7<br>Config B     | MS          | SPD           | In7 LOS<br>Enable          | M        | SPD                        | Input7 Squelch          | MSPD                 | Input7 EBI<br>Enable  | C0h/00h                             | R/W |

| 3Ah*    | Input 6<br>Config B     | MS          | SPD           | In6 LOS<br>Enable          | M        | SPD                        | Input6 Squelch          | MSPD                 | Input6 EBI<br>Enable  | C0h/00h                             | R/W |

| 3Bh*    | Input 5<br>Config B     | MS          | SPD           | In5 LOS<br>Enable          | M        | SPD                        | Input5 Squelch          | MSPD                 | Input5 EBI<br>Enable  | C0h/00h                             | R/W |

| 3Ch *   | Input 4<br>Config B     | MS          | SPD           | In4 LOS<br>Enable          |          |                            |                         | Input4 EBI<br>Enable | C0h/00h               | R/W                                 |     |

| 3Dh*    | Input 3<br>Config B     | MS          | SPD           | In3 LOS<br>Enable          | M        | SPD                        | Input3 Squelch          | MSPD                 | Input3 EBI<br>Enable  | C0h/00h                             | R/W |

| 3Eh     | Input 2<br>Config B     | MS          | SPD           | In/Group2<br>LOS<br>Enable | M        | SPD                        | Input/Group2<br>Squelch | MSPD                 | Input2 EBI<br>Enable  | COh/COh                             | R/W |

| 3Fh     | Input 1<br>Config B     | MS          | SPD           | In/Group1<br>LOS<br>Enable | M        | SPD                        | Input/Group1<br>Squelch | MSPD                 | Input1 EBI<br>Enable  | C0h/C0h                             | R/W |

| 40h     | Input 0<br>Config B     | MS          | SPD           | In/Group0<br>LOS<br>Enable | M        | SPD                        | Input/Group0<br>Squelch | MSPD                 | Input0 EBI<br>Enable  | COh/COh                             | R/W |

| 41h*    | Output 11<br>Config     | 0           | utput 11 Swi  | ng                         | MSPD     | Out                        | tput 11 De-Emphasi      | S                    | MSPD                  | 00h/00h                             | R/W |

| 42h*    | Output 10<br>Config     | 0           | utput 10 Swi  | ng                         | MSPD     | Output 10 De-Emphasis MSPD |                         | MSPD                 | 00h/00h               | R/W                                 |     |

| 43h*    | Output 9 Config         | C           | )utput 9 Swii | ng                         | MSPD     | Ou                         | tput 9 De-Emphasis      | 3                    | MSPD                  | 00h/00h                             | R/W |

| 44h*    | Output 8 Config         | C           | )utput 8 Swii | ng                         | MSPD     | Ou                         | tput 8 De-Emphasis      | 3                    | MSPD                  | 00h/00h                             | R/W |

Table 4-1.M21353 Register Summary Table (3 of 4)

| Address | Register<br>Name                         | D7<br>(MSB)          | D6             | D5            | D4         | D3            | D2                                  | D1             | DO             | Default<br>(Lane/<br>Group<br>mode) | R/W |

|---------|------------------------------------------|----------------------|----------------|---------------|------------|---------------|-------------------------------------|----------------|----------------|-------------------------------------|-----|

| 45h*    | Output 7 Config                          | (                    | utput 7 Swir   | ng            | MSPD       | Ou            | Output 7 De-Emphasis                |                |                | 00h/00h                             | R/W |

| 46h*    | Output 6 Config                          | (                    | Output 6 Swing |               |            | Ou            | tput 6 De-Emphasis                  | 3              | MSPD           | 00h/00h                             | R/W |

| 47h*    | Output 5 Config                          | (                    | Output 5 Swing |               |            | Ou            | tput 5 De-Emphasis                  | 3              | MSPD           | 00h/00h                             | R/W |

| 48h*    | Output 4 Config                          | (                    | Output 4 Swing |               |            | Ou            | Output 4 De-Emphasis                |                |                | 00h/00h                             | R/W |

| 49h*    | Output 3 Config                          | Output 3 Swing       |                |               | MSPD       | Ou            | tput 3 De-Emphasis                  | MSPD           | 00h/00h        | R/W                                 |     |

| 4Ah     | Output 2 Config                          | Output/Group 2 Swing |                |               | MSPD       | Outpu         | Output/Group 2 De-Emphasis          |                |                | 00h/00h                             | R/W |

| 4Bh     | Output 1 Config                          | Output/Group 1 Swing |                |               | MSPD       | Outpu         | Output/Group 1 De-Emphasis          |                |                | 00h/00h                             | R/W |

| 4Ch     | Output 0 Config                          | Outp                 | out/Group 0 S  | Swing         | MSPD       | Outpu         | t/Group 0 De-Emph                   | MSPD           | 00h/00h        | R/W                                 |     |

| C3h     | LOS Alarm                                |                      | M              | SPD           |            | Input11 LOS   | Input10 LOS                         | Input9<br>LOS  | Input8<br>LOS  | N/A                                 | R   |

| C4h     | LOS Alarm                                | Input7<br>LOS        | Input6<br>LOS  | Input5<br>LOS | Input4 LOS | Input 3 LOS   | Input 2 LOS                         | Input 1<br>LOS | Input 0<br>LOS | N/A                                 | R   |

| FCh     | MIC Checksum                             |                      |                |               | Compute    | d Checksum Va | llue                                |                |                | 00h                                 | R   |

| FDh     | Chip Code                                |                      |                |               | M21        | 353 Chip Code |                                     |                |                | 20h                                 | R   |

| FEh     | Chip Revision                            |                      |                |               | M21353     | Revision Numb | Der                                 |                |                | **                                  | R   |

| FFh     | Master Reset                             |                      | Chip Reset     |               |            |               |                                     | 00h            | R/W            |                                     |     |

| U       | rs noted with a * a ister description fo |                      |                |               |            | ,             | abled by setting add<br>Iress FEh). | lress 03h[5]   | to Ob.         | 1                                   |     |

Table 4-1.M21353 Register Summary Table (4 of 4)

4.2 Control Registers Descriptions

#### Register Address: 00h

Description: Controls the behavior of the xAlarm pin when an alarm is asserted.

| Bit | Bit Description                                                                                                              | Default | R/W |

|-----|------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 7:4 | Reserved, set to 0000b                                                                                                       | 0000b   | R/W |

| 3   | 1: xALARM is static high or low depending on Alarm condition<br>0: xALARM toggles once with an interrupt pulse when asserted | Ob      | R/W |

| 2:0 | Reserved, set to 000b                                                                                                        | 000b    | R/W |

#### Register Address: 01h

#### Register Name: Checksum

**Description:** Used with MIC mode. The sum of the value of registers from 00h-4Ch must be equal to 2Eh for to compute a valid checksum after the EEPROM download.

| Bit | Bit Description     | Default | R/W |

|-----|---------------------|---------|-----|

| 7:0 | Checksum seed value | 55h     | R/W |

Downloaded from Elcodis.com electronic components distributor

Register Name: Alarm Mode

#### Register Address: 02h

Register Name: MIC Control

Description: Identifies the number of devices on the serial bus when MIC programming mode is used.

| Bit | Bit Description                                                                                                                                                | Default | R/W |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 7:4 | Reserved, set to 0000b                                                                                                                                         | 0000b   | R/W |

| 3:0 | 0000: No other devices on the serial bus<br>0001: 1 other device on the serial bus<br>:<br>1101: 13 other devices on the serial bus (maximum number supported) | 0000b   | R/W |

#### Register Address: 03h

#### Register Name: General Config

Description: Used to power up/power down device circuitry, configure crosspoint switching modes, clear alarms, and select squelch mode.

| Bit | Bit Description                                                                                                                                                                 | Default | R/W |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 7   | 0: Power up mode, normal operation<br>1: Power down mode                                                                                                                        | Ob      | R/W |

| 6   | Reserved, set to Ob                                                                                                                                                             | Ob      | R/W |

| 5   | 0: Lane Switch Mode<br>1: Group Switch Mode                                                                                                                                     | 1b      | R/W |

| 4   | 0: Normal operation<br>1: Clear global alarms                                                                                                                                   | Ob      | R/W |

| 3   | 0: Switch setting updated with software strobe (address 05h)<br>1: Switch setting updated with hardware xSel pin                                                                | 1b      | R/W |

| 2   | Reserved, set to Ob                                                                                                                                                             | Ob      | R/W |

| 1:0 | 00: Do not squelch<br>01: Output logic high on squelch<br>10: Output logic low on squelch<br>11: Output EBI level (common-mode) on squelch (recommended for AC coupled outputs) | 11b     | R/W |

#### Register Address: 05h Register Name: Strobe

**Description:** Configures the switch core setting changes.

| Bit | Bit Description                                                                                                                                                                                                          | Default | R/W |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 7   | 0: Selects ISC#1 as the active switch state upon a HW/SW strobe<br>1: Selects ISC#2 as the active switch state upon a HW/SW strobe                                                                                       | Ob      | R/W |

| 6   | 0: When the device is configured for HW strobe mode (address 03h, bit 3), ISC#1 becomes active switch setting when xSEL pin is H, ISC#2 becomes the active switch setting when xSEL pin is L                             | Ob      | R/W |

|     | 1: When the device is configured for HW strobe mode (address 03h, bit 3), A transition from H to L on xSEL pin updates the active switch setting (ISC#1 or ISC#2 as determined by bit 7 of address 05h)                  |         |     |

| 5:0 | 000000: Normal operation<br>010101: When the device is configured for SW strobe mode (address 03h, bit 3), Software strobe to<br>update the active switch setting (ISC#1 or ISC#2 as determined by bit 7 of address 05h) | 000000b | R/W |

#### Register Address: 06h, 07h Register Name: Polarity Invert

**Description:** Inverts the polarity of the high-speed inputs.

| Bit | Bit Description                                                                                                                                           | Default | R/W |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 7   | 0: Reserved, set to 0b (address 06h), normal polarity for input 7 (address 07h)<br>1: Not Used (address 06h), inverted polarity for input 7 (address 07h) | Ob      | R/W |

| 6   | 0: Reserved, set to 0b (address 06h), normal polarity for input 6 (address 07h)<br>1: Not Used (address 06h), inverted polarity for input 6 (address 07h) | Ob      | R/W |

| 5   | 0: Reserved, set to 0b (address 06h), normal polarity for input 5 (address 07h)<br>1: Not Used (address 06h), inverted polarity for input 5 (address 07h) | Ob      | R/W |

| 4   | 0: Reserved, set to 0b (address 06h), normal polarity for input 4 (address 07h)<br>1: Not Used (address 06h), inverted polarity for input 4 (address 07h) | Ob      | R/W |

| 3   | 0: Normal polarity for input 11 (address 06h), input 3 (address 07h)<br>1: Inverted polarity for input 11 (address 06h), input 3 (address 07h)            | Ob      | R/W |

| 2   | 0: Normal polarity for input 10 (address 06h), input 2 (address 07h)<br>1: Inverted polarity for input 10 (address 06h), input 2 (address 07h)            | Ob      | R/W |

| 1   | 0: Normal polarity for input 9 (address 06h), input 1 (address 07h)<br>1: Inverted polarity for input 9 (address 06h), input 1 (address 07h)              | Ob      | R/W |

| 0   | 0: Normal polarity for input 8 (address 06h), input 0 (address 07h)<br>1: Inverted polarity for input 8 (address 06h), input 0 (address 07h)              | Ob      | R/W |

#### Register Address: 08h, 09h, 0Ah, 0Bh, 0Ch, 0Dh

Register Name: Active Switch Configuration (ASC)

**Description:** Contains the active crosspoint switch configuration for output channels. In group switch mode, only addresses 0Ch and 0Dh are used.

| Bit | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Default<br>(Group Switch<br>Mode)                                                                                                                                      | Default<br>(Lane Switch Mode)                                                                                                                                                                 | R/W |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7:4 | Address 08h - Selects the input for output 11 (lane switch mode)<br>Address 09h - Selects the input for output 9 (lane switch mode)<br>Address 0Ah - Selects the input for output 7 (lane switch mode)<br>Address 0Bh - Selects the input for output 5 (lane switch mode)<br>Address 0Ch - Selects the input for output 3 (lane switch mode)<br>Address 0Dh - Selects the input for output 1 (lane switch mode)<br>or group 1 (group switch mode)                                   | Address 08h - 0000<br>Address 09h - 0000<br>Address 0Ah - 0000<br>Address 0Bh - 0000<br>Address 0Ch - 0000<br>Address 0Ch - 0000<br>(Input group 0)                    | Address 08h - 1011 (Input 11)<br>Address 09h - 1001 (Input 9)<br>Address 0Ah - 0011 (Input 3)<br>Address 0Bh - 0001 (Input 1)<br>Address 0Ch - 0111 (Input 7)<br>Address 0Dh - 0101 (Input 5) | R/W |

| 3:0 | Address 08h - Selects the input for output 10 (lane switch mode)<br>Address 09h - Selects the input for output 8 (lane switch mode)<br>Address 0Ah - Selects the input for output 6 (lane switch mode)<br>Address 0Bh - Selects the input for output 4 (lane switch mode)<br>Address 0Ch - Selects the input for output 2 (lane switch mode)<br>or group 2 (group switch mode)<br>Address 0Dh - Selects the input for output 0 (lane switch mode)<br>or group 0 (group switch mode) | Address 08h - 0000<br>Address 09h - 0000<br>Address 0Ah - 0000<br>Address 0Bh - 0000<br>Address 0Ch - 0010<br>(Input group 2)<br>Address 0Dh - 0001<br>(Input group 1) | Address 08h - 1010 (Input 10)<br>Address 09h - 1000 (Input 8)<br>Address 0Ah - 0010 (Input 2)<br>Address 0Bh - 0000 (Input 0)<br>Address 0Ch - 0110 (Input 6)<br>Address 0Dh - 0100 (Input 4) | R/W |

#### Register Address: OEh, OFh, 10h, 11h, 12h, 13h

**Register Name:** Intermediate Switch Configuration #1 (ISC #1)

Description: Contains ISC #1 for output channels. In group switch mode, only addresses 12h and 13h are used.

| Bit | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Default<br>(Group Switch<br>Mode)                                                                                                                                      | Default<br>(Lane Switch Mode)                                                                                                                                                                 | R/W |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7:4 | Address 0Eh - Selects the input for output 11 (lane switch mode)<br>Address 0Fh - Selects the input for output 9 (lane switch mode)<br>Address 10h - Selects the input for output 7 (lane switch mode)<br>Address 11h - Selects the input for output 5 (lane switch mode)<br>Address 12h - Selects the input for output 3 (lane switch mode)<br>Address 13h - Selects the input for output 1 (lane switch mode)<br>or group 1 (group switch mode)                                   | Address 0Eh - 0000<br>Address 0Fh - 0000<br>Address 10h - 0000<br>Address 11h - 0000<br>Address 12h - 0000<br>Address 13h - 0000<br>(Input group 0)                    | Address 0Eh - 1011 (Input 11)<br>Address 0Fh - 1001 (Input 9)<br>Address 10h - 0011 (Input 3)<br>Address 11h - 0001 (Input 1)<br>Address 12h - 0111 (Input 7)<br>Address 13h - 0101 (Input 5) | R/W |

| 3:0 | Address 0Eh - Selects the input for output 10 (lane switch mode)<br>Address 0Fh - Selects the input for output 8 (lane switch mode)<br>Address 10h - Selects the input for output 6 (lane switch mode)<br>Address 11h - Selects the input for output 4 (lane switch mode)<br>Address 12h - Selects the input for output 2 (lane switch mode)<br>or group 2 (group switch mode)<br>Address 13h - Selects the input for output 0 (lane switch mode)<br>or group 0 (group switch mode) | Address 0Eh - 0000<br>Address 0Fh - 0000<br>Address 10h - 0000<br>Address 11h - 0000<br>Address 12h - 0010<br>(Input group 2)<br>Address 13h - 0001<br>(Input group 1) | Address 0Eh - 1010 (Input 10)<br>Address 0Fh - 1000 (Input 8)<br>Address 10h - 0010 (Input 2)<br>Address 11h - 0000 (Input 0)<br>Address 12h - 0110 (Input 6)<br>Address 13h - 0100 (Input 4) | R/W |

Register Address: 14h, 15h, 16h, 17h, 18h, 19h

Register Name: Intermediate Switch Configuration #2 (ISC #2)

**Description:** Contains ISC #2 for output channels. In group switch mode, only addresses 18h and 19h are used.

| Bit | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Default<br>(Group Switch<br>Mode)                                                                                                                                      | Default<br>(Lane Switch Mode)                                                                                                                                                                 | R/W |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7:4 | Address 14h - Selects the input for output 11 (lane switch mode)<br>Address 15h - Selects the input for output 9 (lane switch mode)<br>Address 16h - Selects the input for output 7 (lane switch mode)<br>Address 17h - Selects the input for output 5 (lane switch mode)<br>Address 18h - Selects the input for output 3 (lane switch mode)<br>Address 19h - Selects the input for output 1 (lane switch mode)<br>or group 1 (group switch mode)                                   | Address 14h - 0000<br>Address 15h - 0000<br>Address 16h - 0000<br>Address 17h - 0000<br>Address 18h - 0000<br>Address 19h - 0000<br>(Input group 0)                    | Address 14h - 0011 (Input 3)<br>Address 15h - 0001 (Input 1)<br>Address 16h - 0111 (Input 7)<br>Address 17h - 0101 (Input 5)<br>Address 18h - 1011 (Input 11)<br>Address 19h - 1001 (Input 9) | R/W |

| 3:0 | Address 14h - Selects the input for output 10 (lane switch mode)<br>Address 15h - Selects the input for output 8 (lane switch mode)<br>Address 16h - Selects the input for output 6 (lane switch mode)<br>Address 17h - Selects the input for output 4 (lane switch mode)<br>Address 18h - Selects the input for output 2 (lane switch mode)<br>or group 2 (group switch mode)<br>Address 19h - Selects the input for output 0 (lane switch mode)<br>or group 0 (group switch mode) | Address 14h - 0000<br>Address 15h - 0000<br>Address 16h - 0000<br>Address 17h - 0000<br>Address 17h - 0010<br>(Input group 2)<br>Address 19h - 0001<br>(Input group 1) | Address 14h - 0010 (Input 2)<br>Address 15h - 0000 (Input 0)<br>Address 16h - 0110 (Input 6)<br>Address 17h - 0100 (Input 4)<br>Address 18h - 1010 (Input 10)<br>Address 19h - 1000 (Input 8) | R/W |

#### Register Address: 1Ah, 1Bh, 1Ch

Register Name: Input configuration A

Description: Configures buffers for high-speed inputs. In group switch mode, only address 1Ch is used.

| Bit | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Default | R/W |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|

| 7:6 | 00: Input 11 (address 1Ah), input 7 (address 1Bh), input 3 (address 1Ch) powered down with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>01: Input 11 (address 1Ah), input 7 (address 1Bh), input 3 (address 1Ch) powered down with source 50 $\Omega$ single-ended (100 $\Omega$ differential) termination<br>10: Input 11 (address 1Ah), input 7 (address 1Bh), input 3 (address 1Ch) powered on with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>11: Input 11 (address 1Ah), input 7 (address 1Bh), input 3 (address 1Ch) powered on with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>11: Input 11 (address 1Ah), input 7 (address 1Bh), input 3 (address 1Ch) powered on with source 50 $\Omega$ single-ended (100 $\Omega$ differential) termination | 11      | R/W |

| 5:4 | 00: Input 10 (address 1Ah), input 6 (address 1Bh), input 2 (address 1Ch) powered down with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>01: Input 10 (address 1Ah), input 6 (address 1Bh), input 2 (address 1Ch) powered down with source 50 $\Omega$ single-ended (100 $\Omega$ differential) termination<br>10: Input 10 (address 1Ah), input 6 (address 1Bh), input 2 (address 1Ch) powered on with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>11: Input 10 (address 1Ah), input 6 (address 1Bh), input 2 (address 1Ch) powered on with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>11: Input 10 (address 1Ah), input 6 (address 1Bh), input 2 (address 1Ch) powered on with source 50 $\Omega$ single-ended (100 $\Omega$ differential) termination | 11      | R/W |

| 3:2 | 00: Input 9 (address 1Ah), input 5 (address 1Bh), input 1 (address 1Ch) powered down with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>01: Input 9 (address 1Ah), input 5 (address 1Bh), input 1 (address 1Ch) powered down with source 50 $\Omega$ single-ended (100 $\Omega$ differential) termination<br>10: Input 9 (address 1Ah), input 5 (address 1Bh), input 1 (address 1Ch) powered on with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>10: Input 9 (address 1Ah), input 5 (address 1Bh), input 1 (address 1Ch) powered on with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>11: Input 9 (address 1Ah), input 5 (address 1Bh), input 1 (address 1Ch) powered on with source 50 $\Omega$ single-ended (100 $\Omega$ differential) termination      | 11      | R/W |

| 1:0 | 00: Input 8 (address 1Ah), input 4 (address 1Bh), input 0 (address 1Ch) powered down with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>01: Input 8 (address 1Ah), input 4 (address 1Bh), input 0 (address 1Ch) powered down with source 50 $\Omega$ single-ended (100 $\Omega$ differential) termination<br>10: Input 8 (address 1Ah), input 4 (address 1Bh), input 0 (address 1Ch) powered on with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>10: Input 8 (address 1Ah), input 4 (address 1Bh), input 0 (address 1Ch) powered on with high impedance (>100 k $\Omega$ single ended, 100 $\Omega$ differential) termination<br>11: Input 8 (address 1Ah), input 4 (address 1Bh), input 0 (address 1Ch) powered on with source 50 $\Omega$ single-ended (100 $\Omega$ differential) termination      | 11      | R/W |

#### Register Address: 1Dh, 1Eh, 1Fh, 20h, 21h, 22h, 23h, 24h, 25h, 26h, 27h, 28h

Register Name: Input Equalization

**Description:** Sets the equalization for input 11 (address 1Dh), input 10 (address 1Eh), input 9 (address 1Fh), input 8 (address 20h), input 7 (address 21h), input 6 (address 22h), input 5 (address 23h), input 4(address 24h), input 3 (address 25h), input 2/Group 2 (address 26h), input 1/Group 1 (address 27h), input 0/Group 0 (address 28h). In group mode, only addresse 26h, 27h, and 28h are used.

| Bit | Bit Description                                 | Default | R/W |

|-----|-------------------------------------------------|---------|-----|

| 7:0 | 00h: Equalization level 1—Minimum Equalization  | 37h     | R/W |

|     | 20h: Equalization level 2                       |         |     |

|     | 11h: Equalization level 3                       |         |     |

|     | 21h: Equalization level 4                       |         |     |

|     | 31h: Equalization level 5                       |         |     |

|     | A1h: Equalization level 6                       |         |     |

|     | 29h: Equalization level 7                       |         |     |

|     | 33h: Equalization level 8                       |         |     |

|     | 37h: Equalization level 9                       |         |     |

|     | 45h: Equalization level 10                      |         |     |

|     | 59h: Equalization level 11                      |         |     |

|     | 5Eh: Equalization level 12                      |         |     |

|     | 6Eh: Equalization level 13                      |         |     |

|     | 7Fh: Equalization level 14                      |         |     |

|     | FAh: Equalization level 15                      |         |     |

|     | FFh: Equalization level 16—Maximum Equalization |         |     |

Register Address: 35h, 36h, 37h, 38h, 39h, 3Ah, 3Bh, 3Ch, 3Dh, 3Eh, 3Fh, 40h

#### Register Name: Input configuration B

**Description:** Configures the LOS, squelch, and EBI functionality for input 11 (address 35h), input 10 (address 36h), input 9 (address 37h), input 8 (address 38h), input 7 (address 39h), input 6 (address 3Ah), input 5 (address 3Bh), input 4 (address 3Ch), input 3 (address 3Dh), input 2/group (address 3Eh), input 1/group (address 3Fh), input 0/group (address 40h). In group switch mode, only addresses 3Eh, 3Fh, and 40h are used.

| Bit | Bit Description                                                     | Default | R/W |

|-----|---------------------------------------------------------------------|---------|-----|

| 7:6 | Reserved, set to 11b                                                | 11b     | R/W |

| 5   | 0: LOS Enabled<br>1: LOS Disabled                                   | Ob      | R/W |

| 4:3 | Reserved, set to 00b                                                | 00b     | R/W |

| 2   | 0: Normal operation<br>1: Force squelch on input channel            | Ob      | R/W |

| 1   | Reserved, set to Ob                                                 | Ob      | R/W |

| 0   | 0: Disable EBI pass through mode<br>1: Enable EBI pass through mode | Ob      | R/W |

Register Address: 41h, 42h, 43h, 44h, 45h, 46h, 47h, 48h, 49h, 4Ah, 4Bh, 4Ch

Register Name: Output configuration

Description: Configures the output swing and de-emphasis for output 11 (address 41h), output 10 (address 42h), output 9 (address 43h), output 8