# CMOS ST-BUS™ FAMILY

# MT89L80

# SEMICONDUCTOR

## Digital Switch Advance Information

# Features

- 3.3 volt supply

- 5V tolerant inputs and TTL compatible outputs.

- 256 x 256 channel non-blocking switch

- Accepts serial streams at 2.048Mb/s

- Per-channel three-state control

- Patented per channel message mode

- Non-multiplexed microprocessor interface

- Mitel ST-BUS compatible

- Low power consumption: typical 15mW

- Pin compatible with the MT8980DP

## Applications

- Key telephone systems

- PBX systems

- Small and medium voice switching systems

DS5196 ISSUE 2 September 1999

Ordering Information

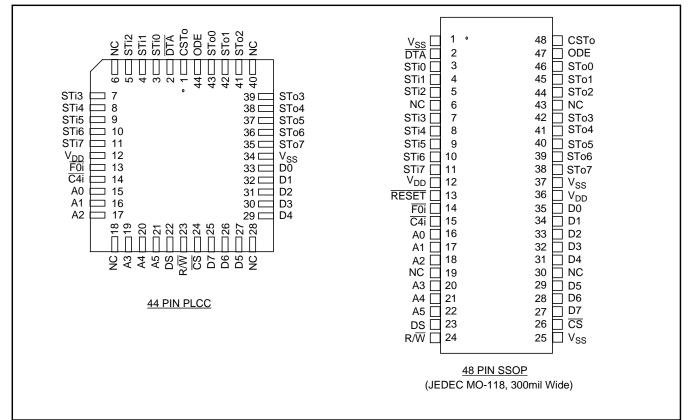

MT89L80AP 44 Pin PLCC MT89L80AN 48 Pin SSOP

-40°C to +85°C

# Description

This VLSI CMOS device is designed for switching PCM-encoded voice or data, under microprocessor control, in a modern digital exchange, PBX or Central Office. It provides simultaneous connections for up to 256 64 kbit/s channels. Each of the eight serial inputs and outputs consist of 32 64 kbit/s channels multiplexed to form a 2048 kbit/s ST-BUS stream. In addition, the MT89L80 provides microprocessor read and write access to individual ST-BUS channels.

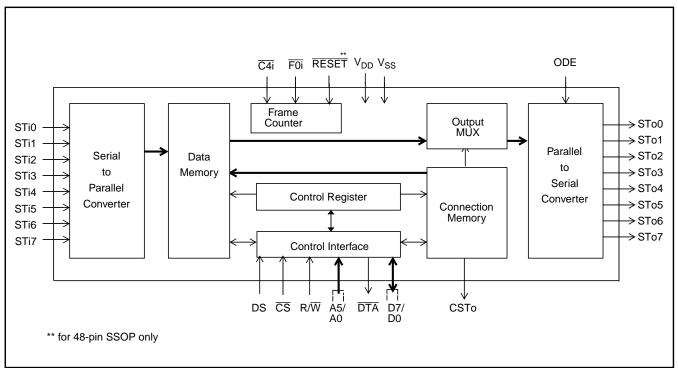

Figure 1 - Functional Block Diagram

## **Pin Description**

| Piı        | Pin #      |          |                                                                                                                                                                                                                                                                                                                                                                     |

|------------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44<br>PLCC | 48<br>SSOP | Name     | Description                                                                                                                                                                                                                                                                                                                                                         |

| 2          | 2          | DTA      | <b>Data Acknowledgment</b> (5V Tolerant Three-state Output). This active low output indicates that a data bus transfer is complete. A pull-up resistor is required at this output.                                                                                                                                                                                  |

| 3-5        | 3-5        | STi0-2   | <b>ST-BUS Inputs 0 to 2</b> (5V-tolerant Inputs). Serial data input streams. These streams have data rates of 2.048Mbit/s with 32 channels.                                                                                                                                                                                                                         |

| 7-11       | 7-11       | STi3-7   | <b>ST-BUS Inputs 3 to 7</b> (5V-tolerant Inputs). Serial data input streams. These streams may have data rates of 2.048Mbit/s with 32channels.                                                                                                                                                                                                                      |

| 12         | 12,36      | $V_{DD}$ | +3.3 Volt Power Supply.                                                                                                                                                                                                                                                                                                                                             |

|            | 13         | RESET    | <b>Device Reset</b> (5v-tolerant input). This pin is only available for the 48-pin SSOP package. This active low input puts the device in its reset state. It clears the internal counters and registers. All ST-BUS outputs are set to the high impedance state. In normal operation. The RESET pin must be held low for a minimum of 100nsec to reset the device. |

| 13         | 14         | F0i      | <b>Frame Pulse</b> (5V-tolerant Input). This is the input for the frame synchronization pulse for the 2048 kbit/s ST-BUS streams. A low on this input causes the internal counter to reset on the next negative transition of $\overline{C4i}$ .                                                                                                                    |

| 14         | 15         | C4i      | <b>4.096 MHz Clock</b> (5V-tolerant Input). ST-BUS bit cell boundaries lie on the alternate falling edges of this clock.                                                                                                                                                                                                                                            |

| 15-17      | 16-18      | A0-2     | Address 0-2 / Input Streams 8-10 (5V-tolerant Input). These are the inputs for the address lines on the microprocessor interface.                                                                                                                                                                                                                                   |

# Pin Description (continued)

| Pin #            |                  |                 |                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|------------------|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 44<br>PLCC       | 48<br>SSOP       | Name            | Description                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 19-21            | 20-22            | A3-5            | Address 3-5 / Input Streams 11-13 (5V-tolerant Input). These are the inputs for the address lines on the microprocessor interface.                                                                                                                                                                                                   |  |  |  |  |

| 22               | 23               | DS              | <b>Data Strobe</b> (5V-tolerant Input). This is the input for the active high data strobe on the microprocessor interface.                                                                                                                                                                                                           |  |  |  |  |

| 23               | 24               | R/W             | <b>Read/Write</b> (5V-tolerant Input). This is the input for the read/write signal on the microprocessor interface - high for read, low for write.                                                                                                                                                                                   |  |  |  |  |

| 24               | 26               | CS              | <b>Chip Select</b> (5V-tolerant Input). This is the input for the active low chip select on the microprocessor interface                                                                                                                                                                                                             |  |  |  |  |

| 25-27            | 27-29            | D7-D5           | <b>Data Bus</b> (5V-tolerant I/O): These are the bidirectional data pins on the microprocessor interface.                                                                                                                                                                                                                            |  |  |  |  |

| 29-33            | 31-35            | D4-D0           | <b>Data Bus</b> (5V-tolerant I/O): These are the bidirectional data pins on the microprocessor interface.                                                                                                                                                                                                                            |  |  |  |  |

| 34               | 1,<br>25,37      | V <sub>SS</sub> | Ground.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 35-39            | 38-42            | STo7-3          | <b>ST-BUS Outputs 7 to 3</b> (5V-Tolerant Three-state Outputs). These are the pins for the eight 2048 kbit/s ST-BUS output streams.                                                                                                                                                                                                  |  |  |  |  |

| 41-43            | 44-46            | STo2-0          | <b>ST-BUS Outputs 2to 0</b> (5V-Tolerant Three-state Outputs). These are the pins for the eight 2048kbit/s ST-BUS output streams.                                                                                                                                                                                                    |  |  |  |  |

| 44               | 47               | ODE             | <b>Output Drive Enable</b> (5V-tolerant Input). If this input is held high, the STo0-STo7 output drivers function normally. If this input is low, the STo0-STo7 output drivers go into their high impedance state. <b>NB:</b> Even when ODE is high, channels on the STo0-STo7 outputs can go high impedance under software control. |  |  |  |  |

| 1                | 48               | CSTo            | <b>Control ST-BUS Output</b> (5V-Tolerant Output). Each frame of 256 bits on this ST-BUS output contains the values of bit 1 in the 256 locations of the Connection Memory High.                                                                                                                                                     |  |  |  |  |

| 6, 18,<br>28, 40 | 6, 19,<br>30, 43 | NC              | No Connection.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

# **Functional Description**

In recent years, there has been a trend in telephony towards digital switching, particularly in association with software control. Simultaneously, there has been a trend in system architectures towards distributed processing or multi-processor systems.

In accordance with these trends, MITEL has devised the ST-BUS (Serial Telecom Bus). This bus architecture can be used both in software-controlled digital voice and data switching, and for interprocessor communications. The uses in switching and in interprocessor communications are completely integrated to allow for a simple general purpose architecture appropriate for the systems of the future.

The serial streams of the ST-BUS operate continuously at 2048 kbit/s and are arranged in 125 µs wide frames which contain 32 8-bit channels. MITEL manufactures a number of devices which interface to the ST-BUS; a key device being the MT89L80 chip.

The MT89L80 can switch data from channels on ST-BUS inputs to channels on ST-BUS outputs, and simultaneously allows its controlling microprocessor to read channels on ST-BUS inputs or write to channels on ST-BUS outputs (Message Mode). To the microprocessor, the MT89L80 looks like a memory peripheral. The microprocessor can write to the MT89L80 to establish switched connections between input ST-BUS channels and output ST-BUS channels, or to transmit messages on output ST-BUS channels. By reading from the MT89L80, the microprocessor can receive messages from ST-BUS input channels or check which switched connections have already been established.

By integrating both switching and interprocessor communications, the MT89L80 allows systems to use distributed processing and to switch voice or data in an ST-BUS architecture.

#### **Hardware Description**

Serial data at 2048 kbit/s is received at the eight ST-BUS inputs (STi0 to STi7), and serial data is transmitted at the eight ST-BUS outputs (STo0 to STo7). Each serial input accepts 32 channels of digital data, each channel containing an 8-bit word which may represent a PCM-encoded analog/voice sample as provided by a codec (e.g., MITEL's MT8964).

This serial input word is converted into parallel data and stored in the 256 X 8 Data Memory. Locations in the Data Memory are associated with particular channels on particular ST-BUS input streams. These locations can be read by the microprocessor which controls the chip.

Locations in the Connection Memory, which is split into high and low parts, are associated with particular ST-BUS output streams. When a channel is due to be transmitted on an ST-BUS output, the data for the channel can either be switched from an ST-BUS input or it can originate from the microprocessor. If the data is switched from an input, then the contents of the Connection Memory Low location associated with the output channel is used to address the Data Memory. This Data Memory address corresponds to the channel on the input ST-BUS stream on which the data for switching arrived. If the data for the output channel originates from the microprocessor (Message Mode), then the contents of the Connection Memory Low location associated with the output channel are output directly, and this data is output repetitively on the channel once every frame until the microprocessor intervenes.

The Connection Memory data is received, via the Control Interface, at D7 to D0. The Control Interface also receives address information at A5 to A0 and handles the microprocessor control signals  $\overline{CS}$ ,  $\overline{\text{DTA}}$ , R/W and DS. There are two parts to any address in the Data Memory or Connection Memory.

| A5 | A4 | A3 | A2 | A1 | A0 | Hex Address | Location                |

|----|----|----|----|----|----|-------------|-------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 00 - 1F     | Control Register *      |

| 1  | 0  | 0  | 0  | 0  | 0  | 20          | Channel 0 <sup>†</sup>  |

| 1  | 0  | 0  | 0  | 0  | 1  | 21          | Channel 1 <sup>†</sup>  |

| •  | •  | •  | •  | •  | •  | •           | •                       |

| •  | •  | •  | •  | •  | •  | •           | •                       |

| •  | •  | •  | •  | •  | •  | •           | •                       |

| 1  | 1  | 1  | 1  | 1  | 1  | 3F          | Channel 31 <sup>†</sup> |

<sup>1</sup> Memory and stream are specified by the contents of the Control Register.

The higher order bits come from the Control Register, which may be written to or read from via the Control Interface. The lower order bits come from the address lines directly.

The Control Register also allows the chip to broadcast messages on all ST-BUS outputs (i.e., to put every channel into Message Mode), or to split the memory so that reads are from the Data Memory and writes are to the Connection Memory Low. The Connection Memory High determines whether individual output channels are in Message Mode, and allows individual output channels to go into a high-impedance state, which enables arrays of MT89L80s to be constructed. It also controls the CSTo pin.

All ST-BUS timing is derived from the two signals  $\overline{C4i}$  and  $\overline{F0i}$ .

#### **Software Control**

The address lines on the Control Interface give access to the Control Register directly or, depending on the contents of the Control Register, to the High or Low sections of the Connection Memory or to the Data Memory. If address line A5 is low, then the Control Register is addressed regardless of the other address lines (see Fig. 3). If A5 is high, then the address lines A4-A0 select the memory location corresponding to channel 0-31 for the memory and stream selected in the Control Register.

The data in the Control Register consists of mode control bits, memory select bits, and stream address bits (see Fig. 4). The memory select bits allow the Connection Memory High or Low or the Data Memory to be chosen, and the stream address bits define one of the ST-BUS input or output streams.

Bit 7 of the Control Register allows split memory operation - reads are from the Data Memory and writes are to the Connection Memory Low.

The other mode control bit, bit 6, puts every output channel on every output stream into active Message Mode; i.e., the contents of the Connection Memory Low are output on the ST-BUS output streams once every frame unless the ODE pin is low. In this mode the chip behaves as if bits 2 and 0 of every Connection Memory High location were 1, regardless of the actual values.

|     |                        | (unused)<br>Mode<br>Control<br>Bits<br>7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|-----|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit | Name                   | Description                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 7   | Split Memory           | When 1, all subsequent reads are from the Data Memory and writes are to the Connection Memory Low, except when the Control Register is accessed again. When 0, the Memory Select bits specify the memory for subsequent operations. In either case, the Stream Address Bits select the subsection of the memory which is made available. |  |  |  |  |  |  |

| 6   | Message<br>Mode        | When 1, the contents of the Connection Memory Low are output on the Serial Output streams except when the ODE pin is low. When 0, the Connection Memory bits for each channel determine what is output.                                                                                                                                  |  |  |  |  |  |  |

| 5   | (unused)               |                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 4-3 | Memory<br>Select Bits  | 0-0 - Not to be used<br>0-1 - Data Memory (read only from the microprocessor port)<br>1-0 - Connection Memory Low<br>1-1 - Connection Memory High                                                                                                                                                                                        |  |  |  |  |  |  |

| 2-0 | Stream<br>Address Bits | The number expressed in binary notation on these bits refers to the input or output ST-BUS stream which corresponds to the subsection of memory made accessible for subsequent operations.                                                                                                                                               |  |  |  |  |  |  |

#### Figure 4 - Control Register Bits

|     |                    | No Corresponding Memory<br>- These bits give 0s if read.     Per Channel<br>Control Bits       7     6     5     4     3     2     1     0                                                                                                                                                                                         |

|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | NameE              | Description                                                                                                                                                                                                                                                                                                                        |

| 2   | Message<br>Channel | When 1, the contents of the corresponding location in Connection Memory Low are output on the location's channel and stream. When 0, the contents of the corresponding location in Connection Memory Low act as an address for the Data Memory and so determine the source of the connection to the location's channel and stream. |

| 1   | CSTo Bit           | This bit is output on the CSTo pin one channel early. The CSTo bit for stream 0 is output first.                                                                                                                                                                                                                                   |

| 0   | Output<br>Enable   | If the ODE pin is high and bit 6 of the Control Register is 0, then this bit enables the output driver for the location's channel and stream. This allows individual channels on individual streams to be made high-impedance, allowing switching matrices to be constructed. A 1 enables the driver and a 0 disables it.          |

Figure 5 - Connection Memory High Bits

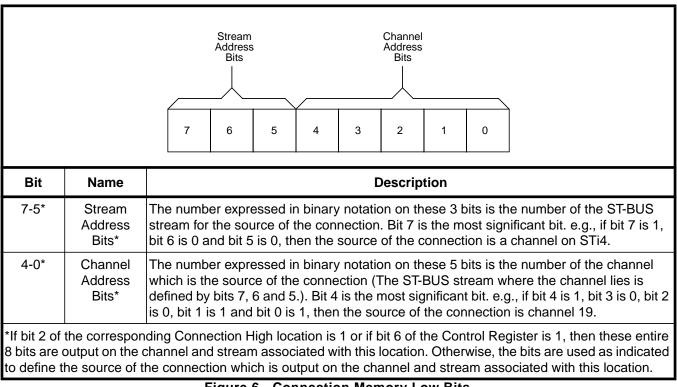

Figure 6 - Connection Memory Low Bits

If bit 6 of the Control Register is 0, then bits 2 and 0 of each Connection Memory High location function normally (see Fig. 5). If bit 2 is 1, the associated ST-BUS output channel is in Message Mode; i.e., the byte in the corresponding Connection Memory Low location is transmitted on the stream at that channel. Otherwise, one of the bytes received on the serial inputs is transmitted and the contents of the Connection Memory Low define the ST-BUS input stream and channel where the byte is to be found (see Fig. 6).

If the ODE pin is low, then all serial outputs are highimpedance. If it is high and bit 6 in the Control Register is 1, then all outputs are active. If the ODE pin is high and bit 6 in the Control Register is 0, then the bit 0 in the Connection Memory High location enables the output drivers for the corresponding individual ST-BUS output stream and channel. Bit 0=1 enables the driver and bit 0=0 disables it (see Fig. 5).

Bit 1 of each Connection Memory High location (see Fig. 5) is output on the CSTo pin once every frame. To allow for delay in any external control circuitry the bit is output one channel before the corresponding channel on the ST-BUS streams, and the bit for stream 0 is output first in the channel; e.g., bit 1's for channel 9 of streams 0-7 are output synchronously with ST-BUS channel 8 bits 7-0.

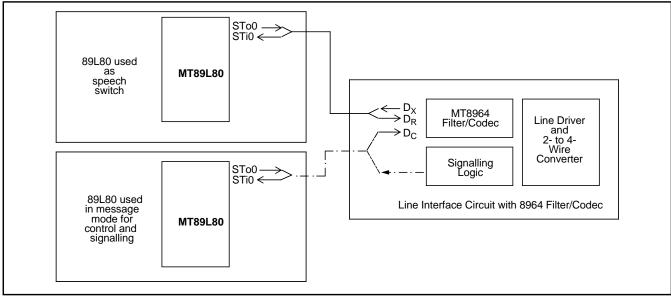

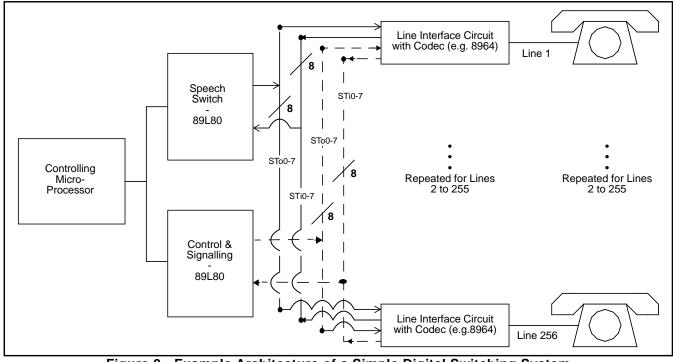

Fig. 7 shows the interface between the MT89L80s and the filter/codecs. Fig. 8 shows the position of these components in an example architecture.

The MT8964 filter/codec in Fig. 7 receives and transmits digitized voice signals on the ST-BUS input  $D_R$ , and ST-BUS output  $D_X$ , respectively. These signals are routed to the ST-BUS inputs and outputs on the top MT89L80, which is used as a digital speech switch.

The MT8964 is controlled by the ST-BUS input  $D_c$  originating from the bottom MT89L80, which generates the appropriate signals from an output channel in Message Mode. This architecture optimizes the messaging capability of the line circuit by building signalling logic, e.g., for on-off hook detection, which communicates on an ST-BUS output. This signalling ST-BUS output is monitored by a microprocessor (not shown) through an ST-BUS input on the bottom MT89L80.

Fig. 8 shows how a simple digital switching system may be designed using the ST-BUS architecture. This is a private telephone network with 256 extensions which uses a single MT89L80 as a speech switch and a second MT89L80 for communication with the line interface circuits.

## Applications

#### Use in a Simple Digital Switching System

Figs. 7 and 8 show how MT89L80s can be used with MT8964s to form a simple digital switching system.

Figure 7 - Example of Typical Interface between 89L80s and 8964s for Simple Digital Switching System

Figure 8 - Example Architecture of a Simple Digital Switching System

### **Absolute Maximum Ratings\***

|   | Parameter                                   | Symbol         | Min                  | Max                  | Units |

|---|---------------------------------------------|----------------|----------------------|----------------------|-------|

| 1 | Supply Voltage                              |                | -0.3                 | 5.0                  | V     |

| 2 | Voltage on any I/O pin (except supply pins) | Vo             | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 3 | Current at Digital Outputs                  | Ι <sub>ο</sub> |                      | 20                   | mA    |

| 4 | Storage Temperature                         | Ts             | -55                  | +125                 | °C    |

| 5 | Package Power Dissipation                   | P <sub>D</sub> |                      | 1                    | W     |

Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

### Recommended Operating Conditions - Voltages are with respect to ground (Vss) unless otherwise stated.

|   | Characteristics                          | Sym             | Min             | Тур | Max             | Units | Test Conditions |

|---|------------------------------------------|-----------------|-----------------|-----|-----------------|-------|-----------------|

| 1 | Operating Temperature                    | T <sub>OP</sub> | -40             |     | +85             | °C    |                 |

| 2 | Positive Supply                          | V <sub>DD</sub> | 3.0             |     | 3.6             | V     |                 |

| 3 | Input High Voltage                       | V <sub>IH</sub> | $0.7V_{DD}$     |     | V <sub>DD</sub> | V     |                 |

| 4 | Input High Voltage on 5V Tolerant Inputs | V <sub>IH</sub> |                 |     | 5.5             | V     |                 |

| 5 | Input Low Voltage                        | V <sub>IL</sub> | V <sub>SS</sub> |     | $0.3V_{DD}$     | V     |                 |

# **DC Electrical Characteristics** - Voltages are with respect to ground ( $V_{ss}$ ) unless otherwise stated.

|    | -      | Characteristics        | Sym             | Min         | Typ‡ | Max         | Units | Test Conditions                                   |

|----|--------|------------------------|-----------------|-------------|------|-------------|-------|---------------------------------------------------|

| 1  | 1      | Supply Current         | I <sub>DD</sub> |             | 4    | 7           | mA    | Outputs unloaded                                  |

| 2  | Ň      | Input High Voltage     | V <sub>IH</sub> | $0.7V_{DD}$ |      |             | V     |                                                   |

| 3  | P<br>U | Input Low Voltage      | V <sub>IL</sub> |             |      | $0.3V_{DD}$ | V     |                                                   |

| 4  | Т      | Input Leakage          | I               |             |      | 5           | μΑ    | $V_{\rm I}$ between $V_{\rm SS}$ and $V_{\rm DD}$ |

| 5  | S      | Input Pin Capacitance  | Cı              |             |      | 10          | pF    |                                                   |

| 6  | 0      | Output High Voltage    | V <sub>OH</sub> | $0.8V_{DD}$ |      |             | V     | I <sub>OH</sub> = 10 mA                           |

| 7  | O<br>U | Output High Current    | I <sub>ОН</sub> | 10          |      |             | mA    | Sourcing. V <sub>OH</sub> =2.4V                   |

| 8  | T<br>P | Output Low Voltage     | V <sub>OL</sub> |             |      | 0.4         | V     | I <sub>OL</sub> = 5 mA                            |

| 9  | U      | Output Low Current     | I <sub>OL</sub> | 5           |      |             | mA    | Sinking. $V_{OL} = 0.4V$                          |

| 10 | T<br>S | High Impedance Leakage | I <sub>oz</sub> |             |      | 5           | μΑ    | $V_{\rm O}$ between $V_{\rm SS}$ and $V_{\rm DD}$ |

| 11 | 3      | Output Pin Capacitance | Co              |             |      | 10          | pF    |                                                   |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

## AC Electrical Characteristics – Timing Parameter Measurement Voltage Levels

|   | Characteristics                       | Sym             | Level       | Units | Test Conditions |

|---|---------------------------------------|-----------------|-------------|-------|-----------------|

| 1 | CMOS Threshold Voltage                | V <sub>TT</sub> | $0.5V_{DD}$ | V     |                 |

| 2 | CMOS Rise/Fall Threshold Voltage high | V <sub>HM</sub> | $0.7V_{DD}$ | V     |                 |

| 3 | CMOS Rise/Fall Threshold Voltage low  | $V_{LM}$        | $0.3V_{DD}$ | V     |                 |

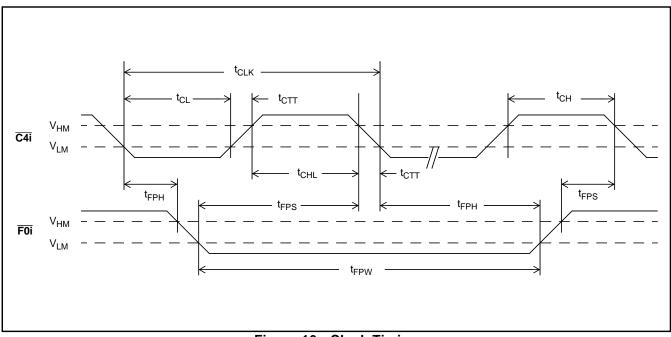

# AC Electrical Characteristics<sup>†</sup> - Clock Timing (Figures 9 and 10)

|   |        | Characteristics       | Sym              | Min | Тур‡ | Max | Units | Test Conditions |

|---|--------|-----------------------|------------------|-----|------|-----|-------|-----------------|

| 1 |        | Clock Period*         | t <sub>CLK</sub> | 220 | 244  | 300 | ns    |                 |

| 2 |        | Clock Width High      | t <sub>CH</sub>  | 85  | 122  | 150 | ns    |                 |

| 3 | N      | Clock Width Low       | t <sub>CL</sub>  | 85  | 122  | 150 | ns    |                 |

| 4 | P<br>U | Clock Transition Time | t <sub>CTT</sub> |     |      | 10  | ns    |                 |

| 5 | Т      | Frame Pulse SetupTime | t <sub>FPS</sub> | 10  |      | 190 | ns    |                 |

| 6 | S      | Frame Pulse Hold Time | t <sub>FPH</sub> | 10  |      | 190 | ns    |                 |

| 7 |        | Frame Pulse Width     | t <sub>FPW</sub> |     | 244  |     | ns    |                 |

† Timing is over recommended temperature & power supply voltages.

Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

\* Contents of Connection Memory are not lost if the clock stops, however, ST-BUS outputs go into the high impedance state.

**NB:** Frame Pulse is repeated every 512 cycles of  $\overline{C4i}$ .

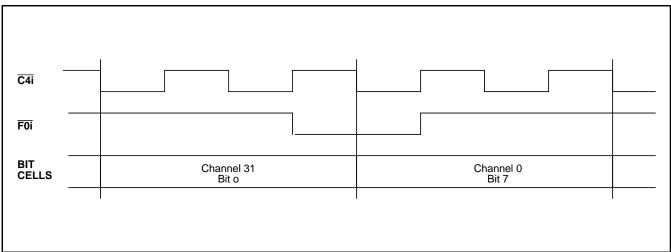

Figure 9- Frame Alignment

Figure 10 - Clock Timing

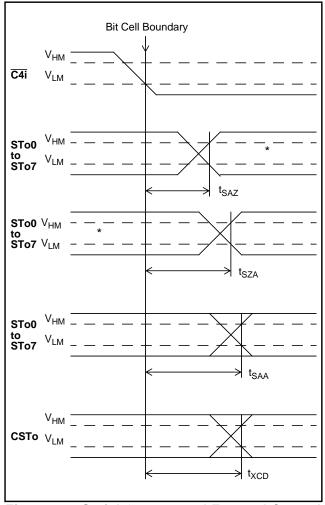

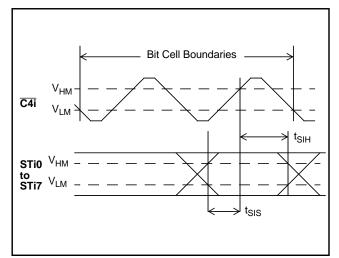

| AC Electrical Characteristics <sup>†</sup> - Serial Streams (Figures 11, 12 and 13) |  |

|-------------------------------------------------------------------------------------|--|

|-------------------------------------------------------------------------------------|--|

|   |          | Characteristics                 | Sym              | Min | Тур‡ | Max | Units | Test Conditions                               |

|---|----------|---------------------------------|------------------|-----|------|-----|-------|-----------------------------------------------|

| 1 | 0        | STo0/7 Delay - Active to High Z | t <sub>SAZ</sub> | 5   |      | 55  | ns    | $R_L$ =1 K $\Omega^*$ , $C_L$ =150 pF         |

| 2 | UT       | STo0/7 Delay - High Z to Active | t <sub>SZA</sub> | 5   |      | 55  | ns    | C <sub>L</sub> =150 pF                        |

| 3 | P        | STo0/7 Delay - Active to Active | t <sub>SAA</sub> | 5   |      | 55  | ns    | C <sub>L</sub> =150 pF                        |

| 4 | U<br>  T | Output Driver Enable Delay      | t <sub>OED</sub> |     |      | 50  | ns    | $R_L=1 \text{ K}\Omega^*, C_L=150 \text{ pF}$ |

| 5 | S        | External Control Delay          | t <sub>XCD</sub> |     |      | 55  | ns    | C <sub>L</sub> =150 pF                        |

| 6 | I        | Serial Input Setup Time         | t <sub>SIS</sub> | 20  |      |     | ns    |                                               |

| 7 | N        | Serial Input Hold Time          | t <sub>SIH</sub> | 20  |      |     | ns    |                                               |

† Timing is over recommended temperature & power supply voltages.

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

\* High Impedance is measured by pulling to the appropriate rail with R<sub>L</sub>, with timing corrected to cancel time taken to discharge C<sub>L</sub>.

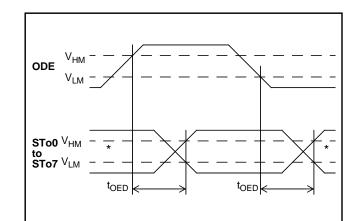

Figure 11 - Serial Outputs and External Control

Figure 12 - Output Driver Enable

Figure 13 - Serial Inputs

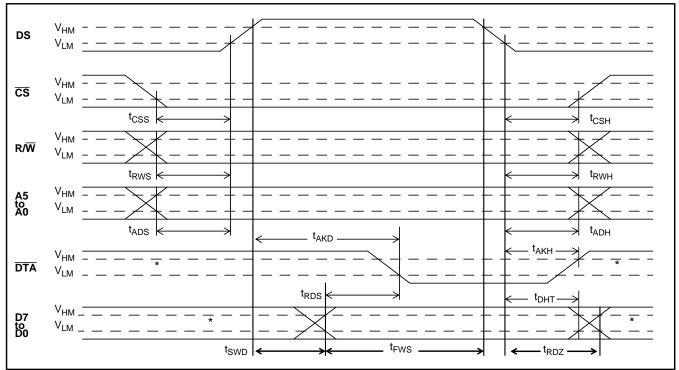

# AC Electrical Characteristics<sup>†</sup> - Processor Bus (Figures 14)

|    | Characteristics                               | Sym              | Min | Typ <sup>‡</sup> | Max  | Units | Test Conditions                               |

|----|-----------------------------------------------|------------------|-----|------------------|------|-------|-----------------------------------------------|

| 1  | Chip Select Setup Time                        | t <sub>CSS</sub> | 0   |                  |      | ns    |                                               |

| 2  | Read/Write Setup Time                         | t <sub>RWS</sub> | 5   |                  |      | ns    |                                               |

| 3  | Address Setup Time                            | t <sub>ADS</sub> | 5   |                  |      | ns    |                                               |

| 4  | Acknowledgment Delay<br>Control Register Read | t <sub>AKD</sub> |     | 52               | 120  | ns    | С <sub>L</sub> =150 рF                        |

|    | Control Register Write                        | t <sub>AKD</sub> |     | 25               | 65   | ns    | C <sub>L</sub> =150 pF                        |

|    | Connection Memory Read                        | t <sub>AKD</sub> |     | 62               | 120  | ns    | C <sub>L</sub> =150 pF                        |

|    | Connection Memory Write                       | t <sub>AKD</sub> |     | 30               | 53   | ns    | C <sub>L</sub> =150 pF                        |

|    | Data Memory Read                              | t <sub>AKD</sub> |     | 560              | 1220 | ns    | C <sub>L</sub> =150 pF                        |

| 5  | Fast Write Data Setup Time                    | t <sub>FWS</sub> | 0   |                  |      | ns    |                                               |

| 6  | Slow Write Data Delay                         | t <sub>SWD</sub> |     |                  | 122  | ns    |                                               |

| 7  | Read Data Setup Time                          | t <sub>RDS</sub> | 0   |                  |      | ns    | C <sub>L</sub> = 150 pF                       |

| 8  | Data Hold Time Read                           | t <sub>DHT</sub> | 10  |                  | 90   | ns    | $R_L=1 K\Omega^*, C_L=150 pF$                 |

|    | Write                                         | t <sub>DHT</sub> | 5   | 10               |      | ns    |                                               |

| 9  | Read Data To High Impedance                   | t <sub>RDZ</sub> | 15  | 50               | 90   | ns    | $R_L=1 K\Omega^*, C_L=150 pF$                 |

| 10 | Chip Select Hold Time                         | t <sub>CSH</sub> | 0   |                  |      | ns    |                                               |

| 11 | Read/Write Hold Time                          | t <sub>RWH</sub> | 0   |                  |      | ns    |                                               |

| 12 | Address Hold Time                             | t <sub>ADH</sub> | 8   |                  |      | ns    |                                               |

| 13 | Acknowledgment Hold Time                      | t <sub>AKH</sub> |     | 50               | 80   | ns    | $R_L=1 \text{ K}\Omega^*, C_L=150 \text{ pF}$ |

† Timing is over recommended temperature & power supply voltages.

<sup>1</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

<sup>\*</sup> High Impedance is measured by pulling to the appropriate rail with R<sub>L</sub>, with timing corrected to cancel time taken to discharge C<sub>L</sub>.

Figure 14 - Processor Bus

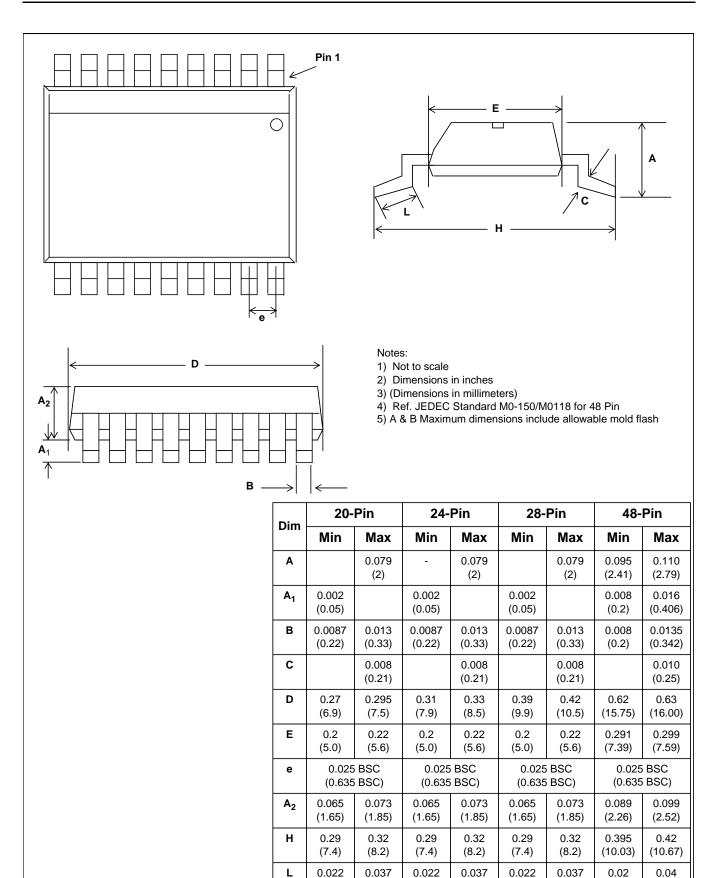

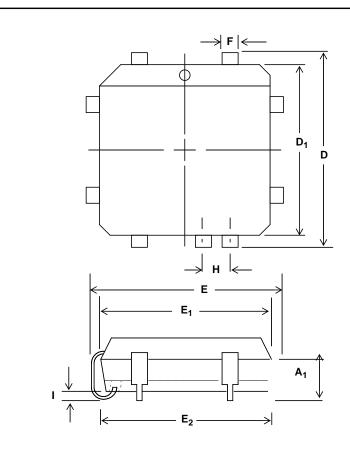

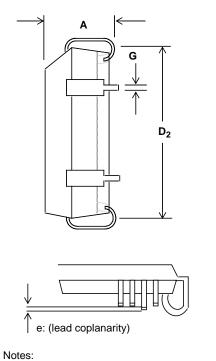

# **Package Outlines**

### Small Shrink Outline Package (SSOP) - N Suffix

(0.95)

(0.55)

(0.95)

(0.55)

(0.95)

(0.51)

(0.55)

(1.02)

# **Package Outlines**

1) Not to scale 2) Dimensions in inches

3) (Dimensions in millimeters)

4) For D & E add for allowable Mold Protrusion 0.010"

| Dim         Min         Max         Min         Max <th>Max<br/>0.200<br/>(5.08)<br/>0.130<br/>(3.30)<br/>1.195<br/>(30.35)<br/>1.158</th>                                                                                                                                                                                                                                                                                                                                                                                                 | Max<br>0.200<br>(5.08)<br>0.130<br>(3.30)<br>1.195<br>(30.35)<br>1.158 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (5.08)<br>0.130<br>(3.30)<br>1.195<br>(30.35)                          |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (3.30)<br>1.195<br>(30.35)                                             |  |

| (9.78)         (10.03)         (12.32)         (12.57)         (17.40)         (17.65)         (25.02)         (25.27)         (30.10)           D1/E1         0.350         0.356         0.450         0.456         0.650         0.656         0.950         0.958         1.150           D2/E2         0.290         0.330         0.390         0.430         0.590         0.630         0.890         0.930         1.090           D2/E2         0.290         0.330         0.390         0.430         0.590         0.630         0.890         0.930         1.090           D2/E2         0.290         0.330         0.390         0.430         0.590         0.630         0.890         0.930         1.090           D2/E3         0.290         0.330         0.390         0.430         0.590         0.630         0.890         0.930         1.090           D3/E4         0.911         (10.92)         (14.99)         (16.00)         (22.61)         (23.62)         (27.69)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (30.35)                                                                |  |

| (8.890)       (9.042)       (11.430)       (11.582)       (16.510)       (16.662)       (24.130)       (24.333)       (29.210) <b>D_2/E_2</b> 0.290       0.330       0.390       0.430       0.590       0.630       0.890       0.930       1.090         (7.37)       (8.38)       (9.91)       (10.92)       (14.99)       (16.00)       (22.61)       (23.62)       (27.69)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 158                                                                  |  |

| (7.37)         (8.38)         (9.91)         (10.92)         (14.99)         (16.00)         (22.61)         (23.62)         (27.69)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (29.413)                                                               |  |

| <b>e</b> 0 0.004 0 0.004 0 0.004 0 0.004 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.130<br>(28.70)                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.004                                                                  |  |

| F         0.026<br>(0.661)         0.032<br>(0.812)         0.026<br>(0.661)         0.032<br>(0.812)         0.026<br>(0.812)         0.032<br>(0.661)         0.032<br>(0.812)         0.026<br>(0.661)         0.032<br>(0.661)         0.032<br>(0.812)         0.026<br>(0.661)         0.032<br>(0.661)         0.032<br>(0.661) | 0.032<br>(0.812)                                                       |  |

| G         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.031)         0.0533)         (0.331)         (0.533)         (0.331)         0.021         0.013         0.021         0.013         0.021         0.013         0.021         0.013         0.031)         0.031)         0.031)         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031         0.031                                                                                                                                                                                                                                                                                                                                                                                                            | 0.021<br>(0.533)                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.050 BSC<br>(1.27 BSC)                                                |  |

| I         0.020<br>(0.51)         0.020<br>(0.51)         0.020<br>(0.51)         0.020<br>(0.51)         0.020<br>(0.51)         0.020<br>(0.51)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                        |  |

### Plastic J-Lead Chip Carrier - P-Suffix

http://www.mitelsemi.com

#### World Headquarters - Canada

Tel: +1 (613) 592 2122 Fax: +1 (613) 592 6909

#### North America

Tel: +1 (770) 486 0194 Fax: +1 (770) 631 8213

#### Asia/Pacific

Tel: +65 333 6193 Fax: +65 333 6192 Europe, Middle East, and Africa (EMEA) Tel: +44 (0) 1793 518528 Fax: +44 (0) 1793 518581

Information relating to products and services furnished herein by Mitel Corporation or its subsidiaries (collectively "Mitel") is believed to be reliable. However, Mitel assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or services conveys any license, either express or implied, under patents or other intellectual property rights owned by Mitel, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Mitel, or non-Mitel furnished goods or services may infringe patents or other intellectual property rights owned by Mitel.

This publication is issued to provide information only and (unless agreed by Mitel in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Mitel without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or services (Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Mitel's conditions of sale which are available on request.

M Mitel (design) and ST-BUS are registered trademarks of MITEL Corporation Mitel Semiconductor is an ISO 9001 Registered Company Copyright 1999 MITEL Corporation All Rights Reserved Printed in CANADA

TECHNICAL DOCUMENTATION - NOT FOR RESALE