# LM111JAN Voltage Comparator

## **General Description**

The LM111 is a voltage comparator that has input currents nearly a thousand times lower than devices such as the LM106 or LM710. It is also designed to operate over a wider range of supply voltages: from standard  $\pm$ 15V op amp supplies down to the single 5V supply used for IC logic. The output is compatible with RTL, DTL and TTL as well as MOS circuits. Further, it can drive lamps or relays, switching voltages up to 50V at currents as high as 50 mA.

Both the inputs and the outputs of the LM111 can be isolated from system ground, and the output can drive loads referred to ground, the positive supply or the negative supply. Offset balancing and strobe capability are provided and outputs can be wire OR'ed. Although slower than the LM106 and LM710 (200 ns response time vs 40 ns) the device is also much less prone to spurious oscillations. The LM111 has the same pin configuration as the LM106 and LM710.

### **Features**

- Operates from single 5V supply

- Input current: 200 nA max. over temperature

- Offset current: 20 nA max. over temperature

- Differential input voltage range: ±30V

- Power consumption: 135 mW at ±15V

- Power supply voltage, single 5V to ±15V

- Offset voltage null capability

- Strobe capability

### **Ordering Information**

| NS PART NUMBER | JAN PART NUMBER  | NS PACKAGE NUMBER | PACKAGE DESCRIPTION |

|----------------|------------------|-------------------|---------------------|

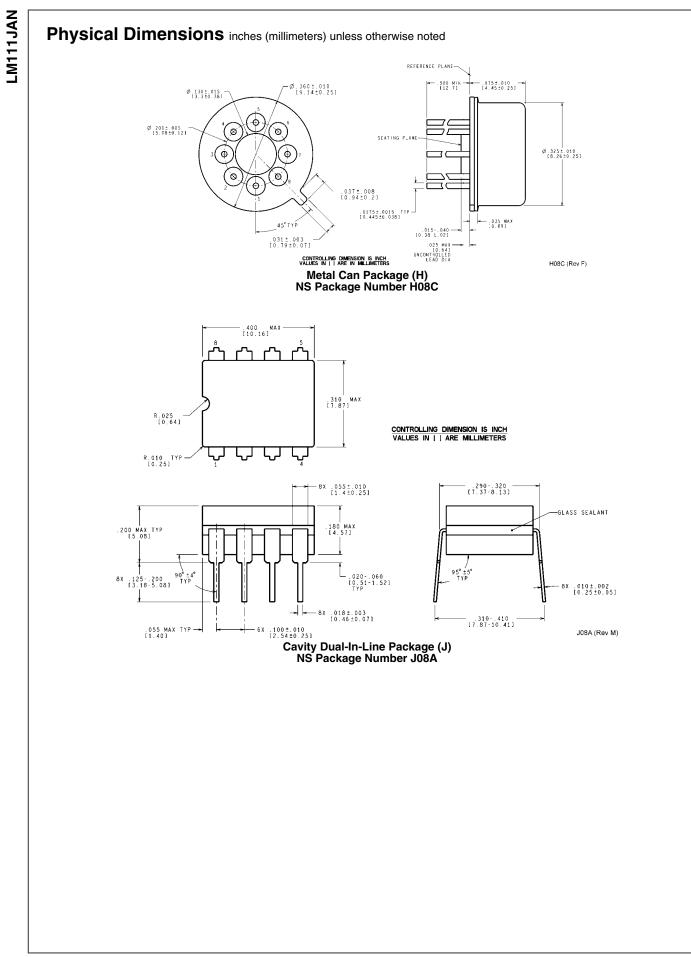

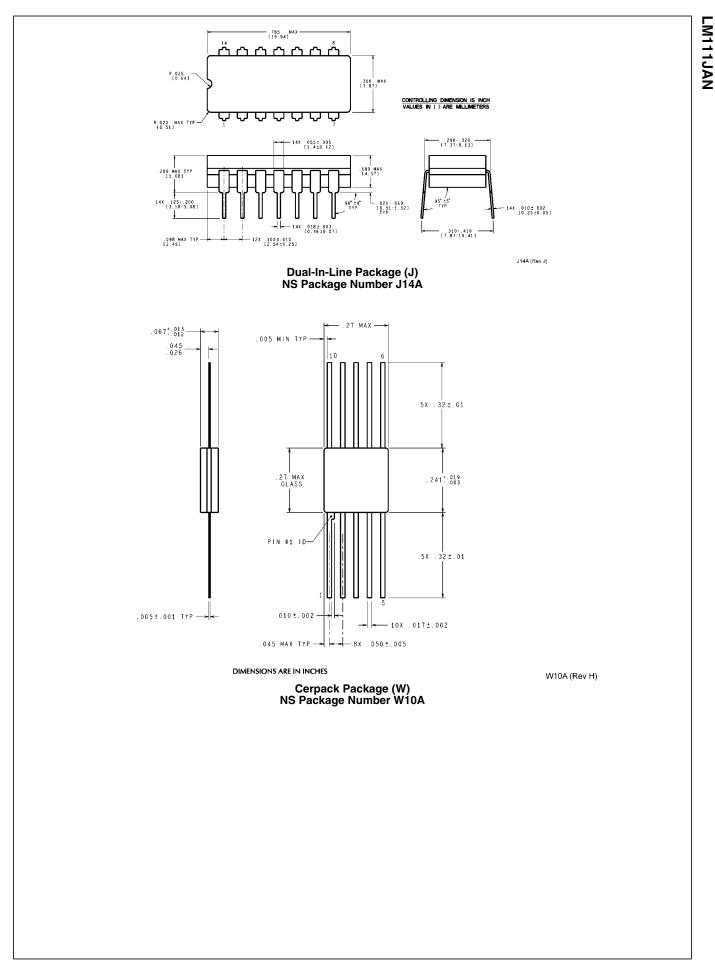

| JL111BCA       | JM38510/10304BCA | J14A              | 14LD CERDIP         |

| JL111BGA       | JM38510/10304BGA | H08C              | 8LD TO-99 Metal Can |

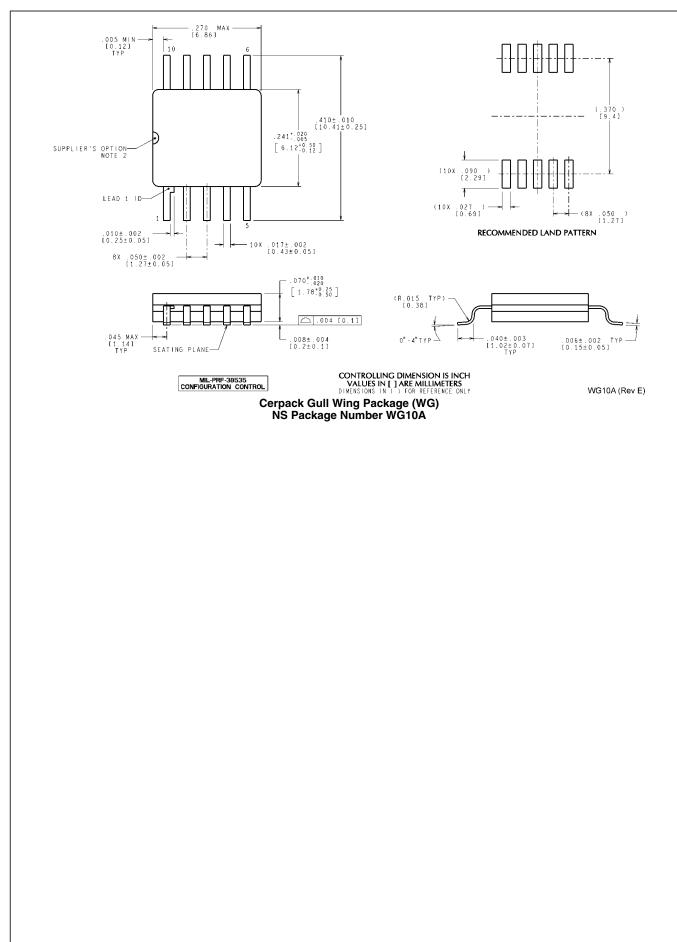

| JL111BHA       | JM38510/10304BHA | W10A              | 10LD CERPACK        |

| JL111BPA       | JM38510/10304BPA | J08A              | 8LD CERDIP          |

| JL111SGA       | JM38510/10304SGA | H08C              | 8LD TO-99 Metal Can |

| JL111SHA       | JM38510/10304SHA | W10A              | 10LD CERPACK        |

| JL111SPA       | JM38510/10304SPA | J08A              | 8LD CERDIP          |

| JL111SZA       | JM38510/10304SZA | WG10A             | 10LD Ceramic SOIC   |

LM111JAN Voltage Comparator

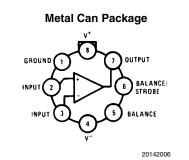

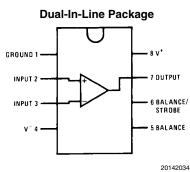

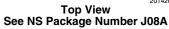

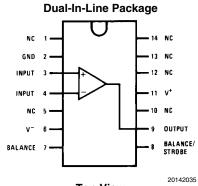

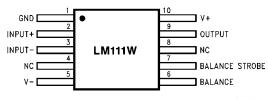

# **Connection Diagrams**

Note: Pin 4 connected to case

Top View See NS Package Number H08C

Top View See NS Package Number J14A

See NS Package Number W10A, WG10A

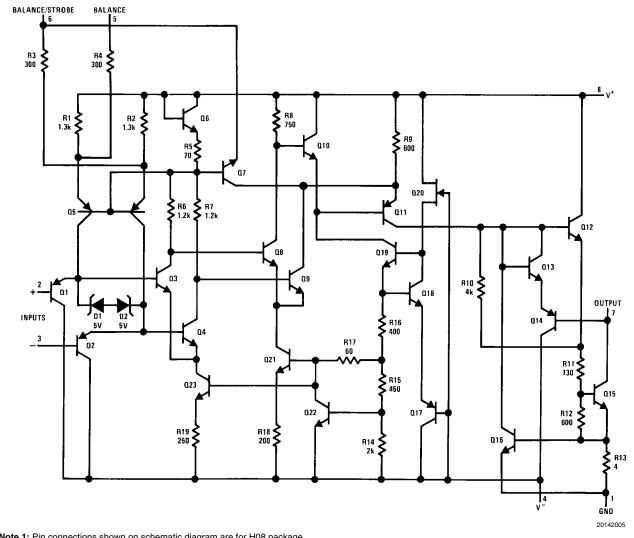

# **Schematic Diagram**

(Note Pin connections shown on schematic diagram are for H08 package.)

Note 1: Pin connections shown on schematic diagram are for H08 package.

# Absolute Maximum Ratings (Note 2)

| Positive Supply Voltage                     | +30.0V                         |

|---------------------------------------------|--------------------------------|

| Negative Supply Voltage                     | -30.0V                         |

| Total Supply Voltage                        | 36V                            |

| Output to Negative Supply Voltage           | 50V                            |

| GND to Negative Supply Voltage              | 30V                            |

| Differential Input Voltage                  | ±30V                           |

| Sink Current                                | 50mA                           |

| Input Voltage (Note 3)                      | ±15V                           |

| Power Dissipation (Note 4)                  |                                |

| 8 LD CERDIP                                 | 400mW @ 25°C                   |

| 8 LD Metal Can                              | 330mW @ 25°C                   |

| 10 LD CERPACK                               | 330mW @ 25°C                   |

| 10 LD Ceramic SOIC                          | 330mW @ 25°C                   |

| 14 LD CERDIP                                | 400mW @ 25°C                   |

| Output Short Circuit Duration               | 10 seconds                     |

| Maximum Strobe Current                      | 10mA                           |

| Operating Temperature Range                 | -55°C ≤ T <sub>A</sub> ≤ 125°C |

| Thermal Resistance                          |                                |

| θ <sub>JA</sub>                             |                                |

| 8 LD CERDIP (Still Air @ 0.5W)              | 120°C/W                        |

| 8 LD CERDIP (500LF/Min Air flow @ 0.5W)     | 76°C/W                         |

| 8 LD Metal Can (Still Air @ 0.5W)           | 150°C/W                        |

| 8 LD Metal Can (500LF/Min Air flow @ 0.5W)  | 92°C/W                         |

| 10 Ceramic SOIC (Still Air @ 0.5W)          | 231°C/W                        |

| 10 Ceramic SOIC (500LF/Min Air flow @ 0.5W) | 153°C/W                        |

| 10 CERPACK (Still Air @ 0.5W)               | 231°C/W                        |

| 10 CERPACK (500LF/Min Air flow @ 0.5W)      | 153°C/W                        |

| 14 LD CERDIP (Still Air @ 0.5W)             | 120°C/W                        |

| 14 LD CERDIP (500LF/Min Air flow @ 0.5W)    | 65°C/W                         |

| θ <sub>JC</sub>                             |                                |

| 8 LD CERDIP                                 | 35°C/W                         |

| 8 LD Metal Can Pkg                          | 40°C/W                         |

| 10 LD Ceramic SOIC                          | 60°C/W                         |

| 10 LD CERPACK                               | 60°C/W                         |

| 14 LD CERDIP                                | 35°C/W                         |

| Storage Temperature Range                   | -65°C ≤ T <sub>A</sub> ≤ 150°C |

| Maximum Junction Temperature                | 175°C                          |

| Lead Temperature (Soldering, 60 seconds)    | 300°C                          |

| Voltage at Strobe Pin                       | V+ -5V                         |

| Package Weight (Typical)                    |                                |

| 8 LD Metal Can                              | 965mg                          |

| 8 LD CERDIP                                 | 1100mg                         |

| 10 LD CERPACK                               | 250mg                          |

| 10 LD Ceramic SOIC                          | 225mg                          |

| 14 LD CERDIP                                | TBD                            |

| ESD Rating (Note 5)                         | 300V                           |

|                                             |                                |

4

# **Recommended Operating Conditions**

Supply Voltage **Operating Temperature Range**

$V_{CC} = \pm 15 V_{DC}$  $-55^{\circ}\mathrm{C} \leq \mathrm{T}_{\mathrm{A}} \leq 125^{\circ}\mathrm{C}$

LM111JAN

| Subgroup | Description         | Temperature (°C) |

|----------|---------------------|------------------|

| 1        | Static tests at     | +25              |

| 2        | Static tests at     | +125             |

| 3        | Static tests at     | -55              |

| 4        | Dynamic tests at    | +25              |

| 5        | Dynamic tests at    | +125             |

| 6        | Dynamic tests at    | -55              |

| 7        | Functional tests at | +25              |

| 8A       | Functional tests at | +125             |

| 8B       | Functional tests at | -55              |

| 9        | Switching tests at  | +25              |

| 10       | Switching tests at  | +125             |

| 11       | Switching tests at  | -55              |

# LM111 JAN Electrical Characteristics

### **DC** Parameters

The following conditions apply, unless otherwise specified.

DC:  $V_{CC} = \pm 15V, V_{CM} = 0$

| Symbol            | Parameter                         | Conditions                                                                                                                                                                           | Notes        | Min  | Мах  | Unit | Sub-<br>groups |

|-------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|----------------|

| V <sub>IO</sub>   | Input Offset Voltage              | V <sub>I</sub> = 0V, R <sub>S</sub> = 50Ω                                                                                                                                            |              | -3.0 | +3.0 | mV   | 1              |

|                   |                                   |                                                                                                                                                                                      |              | -4.0 | +4.0 | mV   | 2, 3           |

|                   |                                   | +V <sub>CC</sub> = 29.5V, -V <sub>CC</sub> = -0.5V,                                                                                                                                  |              | -3.0 | +3.0 | mV   | 1              |

|                   |                                   | $V_{I} = 0V, V_{CM} = -14.5V,$<br>$R_{S} = 50\Omega$                                                                                                                                 |              | -4.0 | +4.0 | mV   | 2, 3           |

|                   |                                   | $+V_{CC} = 2V, -V_{CC} = -28V,$                                                                                                                                                      |              | -3.0 | +3.0 | mV   | 1              |

|                   |                                   | $V_I = 0V, V_{CM} = +13V,$<br>$R_S = 50\Omega$                                                                                                                                       |              | -4.0 | +4.0 | mV   | 2, 3           |

|                   |                                   | +V <sub>CC</sub> = +2.5V, -V <sub>CC</sub> = -2.5V,                                                                                                                                  |              | -3.0 | +3.0 | mV   | 1              |

|                   |                                   | $V_{1} = 0V, R_{S} = 50\Omega$                                                                                                                                                       |              | -4.0 | +4.0 | mV   | 2, 3           |

| V <sub>IO</sub> R | Raised Input Offset Voltage       | $V_1 = 0V, R_S = 50\Omega$                                                                                                                                                           | ( <b>1</b> ) | -3.0 | +3.0 | mV   | 1              |

| 10                |                                   |                                                                                                                                                                                      | (Note 10)    | -4.5 | +4.5 | mV   | 2, 3           |

|                   |                                   | +V <sub>CC</sub> = 29.5V, -V <sub>CC</sub> = -0.5V,                                                                                                                                  |              | -3.0 | +3.0 | mV   | 1              |

|                   |                                   | $V_{I} = 0V, V_{CM} = -14.5V,$<br>$R_{S} = 50\Omega$                                                                                                                                 | (Note 10)    | -4.5 | +4.5 | mV   | 2, 3           |

|                   |                                   | $+V_{CC} = 2V, -V_{CC} = -28V,$                                                                                                                                                      |              | -3.0 | +3.0 | mV   | 1              |

|                   |                                   | $V_1 = 0V, V_{CM} = +13V,$<br>$R_S = 50\Omega$                                                                                                                                       | (Note 10)    | -4.5 | +4.5 | mV   | 2, 3           |

| I <sub>IO</sub>   | Input Offset Current              | $V_1 = 0V, R_S = 50K\Omega$                                                                                                                                                          |              | -10  | +10  | nA   | 1, 2           |

|                   |                                   |                                                                                                                                                                                      |              | -20  | +20  | nA   | 3              |

|                   |                                   | +V <sub>CC</sub> = 29.5V, -V <sub>CC</sub> = -0.5V,                                                                                                                                  |              | -10  | +10  | nA   | 1, 2           |

|                   |                                   | $V_1 = 0V, V_{CM} = -14.5V,$<br>$R_S = 50K\Omega$                                                                                                                                    |              | -20  | +20  | nA   | 3              |

|                   |                                   | $+V_{CC} = 2V, -V_{CC} = -28V,$                                                                                                                                                      |              | -10  | +10  | nA   | 1, 2           |

|                   |                                   | $V_I = 0V, V_{CM} = +13V,$<br>$R_S = 50K\Omega$                                                                                                                                      |              | -20  | +20  | nA   | 3              |

| I <sub>IO</sub> R | Raised Input Offset Current       | V <sub>1</sub> = 0V, R <sub>S</sub> = 50KΩ                                                                                                                                           |              | -25  | +25  | nA   | 1, 2           |

|                   |                                   |                                                                                                                                                                                      | (Note 10)    | -50  | +50  | nA   | 3              |

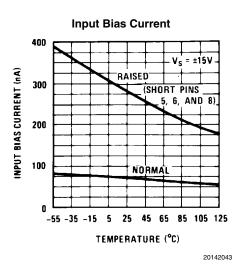

| ±l <sub>IB</sub>  | Input Bias Current                | V <sub>1</sub> = 0V, R <sub>S</sub> = 50KΩ                                                                                                                                           |              | -100 | 0.1  | nA   | 1, 2           |

|                   |                                   | 1 2 3                                                                                                                                                                                |              | -150 | 0.1  | nA   | 3              |

|                   |                                   | +V <sub>CC</sub> = 29.5V, -V <sub>CC</sub> = -0.5V,                                                                                                                                  |              | -150 | 0.1  | nA   | 1, 2           |

|                   |                                   | $V_{I} = 0V, V_{CM} = -14.5V,$<br>$R_{S} = 50K\Omega$                                                                                                                                |              | -200 | 0.1  | nA   | 3              |

|                   |                                   | +V <sub>CC</sub> = 2V, -V <sub>CC</sub> = -28V,                                                                                                                                      |              | -150 | 0.1  | nA   | 1, 2           |

|                   |                                   | $V_{I} = 0V, V_{CM} = +13V,$<br>$R_{S} = 50K\Omega$                                                                                                                                  |              | -200 | 0.1  | nA   | 3              |

| V <sub>O</sub> St | Collector Output Voltage (Strobe) | + $V_I$ = Gnd, - $V_I$ = 15V,<br>I <sub>St</sub> = -3mA, R <sub>S</sub> = 50 $\Omega$                                                                                                | (Note 7)     | 14   |      | v    | 1, 2, 3        |

| CMRR              | Common Mode Rejection             | $\begin{aligned} -28V &\leq -V_{CC} \leq -0.5V, R_{S} = 50\Omega, 2V \\ &\leq +V_{CC} \leq 29.5V, R_{S} = 50\Omega, -14.5V \\ &\leq V_{CM} \leq 13V, R_{S} = 50\Omega \end{aligned}$ |              | 80   |      | dB   | 1, 2, 3        |

| Symbol                   | Parameter                         | Conditions                                                                                                                                        | Notes    | Min  | Max  | Unit  | Sub-<br>groups |

|--------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|-------|----------------|

| V <sub>OL</sub>          | Low Level Output Voltage          | $\begin{split} + V_{CC} &= 4.5V, \ \text{-}V_{CC} = \text{Gnd}, \\ I_{O} &= 8\text{mA}, \ \pm V_{I} = 0.5V, \\ V_{ID} &= -6\text{mV} \end{split}$ | (Note 9) |      | 0.4  | v     | 1, 2, 3        |

|                          |                                   | $\begin{split} + V_{CC} &= 4.5V, -V_{CC} = Gnd, \\ I_{O} &= 8mA, \pm V_{I} = 3V, \\ V_{ID} &= -6mV \end{split}$                                   | (Note 9) |      | 0.4  | v     | 1, 2, 3        |

|                          |                                   | $I_O = 50mA, \pm VI = 13V,$<br>$V_{ID} = -5mV$                                                                                                    | (Note 9) |      | 1.5  | v     | 1, 2, 3        |

|                          |                                   | I <sub>O</sub> = 50mA, ±VI = -14V,<br>V <sub>ID</sub> = -5mV                                                                                      | (Note 9) |      | 1.5  | v     | 1, 2, 3        |

| I <sub>CEX</sub>         | Output Leakage Current            | $+V_{CC} = 18V, -V_{CC} = -18V,$                                                                                                                  |          | -1.0 | 10   | nA    | 1              |

|                          |                                   | V <sub>O</sub> = 32V                                                                                                                              |          | -1.0 | 500  | nA    | 2              |

| IL Input Leakage Current | Input Leakage Current             | +V <sub>CC</sub> = 18V, -V <sub>CC</sub> = -18V,<br>+V <sub>I</sub> = +12V, -V <sub>I</sub> = -17V                                                |          | -5.0 | 500  | nA    | 1, 2, 3        |

|                          |                                   | +V <sub>CC</sub> = 18V, -V <sub>CC</sub> = -18V,<br>+V <sub>I</sub> = -17V, -V <sub>I</sub> = +12V                                                |          | -5.0 | 500  | nA    | 1, 2, 3        |

| +I <sub>cc</sub>         | Power Supply Current              |                                                                                                                                                   |          |      | 6.0  | mA    | 1, 2           |

|                          |                                   |                                                                                                                                                   |          |      | 7.0  | mA    | 3              |

| -I <sub>CC</sub>         | Power Supply Current              |                                                                                                                                                   |          | -5.0 |      | mA    | 1, 2           |

|                          |                                   |                                                                                                                                                   |          | -6.0 |      | mA    | 3              |

| Δ V <sub>IO</sub> / Δ T  | Temperature Coefficient Input     | 25°C ≤ T ≤ 125°C                                                                                                                                  | (Note 8) | -25  | 25   | uV/°C | 2              |

|                          | Offset Voltage                    | -55°C ≤ T ≤ 25°C                                                                                                                                  | (Note 8) | -25  | 25   | uV/°C | 3              |

| Δ Ι <sub>ΙΟ</sub> / Δ Τ  | Temperature Coefficient Input     | 25°C ≤ T ≤ 125°C                                                                                                                                  | (Note 8) | -100 | 100  | pA/°C | 2              |

|                          | Offset Current                    | -55°C ≤ T ≤ 25°C                                                                                                                                  | (Note 8) | -200 | 200  | pA/°C | 3              |

| I <sub>os</sub>          | Short Circuit Current             | $V_{O} = 5V, t \le 10mS, -V_{I} = 0.1V,$                                                                                                          |          |      | 200  | mA    | 1              |

|                          |                                   | $+\dot{V}_{I} = 0V$                                                                                                                               |          |      | 150  | mA    | 2              |

|                          |                                   |                                                                                                                                                   |          |      | 250  | mA    | 3              |

| +V <sub>IO</sub> adj.    | Input Offset Voltage (Adjustment) | $V_0 = 0V, V_1 = 0V, R_S = 50\Omega$                                                                                                              |          | 5.0  |      | mV    | 1              |

| -V <sub>IO</sub> adj.    | Input Offset Voltage (Adjustment) | $V_{0} = 0V, V_{1} = 0V, R_{S} = 50\Omega$                                                                                                        |          |      | -5.0 | mV    | 1              |

| ±A <sub>VE</sub>         | Voltage Gain (Emitter)            | R <sub>L</sub> = 600Ω                                                                                                                             | (Note 6) | 10   |      | V/mV  | 4              |

|                          |                                   |                                                                                                                                                   | (Note 6) | 8.0  |      | V/mV  | 5, 6           |

## **AC Parameters**

The following conditions apply, unless otherwise specified.

AC:  $V_{CC} = \pm 15V, V_{CM} = 0$

| Symbol            | Parameter                | Conditions                          | Notes | Min | Max | Unit | Sub-<br>groups |

|-------------------|--------------------------|-------------------------------------|-------|-----|-----|------|----------------|

| tR <sub>LHC</sub> | Response Time (Collector | V <sub>OD</sub> (Overdrive) = -5mV, |       |     | 300 | nS   | 7, 8B          |

|                   | Output)                  | $C_{L} = 50 pF, V_{I} = -100 mV$    |       |     | 640 | nS   | 8A             |

| tR <sub>HLC</sub> | Response Time (Collector | V <sub>OD</sub> (Overdrive) = 5mV,  |       |     | 300 | nS   | 7, 8B          |

|                   | Output)                  | $C_{L} = 50 pF, V_{I} = 100 mV$     |       |     | 500 | nS   | 8A             |

LM111JAN

### **DC Drift Parameters**

The following conditions apply, unless otherwise specified.

DC:  $V_{CC} = \pm 15V, V_{CM} = 0$

Delta calculations performed on JANS devices at group B, subgroup 5.

| Symbol           | Parameter              | Conditions                                                                                                                                      | Notes | Min   | Max  | Unit | Sub-<br>groups |

|------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|------|----------------|

| V <sub>IO</sub>  | Input Offset Voltage   | $V_{1} = 0V, R_{S} = 50\Omega$                                                                                                                  |       | -0.5  | 0.5  | mV   | 1              |

|                  |                        | $+V_{CC} = 29.5V, -V_{CC} = -0.5V,$<br>$V_1 = 0V, V_{CM} = -14.5V,$<br>$R_S = 50\Omega$                                                         |       | -0.5  | 0.5  | mV   | 1              |

|                  |                        | $+V_{CC} = 2V, -V_{CC} = -28V,$<br>V <sub>1</sub> = 0V, V <sub>CM</sub> = +13V,<br>R <sub>S</sub> = 50Ω                                         |       | -0.5  | 0.5  | mV   | 1              |

| ±l <sub>IB</sub> | Input Bias Current     | V <sub>I</sub> = 0V, R <sub>S</sub> = 50KΩ                                                                                                      |       | -12.5 | 12.5 | nA   | 1              |

|                  |                        | $\begin{split} + V_{CC} &= 29.5V, \ \text{-}V_{CC} = \text{-}0.5V, \\ V_{I} &= 0V, \ V_{CM} = \text{-}14.5V, \\ R_{S} &= 50K\Omega \end{split}$ |       | -12.5 | 12.5 | nA   | 1              |

|                  |                        | $\begin{aligned} + V_{CC} &= 2V, -V_{CC} = -28V, \\ V_1 &= 0V, V_{CM} = +13V, \\ R_S &= 50K\Omega \end{aligned}$                                |       | -12.5 | 12.5 | nA   | 1              |

| I <sub>CEX</sub> | Output Leakage Current | $+V_{CC} = 18V, -V_{CC} = -18V,$<br>$V_{O} = 32V$                                                                                               |       | -5.0  | 5.0  | nA   | 1              |

**Note 2:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 3: This rating applies for ±15V supplies. The positive input voltage limit is 30 V above the negative supply. The negative input voltage limit is equal to the negative supply voltage or 30V below the positive supply, whichever is less.

**Note 4:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$  (maximum junction temperature),  $\theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower.

Note 5: Human body model, 1.5 k $\Omega$  in series with 100 pF.

Note 6: Datalog reading in K=V/mV.

Note 7:  $I_{ST} = -2mA$  at  $-55^{\circ}C$

Note 8: Calculated parameter.

Note 9:  $V_{ID}$  is voltage difference between inputs.

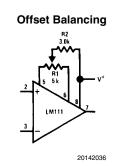

Note 10: Subscript (R) indicates tests which are performed with input stage current raised by connecting BAL and BAL/STB terminals to +V<sub>CC</sub>.

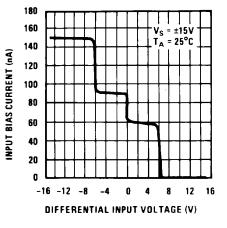

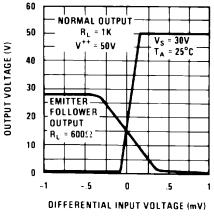

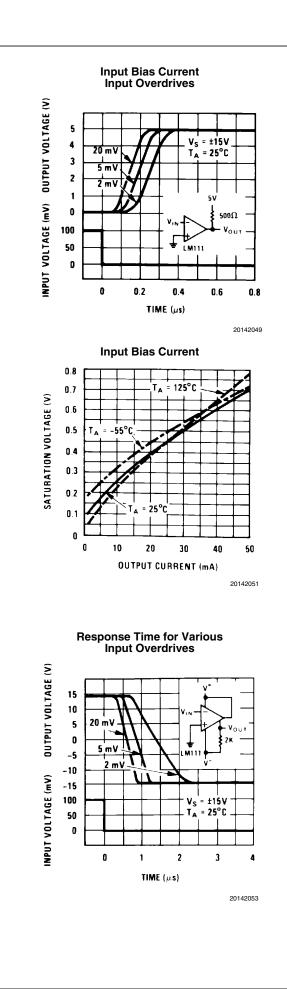

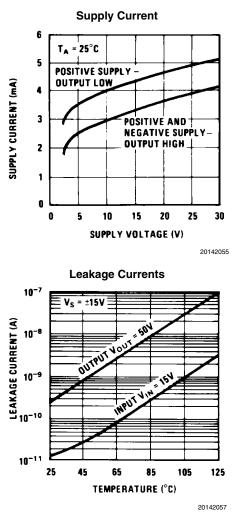

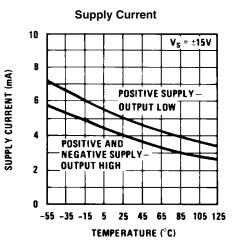

# LM111 Typical Performance Characteristics

20142048

# **Application Hints**

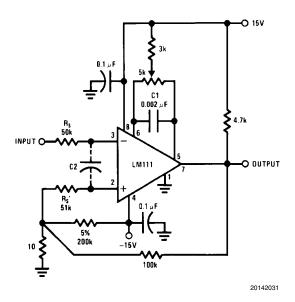

#### CIRCUIT TECHNIQUES FOR AVOIDING OSCILLATIONS IN COMPARATOR APPLICATIONS

When a high-speed comparator such as the LM111 is used with fast input signals and low source impedances, the output response will normally be fast and stable, assuming that the power supplies have been bypassed (with 0.1  $\mu$ F disc capacitors), and that the output signal is routed well away from the inputs (pins 2 and 3) and also away from pins 5 and 6.

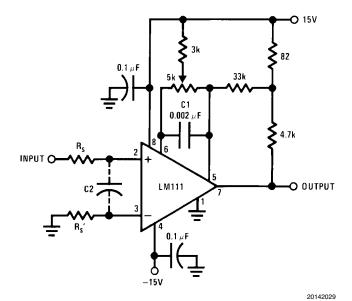

However, when the input signal is a voltage ramp or a slow sine wave, or if the signal source impedance is high (1 k $\Omega$  to 100 k $\Omega$ ), the comparator may burst into oscillation near the crossing-point. This is due to the high gain and wide bandwidth of comparators such as the LM111. To avoid oscillation or instability in such a usage, several precautions are recommended, as shown in *Figure 1* below.

- 1. The trim pins (pins 5 and 6) act as unwanted auxiliary inputs. If these pins are not connected to a trim-pot, they should be shorted together. If they are connected to a trim-pot, a 0.01  $\mu$ F capacitor C1 between pins 5 and 6 will minimize the susceptibility to AC coupling. A smaller capacitor is used if pin 5 is used for positive feedback as in *Figure 1*.

- 2. Certain sources will produce a cleaner comparator output waveform if a 100 pF to 1000 pF capacitor C2 is connected directly across the input pins.

20142056

- 3. When the signal source is applied through a resistive network, R<sub>S</sub>, it is usually advantageous to choose an R<sub>S</sub> ' of substantially the same value, both for DC and for dynamic (AC) considerations. Carbon, tin-oxide, and metal-film resistors have all been used successfully in comparator input circuitry. Inductive wire wound resistors are not suitable.

- 4. When comparator circuits use input resistors (e.g. summing resistors), their value and placement are particularly important. In all cases the body of the resistor should be close to the device or socket. In other words there should be very little lead length or printed-circuit foil run between comparator and resistor to radiate or pick up signals. The same applies to capacitors, pots, etc. For example, if  $R_s=10 \ k\Omega$ , as little as 5 inches of lead between the resistors and the input pins can result in oscillations that are very hard to damp. Twisting these input leads tightly is the only (second best) alternative to placing resistors close to the comparator.

- 5. Since feedback to almost any pin of a comparator can result in oscillation, the printed-circuit layout should be engineered thoughtfully. Preferably there should be a ground plane under the LM111 circuitry, for example, one side of a double-layer circuit card. Ground foil (or, positive supply or negative supply foil) should extend between the output and the inputs, to act as a guard. The foil connections for the inputs should be as small and compact as possible, and should be essentially surrounded by ground foil on all sides, to guard against

capacitive coupling from any high-level signals (such as the output). If pins 5 and 6 are not used, they should be shorted together. If they are connected to a trim-pot, the trim-pot should be located, at most, a few inches away from the LM111, and the 0.01  $\mu$ F capacitor should be installed. If this capacitor cannot be used, a shielding printed-circuit foil may be advisable between pins 6 and 7. The power supply bypass capacitors should be located within a couple inches of the LM111. (Some other comparators require the power-supply bypass to be located immediately adjacent to the comparator.)

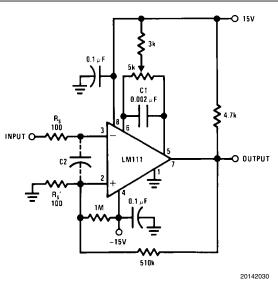

6. It is a standard procedure to use hysteresis (positive feedback) around a comparator, to prevent oscillation, and to avoid excessive noise on the output because the comparator is a good amplifier for its own noise. In the circuit of *Figure 2*, the feedback from the output to the positive input will cause about 3 mV of hysteresis. However, if  $R_s$  is larger than 100 $\Omega$ , such as 50 k $\Omega$ , it would not be reasonable to simply increase the value of the positive feedback resistor above 510 k $\Omega$ . The circuit

of *Figure 3* could be used, but it is rather awkward. See the notes in paragraph 7 below.

- 7. When both inputs of the LM111 are connected to active signals, or if a high-impedance signal is driving the positive input of the LM111 so that positive feedback would be disruptive, the circuit of *Figure 1* is ideal. The positive feedback is to pin 5 (one of the offset adjustment pins). It is sufficient to cause 1 to 2 mV hysteresis and sharp transitions with input triangle waves from a few Hz to hundreds of kHz. The positive-feedback signal across the 82 $\Omega$  resistor swings 240 mV below the positive supply. This signal is centered around the nominal voltage at pin 5, so this feedback does not add to the V<sub>OS</sub> of the comparator. As much as 8 mV of V<sub>OS</sub> can be trimmed out, using the 5 k $\Omega$  pot and 3 k $\Omega$  resistor as shown.

- These application notes apply specifically to the LM111 and LF111 families of comparators, and are applicable to all high-speed comparators in general, (with the exception that not all comparators have trim pins).

Pin connections shown are for LM111H in the H08 hermetic package

#### FIGURE 1. Improved Positive Feedback

Pin connections shown are for LM111H in the H08 hermetic package

FIGURE 2. Conventional Positive Feedback

FIGURE 3. Positive Feedback with High Source Resistance

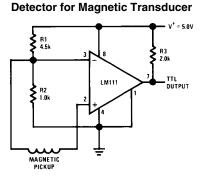

## Typical Applications (Note 13)

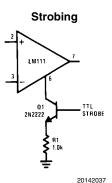

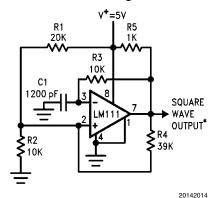

Note: Do Not Ground Strobe Pin. Output is turned off when current is pulled from Strobe Pin.

Note 11: Increases typical common mode slew from 7.0V/ $\mu$ s to 18V/ $\mu$ s.

20142039

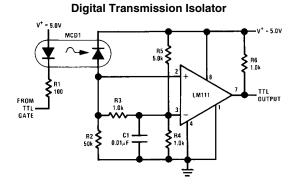

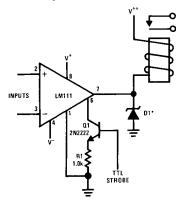

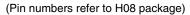

#### **Relay Driver with Strobe**

20142040

20142041

\*Absorbs inductive kickback of relay and protects IC from severe voltage transients on V^++ line.

Note: Do Not Ground Strobe Pin.

Strobing off Both Input and Output Stages (Note Typical input current is 50 pA with inputs strobed off.)

Note: Do Not Ground Strobe Pin.

Note 12: Typical input current is 50 pA with inputs strobed off.

Note 13: Pin connections shown on schematic diagram and typical applications are for H08 metal can package.

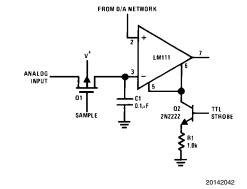

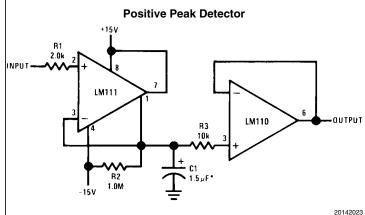

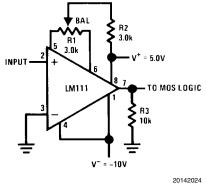

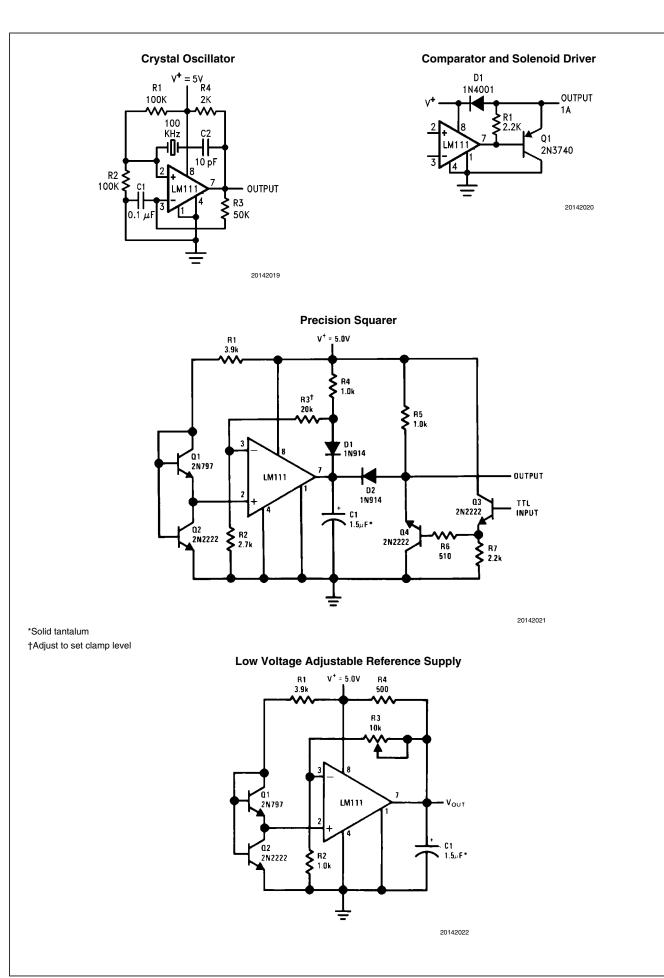

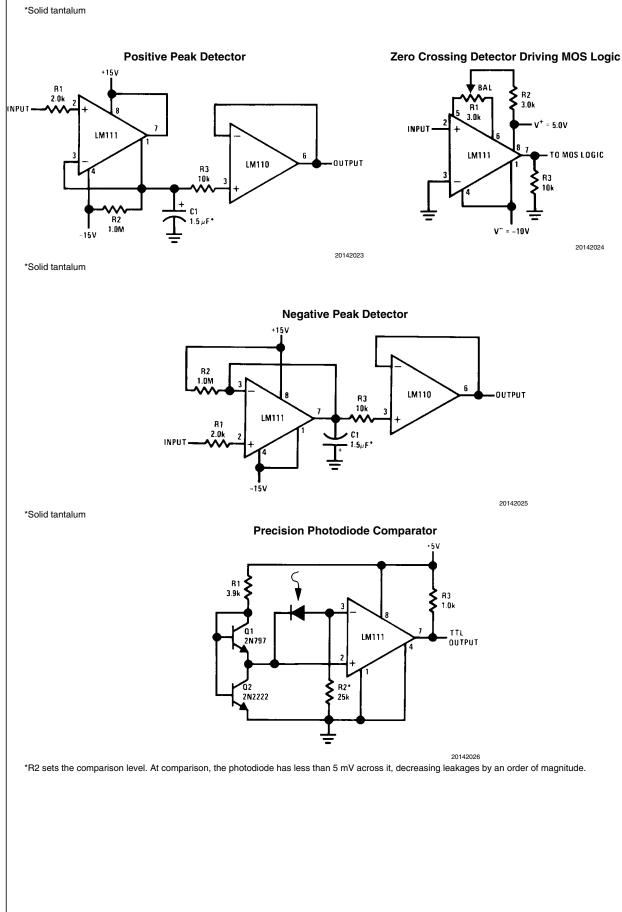

#### Zero Crossing Detector Driving MOS Logic

\*Solid tantalum

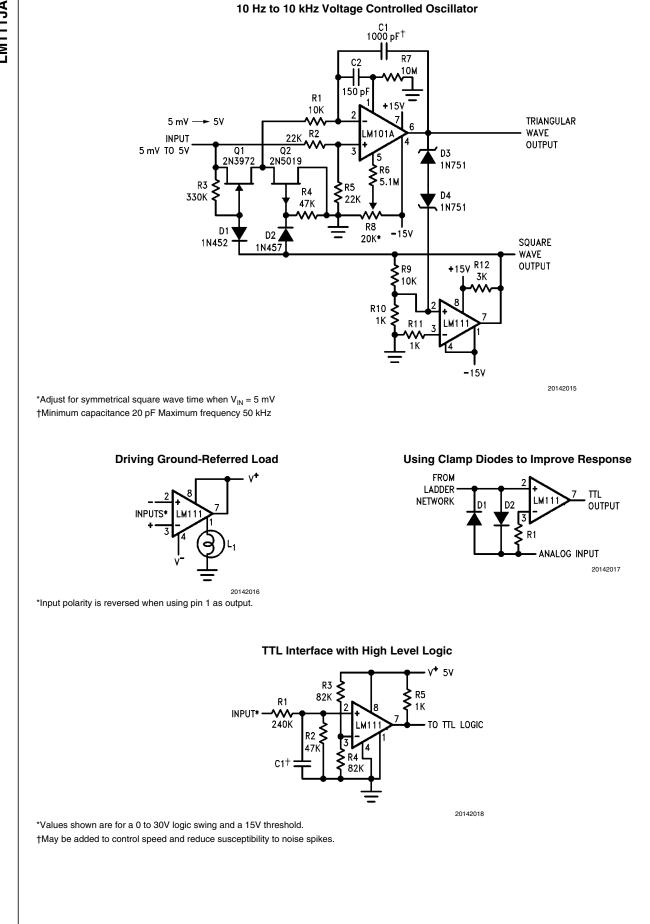

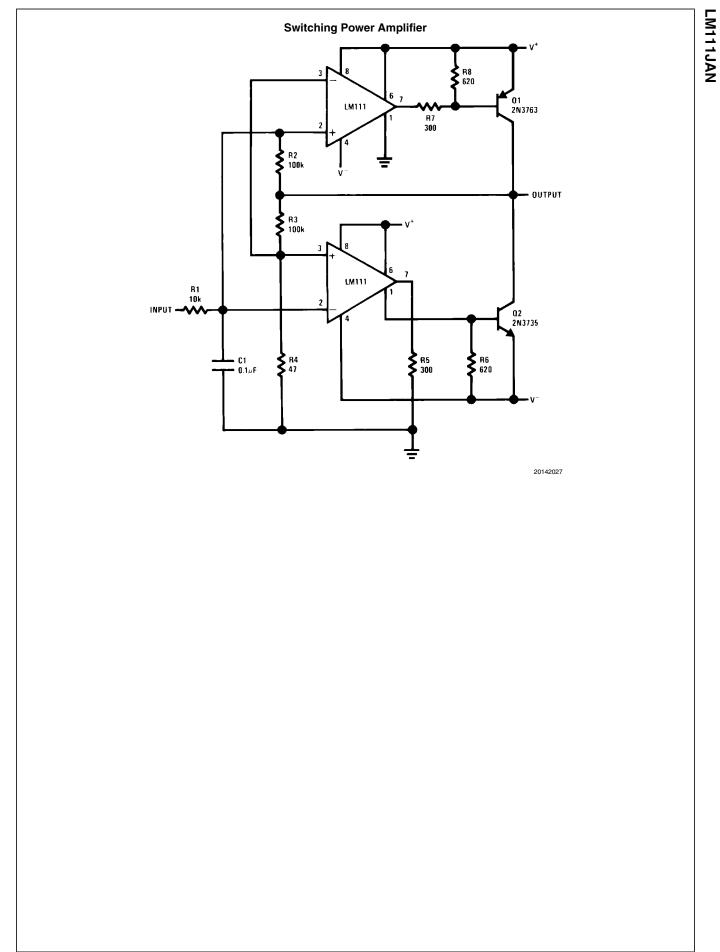

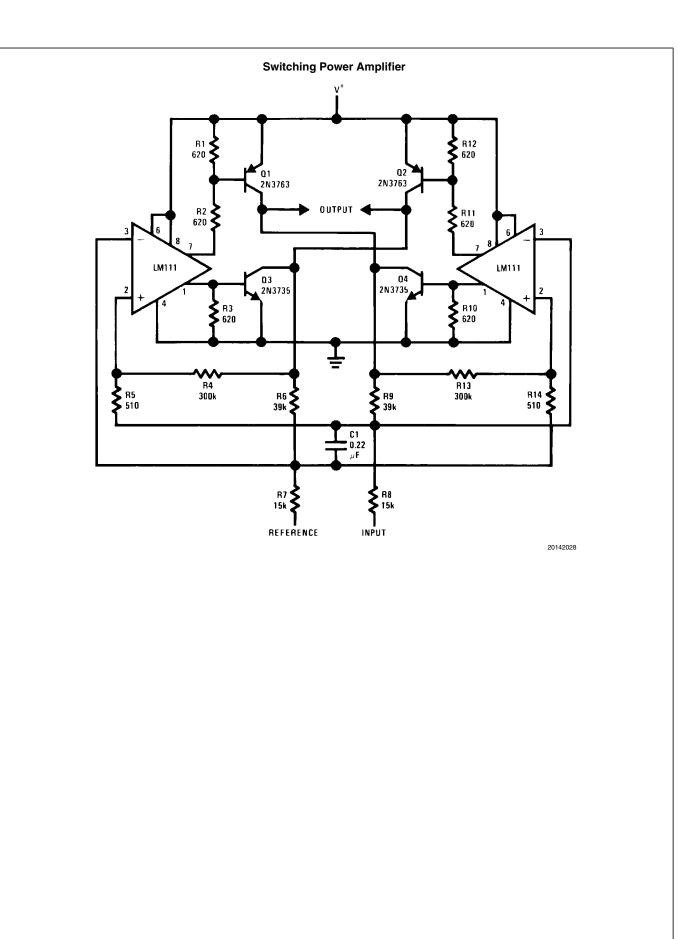

# **Typical Applications**

#### Zero Crossing Detector Driving MOS Switch

100 kHz Free Running Multivibrator

\*TTL or DTL fanout of two

| ~      |  |

|--------|--|

| $\geq$ |  |

| _      |  |

| -      |  |

| -      |  |

| ے      |  |

| ⋗      |  |

| ź      |  |

# **Revision History Section**

| Released | Revision | Section                       | Originator | Changes                                                                                                 |

|----------|----------|-------------------------------|------------|---------------------------------------------------------------------------------------------------------|

| 05/09/05 | A        | New Release, Corporate format | L. Lytle   | 1 MDS data sheets converted into one Corp.<br>data sheet format. MJLM111–X Rev 0D3 will<br>be archived. |

|          |          |                               |            |                                                                                                         |

Notes

# **Notes**

| Products                       |                              | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLÉTENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center new.feedback@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe **Technical Support Center** Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288

National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan **Technical Support Center** Email: jpn.feedback@nsc.com

www.national.com

Email: