# **OKI Semiconductor**

**FEDL87V5002-01** Issue Date: Sep. 1, 2005

# **ML87V5002**

Audio Delay IC with Built-in 2-Mbit DRAM

#### **GENERAL DESCRIPTION**

The ML87V5002 has been developed for solving "Lip-sync problems" in DVD systems, hard disc recording devices, digital TVs and Home Theater Systems. The ML87V5002 can delay the digital audio signal of each of eight channels by setting each register. The ML87V5002 is suitable for synchronizing sounds with motions when loads are too heavy for DSP to control audio delay.

The ML87V5002 does not require any external memory for the audio delay because the ML87V5002 has a built-in 2-Mbit DRAM. The maximum delay time is, for example, 341.3 ms at 48 kHz in 8-ch mode and 1.365 sec at 48 kHz in 2-ch mode. Supporting two to eight audio channels; the ML87V5002 is suitable for applications ranging from simple stereo systems to multi-channel systems. The granularity of the delay time is the sampling period, or Ts. The delay time of each channel can be set in steps of Ts.

The ML87V5002 interfaces to most audio LSIs since the ML87V5002 supports general digital audio formats, such as  $I^2S$ , right justified, and left justified. In addition, suitable digital audio formats can be selected as each of the input and output formats.

#### **FEATURES**

- **Digital audio delay control:** The digital audio signals input from the DI0-DI3 pins are delayed for specific delay times set by an external device and are output from the DO0-DO3 pins.

- No external memory: No external memory is required for the delay because the 2-Mbit DRAM is included.

- Three digital-audio formats: I<sup>2</sup>S, right justified and left justified formats.

- Input/output format settings: I<sup>2</sup>S, right justified, or left justified format can be selected as each of the input and output formats.

- **Data bit lengths:** 16/20/24/32 bits

- Wide range sampling frequencies: 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, and 192 kHz

- Maximum audio delay time:

The maximum delay time (when the audio data length is 16 bits)

- 1.365 sec (48 kHz, 2-ch mode)

- 682.5 ms (96 kHz, 2-ch mode)

- 341.3 ms (192 kHz, 2-ch mode)

- 341.3 ms (48 kHz, 8-ch mode)

- 170.7 ms (96 kHz, 8-ch mode)

- 85.3 ms (192 kHz, 8-ch mode)

- Standard host interface: I<sup>2</sup>C slave interface is supported.

- Minimum delay time step: The granularity of delay time is Ts.

- Independent delay time setting: The delay time of each channel can be set.

- General power supply voltage:  $3.3 \text{ V} \pm 0.3 \text{V}$

- 5V tolerant I/O: Audio interface inputs, I<sup>2</sup>C, and INT are tolerant to 5 V.

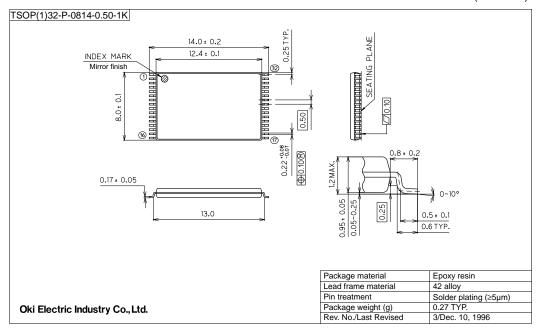

- Package:

32-pin plastic TSOP type I (TSOP(1)32-P-0814-0.50-1K)

#### Note:

- · System clock requirements

- Frequency

The frequency of the system clock should be 128 times the sampling frequency or more. When the sampling frequency is 192 kHz, be sure to set the system clock frequency at 128 times the sampling frequency.

- Phase

The system clock should be synchronized with LRCK and the BCK. In synchronized condition, the phase variation is acceptable.

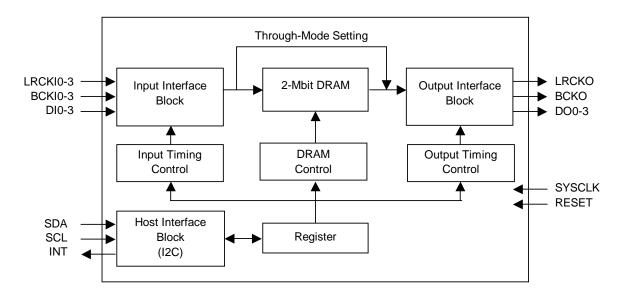

#### **BLOCK DIAGRAM**

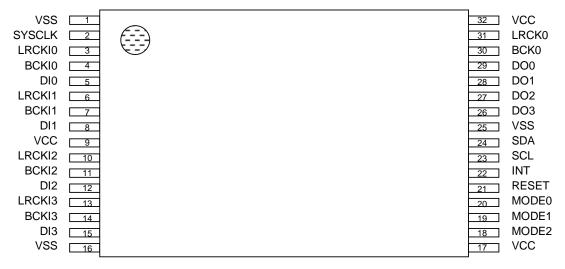

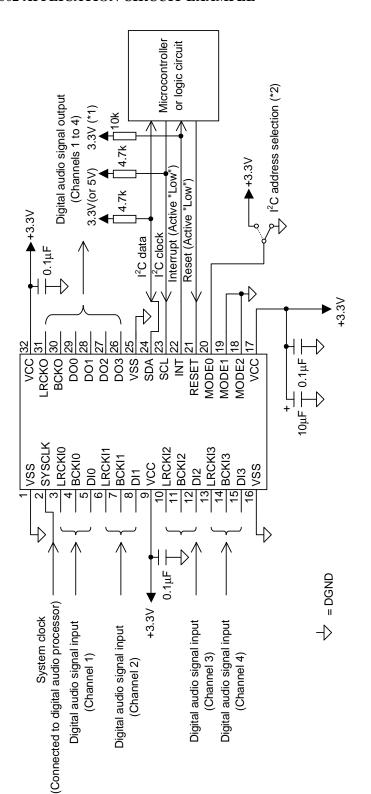

#### PIN CONFIGURATION (TOP VIEW)

32-Pin Plastic TSOP Type I

## PIN DESCRIPTION

| Pin     | Symbol | I/O      | Description                                                                                             |

|---------|--------|----------|---------------------------------------------------------------------------------------------------------|

| 3       | LRCKI0 |          | The LRCK inputs of the input interface                                                                  |

| 6       | LRCKI1 |          | In the 2-channel mode, LRCKI0 to LRCKI3 correspond to DI0 to DI3,                                       |

| 10      | LRCKI2 | <b>!</b> | respectively.                                                                                           |

| 13      | LRCKI3 |          | The polarity of LRCKI can be set by the internal register.                                              |

| 4       | BCKI0  | 1        | The BCK inputs of the input interface                                                                   |

| 7       | BCKI1  |          | In the 2-channel mode, BCKI0 and BCKI3 correspond to DI0 to DI3,                                        |

| 11      | BCKI2  |          | respectively.                                                                                           |

| 14      | BCKI3  |          | The number of BCK pulses in the 1LRCK should be 2× the number of the input bits or more.                |

| 5       | DI0    | I        | The data input pins of the input interface                                                              |

| 8       | DI1    |          | The data is latched in at the rising edges of BCKI0-3.                                                  |

| 12      | DI2    |          |                                                                                                         |

| 15      | DI3    |          |                                                                                                         |

| 31      | LRCKO  | 0        | The LRCK output pin of the output interface                                                             |

|         |        |          | The polarity of LRCKO can be set by the internal register.                                              |

| 30      | BCKO   | 0        | The BCK output pin of the output interface                                                              |

|         |        |          | In the internal generation mode, the number of BCK pulses in 1LRCK can be set by the internal register. |

| 29      | DO0    | 0        | The data output pins of the output interface                                                            |

| 28      | DO1    |          | The data is output at the falling edge of BCKO.                                                         |

| 27      | DO2    |          |                                                                                                         |

| 26      | DO3    |          |                                                                                                         |

| 20      | SCL    | ı        | The clock input pin of I <sup>2</sup> C (SCL)                                                           |

| 24      | SDA    | I/O      | The address data pin of I <sup>2</sup> C (SDA)                                                          |

| 22      | INT    | 0        | The output pin for the interrupt signal to the host CPU                                                 |

|         |        |          | Open drain output                                                                                       |

| 2       | SYSCLK | I        | The input pin of system clock                                                                           |

|         |        |          | The system clock should be synchronized with LRCKI and BCKI and the                                     |

|         |        | ļ .      | frequency should be 128 times the sampling frequency or more.                                           |

| 21      | RESET  | I        | The reset pin of the ML87V5002                                                                          |

|         |        |          | Reset is continued while this pin is low.                                                               |

| 20      | MODE0  | I        | I <sup>2</sup> C address setting pins                                                                   |

| 19      | MODE1  |          |                                                                                                         |

| 18      | MODE2  |          |                                                                                                         |

| 9,17,32 | VCC    | PW       | Power supply                                                                                            |

| 1,16,25 | VSS    | PW       | Ground                                                                                                  |

Note:

The equal supply voltage should be applied to each VCC pin. The equal supply voltage should be applied to each VSS pin. The input pins and I/O pins are tolerant to 5 V.

The output pins support 3.3 V and should not be connected to signal lines with voltages exceeding the supply voltage (VCC).

## ABSOLUTE MAXIMUM RATINGS

| Parameter                    | Symbol           | Condition | Rating Value | Unit |

|------------------------------|------------------|-----------|--------------|------|

| Power Supply Voltage         | VCC              | Ta = 25°C | -0.3 to +4.6 | V    |

| Input Voltage                | Vı               | Ta = 25°C | -0.3 to +6.0 | V    |

| Short Circuit Output Current | los              | Ta = 25°C | 50           | mA   |

| Power Dissipation            | P <sub>D</sub>   | Ta = 25°C | 1            | W    |

| Operating Temperature        | T <sub>opr</sub> | _         | 0 to 70      | °C   |

| Storage Temperature          | $T_{stg}$        | _         | -50 to +150  | °C   |

Note: Stressing the device beyond the "ABSOLUTE MAXIMUM RATINGS", even momentarily, may cause permanent damage.

## RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------|--------|------|------|------|------|

| Power Supply Voltage  | VCC    | 3.0  | 3.3  | 3.6  | V    |

| Power Supply Voltage  | VSS    | 0    | 0    | 0    | V    |

| Operating Temperature | Та     | 0    | _    | 70   | °C   |

## PIN CAPACITANCE

(VCC =  $3.3 \text{ V} \pm 0.3 \text{V}$ , f = 1 MHz, Ta =  $25^{\circ}$ C)

| Parameter                | Symbol         | Min. | Max. | Unit |

|--------------------------|----------------|------|------|------|

| Input Capacitance        | C <sub>i</sub> | _    | 7    | pF   |

| Input Output Capacitance | Cio            | _    | 7    | pF   |

| Output Capacitance       | Co             | _    | 7    | pF   |

## **ELECTRICAL CHARACTERISTICS**

#### **DC** Characteristics

(Ta = 0 to 70°C, VCC = 3.3 V  $\pm$ 0.3V, VSS = 0 V)

| Parameter                           | Symbol           | Condition                     | Min.     | Max.     | Unit |

|-------------------------------------|------------------|-------------------------------|----------|----------|------|

| High-level input voltage            | $V_{\text{IH1}}$ | _                             | VCC×0.7  | 5.5      | V    |

| Low-level input voltage             | $V_{IL1}$        | _                             | -0.3     | VCC×0.3  | V    |

| High-level input voltage (SDA, SCL) | $V_{\text{IH}2}$ | _                             | VCC×0.75 | 5.5      | V    |

| Low-level input voltage (SDA, SCL)  | $V_{\text{IL2}}$ | _                             | -0.3     | VCC×0.25 | V    |

| High-level output voltage           | $V_{OH}$         | $I_{OH} = -4 \text{ mA}$      | 2.4      | _        | V    |

| Low-level output voltage            | $V_{OL}$         | $I_{OL} = 4 \text{ mA}$       | 1        | 0.4      | V    |

| Low-level output voltage (SDA, INT) | $V_{OL2}$        | $I_{OL} = 4 \text{ mA}$       |          | 0.4      | V    |

| Input Leakage Current               | Iμ               | V <sub>IN</sub> = VCC or VSS  | -10      | +10      | μΑ   |

| Output Leakage Current              | I <sub>LO</sub>  | V <sub>OUT</sub> = VCC or VSS | -10      | +10      | μΑ   |

| Supply Current (during operation)   | $I_{DD1}$        | SYSCLK = 24.576 MHz           |          | 30       | mA   |

| Supply Current (during standby)     | I <sub>DD2</sub> | Input pin = 0 V               | _        | 4.5      | mA   |

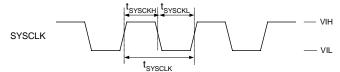

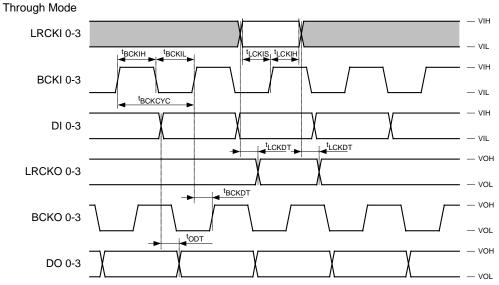

#### **AC Characteristics**

The SYSCLK (system clock) should be synchronized with inputs LRCK and BCK.

(Ta = 0 to 70°C, VCC = 3.3 V  $\pm$ 0.3V, VSS = 0 V)

|                                              |                     | \                     | ,    |      |      |

|----------------------------------------------|---------------------|-----------------------|------|------|------|

| Parameter                                    | Symbol              | Condition             | Min. | Max. | Unit |

| SYSCLK Cycle Time                            | t <sub>SYSCLK</sub> | _                     | 40   | _    | ns   |

| SYSCLK High-Level Time                       | t <sub>SYSCKH</sub> | _                     | 16   | _    | ns   |

| SYSCLK Low-Level Time                        | tsysckl             | _                     | 16   | _    | ns   |

| BCKI Cycle Time                              | t <sub>BCLKI</sub>  | _                     | 80   |      | ns   |

| BCKI High-Level Time                         | t <sub>BCKIH</sub>  | _                     | 30   |      | ns   |

| BCKI Low-Level Time                          | t <sub>BCKIL</sub>  | _                     | 30   |      | ns   |

| DI Setup Time (Ext. sync. / Int. gen.)       | t <sub>DIS</sub>    | _                     | 6    | _    | ns   |

| DI Hold Time (Ext. sync. / Int. gen.)        | t <sub>DIH</sub>    | _                     | 8    | _    | ns   |

| LRCKI Setup Time                             | t <sub>LCKIS</sub>  | _                     | 6    | _    | ns   |

| LRCKI Hold Time                              | t <sub>LCKIH</sub>  | _                     | 8    | _    | ns   |

| BCKO Delay Time (Ext. sync. / Through mode)  | t <sub>BCKDT</sub>  | _                     |      | 15   | ns   |

| DO Delay Time (Ext. sync. / Int. gen.)       | t <sub>ODD</sub>    | C <sub>L</sub> = 20pF | -7   | 12   | ns   |

| DO Delay Time (Through Mode)                 | t <sub>ODT</sub>    | $C_L = 20pF$          |      | 15   | ns   |

| LRCKO Delay Time (Int. gen.)                 | t <sub>LCKOD</sub>  | $C_L = 20pF$          | -7   | 12   | ns   |

| LRCKO Delay Time (Ext. sync. / Through mode) | t <sub>LCKDT</sub>  | C <sub>L</sub> = 20pF | _    | 15   | ns   |

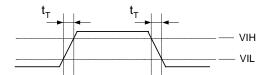

| Input Rise Time, Input Fall Time             | t⊤                  | Except SDA and SCL    | 1    | 5    | ns   |

| Reset Pulse Time                             | t <sub>RSTP</sub>   | _                     | 100  | _    | ns   |

Note: The input voltage level is measured at VCC/0V. The confront level of the output signal is measured at VCC/2.

#### **Input/Output Waveforms**

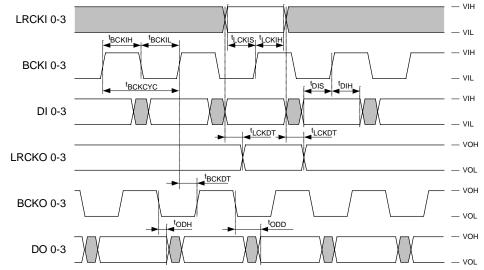

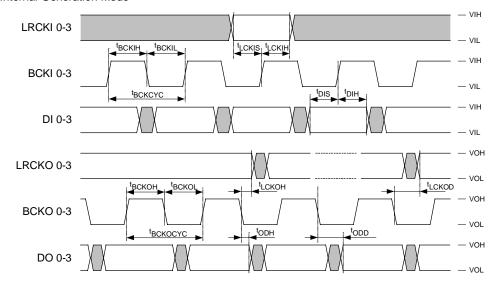

Figure 1 System Clock Diagram

Figure 2 Through-Mode Input and Output Timing Diagram

### External Synchronization Mode

Figure 3 External Sync. Mode Input and Output Timing Diagram

## Internal Generation Mode

Figure 4 Internal Sync. Mode Input and Output Timing Diagram

Figure 5 Rise Time, Fall Time  $(t_T)$

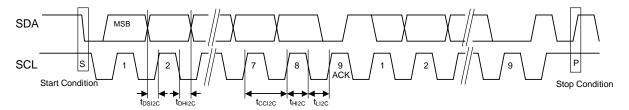

#### I<sup>2</sup>C Interface Timing

The internal register setting is done via  $I^2C$  Interface. The interface is based on the standard mode  $I^2C$  bus (SCL frequency = 100 kHz).

Fig. 6 shows the basic timing. Table 1 summarizes the AC Characteristics of the standard mode I<sup>2</sup>C bus. Do not change the "SDA" level as long as the "SCL" is high except the stop or start condition. Refer to the "AC Characteristics" to know the values of timing parameters.

Figure 6 I<sup>2</sup>C Interface Basic Timing

Table 1 AC Characteristics of Standard Mode I<sup>2</sup>C Bus (SCL Frequency = 100 kHz)

| Parameter                              | Symbol             | Min. | Max. | Unit |

|----------------------------------------|--------------------|------|------|------|

| Reset Pulse Time                       | t <sub>RSTP</sub>  | 100  |      | ns   |

| I <sup>2</sup> C Clock Cycle Time      | t <sub>CCI2C</sub> | 10   | _    | μs   |

| I <sup>2</sup> C Clock High-Level Time | t <sub>HI2C</sub>  | 4    | _    | μs   |

| I <sup>2</sup> C Clock Low-Level Time  | t <sub>LI2C</sub>  | 4.7  | _    | μs   |

| I <sup>2</sup> C Data Setup Time       | t <sub>DSI2C</sub> | 250  | _    | ns   |

| I <sup>2</sup> C Data Holdup Time      | t <sub>DHI2C</sub> | 0    | 3.45 | μs   |

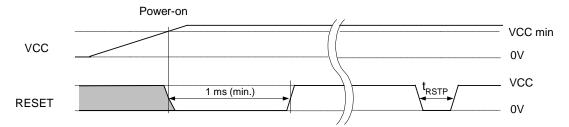

#### Power-On

For the normal operation of the ML87V5002, the pins other than the RESET pin should be maintained at a low level until the VCC has reached the specified voltage level after powered on. Thereafter this LSI is reset by maintaining the RESET pin at a low level for 1 ms or more. The release of the RESET level leads to starting normal operation.

To reset this LSI during normal operation, set the RESET pin at a "L" level for a time  $t_{RSTP}$  or more. To power on again after powered off, verify that VCC is 0 V.

Figure 7 Power-On Sequence

#### **FUNCTIONAL OPERATION**

#### **Mode of Operation**

The ML87V5002 has two modes, 2-channel mode and 8-channel mode. Mode setting is done by the host CPU via the  $I^2C$  interface. When internal register "NOF\_CH" (SUB:00h-bit[2]) is set to "0", the 2-channel mode is set. When "NOF CH" is set to "1", the 8-channel mode is set.

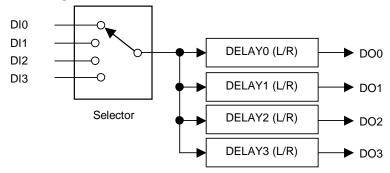

#### • 2-channel mode

In the 2-channel mode, there are four input groups, group0-3. The inputs in group-0 are comprised of LRCK0,BCKI0 and DI0. The inputs in group-1 are LRCK1, BCK1 and DI1. The inputs in group-2 are LRCK12, BCKI2 and DI2. The inputs in group-3 are LCRKI3, BCKI3 and DI3. That is, in the 2-channel mode, it looks four independent delay devices having a common 2-channel input can be provided. The common 2-channel input is connected to the output terminal of the selector that has four input as shown in Fig.7. One of the four inputs can be selected by the setting of the internal register "DI\_SEL" (SUB:00h-bit[1:0]) as shown in the Table 2.

Table 2 Input Source Selection (SUB:00h-bit[1:0])

| DI_ | SEL | Selectable Input |

|-----|-----|------------------|

| [1] | [0] | Source           |

| 0   | 0   | DI0              |

| 0   | 1   | DI1              |

| 1   | 0   | DI2              |

| 1   | 1   | DI3              |

The 2-channel input audio data is selected and transferred to the four delay devices via the common input terminal and being delayed for certain periods. The delayed data are output from DO0 - DO3 controlled by LRCKO and BCKO. Each delay time for the DO0 - DO3 can be set independently by the setting of internal regisiter, "DLYx\_L" ( x=0 - 7, SUB:10h-bit[7:0] - SUB:1fh-bit[7:0]) and "DLYx\_H" ( x=0 - 7, SUB:10h-bit[7:0] - SUB:1fh-bit[7:0]). The settings are shown in the Table 3.

Table 3 Delay Time Setting of Each Output

|                | L/R  | Channel | Register Name | SUB          |

|----------------|------|---------|---------------|--------------|

|                | اء ا | CLIO    | DLY0_L        | 10h-bit[7:0] |

| DO0 Delay Time | Lch  | CH0     | DLY0_H        | 11h-bit[7:0] |

| DELAY0         | Rch  | CH1     | DLY1_L        | 12h-bit[7:0] |

|                | KCII | СП      | DLY1_H        | 13h-bit[7:0] |

|                | Lch  | CH2     | DLY2_L        | 14h-bit[7:0] |

| DO1 Delay Time | LCn  | CHZ     | DLY2_H        | 15h-bit[7:0] |

| DELAY1         | Rch  | СНЗ     | DLY3_L        | 16h-bit[7:0] |

|                |      |         | DLY3_H        | 17h-bit[7:0] |

|                | Lch  | h CII4  | DLY4_L        | 18h-bit[7:0] |

| DO2 Delay Time | LCn  | CH4     | DLY4_H        | 19h-bit[7:0] |

| DELAY2         | Rch  | CH5     | DLY5_L        | 1ah-bit[7:0] |

|                | KCII | СПЭ     | DLY5_H        | 1bh-bit[7:0] |

|                | Lch  | CH6     | DLY6_L        | 1ch-bit[7:0] |

| DO3 Delay Time | LCN  | CHO     | DLY6_H        | 1dh-bit[7:0] |

| DELAY3         | Rch  | CH7     | DLY7_L        | 1eh-bit[7:0] |

|                | KCII | СП      | DLY7_H        | 1fh-bit[7:0] |

Figure 8 shows the concept of the 2-channel mode.

- \*1. DELAY0 (L/R), DELAY1 (L/R), DELAY2 (L/R), and DELAY3 (L/R) can be set independently.

- \*2. The input format and sampling frequency for each of DI0 to DI3 can be set.

- \*3. The output format and the input format can be set independently, however, the output format for DO0 to DO3 is equal.

Figure 8 Conceptual Diagram of 2-Channel Mode

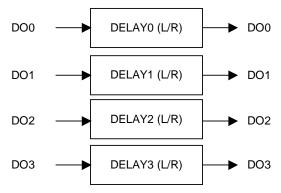

#### • 8-channel mode

In the 8-channel mode the ML87V5002 operates as an 8-channel audio interface input. In this case, LRCKI0 and BCKI0 are used. Note that LRCKI1, LRCKI2, LRCKI3, BCKI1, BCKI2 and BCKI3 are not used in the 8-channel mode. The data of each channel is input to DI0 to DI3 and is delayed for the set delay time. The data input to DI0 to DI3 are output from DO0 to DO3 having certain delay times, respectively. The delay time of each input can be set by the internal registers "DLYx\_L" (x=0 to 7, SUB:10h-bit[7:0]) to SUB:1fh-bit[7:0]) and "DLYx\_H" (x=0 to 7, SUB:10h-bit[7:0]).

Figure 9 shows the concept of 8-channel mode

- \*4. DELAY0 (L/R), DELAY1 (L/R), DELAY2 (L/R), and DELAY3 (L/R) can be set independently.

- \*5. The output format and the input format can be set independently.

Figure 9 Conceptual Diagram of 8-Channel Mode

#### **Operation Sequence**

When reset is released, the internal register INIT( SUB:08h-bit[0] ) is set to "1" and the ML87V5002 starts the initial sequence and then starts its normal operation.

The ML87V5002 keeps the command-wait state (waiting for the register setting of the host CPU) after the initial sequence. In this command-wait state, the delay operation is not started and the output keeps mute states. The delay operation is started by writing each parameter from the host CPU to the internal register and setting internal register "ENBL" (SUB:07h-bit[7]) to "1".

When internal register "ENBL" (SUB:07h-bit[7]) is set to "1", the ML87V5002 starts to investigate the validity of the settings. If the settings are proper, internal register "RUN" (SUB:08h-bit[7]) is set to "1", the mute state is released, and the delay operation is started.

#### • Suspension of the delay operation

This LSI sets the ENBL and RUN bits to "0" and suspends the delay operation when any of the following events occurs:

- 1. "0" is written to internal register ENBL (SUB:07h-bit[7]).

- 2. The signals of LRCKI and BCK become out of synchronization.

- 3. The setting of the audio format except the delay parameters is changed.

- 4. Input source channel is changed.

- 5. Operation mode is changed.

- 6. The operation is started on condition that parameters at settings are not proper.

- 7. The BCK pulses less than the data length are input.

- 8. Overrun or underrun occurs due to a mismatch in clock between the input and output.

When the suspension is caused by event 2, 6, 7, or 8 above, the LSI mutes the output immediately and sets the corresponding error bits in the internal registers shown in Table 4 to "1".

Register **Error Description SUB** Name Set when any change is detected in the input timing after resuming TMG\_ERR 09h-bit[7] the operation and the LSI suspends the delay operation. Indicates the delay operation is suspended due to inconsistency of CFG ERR 09h-bit[6] the setting values. Set when the number of BCK pulses in LRCK is less than the input data length or the output data length in external synchronization BCK ERR 09h-bit[5] mode after starting the operation. The delay operation is suspended. Set when the output data cycle is slower than the input cycle and the **OVRN** 09h-bit[4] delay buffer overflows, and the delay operation is suspended. Set when the output data cycle is faster than the input cycle and the **UDRN** 09h-bit[3]

delay buffer becomes empty, and the delay operation is suspended.

**Table 4 Error Status Registers**

• Restart of delay operation (restart by a command / auto-restart)

There are two options, "restart by a command" and "auto-restart", for restarting the delay operation by setting the internal register.

In the case of the "restart by a command", the INT output is set at "L" at athe same time as error detection. The delay operation is restarted by removing the cause of the error and writing "1" to the "ENBL" bit.

In the case of the "auto-restart" option (the internal register AUTORSTRT (SUB 07h-bit[1] = "1"), if the suspension is due to an error [TMG\_ERR, OVRN, or UDRN] excluding CFG\_ERR and BCK\_ERR, set the error bit to "1" to restart the delay operation. (In this case, this LSI does not set the INT output at "L" or not generate the interrupt even if the interrupt mask register is cleared.)

In the case of the "auto-restart" option, if an error is detected and CFG\_ERR or BCK\_ERR is set to "1", the LSI clears the ENBL bit to "0" and stops the delay operation. (In this case, this LSI sets the INT output at "L" and generates the interrupt if the interrupt mask register has been cleared.) Since the error bit is not automatically cleared, the host CPU writes "0" to the corresponding bit and clears the error bit.

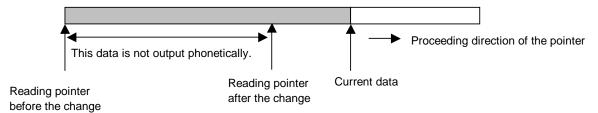

• Change of the delay parameters during the delay operation

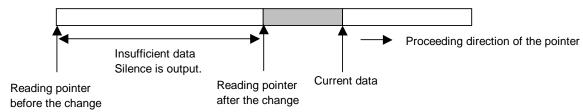

When the newly set value of the delay time is less than the previously set value, the reading pointer is moved forward and the operation is performed with a new delay time. In this case, the data existing between the times before and after the change is not output phonetically. (Figure 10)

Figure 10 When a delay time is changed (when the delay time is shorter than the previously set time.)

Meanwhile, when the newly set value is longer than the former set value, the reading pointer should be moved backward and the operation should be performed with a new delay length. Output is muted ("0" output) for the insufficient data (Figure 11).

Figure 11 When a delay time is changed (when the delay time is longer than the previously set time.)

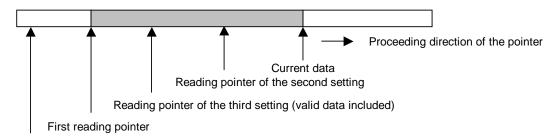

When a delay time is shortened once and then it is lengthened, the audio data is output when the valid audio data is in the memory. Output is muted ("0" output) until the pointer reaches the valid data when no valid audio data is in the memory. (Figure 12)

Reading pointer of the third setting (valid data not included)

Figure 12 When a delay time is shortened once and then lengthened

#### **Operation of Audio Input/Output Port**

By setting the audio input ports (DI0 to DI3, LRCKI0 to LRCKI3, and BCKI0 to BCKI3) and the audio output port (DO0 to DO3, LRCKO, and BCKO) according to the internal register provided in the table 5-10, the formats can be changed. Figure 12 shows the formats supported by the ML87V5002.

Table 5 LRCKI Polarity Specification (SUB:01h-bit[4])

| POLI | LRCKI polarity |

|------|----------------|

| [0]  | LNCKI polarity |

| 0    | Non-inverted   |

| 1    | Inverted       |

Table 6 Input Format Specification (SUB:01h-bit[3:2])

| FM  | 1TI | Form of          |

|-----|-----|------------------|

| [1] | [0] | Format           |

| 0   | 0   | Left justified   |

| 0   | 1   | Right justified  |

| 1   | 0   | l <sup>2</sup> S |

| 1   | 1   | l <sup>2</sup> S |

Table 7 Input Data Bit Length Specification (SUB:01h-bit[1:0])

| DI_I | LEN | Data hit langth |

|------|-----|-----------------|

| [1]  | [0] | Data bit length |

| 0    | 0   | 16 bits         |

| 0    | 1   | 20 bits         |

| 1    | 0   | 24 bits         |

| 1    | 1   | 32 bits         |

Table 8 LRCKO Polarity Specification (SUB:02h-bit[4])

| POLO | LRCKI polarity   |

|------|------------------|

| [0]  | LINGINI POIAINLY |

| 0    | Non-inverted     |

| 1    | Inverted         |

Table 9 Output Format Specification (SUB:02h-bit[3:2])

| FM  | TO  | Format           |

|-----|-----|------------------|

| [1] | [0] | Folillat         |

| 0   | 0   | Left justified   |

| 0   | 1   | Right justified  |

| 1   | 0   | l <sup>2</sup> S |

| 1   | 1   | l <sup>2</sup> S |

Table 10 Output Data Bit Length Specification (SUB:02h-bit[1:0])

| DO_ | LEN | Data bit length |  |  |  |  |

|-----|-----|-----------------|--|--|--|--|

| [1] | [0] | Data bit length |  |  |  |  |

| 0   | 0   | 16 bits         |  |  |  |  |

| 0   | 1   | 20 bits         |  |  |  |  |

| 1   | 0   | 24 bits         |  |  |  |  |

| 1   | 1   | 32 bits         |  |  |  |  |

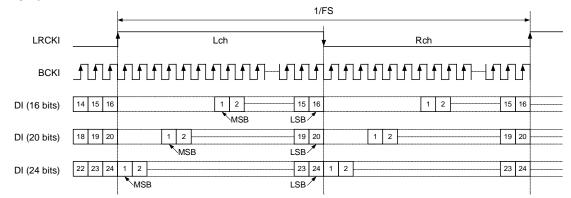

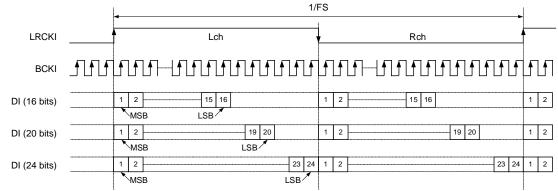

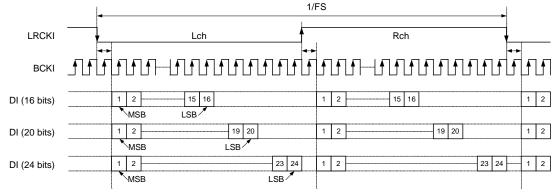

### • Right justified format

#### • Left justified format

## • I<sup>2</sup>S format

#### Notes:

- 1. In the I<sup>2</sup>S format, the MSB data is fixed with a delay of 1 BCK from left justify, and LRCK is inverted.

- 2. The data and LRCK alter on the falling edge of BCK.

- 3. The number of BCK pulses to LRCK requires twice the data length or more.

- 4. This figure shows the case where LRCK is not inverted.

Figure 13 Supported Format

#### Input and Output Data Lengths of DI0-3/DO0-3

This LSI can output data by changing the data length of input data. For instance, the LSI can output the 16-bit data that is input as 20-bit data. When the output bit count is greater than the input bit count, the same value as MSB is output for the lower-order bits. For instance, when the data that is input in a 16-bit length is output in a 20-bit length, the higher-order 16 bits contain the value of the input data and '0' is output in the lower-order 4 bits if MSB is '0' and '1' if MSB is '1'. When the input bit count is greater than the output bit count, the lower-order bits are ignored at output.

However, the data length must be equal to or less than 1/2 of the BCK clock count per LRCK. For instance, when 1 LRCK contains 40 BCKs, the data length must not exceed 20 bits. When the length exceeds 20 bits, BCK\_ERR is set during checking performed at the start of operation, the LSI does not start operation, but activates the INT signal, and reports the occurrence of an error to the host CPU. However, when INTMASK is set (SUB:07h-bit[0] = '1'), the INT signal is not output.

#### External Synchronization Mode/Internal Generation Mode of LRCK/BCK

Two modes are available for signals LRCKO and BCKO, "external synchronous mode (including Through mode)" and "internal generation mode".

In external synchronous mode [INT\_EXT (SUB:00h-bit[3])='0' or THRU (SUB:00h-bit[4])='1'], BCKIx that is selected by a combination of NOF\_CH and DI\_SEL is output through the BCKO pin.

For LRCKO, polarity reversal is performed by POLI, POLO, FMTI, or FMTO for LRCKIx that is selected by a combination of NOF\_CH and DI\_SEL and the result is output.

LRCKO and BCKO are definitely output regardless of the status of the RUN bit when LRCKIx and BCKIx are input.

In internal generation mode [INT\_EXT (SUB:00h-bit[3])='1' and THRU (SUB:00h-bit[4])='0'], LRCKO and BCKO are generated from SYSCLK. As a result, a format different from that of input can be set without being restricted by [output data length  $\leq$  number of BCKIs in LRCK/2] in external synchronous mode.

The LRCKO period can be set in internal register LRCK\_DIV (SUB:04h-bit[3:0]) and the BCKO period can be set in internal register BCK\_DIV (SUB:03h-bit[3:0]). (However, the LRCKO period that is generated by the setting of LRCK\_DIV and BCK\_DIV must match the LRCKI period). In internal generation mode, LRCKO and BCKO are not output while internal register RUN (SUB:08h-bit[7]) is set to '0'. For instance, when the internal generation mode is set immediately after reset, internal register ENBL (SUB:07h-bit[7]) is set to '1' and the RUN bit is set to '0' until delay operation starts. Therefore, LRCKO and BCKO are not output. When operation is stopped due to an error detected during normal operation and the RUN bit is cleared to '0', output of LRCKO and BCKO is stopped. When output of LRCKO and BCKO is stopped due to detection of an error, abnormal LRCKO and BCKO may be output while the operation shifts to a stop state. When the LSI stops operation by writing '0' in the ENBL bit during normal operation, audio data of '0' is output for at least one period of LRCKO and then the LSI stops the operation.

#### **Through Mode**

This LSI can output audio data by performing delay processing by setting internal register THRU (SUB:00h-bit[4]) to '1'. When transition between through modes is performed by setting or resetting the THRU bit, the relationship among DOx, LRCKO, and BCKO may collapse and abnormal LRCKO, LRCKO, and BCKO may be output.

This mode is made available to output audio data without delay when output delay by 1 LRCK causes a problem even if delay time = 0 is set in normal delay operation. Since polarity reversal for LRCK is performed by input and output format registers, POLx and FMTx, set the mode according to the input/output.

#### **SYSCLK**

SYSCLK requires a frequency that is 128 times the sampling frequency and within 12 times BCK. However, since the maximum operation frequency of this LSI is 25MHz, the frequency must not exceed the limit. For instance, when the sampling frequency is 96 kHz, the frequency of 128 times is 12.288 MHz and the frequency of 256 times is 24.576 MHz. Therefore, either frequency can be used.

When the sampling frequency is 192kHz, the frequency of 128 times is 24.576 MHz. In this case, only this frequency can be selected.

LRCKI0 to LRCKI3 and BCKI0 toBCKI3 must synchronize with SYSCLK. As long as the synchronization is maintained, the phase with SYSCLK is irrelevant.

#### I<sup>2</sup>C Address

This LSI can set two types of I2C addresses by the setting of MODE0 to MODE2.

- The I2C address is 0x8C/8D when MODE0 = '0', MODE1 = '0', and MODE2 = '0'

- The I2C address is 0x8E/8F when MODE0= '1', MODE1 = '0', and MODE2 = '0'

Modes other than those indicated above are not allowed since they are test modes of this LSI.

## INTERNAL REGISTERS

## Register Map

| ۵.             |         |         |         | DA       | TA        |            |               |          |               |                                                |

|----------------|---------|---------|---------|----------|-----------|------------|---------------|----------|---------------|------------------------------------------------|

| SA             | BIT7    | BIT6    | BIT5    | BIT4     | BIT3      | BIT2       | BIT1          | BIT0     | Default Value | Function                                       |

| 00h            | -       | -       | CMN_DLY | THRU     | INT_EXT   | NOF_CH     | DI_<br>1      | 0        | xx00_0100b    | Mode setting                                   |

| 01h            |         | -       | -       | POLI     |           | /ITI       |               | LEN      | xxx0_0000b    | Input data                                     |

| $\vdash$       |         |         |         |          | 1<br>EM   | 0<br>ITO   | 1             | 0<br>LEN |               | format setting Output data                     |

| 02h            | -       | -       | -       | POLO     | 1         | 0          | 1             | 0        | xxx0_0000b    | format setting                                 |

| 201            |         |         |         |          |           | BCK        |               | - U      | 04001         | BCKO                                           |

| 03h            |         | -       | -       | -        | 3         | 2          | 1             | 0        | xxxx_0100b    | cycle setting                                  |

| 04h            |         | _       |         |          |           | K_DIV      |               |          | xx01_0000b    | LRCKO                                          |

|                |         |         | 5       | 4        | 3         | 2          | 1             | 0        | 75.01_00002   | cycle setting                                  |

| 05h            | -       | -       | 5       | 4        | 3         | INTVL<br>2 | 1             | 0        | xx01_0110b    | DRAM refresh interval setting                  |

| $\blacksquare$ |         |         |         |          |           |            |               | U        |               | Software                                       |

| 06h            | SFT_RST | -       | -       | -        | -         | -          | -             | -        | 0xxx_xxxxb    | reset                                          |

| 07h            | ENBL    | -       | -       | -        | -         | -          | AUTO<br>RSTRT | INT_MASK | 0xxx_xx01b    | Delay operation control                        |

| 08h            | RUN     | SRC_CHG | SRC_CLK | -        | -         | CFG_ERS    | DRAM          | INIT     | 000x_x001b    | Operation                                      |

| Н              |         |         |         |          |           |            | _RDY          |          | _             | status<br>Eorror                               |

| 09h            | TMG_ERR | CFG_ERR | BCK_ERR | OVRN     | UDRN      | -          | -             | -        | 0000_0xxxb    | status                                         |

| 0ah            |         |         |         |          | SK        |            |               |          | 0000_0000b    | Output data                                    |

|                | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | *****         | mask                                           |

| 10h            | 7       | 6       | 5       | 4        | ′0_L<br>3 | 2          | 1             | 0        | 0000_0000b    | CH0 delay value setting<br>lower-order 8 bits  |

| $\blacksquare$ |         | U       | 3       |          | ′0_H      | 2          |               | U        |               | CH0 delay value setting                        |

| 11h            | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_0000b    | higher-order 8 bits                            |

| 12h            |         |         |         |          | ′1_L      |            |               |          | 0000 0000b    | CH1 delay value setting                        |

|                | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_00002    | lower-order 8 bits                             |

| 13h            | 7       | 6       | 5       | 4        | ′1_H<br>3 | 2          | 1             | 0        | 0000_0000b    | CH1 delay value setting                        |

| $\vdash$       | - /     | 0       | 5       |          | ′2_L      | 2          | ı             | U        |               | higher-order 8 bits<br>CH2 delay value setting |

| 14h            | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_0000b    | lower-order 8 bits                             |

| 15h            |         |         |         | DLY      | ′2_H      |            |               |          | 0000 0000b    | CH2 delay value setting                        |

| 1511           | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_00000    | higher-order 8 bits                            |

| 16h            | 7       | 6       | 5       | 4 DL1    | ′3_L<br>3 | 2          | 1             | 0        | 0000_0000b    | CH3 delay value setting                        |

| $\vdash$       | - /     | 0       | 5       |          | '3_H      | 2          | ı             | U        |               | lower-order 8 bits CH3 delay value setting     |

| 17h            | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_0000b    | higher-order 8 bits                            |

| 18h            |         |         |         | DLY      | ′4_L      | _          |               |          | 0000 0000b    | CH4 delay value setting                        |

| 1011           | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_00000    | lower-order 8 bits                             |

| 19h            | 7       | _       | 5       | DLY<br>4 | ′4_H<br>3 | 2          | 1             | 0        | 0000_0000b    | CH4 delay value setting                        |

| $\vdash$       | - /     | 6       | 5       |          | 3<br>′5_L | 2          | 1             | 0        |               | higher-order 8 bits CH5 delay value setting    |

| 1ah            | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_0000b    | lower-order 8 bits                             |

| 1bh            |         |         |         | DLY      | ′5_H      |            |               |          | 0000 0000b    | CH5 delay value setting                        |

| ווטו           | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_000D     | higher-order 8 bits                            |

| 1ch            | -       |         |         | DL\      |           |            |               |          | 0000_0000b    | CH6 delay value setting                        |

| $\vdash$       | 7       | 6       | 5       | 4<br>DLY | 3<br>6 H  | 2          | 1             | 0        |               | lower-order 8 bits CH6 delay value setting     |

| 1dh            | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_0000b    | higher-order 8 bits                            |

| 1eh            |         |         |         |          | ′7_L      |            |               |          | 0000 0000b    | CH7 delay value setting                        |

| ren            | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        | 0000_0000     | lower-order 8 bits                             |

| 1fh            |         | _       |         |          | 7_H       |            | _             |          | 0000_000b     | CH7 delay value setting                        |

| ш              | 7       | 6       | 5       | 4        | 3         | 2          | 1             | 0        |               | higher-order 8 bits                            |

#### **Register Descriptions**

• Mode setting SUB\_ADDRESS=00h(R/W)

Timing generation of LRCKO, BCKO, and DO0 - 3 outputs, delay register mode, 8-ch/2-ch mode switching and source selection in the 2-ch mode are performed.

Table 11 Mode Setting Register Map

| DATA_BIT      | BIT7 | BIT6 | BIT5    | BIT4 | BIT3    | BIT2   | BIT1 | BIT0 |

|---------------|------|------|---------|------|---------|--------|------|------|

| Register Name | _    | _    | CMN_DLY | THRU | INT_EXT | NOF_CH | DI_  | SEL  |

| WR            |      | _    | V       | V    | V       | V      | V    | V    |

| RD            | 0    | 0    | V       | V    | V       | V      | V    | V    |

| Default Value |      | _    | 0       | 0    | 0       | 1      | 0    | 0    |

V = Valid Data

Table 12 Descriptions of the Mode Setting Register Functions

| Register Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMN_DLY       | Specifies whether the delay value of each channel is set to an equal value or not.  0: Sets each channel to a delay value.  1: Sets each channel to the CH0 delay value.                                                                                                                                                                                                                                                                                                                                                                                                  |

| THRU          | Specifies the output mode.  1: Outputs the input signal specified by the "NOF_CH" or the "DI_SEL" at a delay time of 0.  0: Performs normal delay processing and outputs the input signal.  * While the audio data are input to the DIx (x=0-3) pin (excluding LRCKx and BCKx pins), the setting from normal operation to Through mode and/or from Through mode to normal operation may results in output of the abnormal audio data from the DOx (x=0-3) pin. Therefore, when changing the output mode using this bit, setting the input data to all "0" is recommended. |

| INT_EXT       | Specifies the output timing of LRCK0 / BCK0 / DO0 - 3.  1: Internal generation timing    Outputs data at the timing specified by the TimingGenerate registers.  0: External input timing synchronization    The DO0 - 3 signals are output synchronized to the LRCKIn / BCKn.    LRCKO/BCKO outputs LRCKIn / BCKIn without modification.  * When INT_EXT = "1", set the register so that the FS generated by the TimingGenerate register is coincident with the input FS.                                                                                                 |

| NOF_CH        | Specifies the number of the delay processing channels.  1: 8-ch mode  Samples the DI0 - 3 input pins, performs delay processing for each channel, and outputs data from the DO0 - 3 pins.  0: 2-ch mode  Samples one input out of the DI0-3 pins selected by the "DI_SEL[1:0]" register, performs delay processing of the 4 outputs, and outputs data from the DO0-3 pins (2ch x 4 outputs).  * This setting bit is also valid in Through mode when THRU = "1"                                                                                                            |

| Register Name   | Description                                                                                                                                                                  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DI_SEL<br>[1:0] | Specifies the audio source when "NOF_CH" = "0".  00: DI0  01: DI1  10: DI2  11: DI3  * When "NOF_CH" = "1", this field is meaningless.  This field is valid when THRU = "1". |

## Table 13 Input and Output Relations by NOF\_CH and DI\_SEL[1:0]

| NOF_CH   | DI_SEL[1:0]     | DO0 | DO1 | DO2 | DO3 | ВСКО  | LRCKO  |

|----------|-----------------|-----|-----|-----|-----|-------|--------|

| "1"(8ch) | xx (Don't Care) | DI0 | DI1 | DI2 | DI3 | BCKI0 | LRCKI0 |

|          | 00              | DI0 | DI0 | DI0 | DI0 | BCKI0 | LRCKI0 |

| "0"      | 01              | DI1 | DI1 | DI1 | DI1 | BCKI1 | LRCKI1 |

| (2ch)    | 10              | DI2 | DI2 | DI2 | DI2 | BCKI2 | LRCKI2 |

|          | 11              | DI3 | DI3 | DI3 | DI3 | BCKI3 | LRCKI3 |

• Input data format setting SUB\_ADDRESS=01h(R/W)

This register specifies the data bit length,  $I^2S$ , input data formats (left justified and right justified), and the polarity of the LRCK.

Table 14 Input Data Format Setting Register Map

| DATA_BIT      | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|---------------|------|------|------|------|------|------|------|------|

| Register Name | _    | _    |      | POLI | FN   | /ITI | DI_  | LEN  |

| WR            | _    | _    | _    | V    | V    | V    | V    | V    |

| RD            | 0    | 0    | 0    | V    | V    | V    | V    | V    |

| Default Value | _    | _    | _    | 0    | 0    | 0    | 0    | 0    |

Table 15 Descriptions of Input Data Format Setting Register Functions

| Register Name |                          | Description                          |       |       |       |       |   |  |  |  |  |

|---------------|--------------------------|--------------------------------------|-------|-------|-------|-------|---|--|--|--|--|

|               | Specifies th             | Specifies the polarity of the LRCKI. |       |       |       |       |   |  |  |  |  |

|               | 1: Inverted              |                                      |       |       |       |       |   |  |  |  |  |

|               | 0: Non-inve              | 0: Non-inverted                      |       |       |       |       |   |  |  |  |  |

|               |                          |                                      | POL=1 |       | POL=0 |       | Í |  |  |  |  |

| POLI          |                          |                                      | LRCKI |       | LRCKI |       | Í |  |  |  |  |

|               |                          |                                      | LEFT  | RIGHT | LEFT  | RIGHT | Í |  |  |  |  |

|               |                          | l <sup>2</sup> S                     | 1     | 0     | 0     | 1     | Í |  |  |  |  |

|               |                          | Left justified (MSB)                 | 0     | 1     | 1     | 0     | İ |  |  |  |  |

|               |                          | Right justified (LSB)                | 0     | 1     | 1     | 0     | ı |  |  |  |  |

|               | Specifies th             | e input format.                      |       |       |       |       |   |  |  |  |  |

| FMTI          | 00: Left jus             | tified (MSB)                         |       |       |       |       |   |  |  |  |  |

| [1:0]         | 00: Right ju             | ustified (LSB)                       |       |       |       |       |   |  |  |  |  |

|               | 10, 11: I <sup>2</sup> S |                                      |       |       |       |       |   |  |  |  |  |

|               | Specifies th             | e input data bit length.             |       |       |       |       |   |  |  |  |  |

|               | 00: 16 bits              |                                      |       |       |       |       |   |  |  |  |  |

| DI_LEN        | 01: 20 bits              | 01: 20 bits                          |       |       |       |       |   |  |  |  |  |

| [1:0]         | 10: 24 bits              |                                      |       |       |       |       |   |  |  |  |  |

|               | 11: 32 bits              |                                      |       |       |       |       |   |  |  |  |  |

|               | * This field             | is not valid in Through              | mode. |       |       |       |   |  |  |  |  |

• Output data format setting SUB\_ADDRESS=02h(R/W)

This register specifies the data bit length,  $I^2S$ , output data formats (left justified, and right justified), and the polarity of LRCK.

**Table 16 Output Data Format Setting Register Map**

| DATA_BIT      | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|---------------|------|------|------|------|------|------|------|------|

| Register Name |      |      |      | POLO | FM   | FMTO |      | LEN  |

| WR            | _    | _    | _    | V    | V    | V    | V    | V    |

| RD            | 0    | 0    | 0    | V    | V    | V    | V    | V    |

| Default Value | _    | _    | _    | 0    | 0    | 0    | 0    | 0    |

Table 17 Descriptions of Output Data Format Setting Register Functions

| Register Name |                          | Description                          |       |       |       |       |  |  |  |  |  |

|---------------|--------------------------|--------------------------------------|-------|-------|-------|-------|--|--|--|--|--|

|               | Specifies th             | Specifies the polarity of the LRCKO. |       |       |       |       |  |  |  |  |  |

|               | 1: Inverted              |                                      |       |       |       |       |  |  |  |  |  |

|               | 0: Non-inv               | erted                                |       |       |       |       |  |  |  |  |  |

|               |                          |                                      | POL=1 |       | POL=0 |       |  |  |  |  |  |

| POLO          |                          |                                      | LRCKI |       | LRCKI | _     |  |  |  |  |  |

|               |                          |                                      | LEFT  | RIGHT | LEFT  | RIGHT |  |  |  |  |  |

|               |                          | I <sup>2</sup> S                     | 1     | 0     | 0     | 1     |  |  |  |  |  |

|               |                          | Left justified (MSB)                 | 0     | 1     | 1     | 0     |  |  |  |  |  |

|               |                          | Right justified (LSB)                | 0     | 1     | 1     | 0     |  |  |  |  |  |

|               | Specifies th             | ne output format.                    |       |       |       |       |  |  |  |  |  |

| FMTO          |                          | stified (MSB)                        |       |       |       |       |  |  |  |  |  |

| [1:0]         | -                        | ustified (LSB)                       |       |       |       |       |  |  |  |  |  |

| []            | 10, 11: I <sup>2</sup> S |                                      |       |       |       |       |  |  |  |  |  |

|               | ·                        | ne output data bit length            | h.    |       |       |       |  |  |  |  |  |

|               | 00: 16 bits              | · -                                  |       |       |       |       |  |  |  |  |  |

| DO_LEN        | 01: 20 bits              | 01: 20 bits                          |       |       |       |       |  |  |  |  |  |

| [1:0]         | 10: 24 bits              |                                      |       |       |       |       |  |  |  |  |  |

|               | 11: 32 bits              |                                      |       |       |       |       |  |  |  |  |  |

|               | * This field             | is not valid in Through              | mode. |       |       |       |  |  |  |  |  |

#### • BCKO cycle setting SUB\_ADDRESS=03h(R/W)

This register specifies the cycle of BCKO which is generated internally when INT\_EXT of the mode setting register is "1".

**Table 18 BCKO Cycle Setting Register Map**

| DATA_BIT      | BIT7 | BIT6 | BIT5 | BIT4 | BIT3    | BIT2 | BIT1 | BIT0 |

|---------------|------|------|------|------|---------|------|------|------|

| Register Name |      |      |      |      | BCK_DIV |      |      |      |

| WR            | _    | _    | _    | _    | V       | V    | V    | V    |

| RD            | 0    | 0    | 0    | 0    | V       | V    | V    | V    |

| Default Value |      |      | _    | _    | 0       | 1    | 0    | 0    |

#### • LRCKO Cycle Setting SUB\_ADDRESS=04h(R/W)

This register specifies the cycle of LRCKO which is generated internally when INT\_EXT of the mode setting register is "1".

Table 19 LRCKO Cycle Setting Register Map

| DATA_BIT      | BIT7 | BIT6 | BIT5     | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|---------------|------|------|----------|------|------|------|------|------|

| Register Name |      | _    | LRCK_DIV |      |      |      |      |      |

| WR            | _    | _    | V        | V    | V    | V    | V    | V    |

| RD            | 0    | 0    | V        | V    | V    | V    | V    | V    |

| Default Value |      | _    | 0        | 1    | 0    | 0    | 0    | 0    |

Note: Both of the registers BCK\_DIV and LRCK\_DIV should be configured. The new data is valid if the both registers are configured. For example, when only the BCK\_DIV register is to be changed, the BCK\_DIV register is first configured, then the LRCK\_DIV register should be configured with the value equal to the current value.

Register Name Description Specifies the half cycle of the BCKO. The half cycle is specified according to the number of SYSCLK pulses. When  $BCK_DIV = 0b0001$ , the cycle of the BCKO is 2 x SYSCLK. When BCK\_DIV = 0b0100, the cycle of the BCKO is 8 x SYSCLK. **BCK\_DIV** Set BCK\_DIV to 6 or less. [3:0] (BCK DIV \* SYSCLK) \* 2 BCK DIV \* SYSCLK BCK DIV \* SYSCLK **BCKO** Specifies the half cycle of the LRCKO. The half cycle is specified according to the number of BCKO pulses. When LRCK\_DIV = 0b01\_0000, the cycle of the LRCKO is 32 x BCKO. When LRCK\_DIV =  $0b01_{1000}$ , the cycle of the LRCKO is  $64 \times BCKO$ . LRCK\_DIV (LRCK DIV \* BCKO) \* 2 [5:0] LRCK DIV \* BCKO LRCK DIV \* BCKO **LRCKO**

Table 20 Descriptions of BCKO/LRCKO Cycle Register Functions

Table 21 Examples of Setting BCK\_DIV and LRCK\_DIV

|        | DO LEN        | 00           | 01                | 10           | 11           |

|--------|---------------|--------------|-------------------|--------------|--------------|

|        | DO_LEN        | (16 bits)    | (20bits)          | (24 bits)    | (32 bits)    |

| SYSCLK | Register Name |              |                   |              |              |

| E40E0  | BCK_DIV       |              | 0100 (4)          | 0100 (4)     | 0100 (4)     |

| 512FS  | LRCK_DIV      |              | 10_0000 (32)      | 10_0000 (32) | 10_0000 (32) |

| 20450  | BCK_DIV       | 0110 (6)     | 0100 (4) 0100 (4) |              | 0011 (3)     |

| 384FS  | LRCK_DIV      | 01_0000 (16) | 01_1000 (24)      | 01_1000 (24) | 10_0000 (32) |

| 25650  | BCK_DIV       | 0100 (4)     | 0010 (2)          | 0010 (2)     | 0010 (2)     |

| 256FS  | LRCK_DIV      | 01_0000 (16) | 10_0000 (32)      | 10_0000 (32) | 10_0000 (32) |

| 10255  | BCK_DIV       | 0011 (3)     | 0010 (2)          | 0010 (2)     |              |

| 192FS  | LRCK_DIV      | 01_0000 (16) | 01_1000 (24)      | 01_1000 (24) |              |

| 40000  | BCK_DIV       | 0010 (2)     |                   |              |              |

| 128FS  | LRCK_DIV      | 01_0000 (16) |                   |              |              |

<sup>\*1:</sup> When ENBL is set to "1" with the configuration of BCK\_DIV x LRCK\_DIV over 192, the CFG\_ERR bit is set to "1" and the delay operation is not started.

<sup>\*2:</sup> Both of the registers BCK\_DIV and LRCK\_DIV should be configured. The new data is valid if the both registers are configured. For example, when only the BCK\_DIV register is to be changed, the BCK\_DIV register should be configured and then the LRCK\_DIV register should be configured with the value equal to the current value.

• DRAM refresh interval setting SUB\_ADDRESS=05h(R/W)

## Table 22 DRAM Refresh Interval Setting Register Map

| DATA_BIT      | BIT7 | BIT6 | BIT5     | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|---------------|------|------|----------|------|------|------|------|------|

| Register Name | _    | _    | REF_ITVL |      |      |      |      |      |

| WR            | _    | _    | V        | V    | V    | V    | V    | V    |

| RD            | 0    | 0    | V        | V    | V    | V    | V    | V    |

| Default Value | _    | _    | 0        | 1    | 0    | 1    | 1    | 0    |

## Table 23 Descriptions of DRAM Refresh Interval Setting Register Functions

| Register Name     | Description                                                                                                                                                                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF_ITVL<br>[5:0] | Specifies the DRAM refresh interval.  The refresh interval is 8 x SYSCLK x REF_ITVL.  The value (refresh interval) should be set around 14 µs (15.6µs x 0.9) by this register. |

## Table 24 Examples of REF\_ITVL Setting by SYSCLK

|       | 32kHz                      | 44.1kHz                    | 48kHz                      | 96kHz                      | 192kHz                     |

|-------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| 512FS | 01_1101 (29)<br>(14.16 µs) | 10_1000 (40)<br>(14.17 µs) | 10_1011 (43)<br>(13.99 µs) | 1                          |                            |

| 384FS | 01_0110 (22)<br>(14.32 µs) | 01_1110 (30)<br>(14.17 µs) | 10_0000 (32)<br>(13.88 µs) | 1                          |                            |

| 256FS | 00_1110 (14)<br>(13.67 µs) | 01_0100 (20)<br>(14.17 µs) | 01_0110 (22)<br>(14.32 µs) | 10_1011 (43)<br>(13.99 µs) |                            |

| 192FS | 00_1011 (11)<br>(14.32 µs) | 00_1111 (15)<br>(14.17 μs) | 01_0000 (16)<br>(13.88 µs) | 10_0000 (32)<br>(13.88 µs) |                            |

| 128Fs | 00_0111 (07)<br>(13.67 µs) | 00_1010 (10)<br>(14.17 μs) | 00_1011 (11)<br>(14.32 µs) | 01_0110 (22)<br>(14.32 µs) | 10_1011 (43)<br>(13.99 µs) |

## Table 25 SYSCLK Cycle by SYSCLK Input

|       | 32kHz      | 44.1kHz    | 48kHz      | 96kHz     | 192kHz    |

|-------|------------|------------|------------|-----------|-----------|

| 512FS | 61.035 ns  | 44.289 ns  | 40.690 ns  | -         | -         |

| 384FS | 81.380 ns  | 59.051 ns  | 54.253 ns  | 1         | 1         |

| 256FS | 122.070 ns | 88.577 ns  | 81.380 ns  | 40.690 ns | 1         |

| 192FS | 162.760 ns | 118.103 ns | 122.070 ns | 54.253 ns | 1         |

| 128Fs | 244.141 ns | 177.154 ns | 162.760 ns | 81.380 ns | 40.690 ns |

• Software reset SUB\_ADDRESS=06h(R/W)

## Table 26 Software Reset Register Map

| DATA_BIT      | BIT7    | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|---------------|---------|------|------|------|------|------|------|------|

| Register Name | SFT_RST |      |      |      | _    | _    | _    |      |

| WR            | V       | _    | _    | _    | _    | _    | _    | _    |

| RD            | V       | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Default Value | 0       | _    | _    | _    | _    | _    | _    | _    |

## Table 27 Descriptions of Software Reset Register Functions

| Register Name | Description                                                                                  |

|---------------|----------------------------------------------------------------------------------------------|

|               | Specifies the execution of software reset.                                                   |

| SFT RST       | 0: NOP  1: Resets all the blocks except the I <sup>2</sup> C block.                          |

| SFI_KSI       | This reset is done in the same manner as the hardware reset except that the I <sup>2</sup> C |

|               | block is not reset. When the reset is done, this bit is cleared automatically.               |

• Delay operation start/stop, interrupt mask control SUB\_ADDRESS=07h(R/W)

**Table 28 Delay Operation Control Register Map**

| DATA_BIT      | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1          | BIT0        |

|---------------|------|------|------|------|------|------|---------------|-------------|

| Register Name | ENBL |      | _    |      |      | _    | AUTOR<br>STRT | INT<br>MASK |

| WR            | V    | _    | _    | _    | _    | _    | V             | V           |

| RD            | V    | 0    | 0    | 0    | 0    | 0    | V             | V           |

| Default Value | 0    | _    | _    | _    | _    | _    | 0             | 0           |

## **Table 29 Descriptions of Delay Operation Control Register Functions**

| Register Name | Description                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Controls the delay operation.                                                                                                                                   |

|               | 0: Stop                                                                                                                                                         |

|               | 1: Start                                                                                                                                                        |

| ENBL          | * When the CFG_ERR bit is set due to the inconsistency in the setting even if the ENBL register is set to "1", the delay operation is not started.              |

|               | When the synchronization of LRCK and BCK is lost during the delay operation, the ENBL register is set to "0" and the operation is suspended (AUTORSTRT = 0).    |

|               | Performs resynchronization automatically when an input timing error occurs.                                                                                     |

|               | 0: NOP                                                                                                                                                          |

| AUTORSTRT     | 1: Automatic resynchronization                                                                                                                                  |

| , ioronomi    | * When this register is set to "1", the INT output is fixed to a "H" level even if the INT_MASK is "0" except when the delay operation is suspended by CFG_ERR. |

|               | However, the error statuses which cause interrupts are set.                                                                                                     |

|               | Masks interrupt outputs.                                                                                                                                        |

|               | 0: NOP                                                                                                                                                          |

| INT_MASK      | 1: Mask                                                                                                                                                         |

|               | * When this register is set to "1", the error statuses which cause interrupts are masked though the INT output is fixed to a "H" level.                         |

• Operation Status SUB\_ADDRESS=08h(R/W)

## **Table 30 Operation Status Register Map**

| DATA_BIT      | BIT7 | BIT6    | BIT5    | BIT4 | BIT3 | BIT2    | BIT1     | BIT0 |

|---------------|------|---------|---------|------|------|---------|----------|------|

| Register Name | RUN  | SRC_CHG | SRC_CLK |      |      | CFG_ERS | DRAM_RDY | INIT |

| WR            |      | _       | _       |      |      | _       |          | _    |

| RD            | V    | V       | V       | 0    | 0    | V       | V        | V    |

| Default Value | 0    | _       |         |      |      | _       |          | _    |

## **Table 31 Descriptions of Operation Status Register Functions**

|               | Able 31 Descriptions of Operation Status Register Functions                                                                                                                                                                                                                                                                                                                                                                |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 1: Indicates that the delay operation is being performed.                                                                                                                                                                                                                                                                                                                                                                  |

|               | 0: Indicates that the delay operation is being suspended.                                                                                                                                                                                                                                                                                                                                                                  |

| RUN           | * When various settings are correct after the ENBL bit is set to '1' and input data formats are recognized correctly, the delay operation is started and the register is set to '1'. When an error is detected while the input data formats are recognized, the register is remained '0'. The register is set to '0' when the TMG_ERR bit is set to '1' by the change of the input signal or when the ENBL bit is cleared. |

|               | 1: Indicates the input switching sequence is ready when switching 8ch $\to$ 2ch or switching the source in the 2-ch mode.                                                                                                                                                                                                                                                                                                  |

| SRC_CHG       | This bit is changed to '1' when the input masking is performed by changing of input and output formats. When the ENBL bit is set while this bit is being set, the delay operation is not started until the interval operation is completed and this bit is cleared.                                                                                                                                                        |

|               | 1: Indicates the clock of the clock source which is being selected is internally valid.                                                                                                                                                                                                                                                                                                                                    |

| SRC_CLK       | 0: Indicates the clock of the clock which is being selected is internally invalid.                                                                                                                                                                                                                                                                                                                                         |

| OKO_OLK       | * This bit is changed to '0' when the clock masking is performed by changing of input source.                                                                                                                                                                                                                                                                                                                              |

|               | 1: Indicates any inconsistency arises from the various setting values.                                                                                                                                                                                                                                                                                                                                                     |

| CFG_ERS       | 0:                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CFG_ER3       | * The delay operation is not started when the ENBL bit is set while this bit is being set. This bit is changed each time data is written in each setting register.                                                                                                                                                                                                                                                         |

|               | 1: Indicates the initialization of the internal DRAM is completed and normal operations are ready.                                                                                                                                                                                                                                                                                                                         |

| DRAM_RDY      | 0: Indicates the internal DRAM is being initialized.                                                                                                                                                                                                                                                                                                                                                                       |

|               | * When the ENBL bit is set while this bit is being set, the delay operation is postponed until initialization of the internal DRAM is completed.                                                                                                                                                                                                                                                                           |

| INIT          | 1: Indicates initialization is in progress. 0:                                                                                                                                                                                                                                                                                                                                                                             |

• Error status SUB\_ADDRESS=09h(R/W)

## **Table 32 Error Status Register Map**

| DATA_BIT      | BIT7    | BIT6    | BIT5    | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|---------------|---------|---------|---------|------|------|------|------|------|

| Register Name | TMG_ERR | CFG_ERR | BCK_ERR | OVRN | UDRN |      |      | _    |

| WR            | V       | V       | V       | V    | V    | _    | _    | _    |

| RD            | V       | V       | V       | V    | V    | 0    | 0    | 0    |

| Default Value | 0       | 0       | 0       | 0    | 0    | _    | _    | _    |

## Table 33 Descriptions of the Status Register Functions

| Register Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|